Лекция 4. Операционные блоки цифровых устройств. Принципы работы и основные характеристики.

Преподаватель: Джунусов Нуридин Ауелович, лектор. Кафедры «Электроники, телекоммуникаций и космических технологий»

n.aueluly@gmail.com

## Содержание

- 1. Операционные блоки цифровых устройств.

- 2. Принципы работы и основные характеристики.

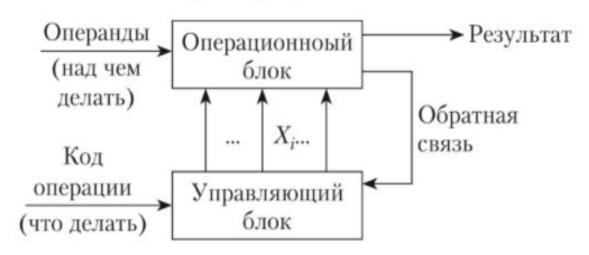

### Структура цифрового устройства

Операционный блок состоит из операционных элементов, набор которых может быть одним и тем же для выполнения разных алгоритмов обработки.

Под действием кода операции управляющий блок вырабатывает последовательность управляющих сигналов  $X_i$  в течение необходимого числа тактов, порождающих в операционном блоке нужную последовательность микроопераций.

#### Введение

Набор микроопераций в каждом вычислителе свой и колеблется от нескольких единиц до нескольких десятков. Наиболее часто используются такие микрооперации:

- установка <слово> : = <число>;

- передача <слово> : = <слово1>;

- 3) счет <слово>: = <слово $> \pm 1$ ;

- 4) сложение <слово> := <слово1> + <слово2> := <

- дизъюнкция <слово> : = <слово1> ∨ <слово2>;

- 6) конъюнкция <слово> : = <слово $1> \land <$ слово2>;

- 7) инверсия <слово> : = < слово1 > (поразрядная инверсия двоичных разрядов);

- 8) логическая неравнозначность (или сумма по модулю два) <слово>: = <слово1> ⊕ <слово2>;

- 9) логическая равнозначность <слово> := <слово $1> \infty <$ слово2>, где  $\infty$  подобие;

- 10) сдвиг <слово> : =  $R_m <$ слово1> (R- сдвиг вправо на m бит);  $L_m <$ слово1> (L- сдвиг влево на m бит).

Эти и другие микрооперации выполняются операционными элементами.

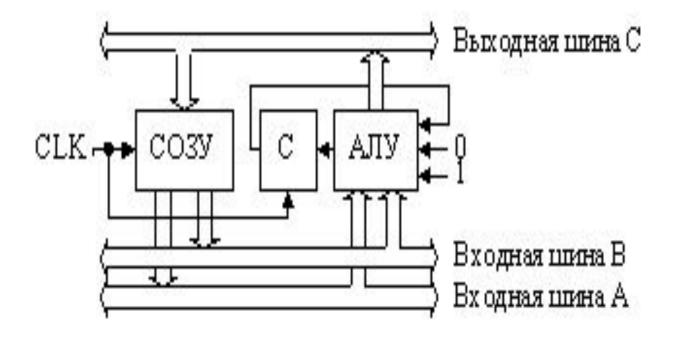

### Трёхшинная структура операционного блока микропроцессора

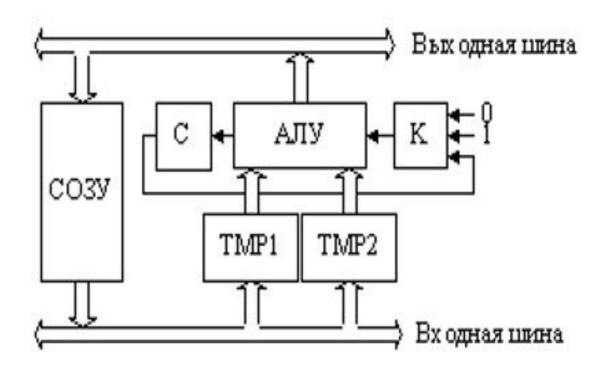

## Двухшинная структура операционного блока микропроцессора

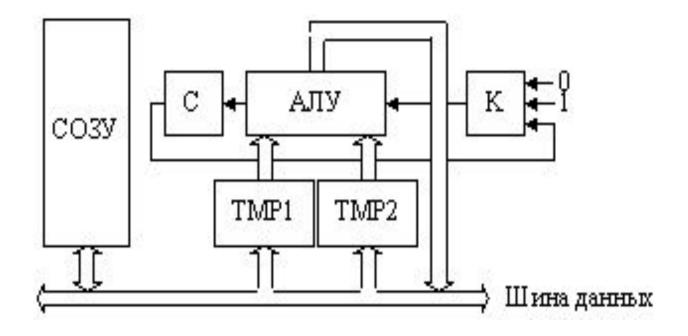

## Одношинная структура операционного блока микропроцессора

#### Шина

В настоящее время схемы с тремя состояниями широко используются для построения шин. Шина представляет собой проводник к которому могут подключаться несколько микросхем. При этом часть из них используют этот проводник для передачи по нему цифрового сигнала, а часть используют его для получения информации. То есть этот проводник может быть использован в качестве элемента коммутации.

При этом особенно важно, что в отличие от коммутаторов ( мультиплексоров и демультиплексоров) количество входов и выходов в шине заранее не определено. Поэтому к шине можно подключать (и отключать) устройства без перенастройки принципиальной схемы.

Часто в микросхеме, содержащей элементы с тремя состояниями выходного каскада объединяют управляющие сигналы всех элементов в один провод. (точно так же как это делалось в параллельных регистрах) Такие микросхемы называют шинными формирователями и изображают на схемах как показано на рисунке 7.

| 4         | 0 | $\triangleright$ | $\nabla$ |   |

|-----------|---|------------------|----------|---|

| $\exists$ | 1 |                  | 0        | H |

| $\dashv$  | 2 |                  | 1        | H |

| -         | 3 |                  | 2        | - |

| $\dashv$  | V |                  | 3        | r |

Рисунок 7. Условно-графическое обозначение шинного формирователя

## Функциональное назначение АЛУ

АЛУ – узел электронновычислительных устройств, предназначенный для выполнения логических, арифметических операций и операций сравнения.

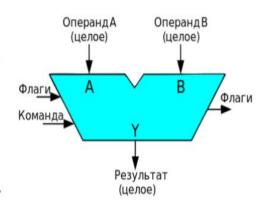

#### Условное обозначение АЛУ

Рассмотрим типовое АЛУ. ВИС имеются входы чисел А и В, входы выбора операций S, вход переноса Сх из младшего разряда и вход М, сигнал которого задает тип выполняемых операций: логические (M= 1) или арифметико-логические (M = 0). Результат операции вырабатывается на выходах F. Выходы G и H используются для организации параллельных переносов при наращивании разрядности обрабатываемых слов. Сигнал С о — выходной перенос в старший разряд, а выход «A = B» выход, равный «1» при условии A = B.

## АЛУ как отдельная микросхема

АЛУ имеет входы операндов А и В, входы выбора операций S, вход переноса Cі и вход М (Mode), сигнал которого задает тип выполняемых операций: логические (М = 1) или арифметикологические (М = 0). Результат операции вырабатывается на выходах F, выходы G и H дают функции генерации и прозрачности, используемые для организаций параллельных переносов при наращивании размерности АЛУ. Сигнал С0 — выходной перенос, а выход А = В есть выход сравнения на равенство с открытым коллектором.

# Обобщённая блок-схема арифметико-логического устройства (АЛУ).

### Арифметико – логическое устройство

**АЛУ** — устройство, предназначенное для выполнения логических и математически операций над двоичными числами. АЛУ входит в состав любого микропроцессора.

ALU - Arithmetic Logic Unit

#### По способу действия над операндами АЛУ делят на:

- Параллельные Операнды представляются параллельным кодом и операции совершаются одновременно над всеми разрядами операндов.

- 2. Последовательные Операции над операндами производятся последовательно во времени над их отдельными разрядами.

Стрелками указаны выходные входные И Флаги слова. (например, признаки сравнения результата операндов) выполнения предыдущей операции (вход) результата выполнения текущей (выход). операции одноместных операциях таких, например, как битов инверсия слова битовый или СДВИГ второй операнд (В) не участвует в операции. Слово команды указывает необходимую операцию.

#### Принцип работы

| Состояние входов S |    |    | ов S | Состояние входа М |                |

|--------------------|----|----|------|-------------------|----------------|

| <b>S3</b>          | S2 | S1 | SO   | M=1               | M=0 (C=0)      |

| 0                  | 0  | 0  | 0    | Α                 | AV1            |

| 0                  | 0  | 0  | 1    | A+B               | (A+B)\/1       |

| 0                  | 0  | 1  | 0    | A+B               | (A+B)\/1       |

| 0                  | 0  | 1  | 1    | 0                 | 0              |

| 0                  | 1  | 0  | 0    | A+B               | (A\/A)x(B\/1)  |

| 0                  | 1  | 0  | 1    | В                 | (A+B)\/A(B\/1) |

| 0                  | 1  | 1  | 0    | AxB\/AxB          | A-B            |

| 0                  | 1  | 1  | 1    | AxB               | AxB            |

| 1                  | 0  | 0  | 0    | A+B               | A\/AxB\/1      |

| 1                  | 0  | 0  | 1    | AxB+AxB           | A\/B\/1        |

| 1                  | 0  | 1  | 0    | В                 | (A+B)\/AxB\/1  |

| 1                  | 0  | 1  | 1    | AxB               | AxB            |

| 1                  | 1  | 0  | 0    | 1                 | A\/A\/1        |

| 1                  | 1  | 0  | 1    | A+B               | (A+B)\/A1\/1   |

| 1                  | 1  | 1  | 0    | A+B               | (A+B)\/A\/1    |

| 1                  | 1  | 1  | 1    | Α                 | Α              |

УГО четырехразрядного АЛУ

В зависимости от значений, поступающих на входы S и M, выполняется одна из 32 возможных операций. Разные операции требуют различного количества времени на свое выполнение.

## АЛУ

- Арифметико-логические устройства АЛУ (ALU, Arithmetic-Logic Unit) выполняют над словами ряд действий.

- Основой АЛУ служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛУ и обеспечивающей его перестройку с одной операции на другую.

## АЛУ как отдельная микросхема

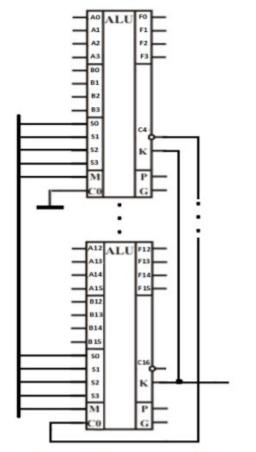

- Обычно АЛУ четырехразрядные и для наращивания разрядности объединяются с формированием последовательных или параллельных переносов.

- В силу самодвойственности выполняемых операций условное обозначение и таблица истинности АЛУ встречаются в двух вариантах, отличающихся взаимно инверсными значениями переменных.

### Увеличение разрядности АЛУ

Последовательное - выход переноса предыдущей ИС соединяется со входом переноса последующей, пока не будет получена требуемая разрядность. При этом во всех АЛУ входы выбора операции и ее типа соединяются общей шиной.

При последовательном соединении АЛУ увеличивается время выполнения операции, что уменьшает быстродействие конечного устройства. Для устранения этого недостатка в АЛУ предусмотрены выходы быстрого переноса, используемые при параллельном соединении.

Схема последовательного подключения АЛУ

### Увеличение разрядности АЛУ

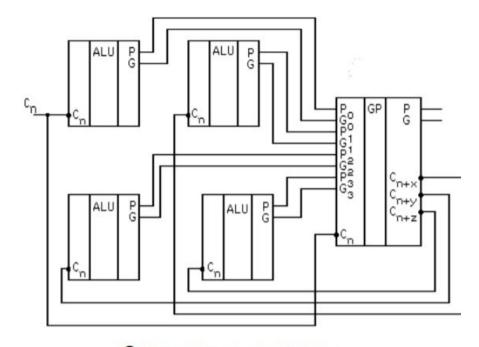

Параллельное — для этого типа подключения используются специальные микросхемы, называемые схемами ускоренного переноса. Выходы G и Р АЛУ подключаем к аналогичным входам G и Р схемы УП, а выходы переноса последней ко входам переноса АЛУ. При этом входы М всех микросхем должны быть объединены

Схема параллельного подключения АЛУ