Элементы задержки, формирования, обнаружения и генерации импульсов. Типовые ситуации в схемотехнике ЛЭ.

Кафедра ВТ и СУ, ВЛГУ, Туляков В.С.

#### Элементы задержки

□ Применяются для согласования времени распространения сигналов по цепям схемы, с целью борьбы с эффектом гонок.

- Последовательные схемы ЛЭ;

- RC цепи;

- Схемы деления частоты тактовых сигналов;

- Отрезки кабеля.

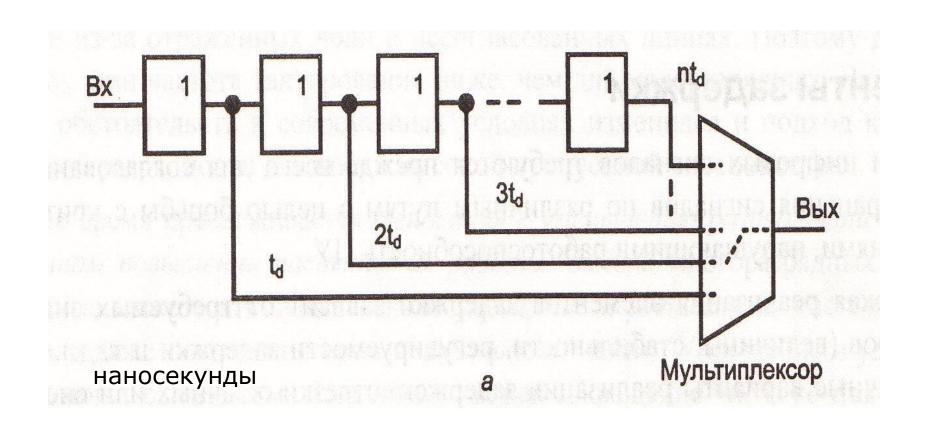

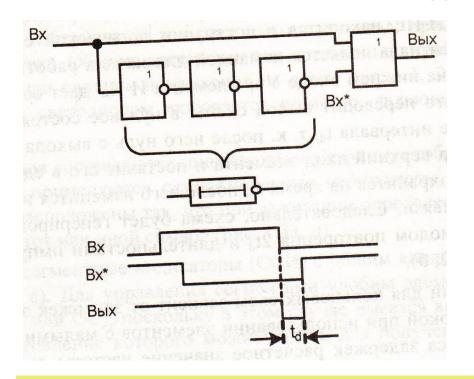

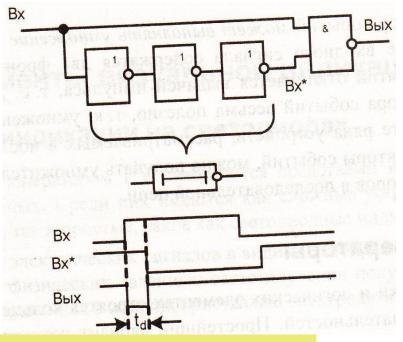

## Схемы задержки на ЛЭ

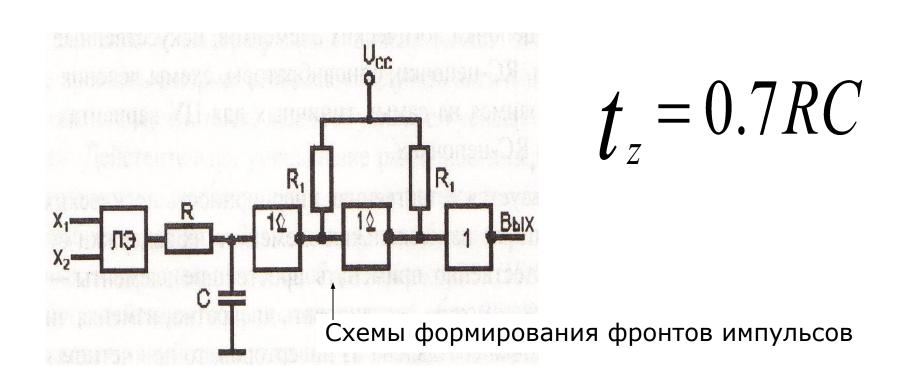

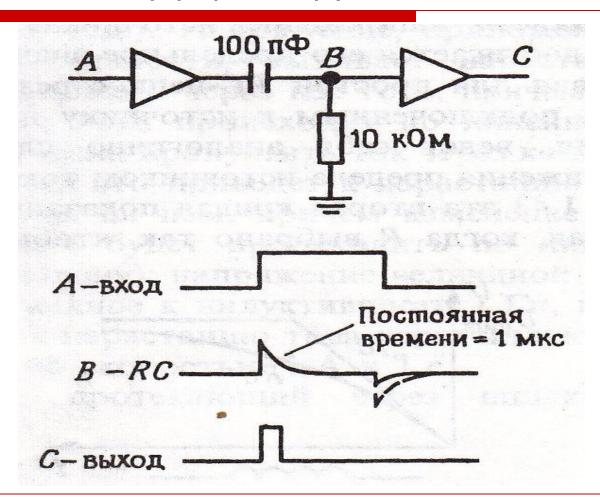

#### Схемы задержки на RC элементах

Для формирования микросекундных задержек

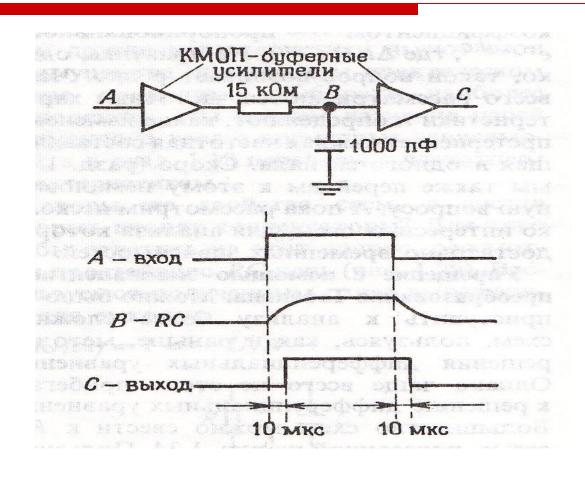

### Использование RC-цепи для задержки цифрового сигнала

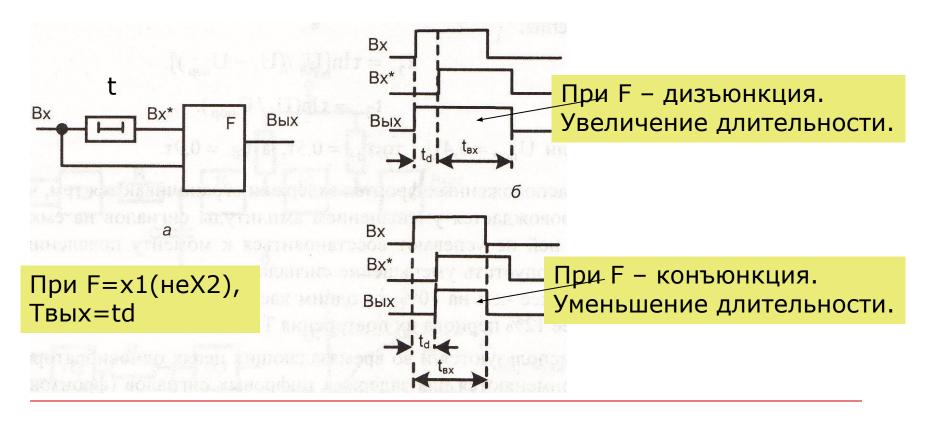

# Формирование импульсов по длительности

Это задачи расширения, сужения и стандартизации длительности сигнала с помощью элементов задержки.

#### Разностные преобразователи

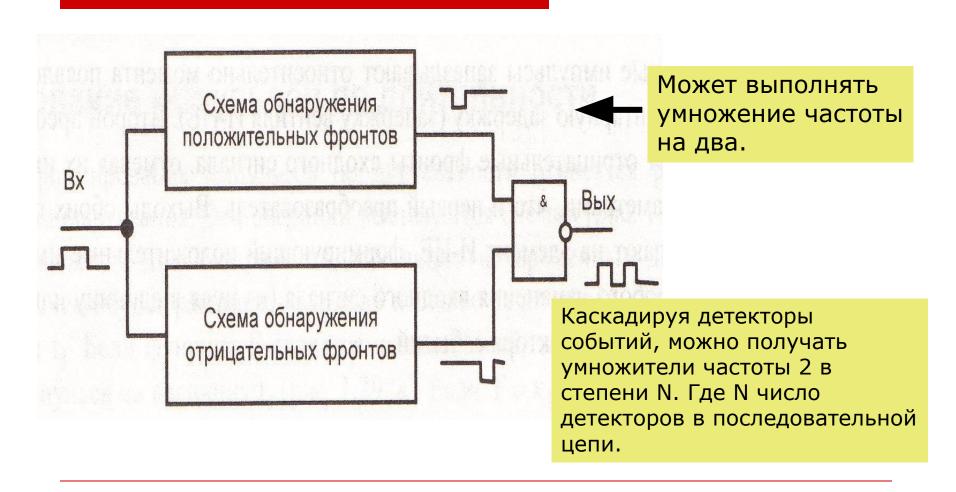

Это схемы формирующие стандартный импульс в ответ на изменение входного сигнала.

# Выделение переднего фронта импульса с помощью дифференцирующей цепи

# Детектор событий

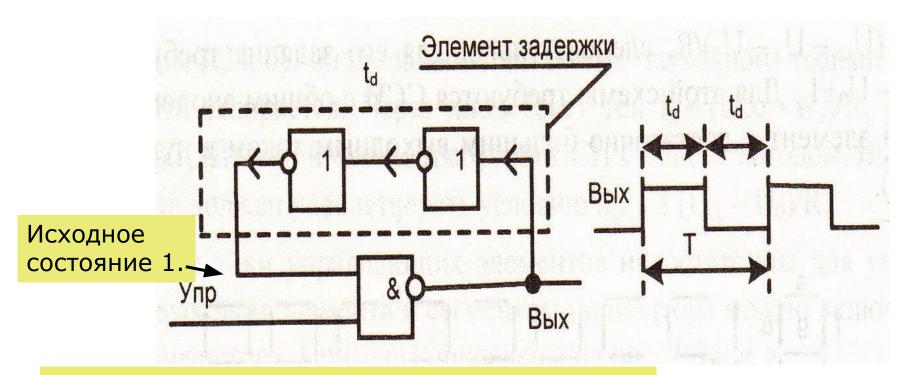

## Кольцевой генератор

Изменение управляющего сигнала с 0 на 1 запускает работу генератора.

#### Некоторые типовые ситуации

- Режимы неиспользуемых выходов.

- Согласование уровней сигналов при использовании разнотипных ЛЭ.

- Режимы неиспользуемых элементов.

- Наращивание числа входов.

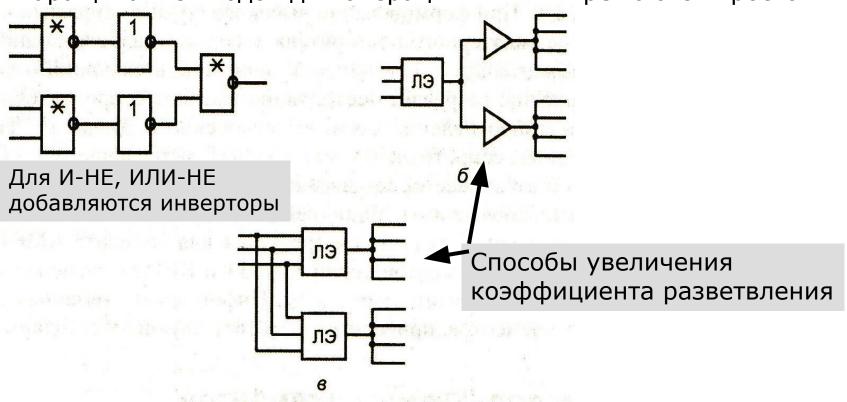

- Снижение нагрузки на выходах ЛЭ.

Или увеличение коэффициента разветвления.

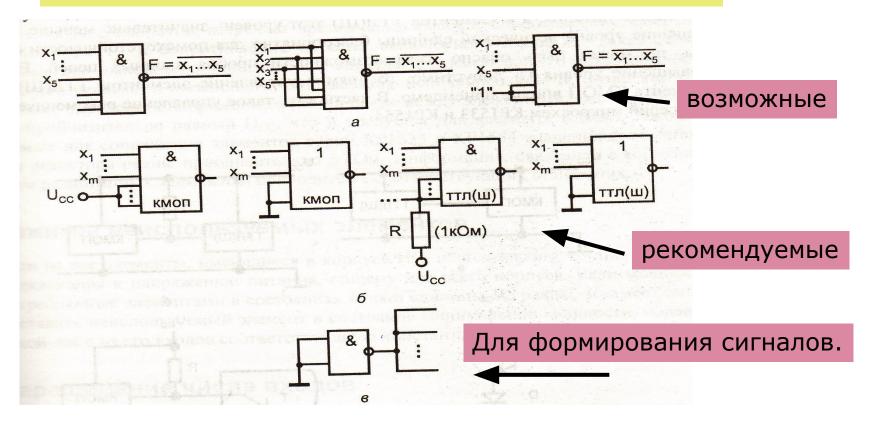

#### Режимы не используемых входов

Данный вопрос решается с учетом типа базовых ЛЭ.

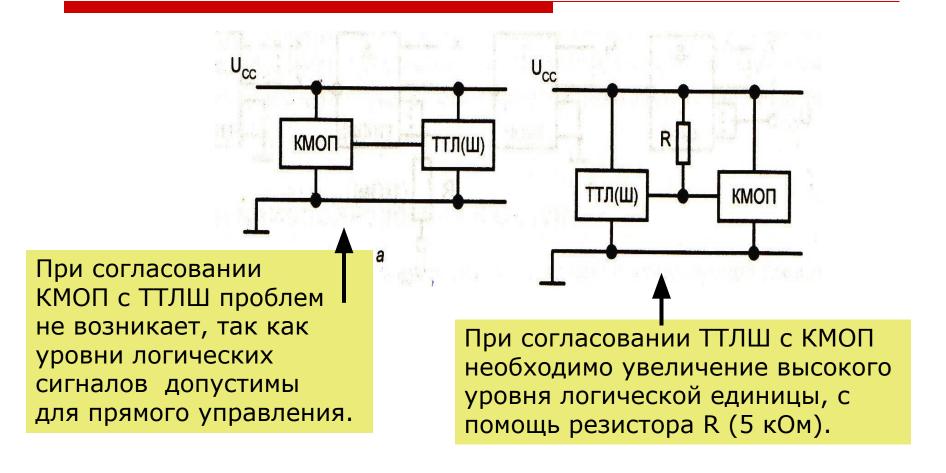

# Согласование уровней сигналов при сопряжении разнотипных ЛЭ

#### Неиспользуемые элементы

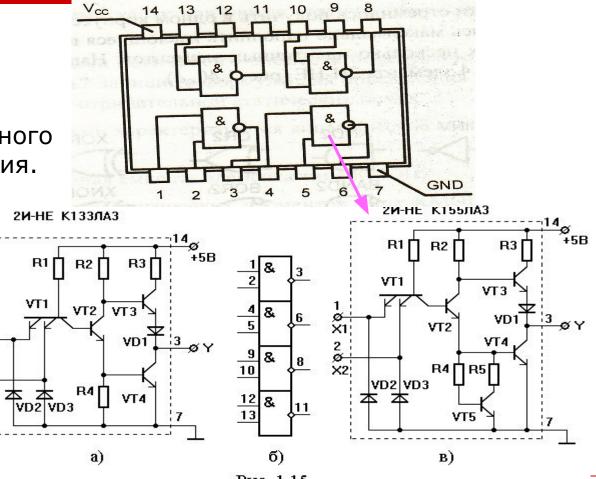

13

12

Vcc

VT1

Ø X1

Необходимо обеспечить режим минимального энергопотребления.

10

11

9

Рис. 1.15

#### Наращивание числа входов ЛЭ и увеличение коэффициента разветвления

Наращивание входов для операций И и ИЛИ решаются просто.

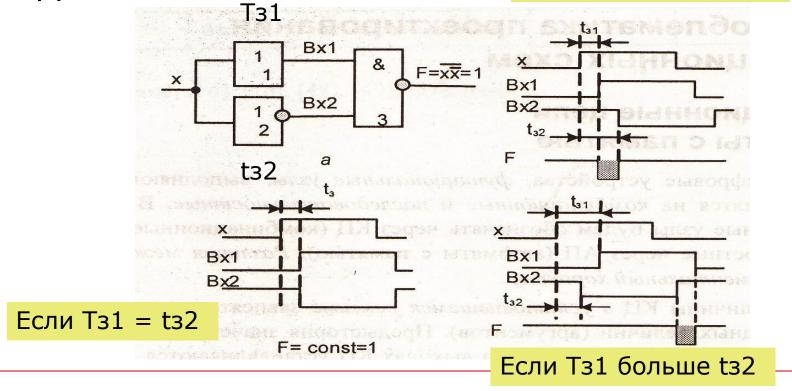

#### Риски сбоя в работе схемы

Статические.

Динамические.

ЕслиТз1 меньше tз2

#### Методы борьбы с рисками

- □ Синтез схем свободных от рисков.

Предполагает сложный анализ процессов в схеме и введение избыточных элементов для исключения рисков. Данный метод практически не применяется, точнее редко.

- Запрещение восприятия сигналов комбинационной схемы элементами памяти, на время переходных процессов. Данный метод является основным.

#### Диаграмма приема сигналов в КС

Момент окончания переходного процесса в КЦ

Момент изменения входных сигналов