# ИНФОРМАТИКА

# 1.3. Логические основы построения компьютеров

1.3.1. Логические операции

1.3.2. Логические элементы ЭВМ

#### Логические элементы ЭВМ

- Базовые логические схемы

- **Триггеры**

- Регистры

- Полусумматор

- Сумматор

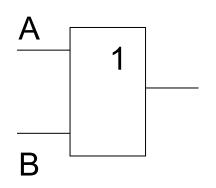

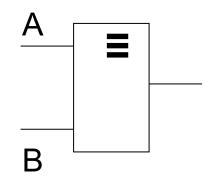

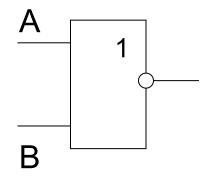

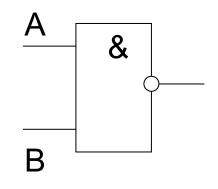

# ГОСТ 2.743-91 Базовые элементы (УГО)

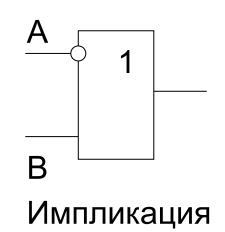

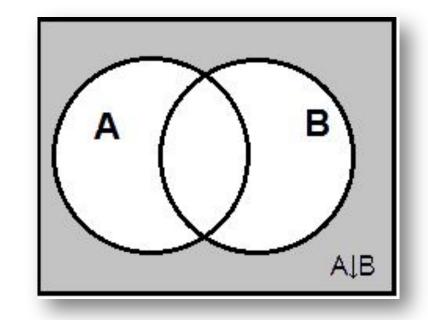

Дизъюнкция

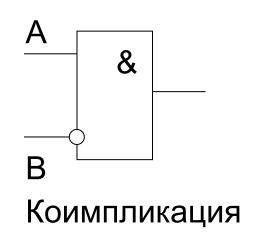

Эквивалентность

Элемент Вебба

Элемент Шеффера

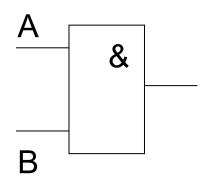

Конъюнкция

#### Базовые логические схемы

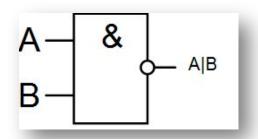

**И-НЕ (штрих Шеффера)** — логический элемент, реализующий операцию значение которой ложно только тогда когда ложны значения обоих ее аргументов.

| A | В | A B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

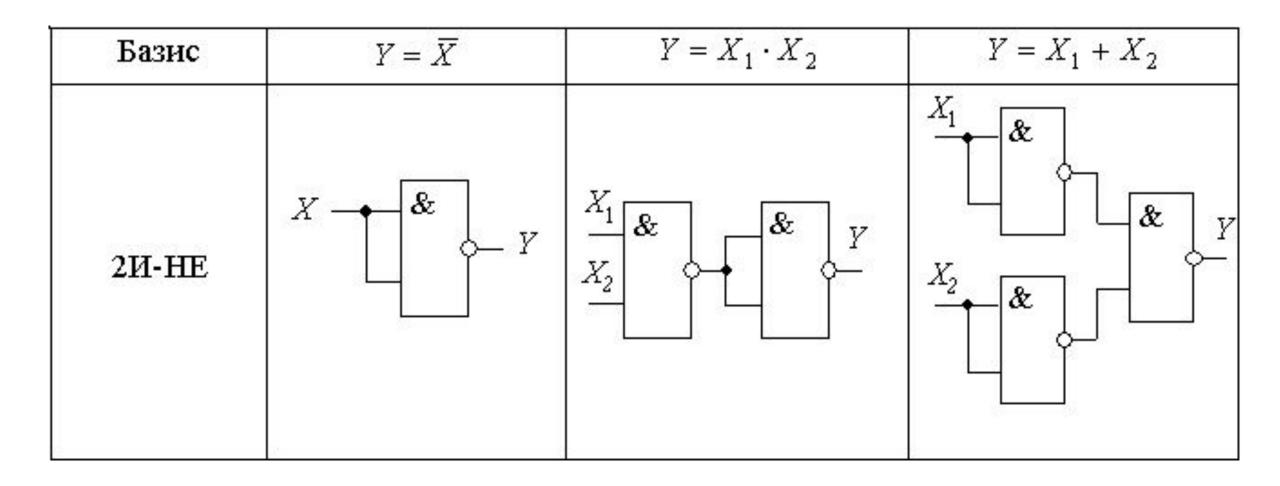

#### Базис И-НЕ

#### Базовые логические схемы

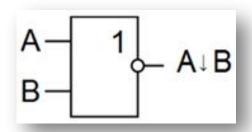

**ИЛИ-НЕ (стрелка Пирса)** — логический элемент, реализующий операцию значение которой истинно только тогда когда ложны значения обоих ее аргументов.

| A | В | $\mathbf{A} \!\!\downarrow \!\! \mathbf{B}$ |

|---|---|---------------------------------------------|

| 0 | 0 | 1                                           |

| 0 | 1 | 0                                           |

| 1 | 0 | 0                                           |

| 1 | 1 | 0                                           |

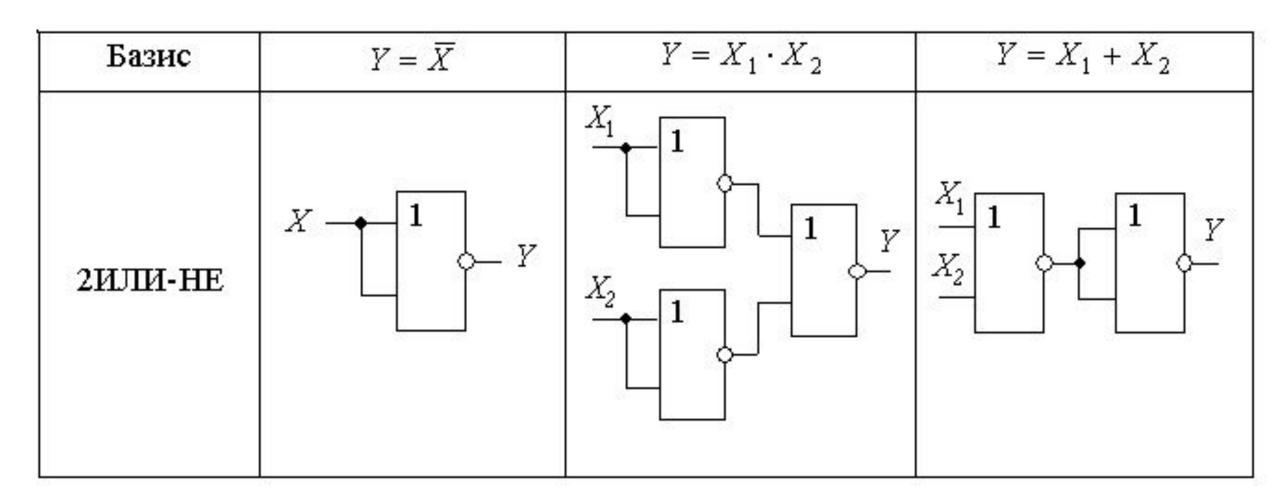

#### Базис ИЛИ-НЕ

#### Базовые логические схемы

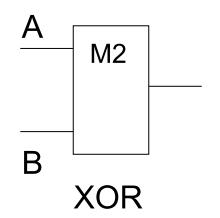

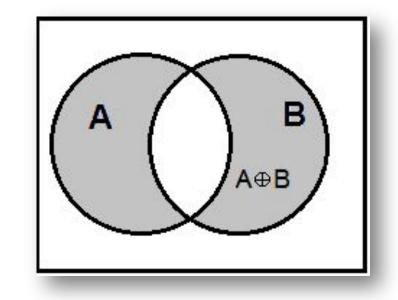

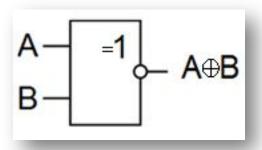

**Исключающее ИЛИ (XOR)** — логический элемент, реализующий операцию значение которой истинно тогда, когда значение одного из аргументов истинно, а второго — ложно.

| A | В | A⊕B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

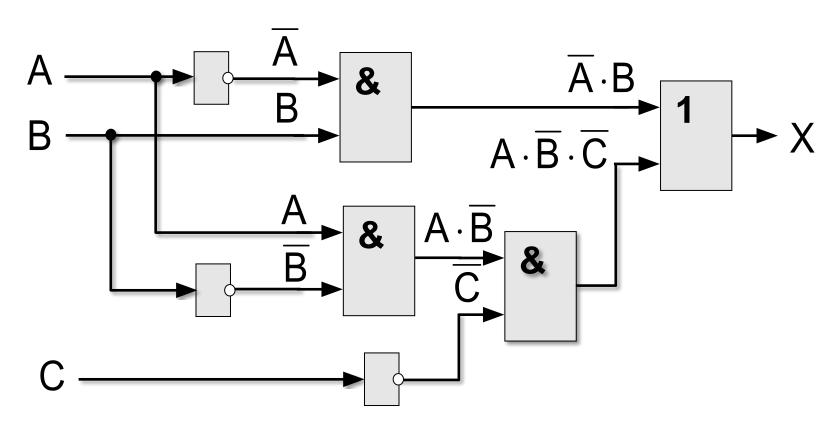

# Пример 1

$$X = \overline{A} \cdot B + A \cdot \overline{B} \cdot \overline{C}$$

Пример взят с сайта: http://kpolyakov.spb.ru/

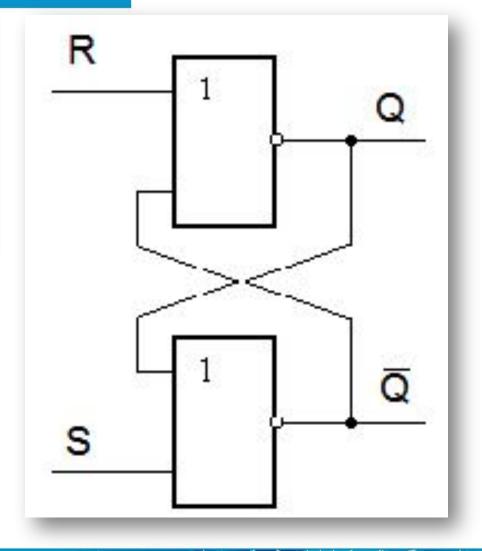

### Триггеры

**Триггер** — класс устройств, способных длительно находится в одном из двух устойчивых состояний (логический «0» или логическая «1») и чередовать их под действием внешних сигналов.

| S | R | Q                     |   | Режим                  |

|---|---|-----------------------|---|------------------------|

| 1 | 0 | 1                     | 0 | Установка 1            |

| 0 | 1 | 0                     | 1 | Установка 0            |

| 0 | 0 | Последнее<br>значение |   | Хранение<br>информации |

| 1 | 1 | Запрещено             |   |                        |

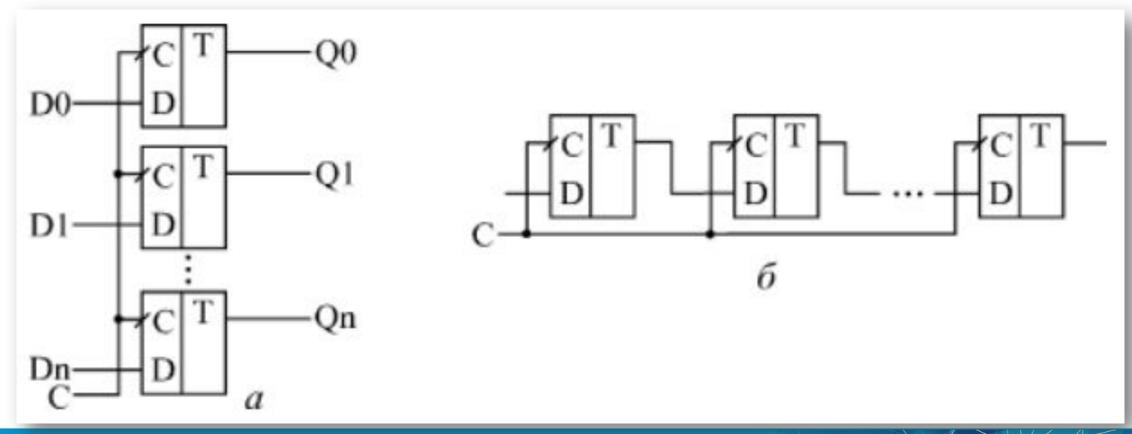

#### Регистры

**Регистр** — класс устройств, представляющих собой несколько **триггеров**, соединенных способом, зависящим от типа регистра.

**Регистры** — основа сверхоперативной памяти компьютера.

# Регистры. Пример

В зависимости от способа соединения регистры делятся на **параллельные регистры** (a) и **регистры сдвига** ( $\delta$ ).

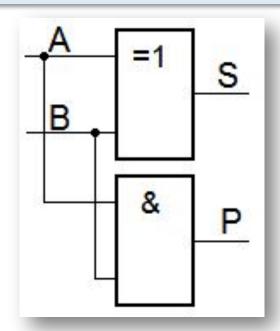

#### Полусумматор

**Полусумматор** — логическая схема, имеющая два входа и два выхода (двухразрядный бинарный сумматор), которая позволяет вычислить сумму разрядов двоичных чисел **A** и **B**, результатом будут два бита **S** —бит суммы по модулю 2, **P** — бит переноса.

| A | В | S | P |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

# Сумматор

**Сумматор** — логическая схема, имеющая три входа и два выхода, которая позволяет вычислить сумму разрядов двоичных чисел **A** и **B** с учетом переноса из предыдущего разряда **P**<sub>n-1</sub>, результатом будут **S** — бит суммы по модулю и **P** — бит переноса.

| A | B | $P_{n-1}$ | S | P |

|---|---|-----------|---|---|

| 0 | 0 | 0         | 0 | 0 |

| 0 | 0 | 1         | 0 | 1 |

| 0 | 1 | 0         | 0 | 1 |

| 0 | 1 | 1         | 1 | 0 |

| 1 | 0 | 0         | 0 | 1 |

| 1 | 0 | 1         | 1 | 0 |

| 1 | 1 | 0         | 1 | 0 |

| 1 | 1 | 1         | 1 | 1 |

# Спасибо за внимание!

#### Уржумов Даниил Владимирович

старший преподаватель кафедры информатики ФГБОУ ВО «ПГТУ», г. Йошкар-Ола

urzhumovdv@volgatech.net

#### Ипатов Юрий Аркадьевич

к.т.н., доцент кафедры информатики ФГБОУ ВО «ПГТУ», г. Йошкар-Ола ipatovya@volgatech.net

# Источники информации

- 1. Информатика: теоретические разделы : учебное пособие / Л. А. Бояркина, Л. П. Ледак, А. В. Кревецкий ; под ред. А. В. Кревецкого ; М-во образования и науки Рос. Федерации, ФГБОУ ВПО "Поволж. гос. технол. ун-т". Йошкар-Ола : ПГТУ, 2015. 210 с.

- 2. Симонович С. В. Информатика. Базовый курс: Учебник для вузов. 3-е изд. Стандарт третьего поколения. СПб.: Питер, 2011. 640 с.