# Комбинационные логические схемы Интегральная микросхема (ИМС) дешифратора

#### Комбинационные логические схемы

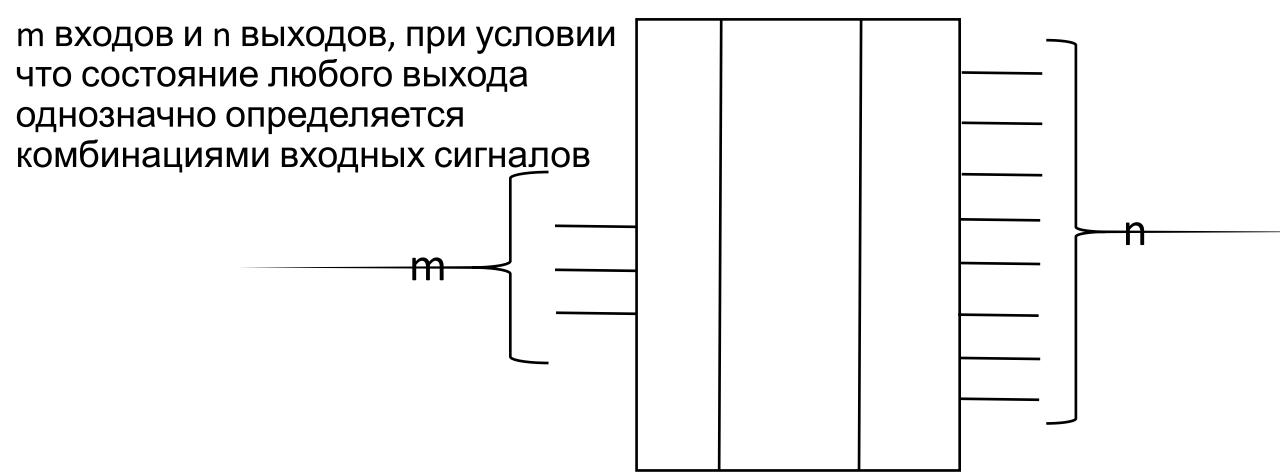

• Комбинационная логическая схема – это устройство состоящее из

# Дешифратор

Логическая комбинационная схема имеющая N входов и  $2^N$  выходов, работа обеспечивается следующим образом, если имеется определенная комбинация входных сигналов то на выходе получаем тот сигнал только на том контакте номер которого совпадает с заданным кодом

# Дешифратор

- Дешифратором (DC) называется комбинационная схема с несколькими водами и выходами, у которой, каждой комбинации входных сигналов соответствует активный сигнал только на одном выходе. Дешифратор преобразует десятичный или двоично-десятичный код в унитарный позиционный

- Унитарный код активный сигнал, присутствует только в одном разряде этого кода

- Позиционный код позиция активного сигнала определяется набором входных сигналов.

- Дешифратор, который имеет n входов и 2<sup>n</sup> выходов называется полным

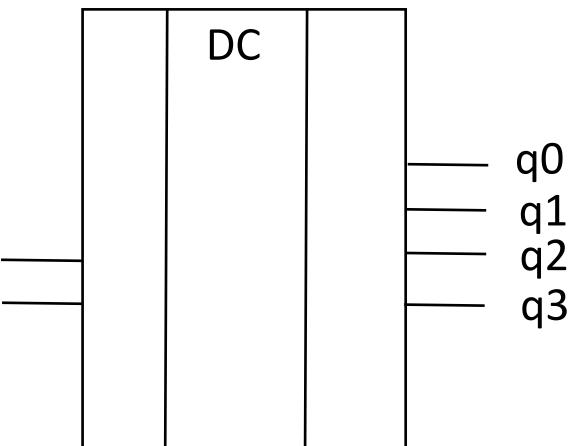

# Принцип работы

• Логическое выражение записывается в таблице истинности

d2

|   | D2 | D1 | Q0 | Q1 | Q2 | Q3 |

|---|----|----|----|----|----|----|

| 0 | 0  | 0  | 1  | 0  | 0  | 0  |

| 1 | 0  | 1  | 0  | 1  | 0  | 0  |

| 2 | 1  | 0  | 0  | 0  | 1  | 0  |

| 3 | 1  | 1  | 0  | 0  | 0  | 1  |

# Минтермы

|   | D2 | D1 | Минтерм |

|---|----|----|---------|

| 0 | 0  | 0  |         |

| 1 | 0  | 1  |         |

| 2 | 1  | 0  |         |

| 3 | 1  | 1  |         |

#### **©**ДНФ ФУНКЦИЙ

• Q0 -

$$\overline{D2}$$

$^{\wedge}\overline{D1}$

• Q1 -

$$\overline{D2}$$

^ D1

• Q2 - **D2**^

$$\overline{D1}$$

• Q3 - **D2**^**D1**

|   | D2 | D1 | Q0 | Q1 | Q2 | Q3 |

|---|----|----|----|----|----|----|

| 0 | 0  | 0  | 1  | 0  | 0  | 0  |

| 1 | 0  | 1  | 0  | 1  | 0  | 0  |

| 2 | 1  | 0  | 0  | 0  | 1  | 0  |

| 3 | 1  | 1  | 0  | 0  | 0  | 1  |

# Дешифраторы

КР1533ИД4

КР1533ИД7

**КР**1533ИД3

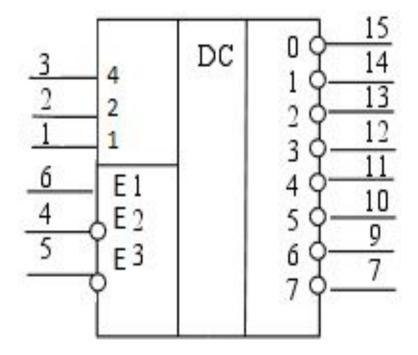

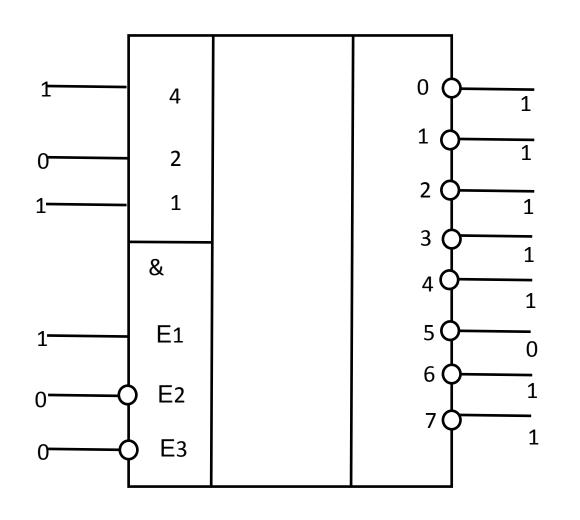

### КР1533ИД7

- Дешифратор 3на8:

- 4,2,1 информационные входы DC

- 0#-7# выходы, активный уровень сигнала логический 0

- E1, E2, E3 входы разрешения работы, E2, E3 активный уровень сигнала логический 0

- Работать дешифратору разрешено если E1=1,E2=0, E3=0, при любой другой кодовой комбинации на входе E, работать дешифратору запрещено дешифратор реагирует на информационный входы 4, 2, 1,на всех входах 7-0, присутствует активный уровень сигнала 1

- Номера входов указаны в 10й- СС, для того что бы определить какой выход DC, реагирует на двоичный код, поступающий на информационные входы 4,2,1.

- Так же следует сложить весовые коэффициенты тех разрядов на который поступил активный уровень сигналов.

В итоге видим что активный сигнал присутствует на позиции **5** и получаем код **11111011**

|   | <b>E1</b> | E2# | E3# | 4 | 2 | 1 | 0# | 1# | 2# | 3# | 4# | 5# | 6# | 7# |

|---|-----------|-----|-----|---|---|---|----|----|----|----|----|----|----|----|

|   | 0         | 1   | 1   | X | X | X |    |    |    |    |    |    |    |    |

| 0 | 1         | 0   | 0   | 0 | 0 | 0 |    |    |    |    |    |    |    |    |

| 1 | 1         | 0   | 0   | 0 | 0 | 1 |    |    |    |    |    |    |    |    |

| 2 | 1         | 0   | 0   | 0 | 1 | 0 |    |    |    |    |    |    |    |    |

| 3 | 1         | 0   | 0   | 0 | 1 | 1 |    |    |    |    |    |    |    |    |

| 4 | 1         | 0   | 0   | 1 | 0 | 0 |    |    |    |    |    |    |    |    |

| 5 | 1         | 0   | 0   | 1 | 0 | 1 |    |    |    |    |    |    |    |    |

| 6 | 1         | 0   | 0   | 1 | 1 | 0 |    |    |    |    |    |    |    |    |

| 7 | 1         | 0   | 0   | 1 | 1 | 1 |    |    |    |    |    |    |    |    |

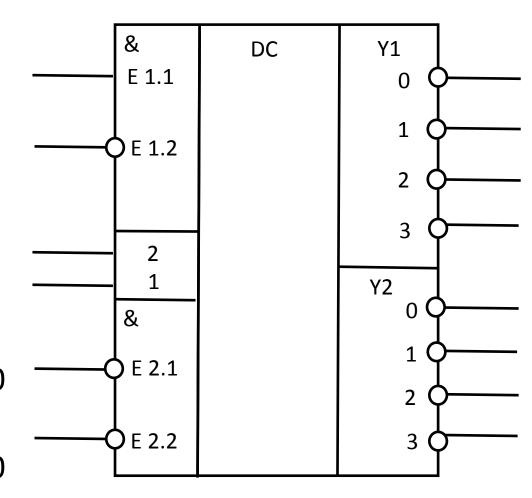

• ИМС содержит два DC

2 на 4 с общими информационными входами 2,1

- Y1.3 Y1.0 выходы первого DC, активный уровень «0»

- Y2.3 Y2.0 выходы второго DC, активный уровень «0»

- E1.1-E1.2 входы разрешения работы 1-го DC, если E1.1 = 0, E2.2 = 0

- E2.1-E2.2 входы разрешения работы 2-го DC, если E2.1 = 0, E2.2 = 0

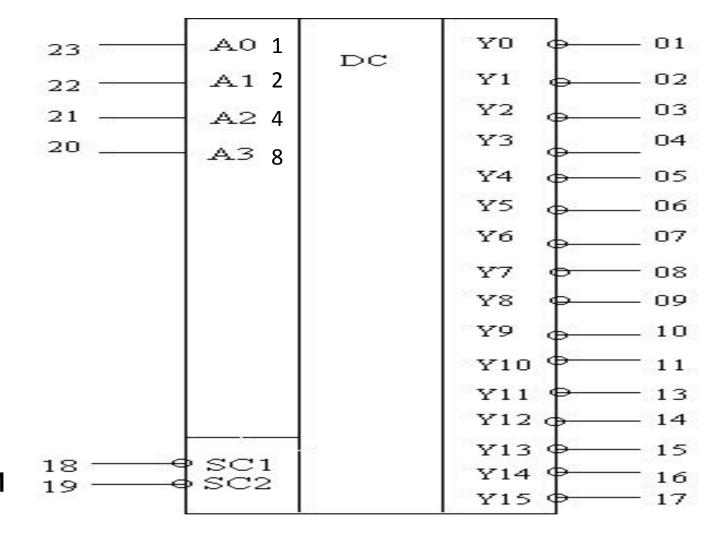

## КР 1533ИД3

- А0-А3 информационные входы

- SC1-SC2 вход разрешения работы. Активный уровень сигнала логический 0

- Y0-Y15 Выходы

- Разрешено работать, если SC1=0 и SC2=0, при другой комбинации работать дешифратор не будет. Все входы в неактивном состоянии