# КМОП технология вблизи физических пределов масштабирования

В.П. Попов

### Прогнозируемые и достигнутые параметры логических элементов

| Device                    |               |         |                                                                                            |                                                                  |                                                          |                                                   |                                 |                                                    |

|---------------------------|---------------|---------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------|---------------------------------|----------------------------------------------------|

|                           |               | ,       | FET Extension                                                                              |                                                                  |                                                          | ·                                                 |                                 | !                                                  |

|                           |               | FET [A] | 1D structures                                                                              | Channel replacement                                              | SET                                                      | Molecular                                         | Ferromagnetic<br>logic          | Spin transistor                                    |

| Typical example devices   |               | Si CMOS | CNT FET NW FET NW heterostructures Nanoribbon transistors with                             | III-V compound<br>semiconductor and<br>Ge channel<br>replacement | SET                                                      | Crossbar latch Molecular transistor Molecular QCA | Moving domain<br>wall<br>M: QCA | Spin Gain<br>transistor<br>Spin FET<br>Spin Torque |

| ı <b></b>                 |               |         | graphene                                                                                   |                                                                  |                                                          |                                                   |                                 | Transistor                                         |

| Cell Size                 | Projected     | 100 nm  | 100 nm [D]                                                                                 | 300 nm [I]                                                       | 40 nm [O]                                                | 10 nm [U]                                         | 140 nm [Y]                      | 100 nm [C]                                         |

| (spatial<br>pitch) [B]    | Demonstrated  | 590 nm  | ~1.5 μm [E]                                                                                | 1700 nm [J]                                                      | ~200 nm [K, L]                                           | ~2 µm [V]                                         | 250 nm [Z, AA]                  | 100 μm [AB]                                        |

| Density                   | Projected     | 1E10    | 4.5E9                                                                                      | 6.1E9                                                            | 6E10                                                     | 1E12                                              | 5E9                             | 4.5E9                                              |

| (device/cm <sup>2</sup> ) | Demonstrated  | 2.8E8   | 4E7                                                                                        | 3.5E7                                                            | ~2E9                                                     | 2E7                                               | 1.6E9                           | 1E4                                                |

| Switch Speed              | Projected     | 12 THz  | 6.3 THz [F]                                                                                | >1 THz                                                           | 10 THz [Q]                                               | 1 THz [W]                                         | 1 GHz [Y]                       | 40 GHz [AC]                                        |

| Switch Speed              | Demonstrated  | 1.5 THz | 200 MHz [G]                                                                                | >300 GHz                                                         | 2 THz [R]                                                | 100 Hz [V]                                        | 30 Hz [Z, AA]                   | Not known                                          |

| Circuit Speed             | Projected     | 61 GHz  | 61 GHz [C]                                                                                 | 61 GHz [C]                                                       | 1 GHz [O]                                                | 1 GHz [U]                                         | 10 MHz [Y]                      | Not known                                          |

| Circui speed              | Demonstrated  | 5.6 GHz | 220 Hz [H]                                                                                 | Data not available                                               | 1 MHz [P]                                                | 100 Hz [V]                                        | 30 Hz [Z]                       | Not known                                          |

| Switching                 | Projected     | 3E-18   | 3E-18                                                                                      | 3.00E-18                                                         | 1×10 <sup>-18</sup> [O]<br>[>1.5×10 <sup>-17</sup> ] [S] | 5E-17 [X]                                         | ~1E-17 [Z]                      | 3E-18                                              |

| Energy, J                 | Demonstrated  | 1E-16   | 1E-11 [H]                                                                                  | 1E-16 [J]                                                        | 8×10 <sup>-17</sup> [T]<br>[>1.3×10 <sup>-14</sup> ] [S] | 3E-7 [V]                                          | 6E-18 [AA]                      | Not known                                          |

| Binary<br>Throughput,     | Projected     | 238     | 238                                                                                        | 61                                                               | 10                                                       | 1000                                              | 5E-2                            | Not known                                          |

| GBit/ns/cm <sup>2</sup>   | Demonstrated  | 1.6     | 1E-8                                                                                       | Data not available                                               | 2E-4                                                     | 2E-9                                              | 5E-8                            | Not known                                          |

| 2000 00 0                 | l Temperature | RT      | RT                                                                                         | RT                                                               | RT [M, N]                                                | RT                                                | RT                              | RT                                                 |

| Materials System          |               | Si      | CNT,<br>Si, Ge, III-V,<br>In <sub>2</sub> O <sub>3</sub> , ZnO, TiO <sub>2</sub> ,<br>SiC, | InGaAs, InAs,<br>InSb                                            | III-V, Si, Ge,                                           | Organic<br>molecules                              | Ferromagnetic<br>alloys         | Si, III-V,<br>complex metals<br>oxides             |

| Research Activity [AD]    |               |         | 379                                                                                        | 62                                                               | 91                                                       | 244                                               | 32                              | 122                                                |

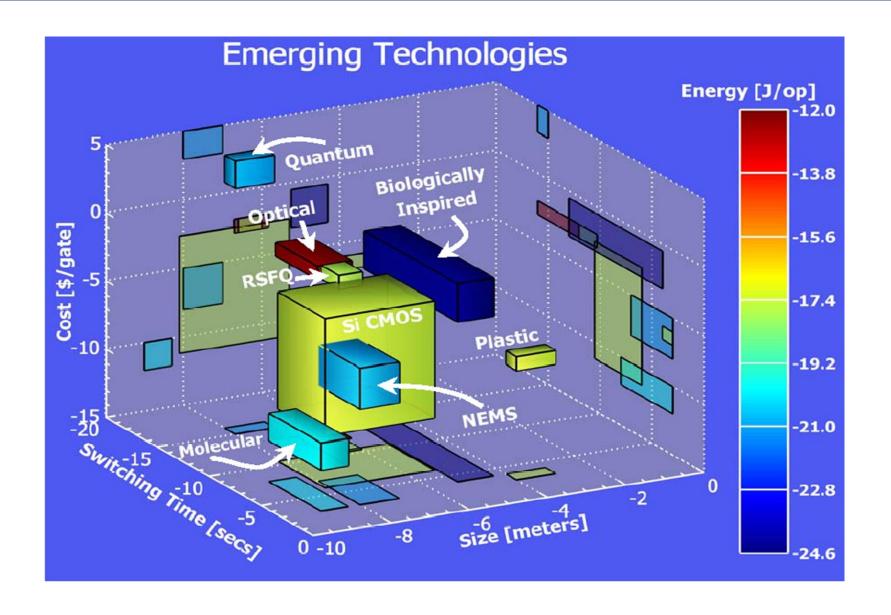

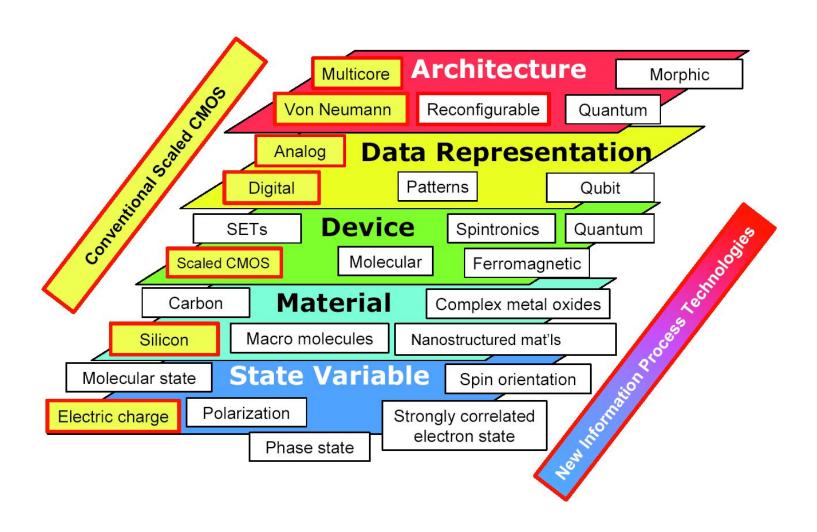

### Технико-экономические параметры элементных базисов

### Развивающиеся и поисковые информационные технологии

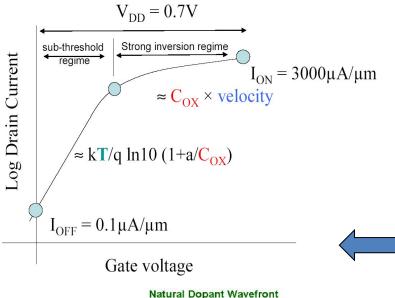

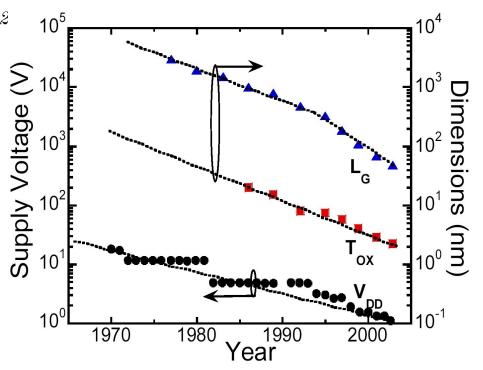

### Принцип электростатического подобия и закон Мура

$$P_{dyn} = n \cdot I_{on} \cdot V_{DD} \rightarrow k^{-2} \cdot k \cdot k = const$$

$k \sim 0.7$

$$F_{dvn} = I_{on} / (C_{ox} \cdot W \cdot L \cdot V_{DD}) \rightarrow k / (k^{-1} \cdot k \cdot k \cdot k) = k^{-1}$$

Текущее масштабирование по мощности и частоте для схем на классических КМОП транзисторах

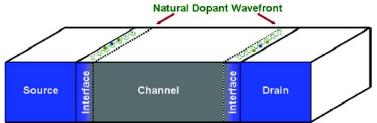

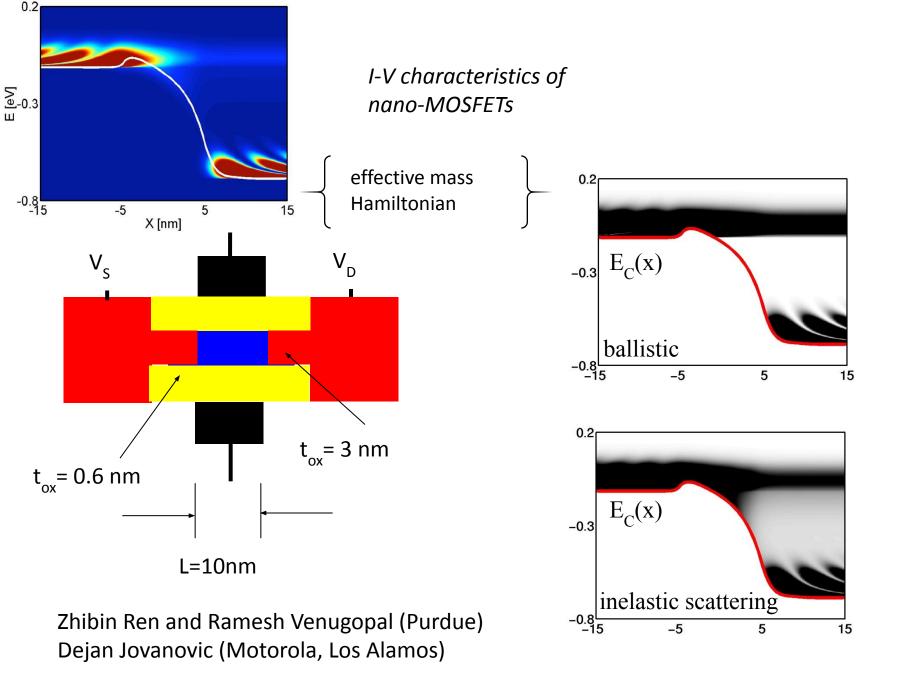

$* L_g = 5 nm n-MOSFET$ Lch =  $6 \pm 3 nm$ из-за флуктуаций  $n_{SD}^+$

#### Ограничения нанотранзисторов:

Предел масштабирования по туннельному току затвора  $I_G$  достигнут при 90 нм норме  $GOT = 1.5 \ nm$

Для 45 nm – high-k диэлектрики GOT = 1.0 nm Для 14 nm – GOT = 0.5 nm (SiO<sub>2</sub>)

При 14 нм проектной норме (2015 г.)\* – баллистический режим (L<  $\lambda$ ) , но туннелирование S-D

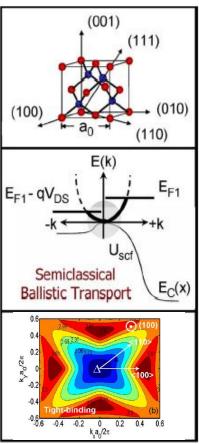

При L=3 нм (10 нм норма 2020 г.) - изменения зонной структуры (скорости, ёмкости)

- Снижение температуры

- Уменьшение ёмкости оксида

- Увеличение скорости

### INSTITUTE OF SEMICONDUCTOR PHYSICS

RUSSIAN ACADEMY OF SCIENCES, SIBERIAN BRANCH

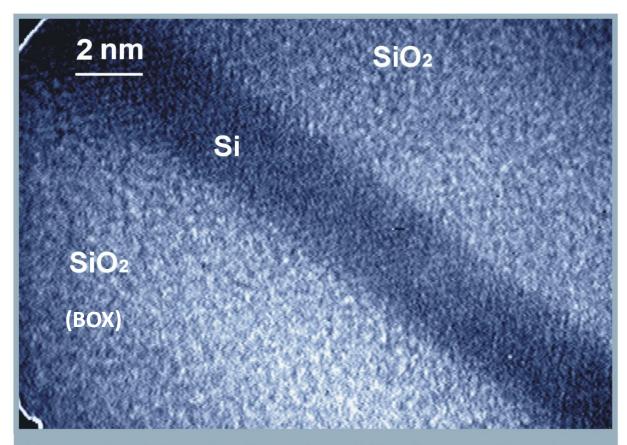

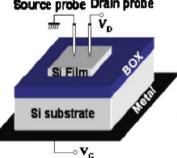

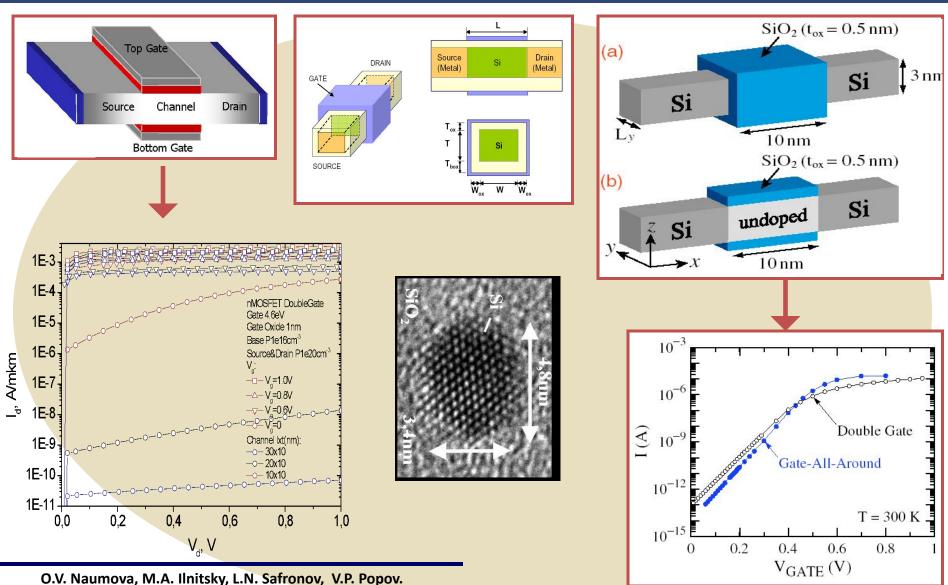

### Silicon-on-Isolator (SOI) ultra-thin structure

Electron microphotography with atomic resolution of cross-section of monocrystalline ultra-thin cut-off 3 nm silicon layer between upper oxide and buried dielectric of SOI-structure

### World record presented in 1999 at E-MRS Meeting

V.P. Popov, I.V. Antonova, V.F. Stas et al., J. Mater. Sci. Eng. B, 73, 82 (2000)

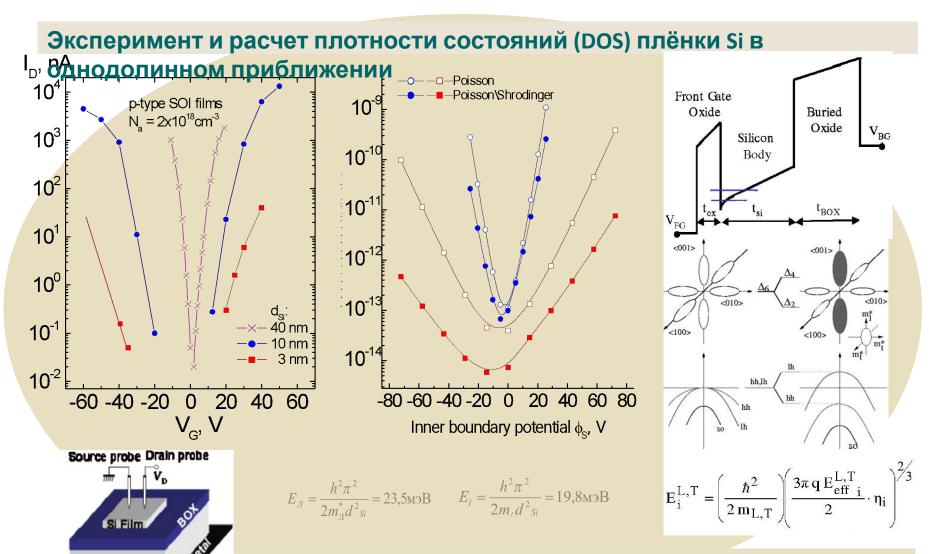

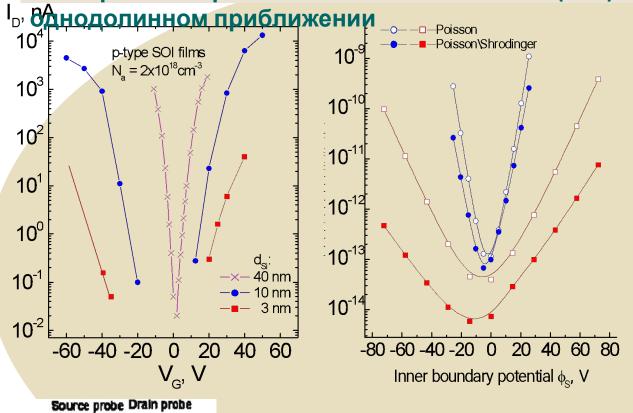

### Проводимость 3 нм пленок Si в КНИ: измерения ВАХ точечноконтактного псевдо МОП-транзистора и расчет DOS в ОДП

Квантовые поправки в проводимость 3 нм канала − 1-2 порядка

Si substrate

$\neg \mathbf{V_c}$

### Проводимость 3 нм пленок Si в КНИ: измерения ВАХ точечноконтактного псевдо МОП-транзистора и расчет DOS в ОДП

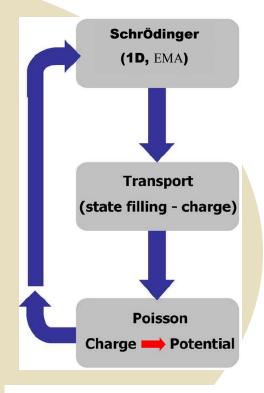

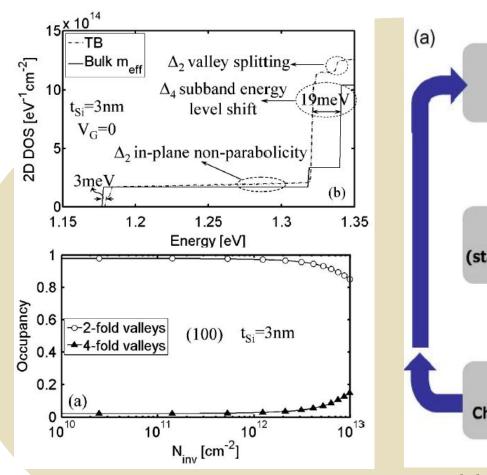

### Эксперимент и расчет плотности состояний (DOS) плёнки Si в

$$E_{II} = \frac{h^2 \pi^2}{2m_{_{II}}^* d_{_{Si}}^2} = 23,5$$

M9B  $E_{I} = \frac{h^2 \pi^2}{2m_{_{I}} d_{_{Si}}^2} = 19,8$ M9B

$$E_{II} = \frac{h^2 \pi^2}{2m_{II}^* d^2_{Si}} = 23,5 \text{M3B} \qquad E_{I} = \frac{h^2 \pi^2}{2m_{I} d^2_{Si}} = 19,8 \text{M3B} \qquad \qquad E_{I}^{L,T} = \left(\frac{\hbar^2}{2 m_{L,T}}\right) \left(\frac{3\pi \, \mathbf{q} \, \mathbf{E}_{\text{eff} \, i}^{L,T}}{2} \cdot \eta_{i}\right)^{2/3}$$

Квантовые поправки в проводимость 3 нм канала - 1-2 порядка

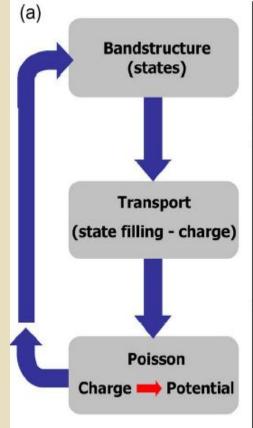

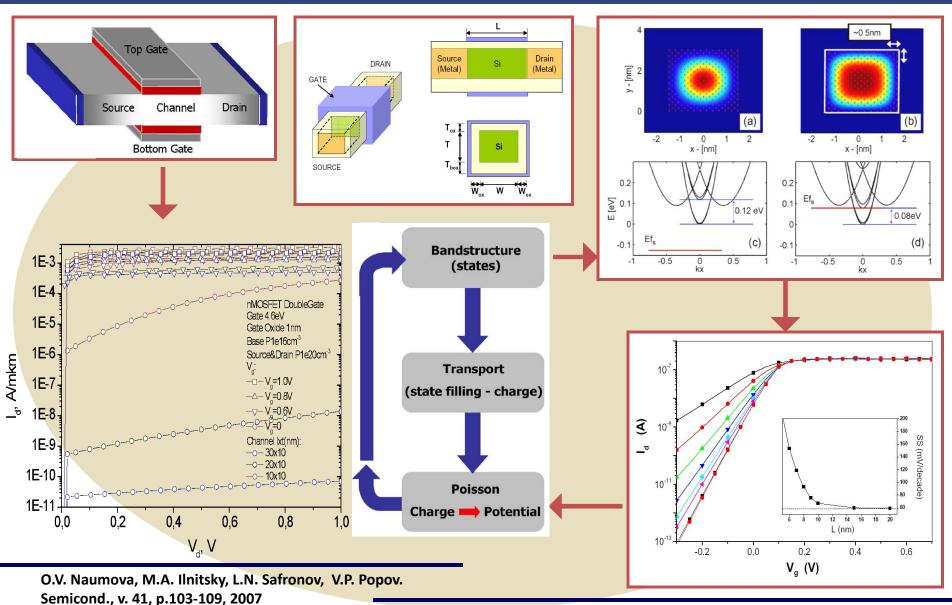

### Проводимость 3 нм пленок Si в КНИ: расчет DOS в EMA и ТВ

$$E_{II} = \frac{h^2 \pi^2}{2m_{II}^* d^2_{Si}} = 23,5 \text{M} \Rightarrow \text{B}$$

$$E_{II} = \frac{h^2 \pi^2}{2m_{II}^* d^2 s_i} = 23,5 \text{M} \Rightarrow B$$

$E_I = \frac{h^2 \pi^2}{2m_I d^2 s_i} = 19,8 \text{M} \Rightarrow B$

<u>www.nanohu</u>

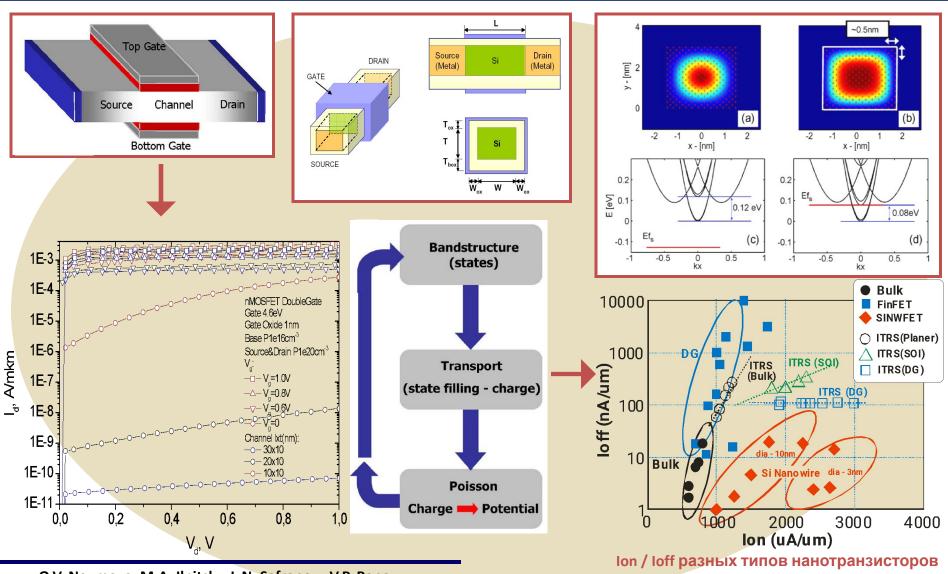

b.org Квантовые поправки определяются зонной структурой и зарядом

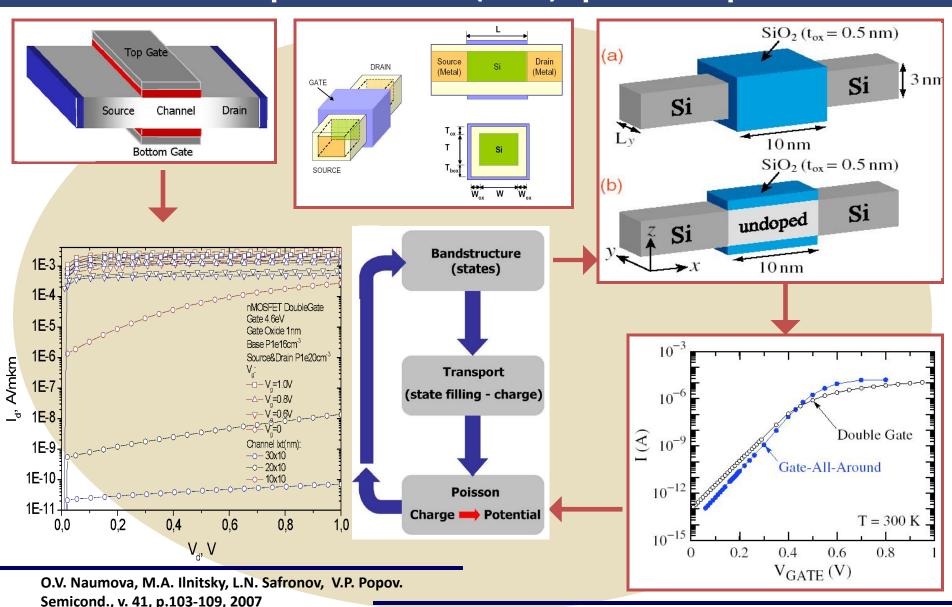

Semicond., v. 41, p.103-109, 2007

O.V. Naumova, M.A. Ilnitsky, L.N. Safronov, V.P. Popov. Semicond., v. 41, p.103-109, 2007

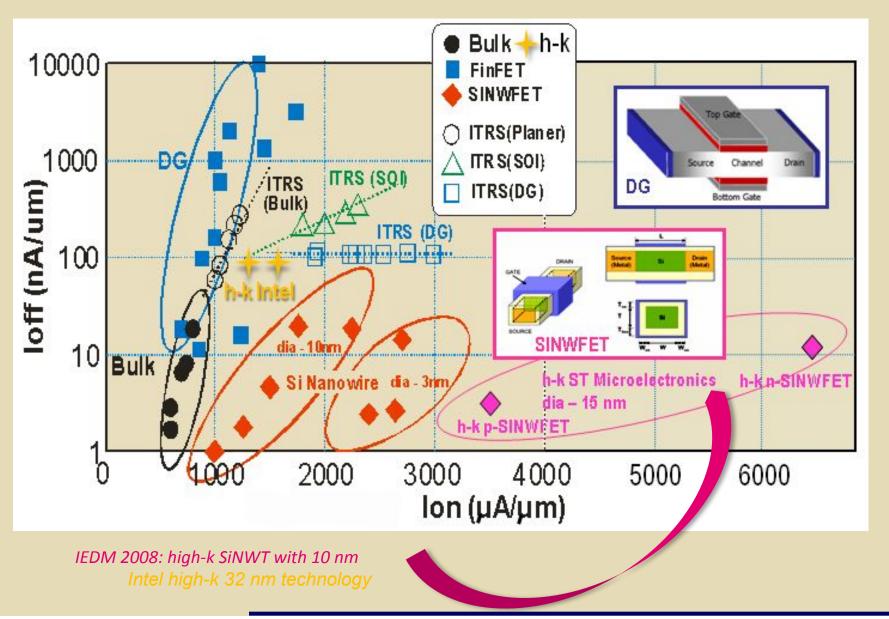

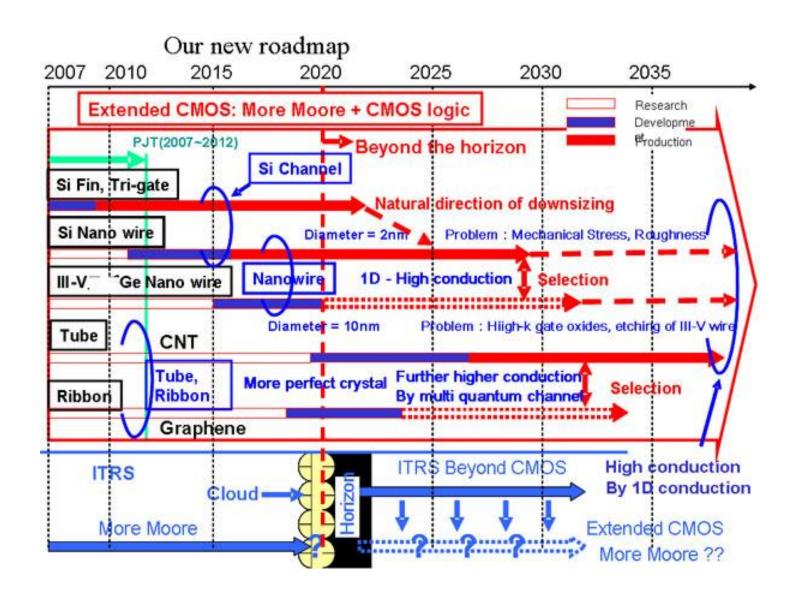

### Двухзатворные (DG) и нанопроволочые (SINW) транзисторы для СБИС

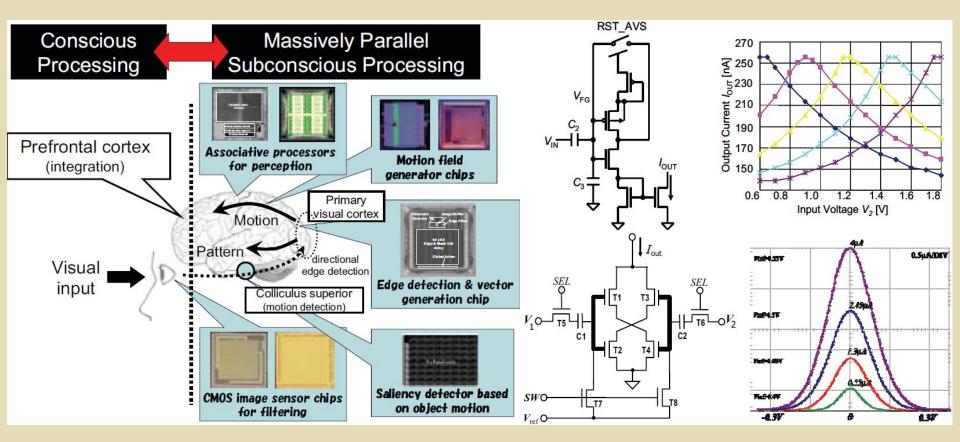

### КМОП СБИС чип эмуляции процессов опознавания, обучения и принятия решений

Архитектура кремниевого чипа с ~10 млрд. КМОП транзисторов, эмулирующих мозг (Тадаши Шибата)

Резонансные характеристики логики для ассоциативных «голосующих» процессоров на КМОП и NMOП нанотранзисторах

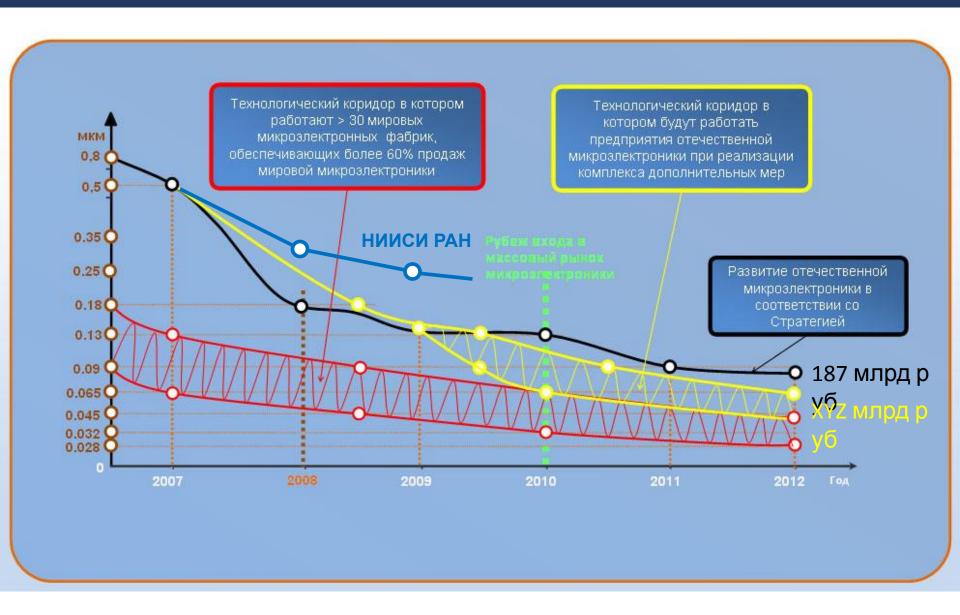

### Техпроцессы системообразующей ЭКБ микроэлектроники

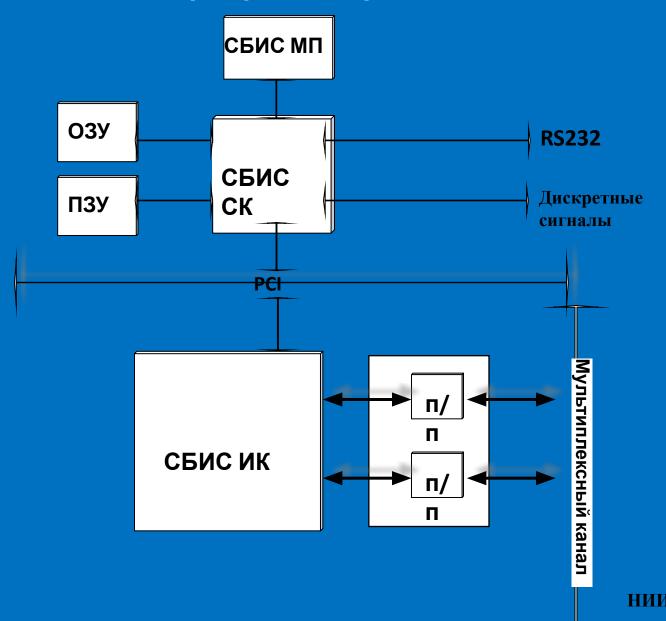

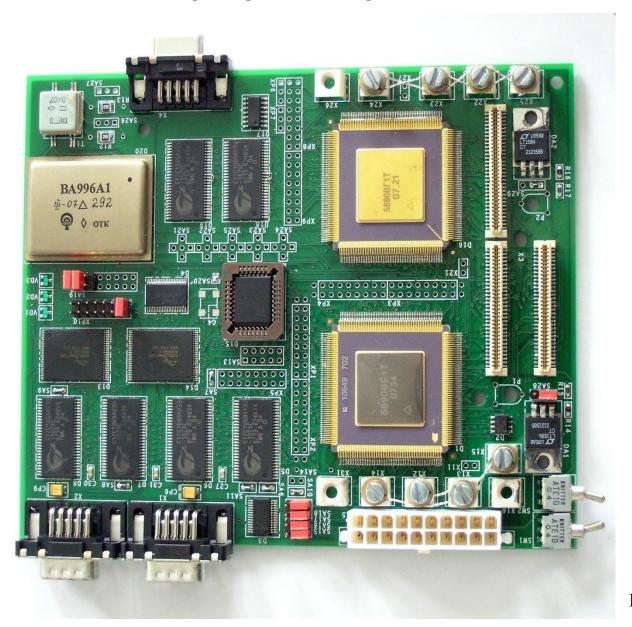

# Структура управляющей ЭВМ с 32-разрядным RISC микропроцессором КОМДИВ32-С

## Плата управляющей ЭВМ с 32-разрядным RISC микропроцессором КОМДИВ32-С

### 0.18 мкм технология ST Microelectronics 2007г.

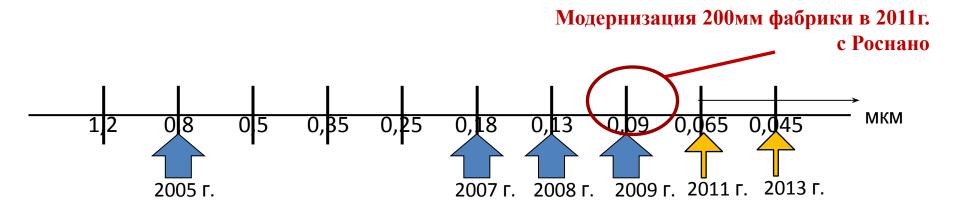

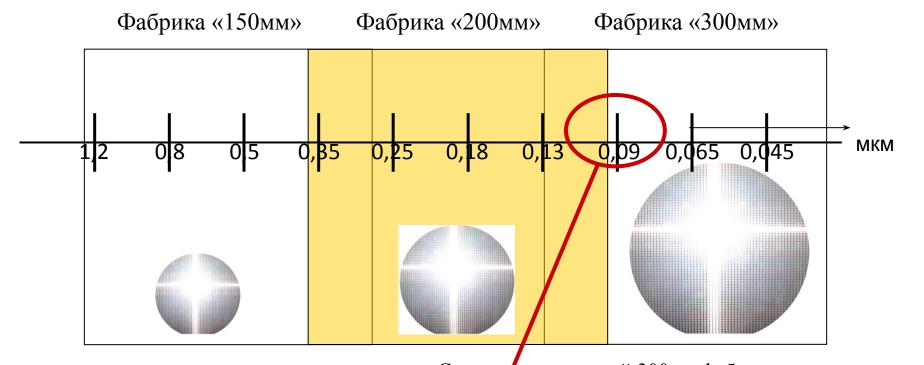

### Планы технологического развития «НИИМЭ и Микрон»

Строительство новой 300мм фабрики для уже существующей на 200мм технологии

### Результаты и перспективы развития КМОП технологии

- Имеющийся научно-технический задел по кремниевой КМОП технологии позволяет прогнозировать масштабированное уменьшение размеров от 45 нм до 4-5 нм в течение ближайших 20-25 лет. Дальнейший прогресс бинарной (цифровой) логики будет основан не на принципах переноса заряда или спина.

- Существующий сегодня уровень интеграции в КМОП СБИС достаточен для формирования многопроцессорных параллельных систем, в том числе систем ассоциативной логики.

- Одновременная разработка новых материалов (графена, п/п наноструктур, квантовых точек) и новой архитектуры микропроцессоров являются необходимым условием создания искусственного интеллекта, не уступающего по уровню человеку.

- - Отставание России от мировых лидеров в развитии подобных систем

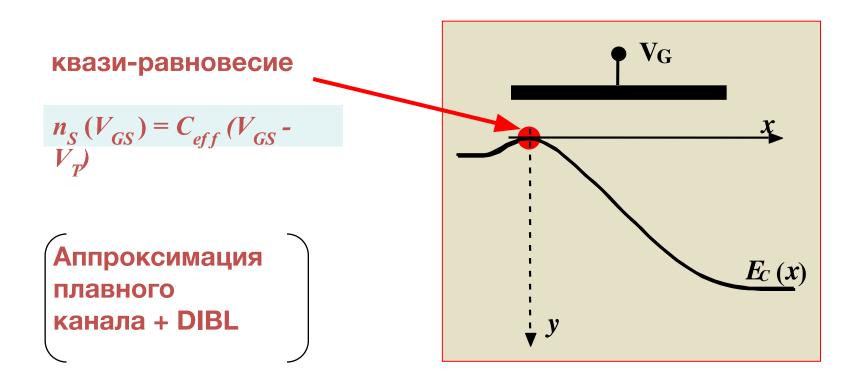

### Проблема плотности тока при размерном квантовании

### ток, зависящий от пропускания.....

$$I_{DS} = W C_{ox} \upsilon_{T} (V_{GS} - V_{T}) \left[ \frac{1 - e^{-qV_{DS}/k_{B}T_{L}}}{1 + e^{-qV_{DS}/k_{B}T_{L}}} \right] \upsilon_{T} = \sqrt{\frac{2k_{B}T_{L}}{\pi m^{*}}}$$

(Статистика Больцмана и одна подзона)

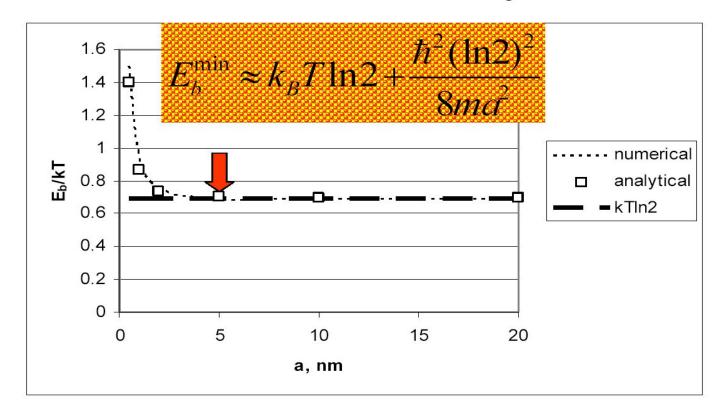

### 5 nm MOS is Theoretically Feasible

Minimum energy per switch operation as a function of minimum switch size

### Более реалистические оценки мощности

#### Сверху:

$$P=P_{

m stat}+P_{

m dyn}pprox~100~Bm\cdot cm^{-2}$$

где

$$P_{

m stat}=V_{

m DD}\cdot I_{

m off}$$

$$P_{

m dyn}=C\cdot V_{

m DD}^{-2}\cdot f$$

#### Снизу:

$$kTLn\left(\frac{N\tau_{mbf}}{\tau}\right) = C_L \cdot V_{\min}^2$$

$$V_{min} = \left(\frac{kTLn\left(\frac{N\tau_{mbf}}{\approx 10}\right)}{C_L}\right)^{\frac{1}{2}} MB \quad T = 300 \text{ K, } C_L = 0.4 \text{ fF } (t_{ox} = 1 \text{ hm})$$

$$= 10^9, \tau = 10 \text{ ps, } \tau_{mbf} = 1000 \text{ h}$$

The International Technology Roadmap for Semiconductors, edn. 2005

Hiroshi Iwai "Gate Stack Technology for the Next 25 Years" 4th International Symposium on Advanced Gate Stack Technology 25-28 September 2007 Dallas, Texas

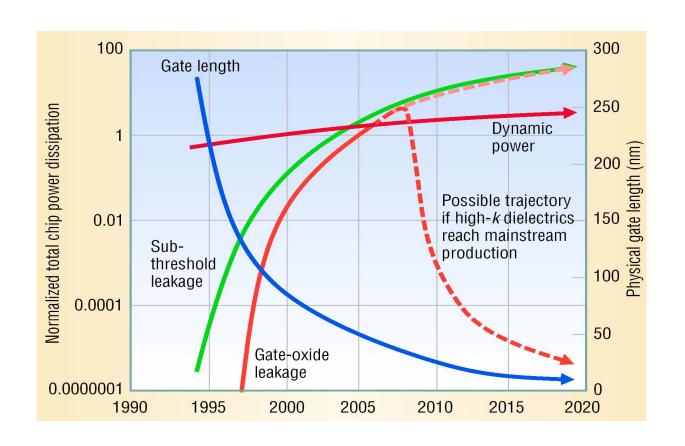

# Изменение потребляемой мощности СБИС при переходе к high-k диэлектрикам

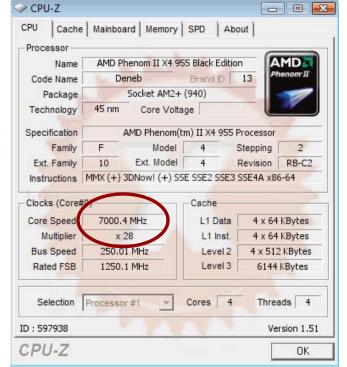

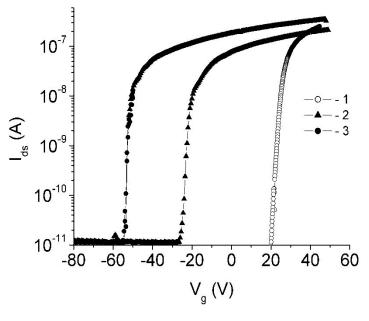

### Криогенная стабильность МП AMD Phenom II X4 и сдвиг сток-затворных характеристик КНИ нанопроволочных транзисторов

$I_{\rm DS}$ - $V_{\rm DS}$  кривые КНПТ ( $V_{\rm ds}$ =0.15 V) измеренные при температуре :

1 – 300 K; 2 – 14 K; 3 – 7 3 K

Адсорбционный газоанализатор!