### Встроенные Системы

## Часть 7. Технология разработки и производства ИС

Кафедра Информатики, мат-мех СПбГУ

Copyright © 2004 Victor Vengerov vvv@oktetlabs.ru

http://www.oktetlabs.ru/~vvv/es-2004

# HDL – Hardware Description Language

- HDL используются для концептуальной разработки цифровых интегральных схем.

- Наиболее распространенные HDL:

- Verilog

- VHDL

### Абстракция Дизайна

- HDL позволяют иерархически описать систему как совокупность блоков (черных ящиков), имеющих внешние интерфейсы.

- Блок может быть описан как состоящий из составных блоков.

- Абстрагирование позволяет скудному человеческому мозгу иметь дело с очень сложными системами.

### Абстракция Описания

- HDL позволяет описывать систему с различными уровнями детализации.

- Обычно разработка ведется сверху вниз, путем последовательного уточнения дизайна.

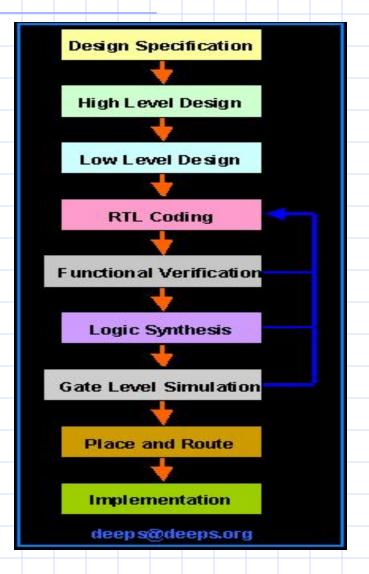

### **HDL Design Flow**

- Уровни абстракции Verilog:

- Behavioral система описывается как совокупность параллельных алгоритмов

- RTL (Register-Transfer Level)

система описывается в терминах регистров и пересылок данных.

- Gate Level система описана как сеть базовых логических примитивов. Заданы временные свойства элементов и связей. Gate Level обычно синтезируется из RTL.

### Simulation (Моделирование)

- Программа на Verilog может быть промоделирована.

- Обычно моделирование осуществляется в тестовом окружении (test bench).

- Используя встроенные функции, в процессе моделирования можно выполнять вывод данных на экран или собирать трассу интересующих сигналов.

## PLI – Programming Language Interface

- Описание Verilog и VHDL включает также С-интерфейс, позволяющий программному коду на языке С выполняться во время моделирования Verilog-программы.

- PLI позволяет получить полную информацию о структуре и состоянии системы.

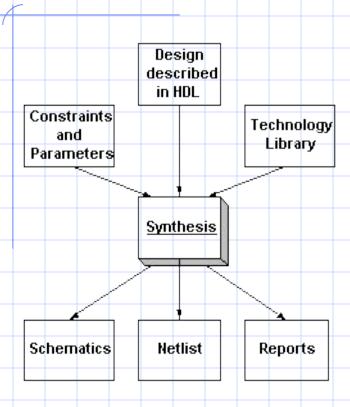

#### Синтез

- Не каждая конструкция Verilog может быть синтезирована.

- Technology library определяет особенности технологического процесса (набор базовых элементов)

- Constraints параметры, описывающие что мы ждем от результата синтеза (скорость, площадь, ...)

- Netlist код на Verilog или в другом виде, описывающий соединения базовых элементов.

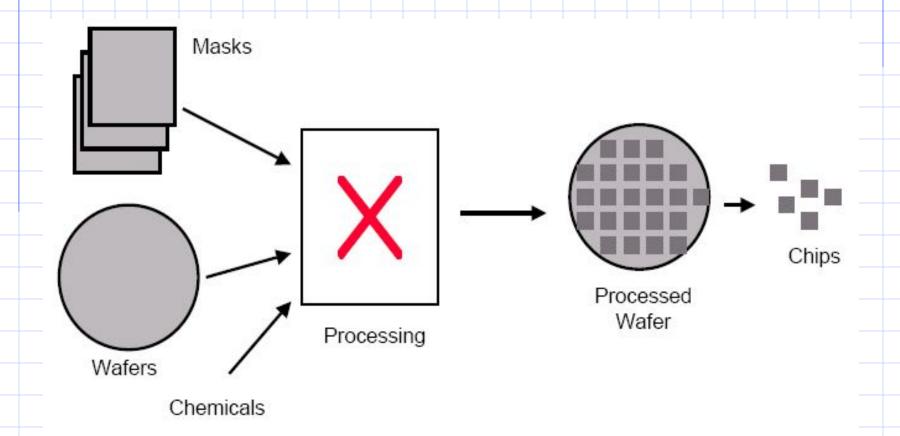

### Изготовление ИС

### Фотолитография

Start with wafer at current step

Spin on a photoresist

Pattern photoresist with mask

Step specific processing etch, implant, etc...

Wash off resist

#### Маска

- Маска стеклянная пластина, покрытая хромом, на которой вытравлен «рисунок» соответствующего слоя, в соответствии с библиотекой технологии и синтезированной сетью.

- Длина световой волны, используемой при проецировании на подложку (wafer вафля) важная характеристика технологического процесса.

### FPGA – Field Programmable Gate Array

- Устройство, позволяющее запрограммировать логику своей работы.

- Представляет из себя регулярную структуру из базовых логических блоков (CLB), блоков ввода/вывода, матрицы соединений.

- Дорого при массовом использовании, выгодно при мелкосерийном производстве и прототипировании.

### FPGA (продолжение)

• FPGA может быть интегрировано в одном устройстве с готовыми типовыми ядрами (CPU core, интерфейсы и т.д.)