# Лекция 1 на тему: «Основы микропроцессорной техники»

Леонов С.В., доцент ОАР, к.т.н.

## Математическая логика. Булева алгебра

2 ноября 1815 – 8 декабря 1864

- Английский математик и логик. Профессор математики Королевского колледжа Корка (ныне Университетский колледж Корк).

- Один из основателей математической логики.

- В честь него назван тип данных *Boolean* в программировании

# Простые логические элементы

| Название эле                    | мент | ra  | И           | или        | Исключающее<br>ИЛИ | И-НЕ  | или-не          |

|---------------------------------|------|-----|-------------|------------|--------------------|-------|-----------------|

| F                               |      |     | x · y       | x + y      | $x \oplus y$       | x y   | x y             |

|                                 |      |     | х & у       | x   y      | x ⊙ y              | 00000 | 47.500 A.W.     |

|                                 |      |     | x A y       | xVy        | 1000000            |       | - 11-352 rg- 12 |

| Графическое<br>обозначение<br>[ | гост | NSI | <b>8</b> -/ |            | =1                 |       |                 |

| Таблица                         | х    | V   | конъюнкция  | дизъюнкция | неравнозначность   | /     | /               |

| истинности                      | 0    | 0   | 0           | 0          | О                  | 1     | 1               |

| истинности                      |      | -   |             | 1          | 1                  | 1     | 1               |

|                                 | 0    | 1   | 0           | 1          | 1                  | 1     | 0               |

| 8                               | 1    | 0   | 0           | 1          | 1                  | 1     | 0               |

| ]                               | 1    | 1   | 1           | 1          | 0                  | 0     | 0               |

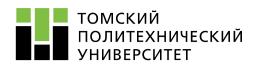

#### Сложные логические элементы

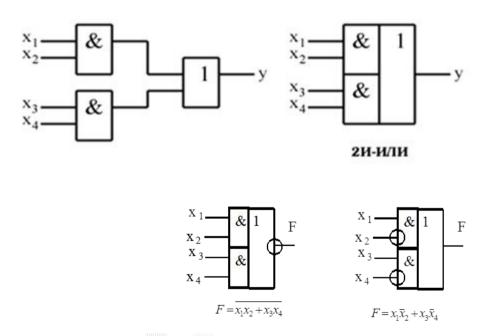

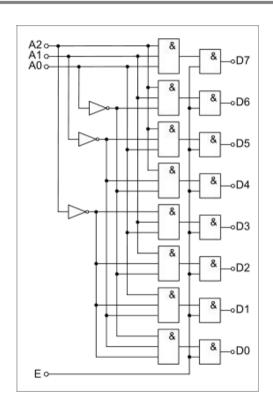

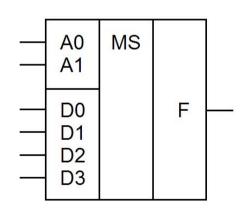

## Обозначение дешифратора

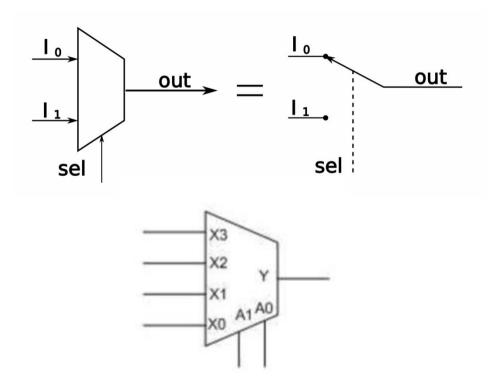

### Принцип действия мультиплексора

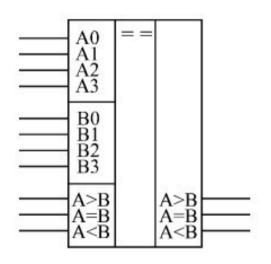

## Компаратор кода (цифровой компаратор)

| Вхс              | ды | Выходы |       |       |  |

|------------------|----|--------|-------|-------|--|

| $\boldsymbol{A}$ | B  | A < B  | A = B | A > B |  |

| 0                | 0  | 0      | 1     | 0     |  |

| 0                | 1  | 1      | 0     | 0     |  |

| 1                | 0  | 0      | 0     | 1     |  |

| 1                | 1  | 0      | 1     | 0     |  |

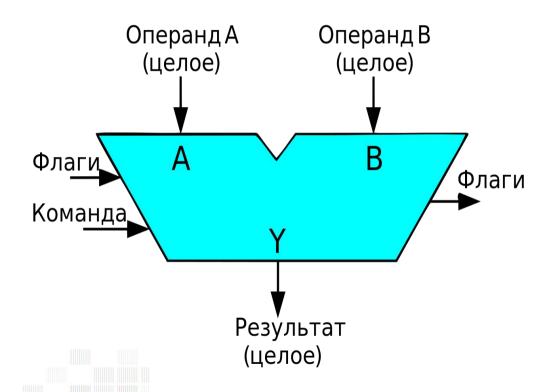

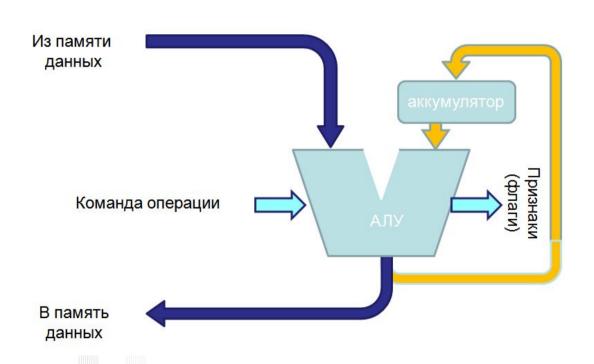

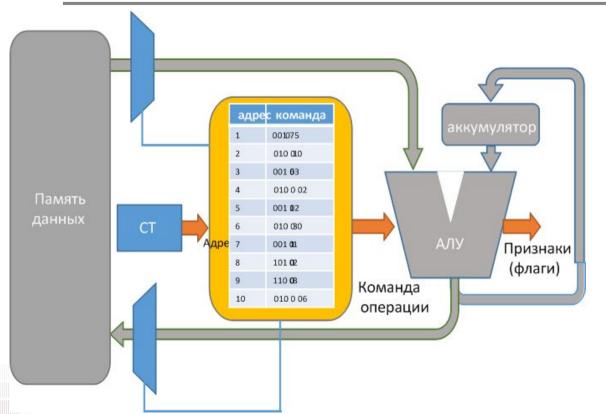

### Арифметико-логическое устройство

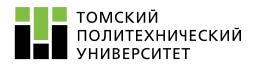

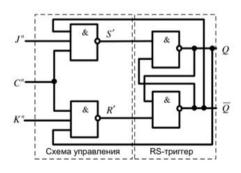

## RS mpurrep

| R <sub>i</sub> | Si | Q <sub>i-1</sub> | Q <sub>i</sub> |                          |

|----------------|----|------------------|----------------|--------------------------|

| 0              | 0  | 0                | 0              | Режим хранения           |

| 0              | 0  | 1                | 1              | Режим хранения           |

| 0              | 1  | 0                | 1              | Установка лог.1          |

| 0              | 1  | 1                | 1              | Установка лог.1          |

| 1              | 0  | 0                | 0              | Установка лог.0          |

| 1              | 0  | 1                | 0              | Установка лог.0          |

| 1              | 1  | X                | ?              | Запрещенное<br>состояние |

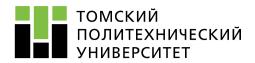

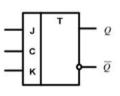

## ЈК триггер

J(Jump) – установка лог. 1

K(Kill) – установка лог. 0

C(Clock) – синхронный вход

| K <sub>i</sub> | J <sub>i</sub> | Q <sub>i</sub> | Q <sub>i+1</sub> |                 |

|----------------|----------------|----------------|------------------|-----------------|

| 0              | 0              | 0              | 0                | Режим хранения  |

| 0              | 0              | 1              | 1                | Режим хранения  |

| 0              | 1              | 0              | 1                | Установка лог.1 |

| 0              | 1              | 1              | 1                | Установка лог.1 |

| 1              | 0              | 0              | 0                | Установка лог.0 |

| 1              | 0              | 1              | 0                | Установка лог.0 |

| 1              | 1              | 0              | 1                | Счётный режим   |

| 1              | 1              | 1              | 0                | Счётный режим   |

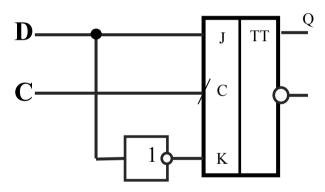

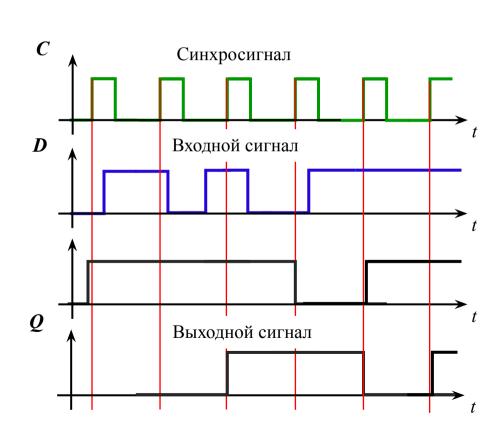

#### **D** триггер

D-триггер (Delay) – триггер задержки. На выходе триггера сигнал будет сохранятся до тех пор пока не поступит синхроимпульс.

Используется для фильтрации, нормализации, синхронизации и задержки цифрового сигнала

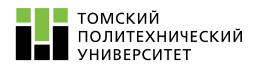

## Параллельный регистр

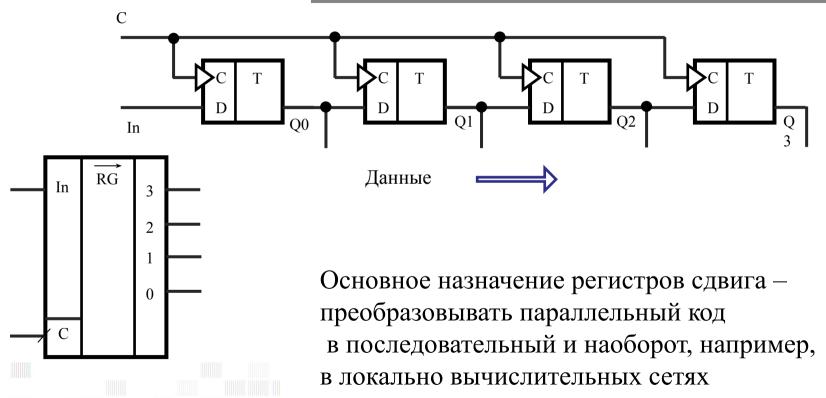

#### Сдвиговый регистр

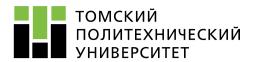

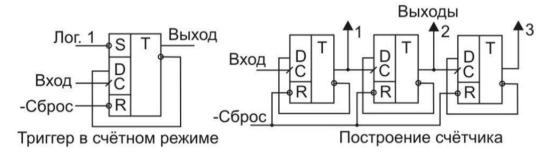

#### Счётчик прямой

#### Построение счётчика из триггеров

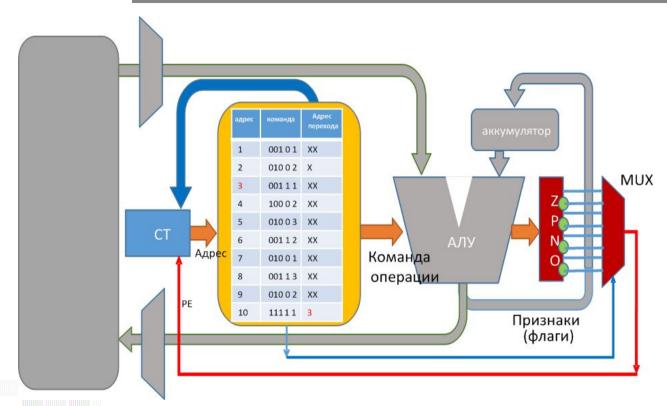

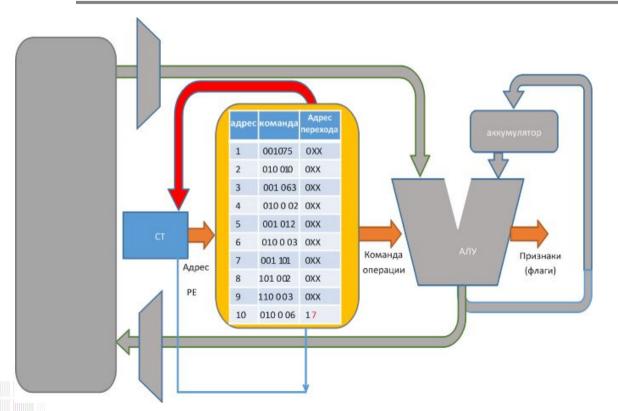

## Структура операционного блока

| Адрес<br>памяти | значение | Условное название                         | LD 75<br>SV #1  |

|-----------------|----------|-------------------------------------------|-----------------|

| #1              | 75       | Показания счётчика в текущем месяце (ct9) | LD 63           |

| #2              | 63       | Показания счётчика в прошлом месяце (ct8) | SV #2<br>LD 12  |

| #3              | 12       | Тариф (k)                                 | SV #3           |

| #4              |          | [количество] ← ct9 – ct8                  | 0,110           |

| #5              |          |                                           | LD #1           |

| #6              |          | [результат] <del>←</del> количество*k     | SUB #2<br>SV #4 |

| #7              |          |                                           | 1 17 43         |

|                 |          |                                           | LD #3<br>MUL #4 |

SV #6

ЛИНЕЙНАЯ ПРОГРАММА

#### Структура операционного блока

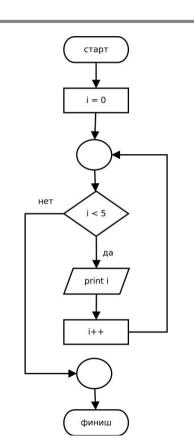

Условные переходы позволяют выполнить ветвление алгоритма в зависимости от результатов промежуточных расчётов.

Безусловные переходы позволяют организовывать циклы: многократное повторение выполнения одинаковых операций.

Циклы можно так же организовать с применением условных переходов.

| Мнемоника | код                          | Условное название                                        |

|-----------|------------------------------|----------------------------------------------------------|

| JMP       | 111 0 1 [адрес]              | Безусловный переход                                      |

| JZ        | 001 <mark>1</mark> 1 [адрес] | Условный переход по нулевому признаку результата         |

| JNZ       | 001 <mark>2</mark> 1 [адрес] | Условный переход по ненулевому признаку результата       |

| JP        | 001 <mark>3</mark> 1 [адрес] | Условный переход по положительному признаку результата   |

| JNP       | 001 <mark>4</mark> 1 [адрес] | Условный переход по неположительному признаку результата |

| JNN       | 001 <mark>5</mark> 1 [адрес] | Условный переход по отрицательному признаку результата   |

| JO        | 001 6 1 [адрес]              | Условный переход по нечётному признаку результата        |

| JNO       | 001 <mark>7</mark> 1 [адрес] | Условный переход по чётному признаку результата          |