Содержание

- 2. Содержание Основные понятия Полусумматор Сумматор Построение схемы последовательного сумматора Работа сумматора

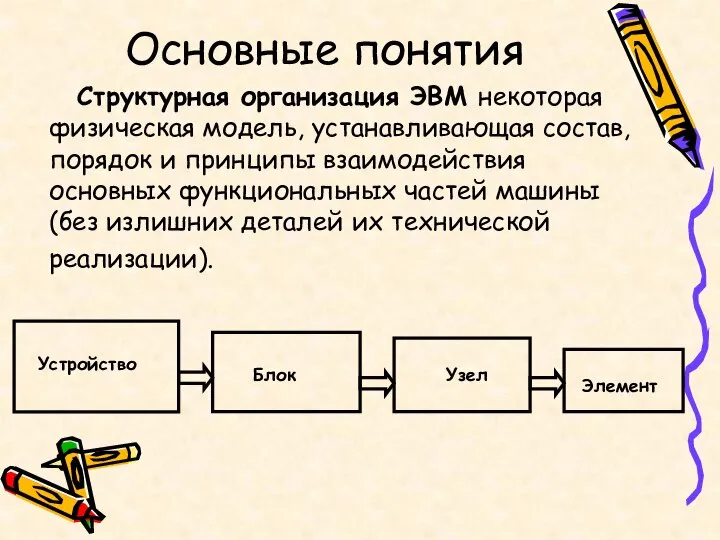

- 3. Основные понятия Структурная организация ЭВМ некоторая физическая модель, устанавливающая состав, порядок и принципы взаимодействия основных функциональных

- 4. Элемент, простейшее устройство ЭВМ, выполняющее одну операцию над входными сигналами (пример – логический элемент).

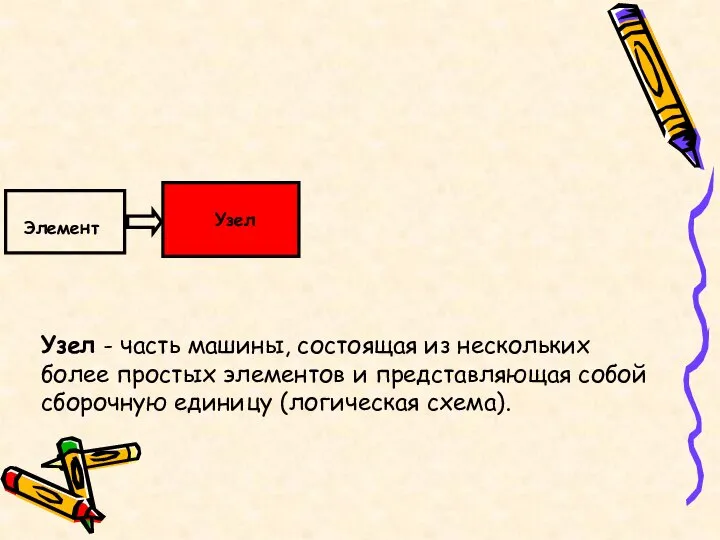

- 5. Узел - часть машины, состоящая из нескольких более простых элементов и представляющая собой сборочную единицу (логическая

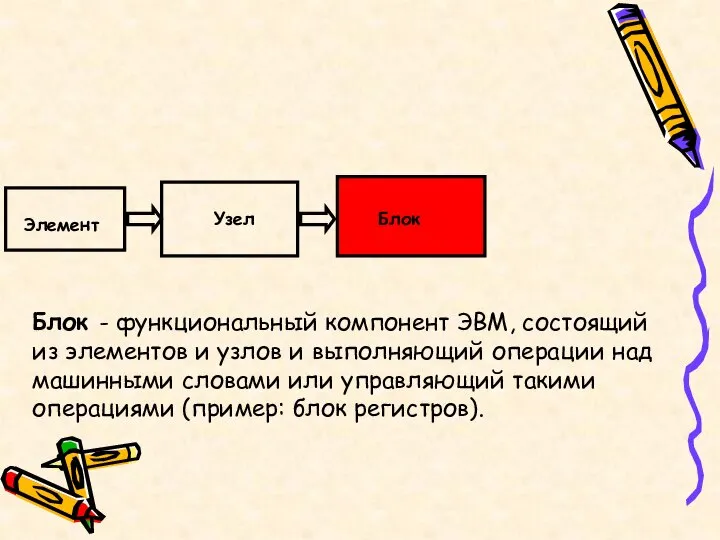

- 6. Блок - функциональный компонент ЭВМ, состоящий из элементов и узлов и выполняющий операции над машинными словами

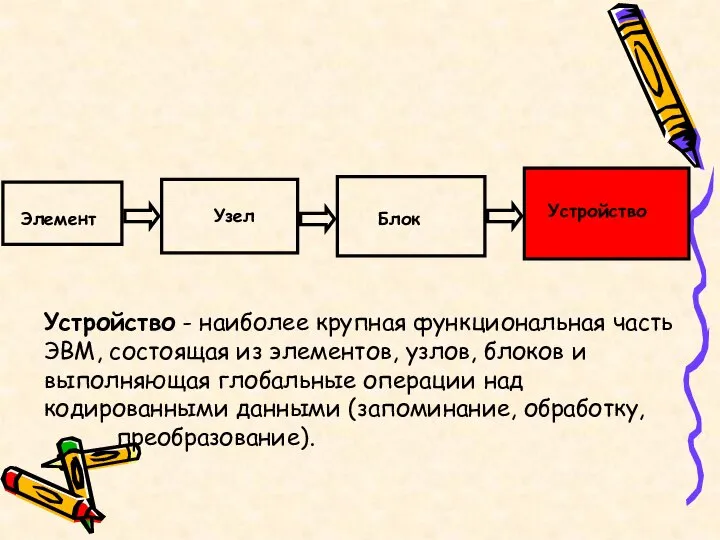

- 7. Устройство - наиболее крупная функциональная часть ЭВМ, состоящая из элементов, узлов, блоков и выполняющая глобальные операции

- 8. Узел ЭВМ выполняющий арифметическое суммирование кодов чисел, называется сумматором.

- 9. Операция суммирования осуществляется в сумматорах поразрядно с использованием одноразрядных суммирующих схем. При этом в каждом разряде

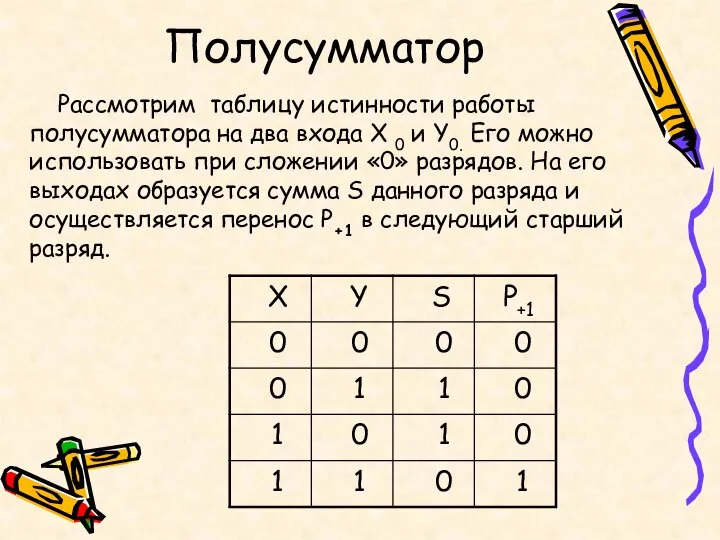

- 10. Полусумматор Рассмотрим таблицу истинности работы полусумматора на два входа X 0 и Y0. Его можно использовать

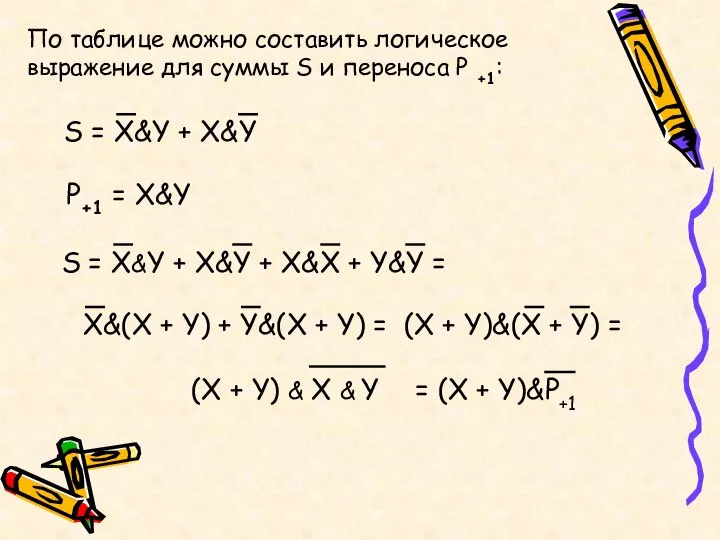

- 11. По таблице можно составить логическое выражение для суммы S и переноса Р +1: P+1 = X&Y

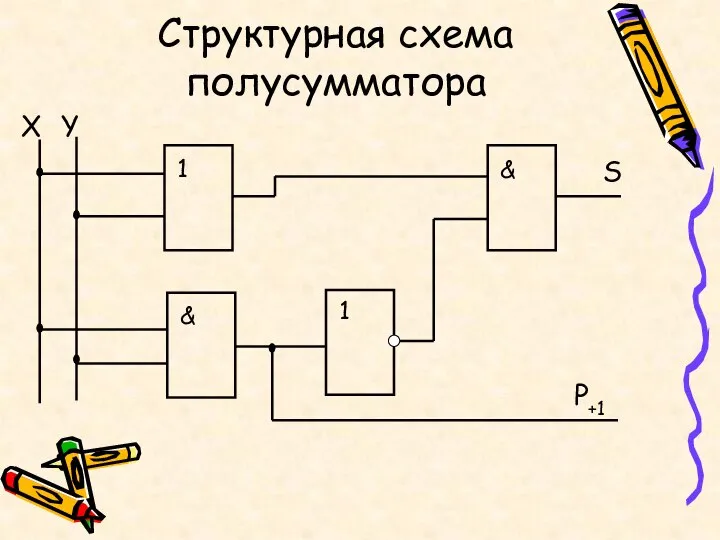

- 12. Структурная схема полусумматора

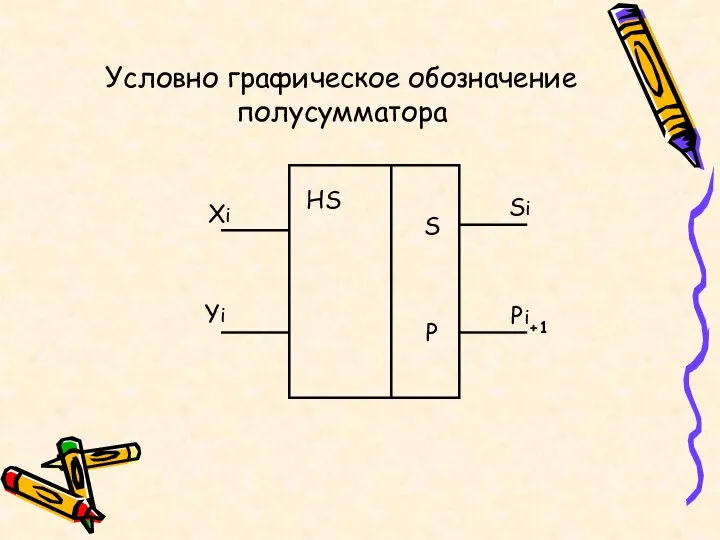

- 13. Условно графическое обозначение полусумматора HS S P Xi Yi Si Pi+1

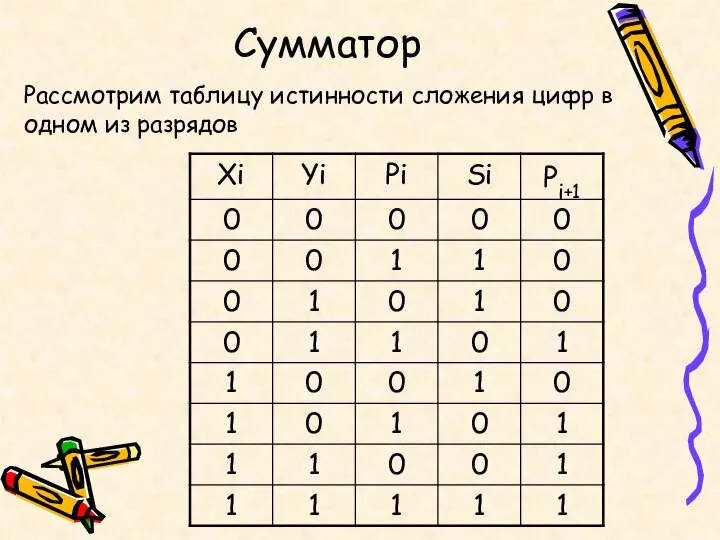

- 14. Сумматор Рассмотрим таблицу истинности сложения цифр в одном из разрядов

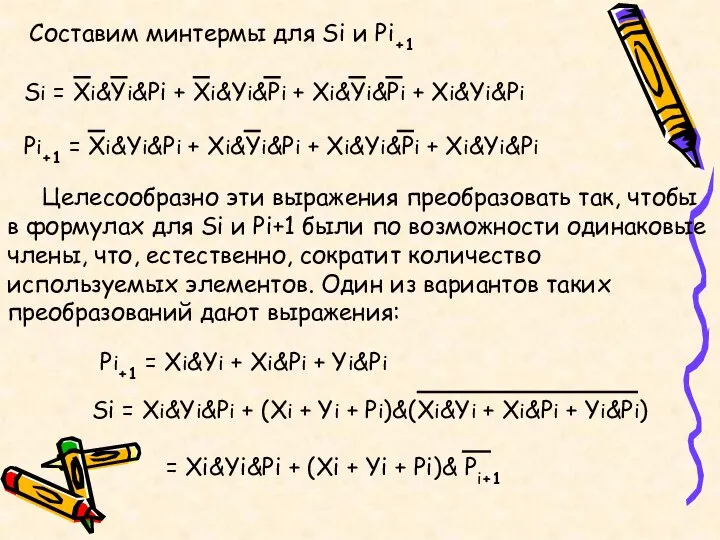

- 15. Составим минтермы для Si и Pi+1 Целесообразно эти выражения преобразовать так, чтобы в формулах для Si

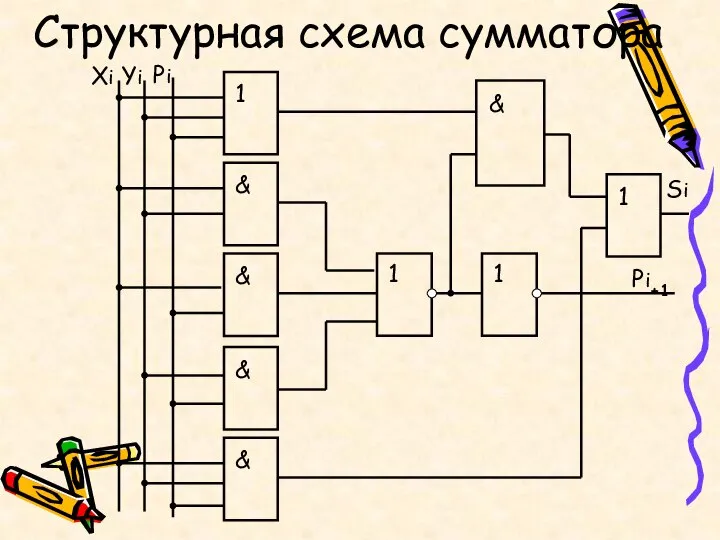

- 16. Структурная схема сумматора

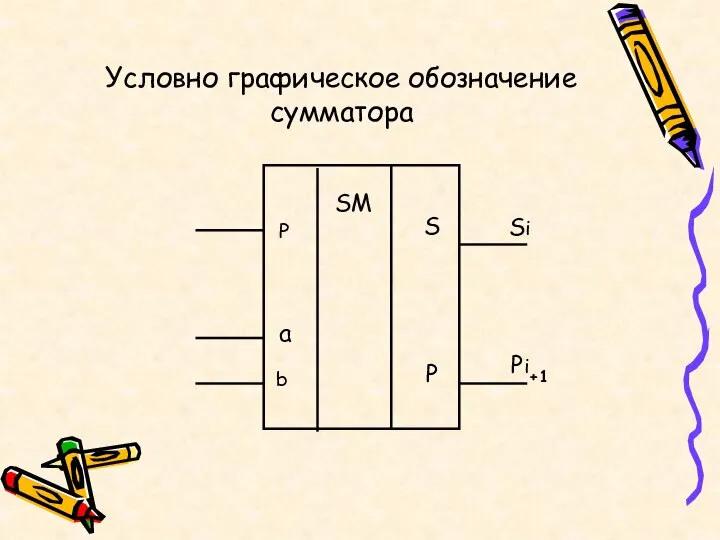

- 17. SM S P Si Pi+1 a b P Условно графическое обозначение сумматора

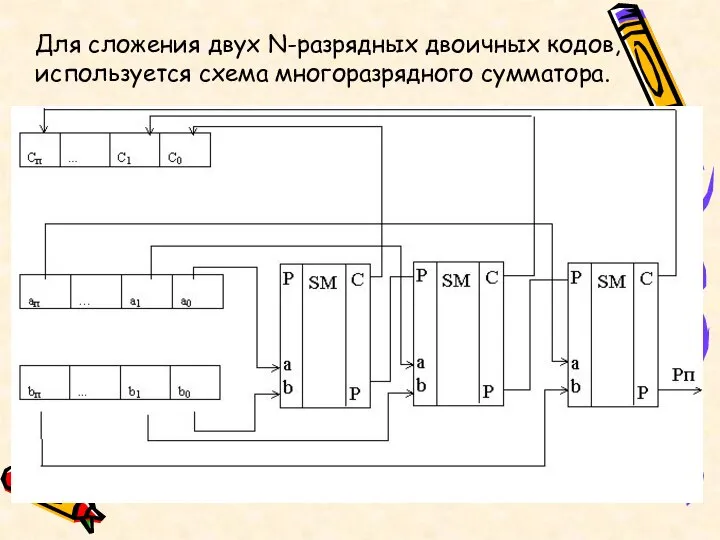

- 18. Для сложения двух N-разрядных двоичных кодов, используется схема многоразрядного сумматора.

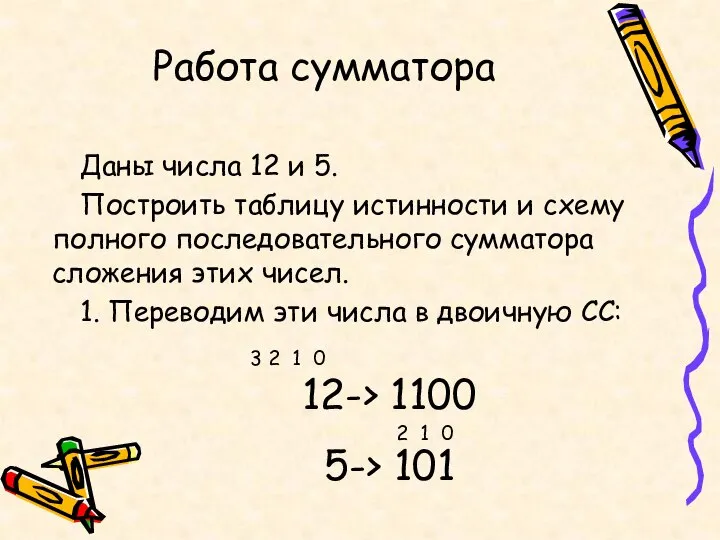

- 19. Работа сумматора Даны числа 12 и 5. Построить таблицу истинности и схему полного последовательного сумматора сложения

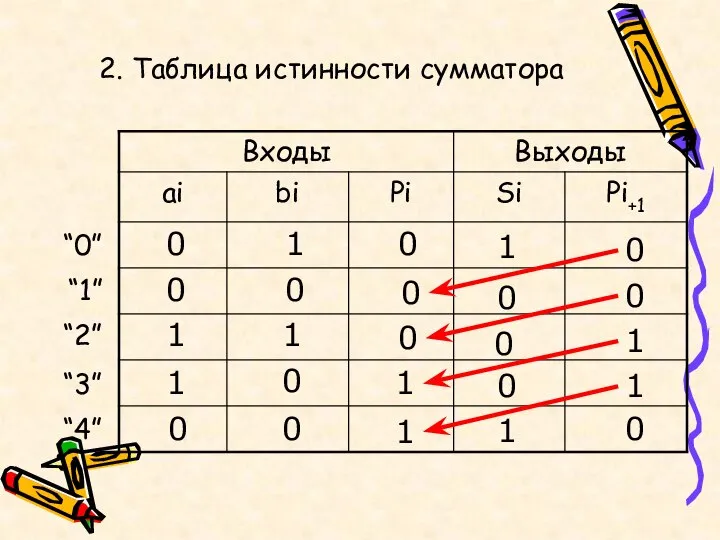

- 20. 2. Таблица истинности сумматора 0 1 1 0 0 0 0 0 0 0 1 1

- 21. Структурная схема сумматора 0

- 23. Скачать презентацию

Создание чувства безопасности

Создание чувства безопасности Презентация на тему Человек в ландшафте

Презентация на тему Человек в ландшафте Северный ледовитый океан

Северный ледовитый океан Рабочая программа по учебному предмету «Математика» 9 класс

Рабочая программа по учебному предмету «Математика» 9 класс Виды ответственности за невыполнение нормативных правовых актов по охране труда

Виды ответственности за невыполнение нормативных правовых актов по охране труда Файлы

Файлы Решения для кабельной проводки в промышленных условиях

Решения для кабельной проводки в промышленных условиях SEO

SEO Именные и другие виды стипендии

Именные и другие виды стипендии Женской судьбы страницы

Женской судьбы страницы Новогодний квиз

Новогодний квиз Презентация по геометрии на тему: «Векторы в пространстве.»

Презентация по геометрии на тему: «Векторы в пространстве.» Presentation

Presentation Теорема Минковского о многогранниках

Теорема Минковского о многогранниках С новым годом !

С новым годом ! Ошибки в цвете

Ошибки в цвете методы стандартизации

методы стандартизации Искусство мозаики

Искусство мозаики Технологии регулярного менеджмента: основа, ключевые принципы, векторы и последовательность внедрения

Технологии регулярного менеджмента: основа, ключевые принципы, векторы и последовательность внедрения Who is he?

Who is he? Конституция Республики Беларусь

Конституция Республики Беларусь Презентация

Презентация Условия для прорастания семян и роста растений (2 класс)

Условия для прорастания семян и роста растений (2 класс) Microsoft Message Queuing

Microsoft Message Queuing Компьютерный зрительный синдрому детей

Компьютерный зрительный синдрому детей Производство обжаренного кофе «Кофе Хауз»

Производство обжаренного кофе «Кофе Хауз» Конструкция и декоративное убранство татарского традиционного жилища

Конструкция и декоративное убранство татарского традиционного жилища Funny animals

Funny animals