Содержание

- 2. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Базовые матричные кристаллы (GA) БМК – это кристалл,

- 3. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Для снижения потерь площади кристалла затрачиваемой на трассировочные

- 4. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Из элементов базовой матрицы ячеек может быть сформирован

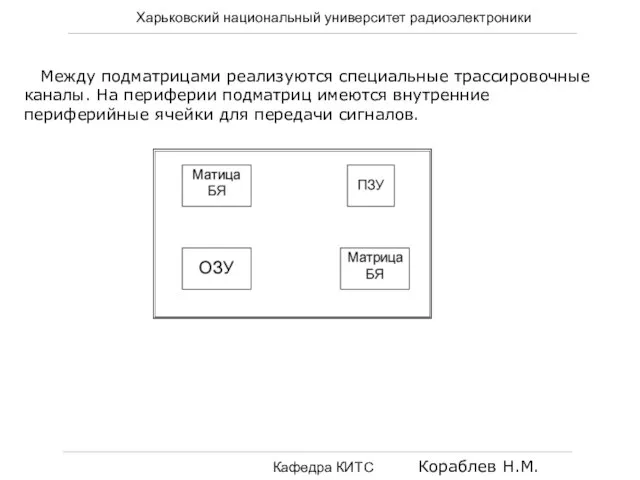

- 5. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Между подматрицами реализуются специальные трассировочные каналы. На периферии

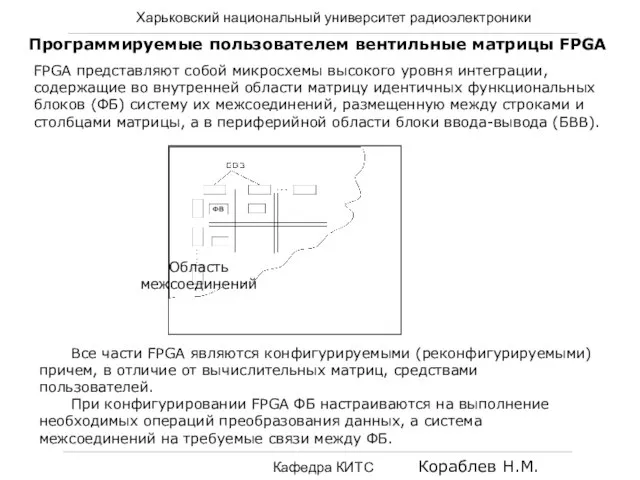

- 6. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Программируемые пользователем вентильные матрицы FPGA FPGA представляют собой

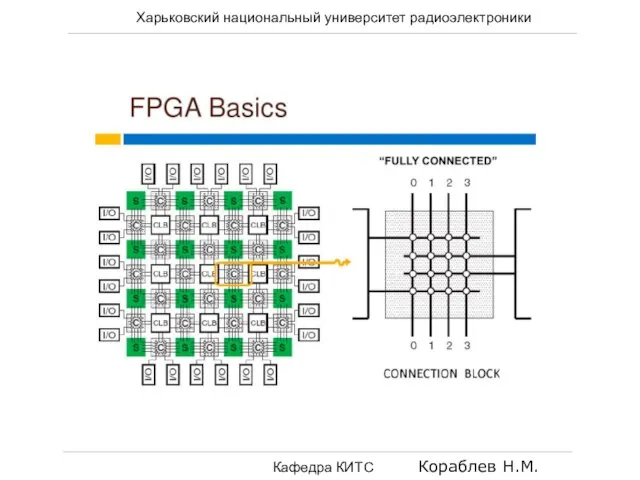

- 7. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М.

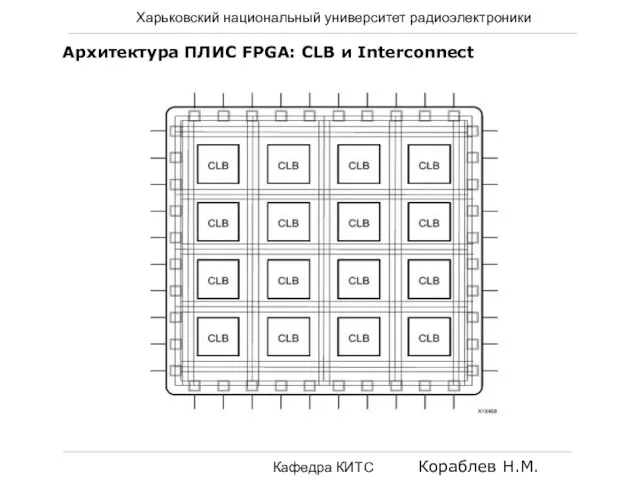

- 8. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Архитектура ПЛИС FPGA: CLB и Interconnect

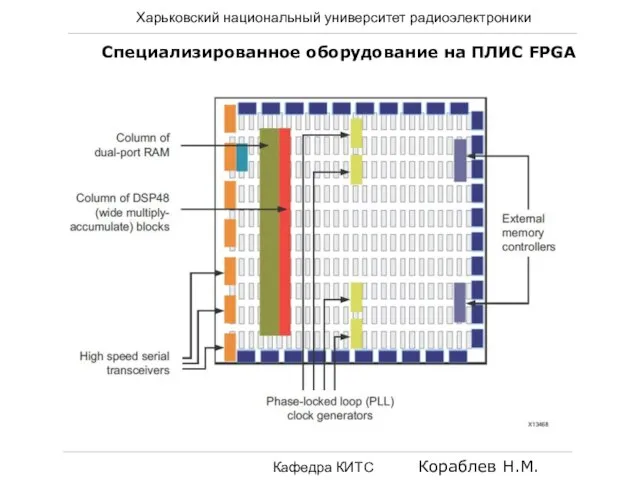

- 9. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Специализированное оборудование на ПЛИС FPGA

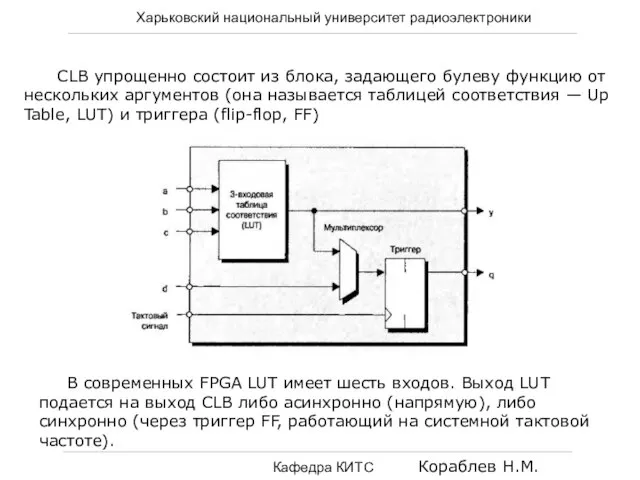

- 10. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. CLB упрощенно состоит из блока, задающего булеву функцию

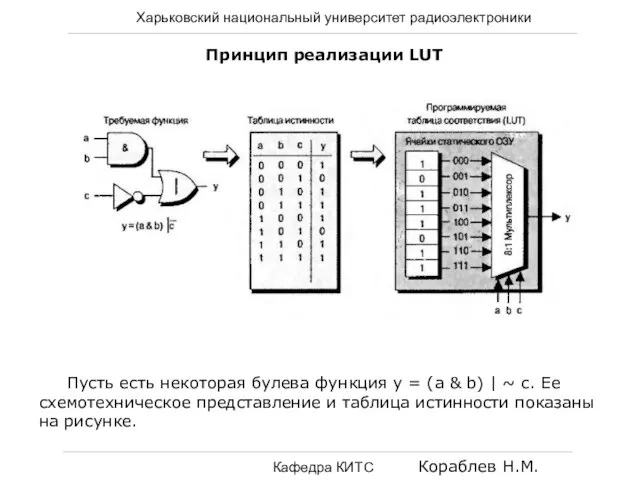

- 11. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Принцип реализации LUT Пусть есть некоторая булева функция

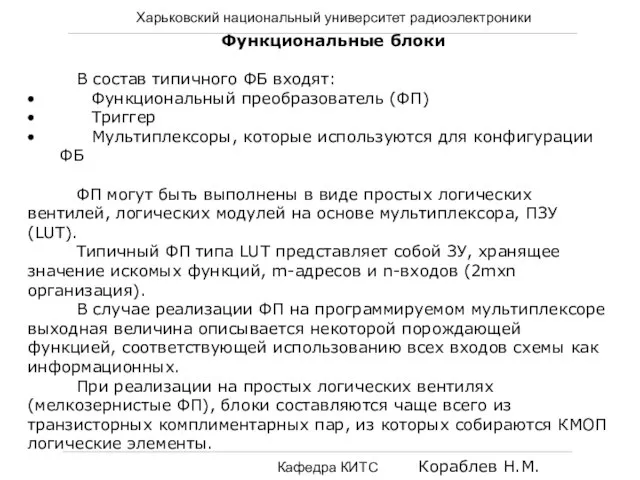

- 12. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Функциональные блоки В состав типичного ФБ входят: Функциональный

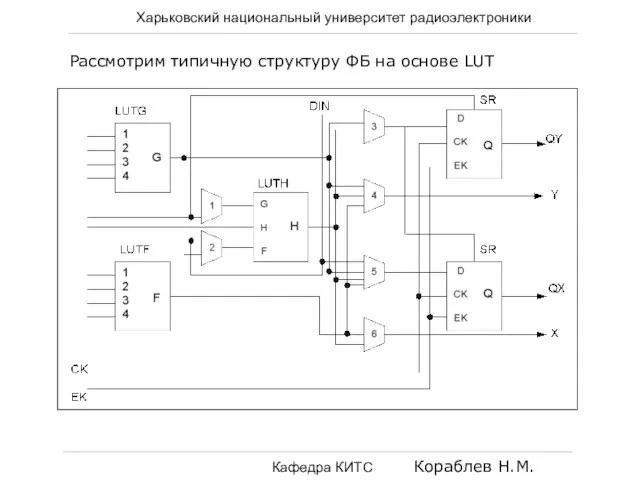

- 13. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Рассмотрим типичную структуру ФБ на основе LUT

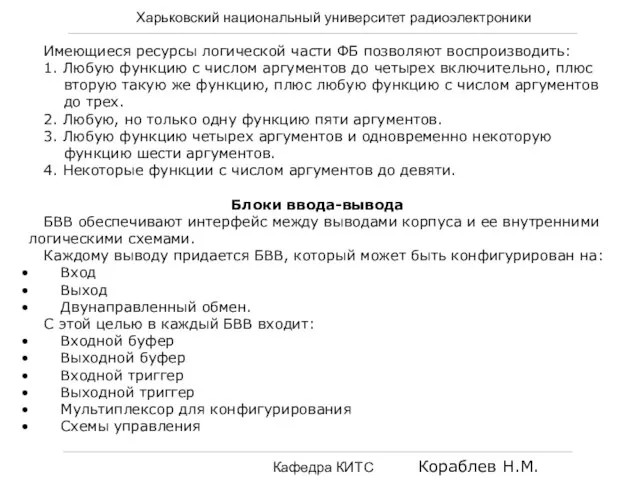

- 14. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Имеющиеся ресурсы логической части ФБ позволяют воспроизводить: 1.

- 15. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Система межсоединений Для системы межсоединений в FPGA организация

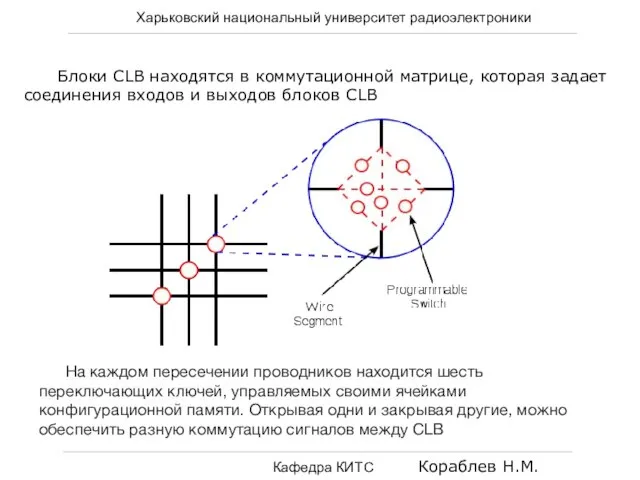

- 16. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Блоки CLB находятся в коммутационной матрице, которая задает

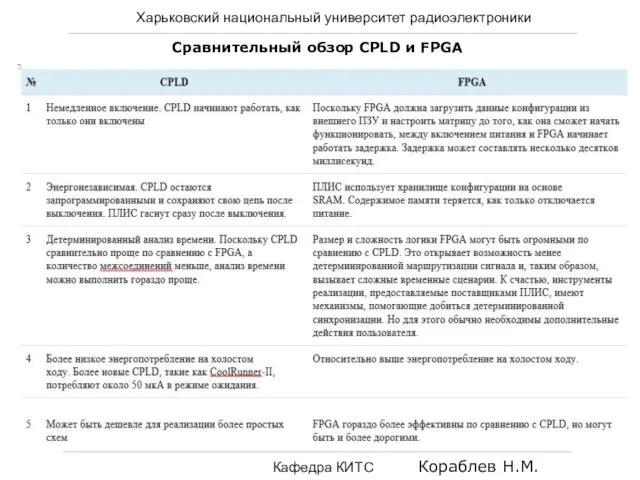

- 17. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Cравнительный обзор CPLD и FPGA

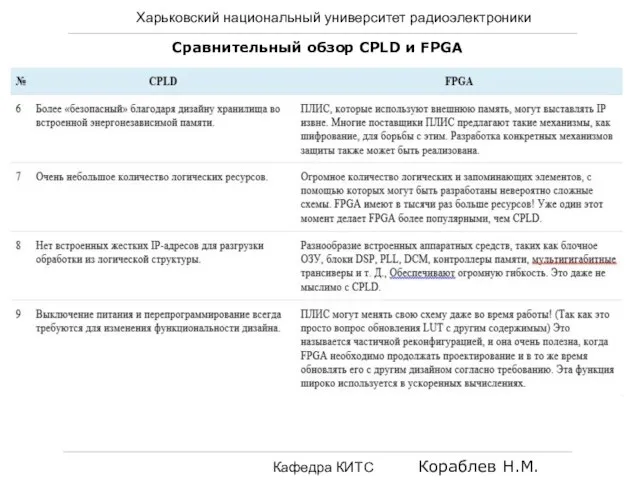

- 18. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Cравнительный обзор CPLD и FPGA

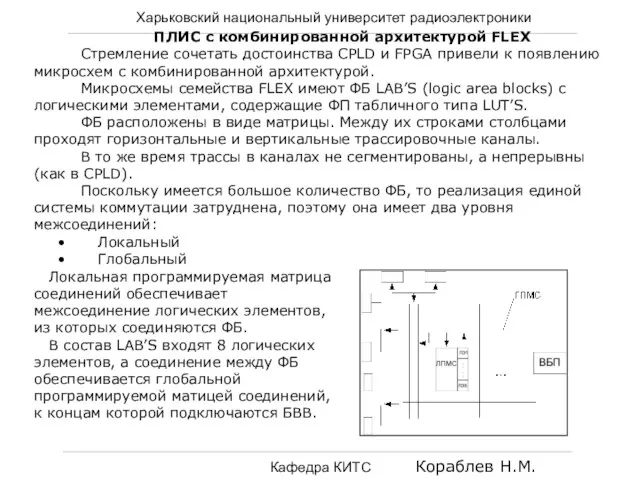

- 19. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. ПЛИС с комбинированной архитектурой FLEX Стремление сочетать достоинства

- 20. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. В составе многих микросхем имеются встроенные блоки памяти,

- 21. Харьковский национальный университет радиоэлектроники Кафедра КИТС Кораблев Н.М. Рассмотрим упрощенную структуру такого логического элемента:

- 23. Скачать презентацию

ООО Континент тур

ООО Континент тур Блудный сын

Блудный сын Правописание жи и ши

Правописание жи и ши Лекция №5. Особенности реконструкции дорожных одежд нежесткого типа

Лекция №5. Особенности реконструкции дорожных одежд нежесткого типа Япония Столица-город Токио

Япония Столица-город Токио Мочевыделительная система

Мочевыделительная система Strategic marketing

Strategic marketing Музеи искусства

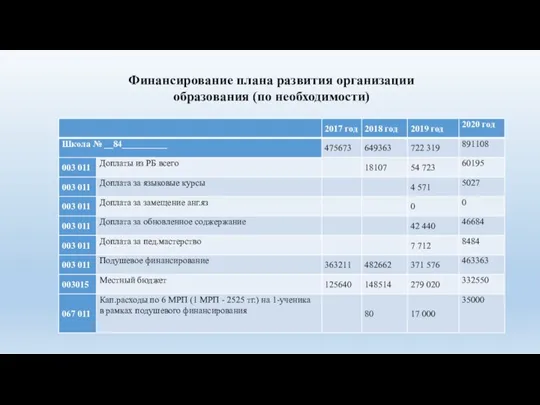

Музеи искусства Финансирование плана развития организации образования

Финансирование плана развития организации образования Современное стрелковое оружие

Современное стрелковое оружие Зоогостиница Лесси

Зоогостиница Лесси Хостел Достоевский в центре Челябинска

Хостел Достоевский в центре Челябинска Псалом 9. Полны клятв слова его, уста полны лести и лжи

Псалом 9. Полны клятв слова его, уста полны лести и лжи Стандартизация. Общие положения стандартизации

Стандартизация. Общие положения стандартизации Десерт Шокомяч

Десерт Шокомяч ВИЧ и СПИД

ВИЧ и СПИД Фонды целевого капитала: состояние рынка Киев, 23 февраля 2012

Фонды целевого капитала: состояние рынка Киев, 23 февраля 2012 Афины и Спарта

Афины и Спарта Руководитель маркетинга как им быть или как им стать

Руководитель маркетинга как им быть или как им стать Гимнастика. Виды гимнастики

Гимнастика. Виды гимнастики Экономический рост

Экономический рост Информационные технологии в производстве авиационных двигателей УМПО

Информационные технологии в производстве авиационных двигателей УМПО Братья наши меньшие.

Братья наши меньшие. Кандалакшская районная организация профсоюза работников народного образования: публичный отчёт 2020

Кандалакшская районная организация профсоюза работников народного образования: публичный отчёт 2020 МЕТОДЫ УПРАВЛЕНИЯ

МЕТОДЫ УПРАВЛЕНИЯ Современная туристическая одежда

Современная туристическая одежда Профессия моей мамы

Профессия моей мамы Презентация на тему Одиссея Гомера (5 класс)

Презентация на тему Одиссея Гомера (5 класс)