Содержание

- 2. Конечные автоматы. Автомат Мура Текущее состояние

- 3. Конечные автоматы. Автомат Мили Текущее состояние

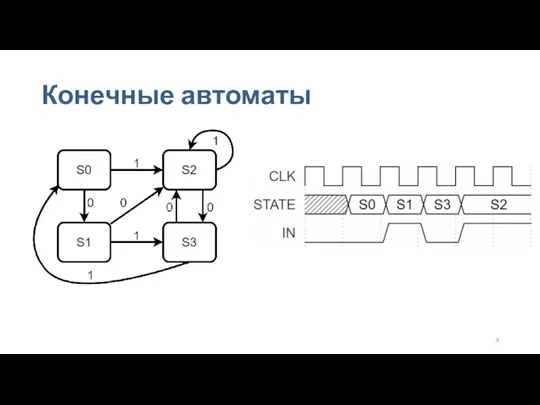

- 4. Конечные автоматы

- 5. Конечные автоматы. Verilog HDL module my_fsm ( … ); reg [1:0] STATE; always @(posedge CLK) begin

- 6. Упражнение: кодовый замок wire [3:0] key_db; sync_and_debounce # (.w (4), .depth (debounce_depth)) i_sync_and_debounce_key (clk, reset, ~

- 7. Упражнение: кодовый замок wire [3:0] out_reg; shift_register # (.w (4)) i_shift_reg ( .clk ( clk ),

- 8. Упражнение: кодовый замок wire [7:0] shift_strobe_count; counter # (8) i_shift_strobe_counter ( .clk ( clk ), .reset

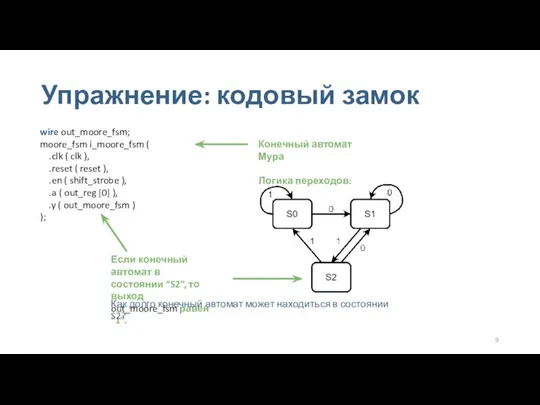

- 9. Упражнение: кодовый замок wire out_moore_fsm; moore_fsm i_moore_fsm ( .clk ( clk ), .reset ( reset ),

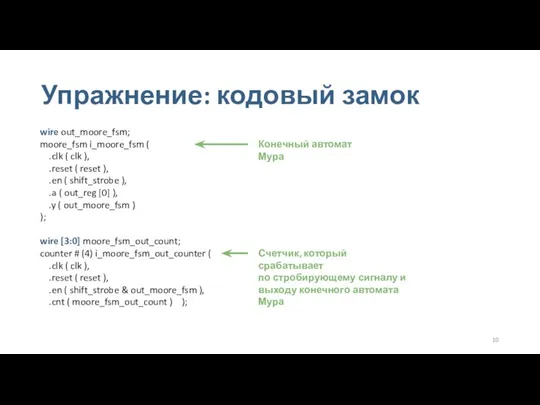

- 10. Упражнение: кодовый замок wire out_moore_fsm; moore_fsm i_moore_fsm ( .clk ( clk ), .reset ( reset ),

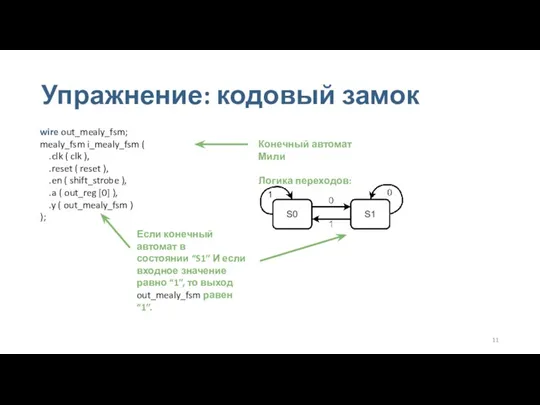

- 11. Упражнение: кодовый замок Если конечный автомат в состоянии “S1” И если входное значение равно “1”, то

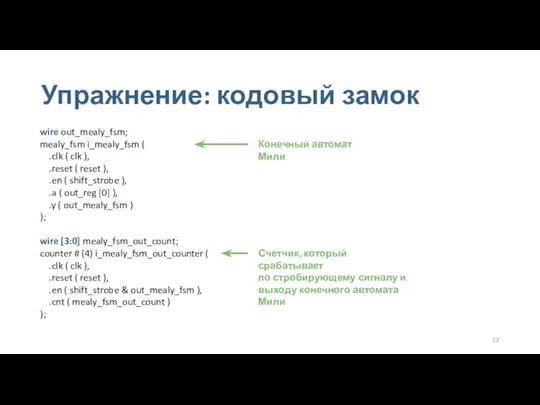

- 12. Упражнение: кодовый замок wire out_mealy_fsm; mealy_fsm i_mealy_fsm ( .clk ( clk ), .reset ( reset ),

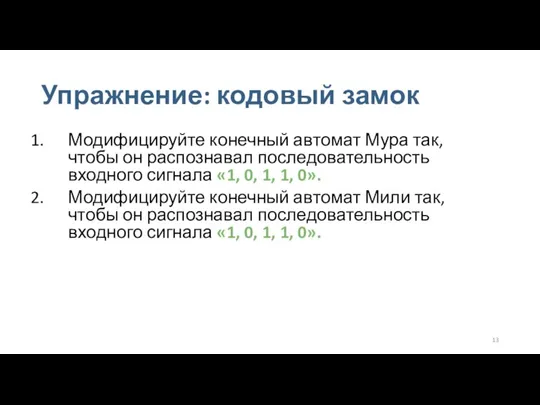

- 13. Упражнение: кодовый замок Модифицируйте конечный автомат Мура так, чтобы он распознавал последовательность входного сигнала «1, 0,

- 14. Конечные автоматы. Источники информации Материалы для это части презентации взяты из материалов: Clifford E. Cummings The

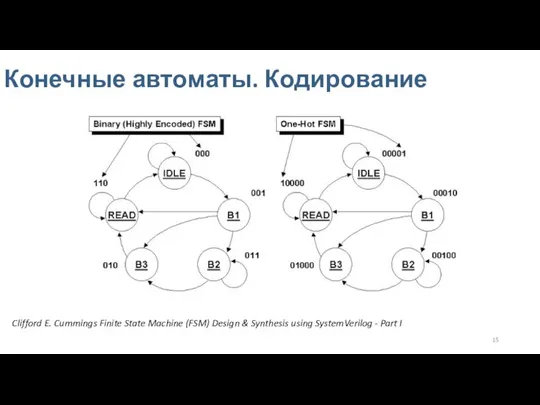

- 15. Конечные автоматы. Кодирование Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis using SystemVerilog -

- 16. Конечные автоматы. Требования к описанию FSM Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis

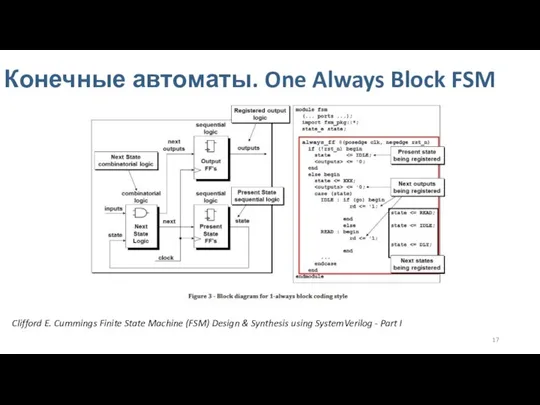

- 17. Конечные автоматы. One Always Block FSM Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis

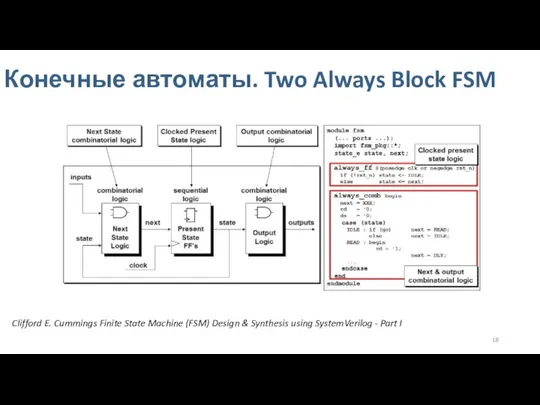

- 18. Конечные автоматы. Two Always Block FSM Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis

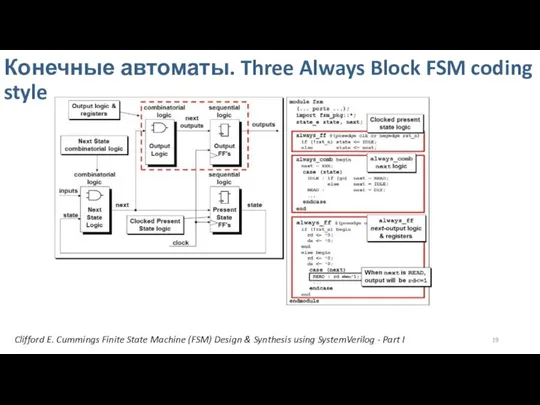

- 19. Конечные автоматы. Three Always Block FSM coding style Clifford E. Cummings Finite State Machine (FSM) Design

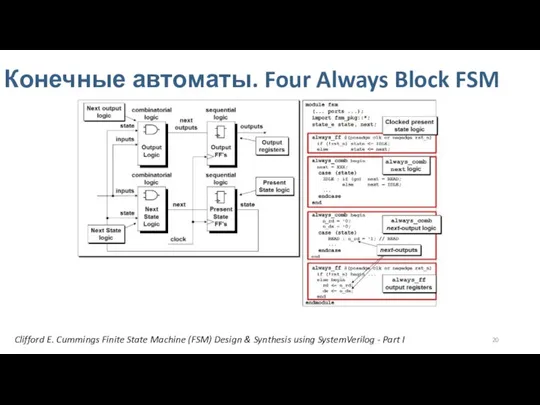

- 20. Конечные автоматы. Four Always Block FSM Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis

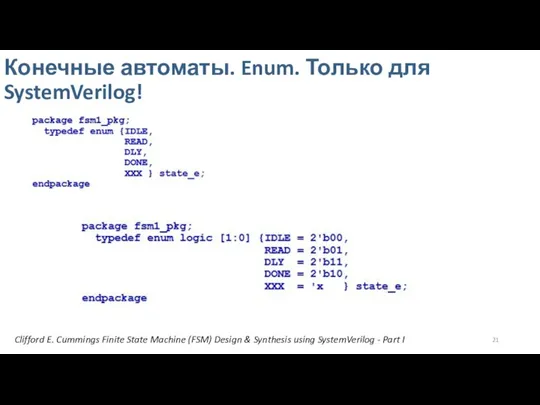

- 21. Конечные автоматы. Enum. Только для SystemVerilog! Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis

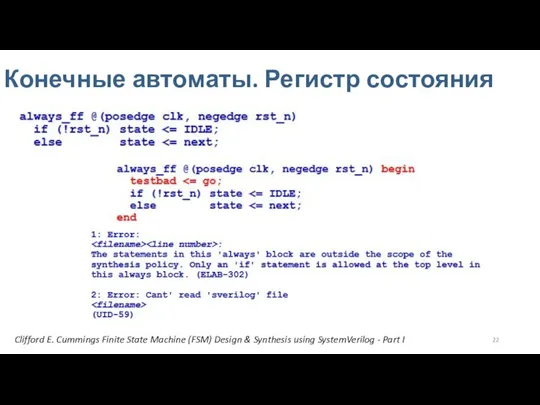

- 22. Конечные автоматы. Регистр состояния Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis using SystemVerilog

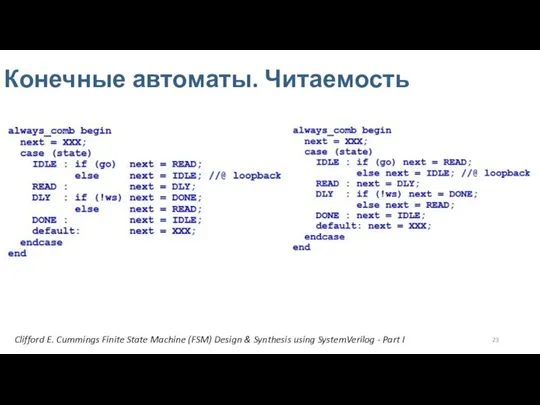

- 23. Конечные автоматы. Читаемость Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis using SystemVerilog -

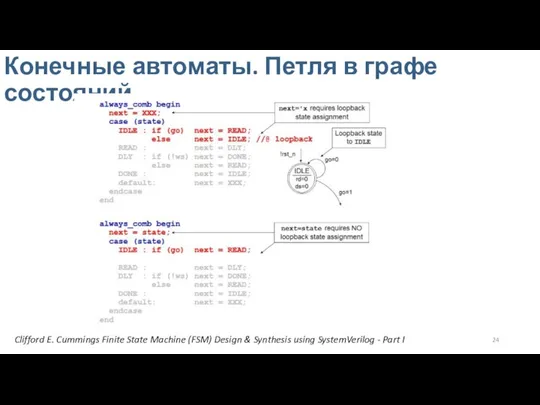

- 24. Конечные автоматы. Петля в графе состояний Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis

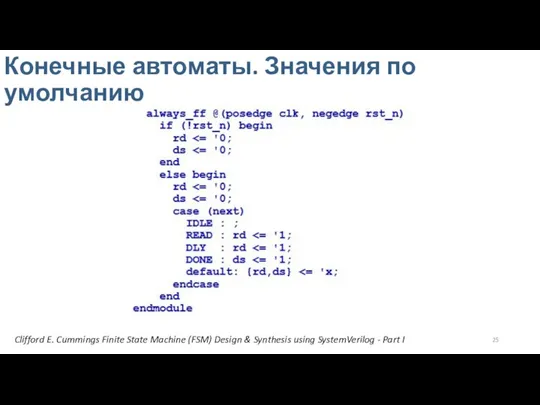

- 25. Конечные автоматы. Значения по умолчанию Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis using

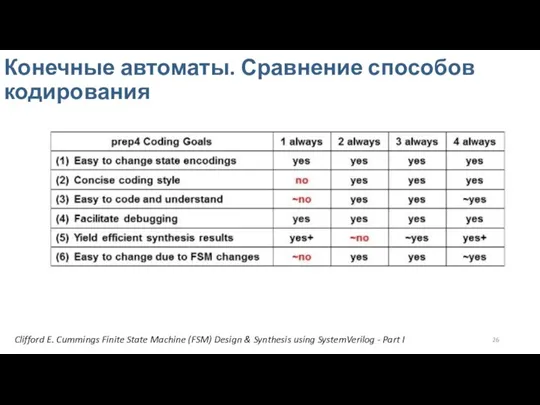

- 26. Конечные автоматы. Сравнение способов кодирования Clifford E. Cummings Finite State Machine (FSM) Design & Synthesis using

- 27. Упражнение: игра Есть игровое устройство с 4 индикаторами на HEX. На каждом циклически изменяется выводимое значение

- 28. Упражнение: игра, первый уровень Цель игры набрать на индикаторах последовательность цифр заданную в проекте. Например, 7489.

- 29. Упражнение: игра, второй уровень Измените логику работы конечного автомата так чтобы неправильная последовательность нажатия кнопок приводила

- 30. Упражнение: игра, третий уровень Добавьте дополнительные модули генерации стробов для того чтобы скорость изменения индикаторов была

- 31. Упражнение: игра, четвёртый уровень Хорошо если бы цифры менялись на индикаторах не последовательно а случайно. Модифицируйте

- 32. Генерация псевдослучайной последовательности чисел в RTL Материалы для это части презентации взяты из лекции Patrick Schaumont

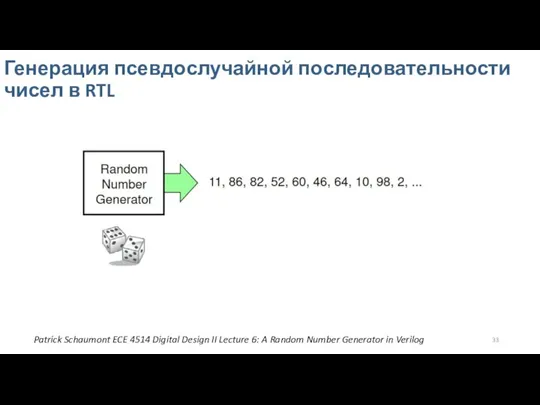

- 33. Генерация псевдослучайной последовательности чисел в RTL Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A

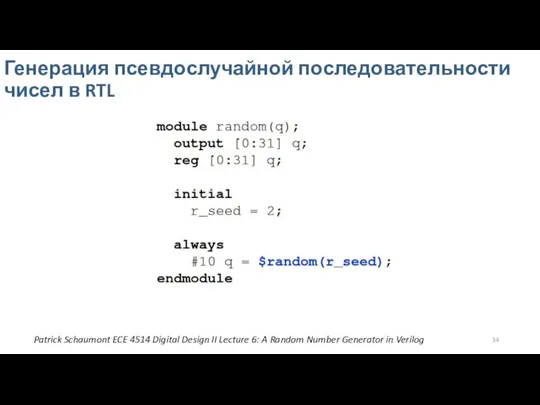

- 34. Генерация псевдослучайной последовательности чисел в RTL Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A

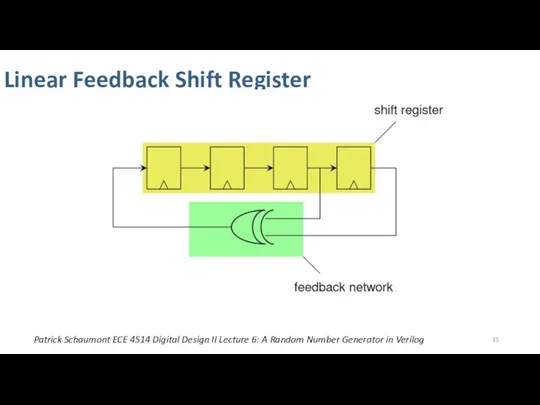

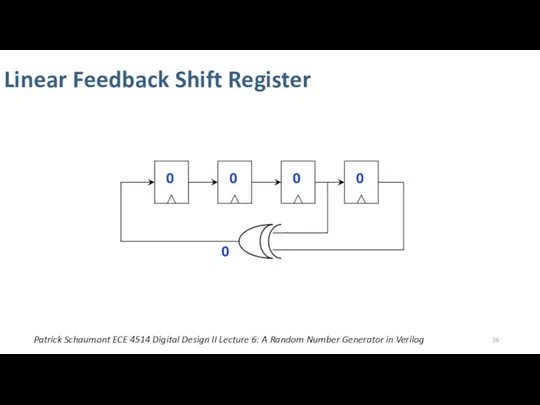

- 35. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

- 36. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

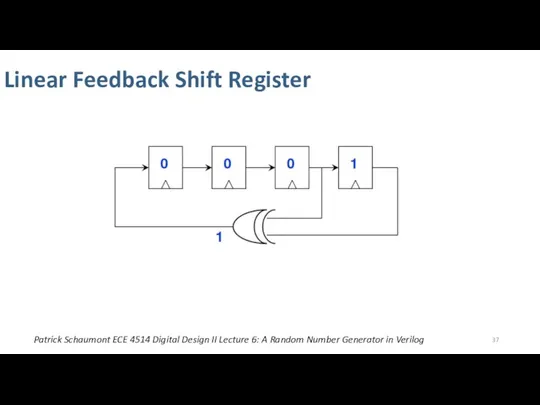

- 37. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

- 38. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

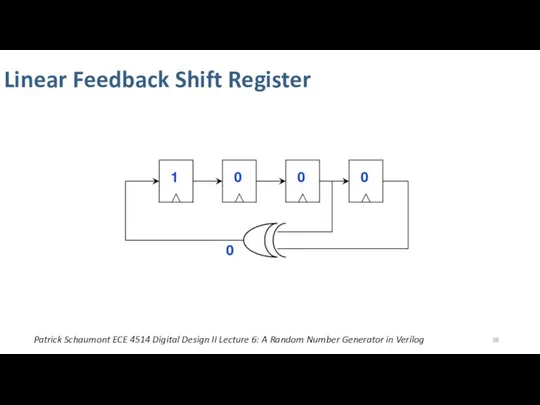

- 39. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

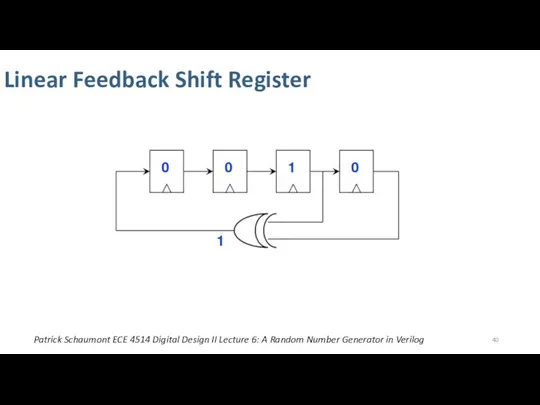

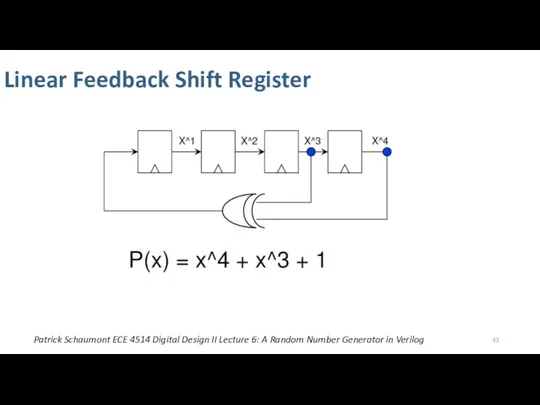

- 40. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

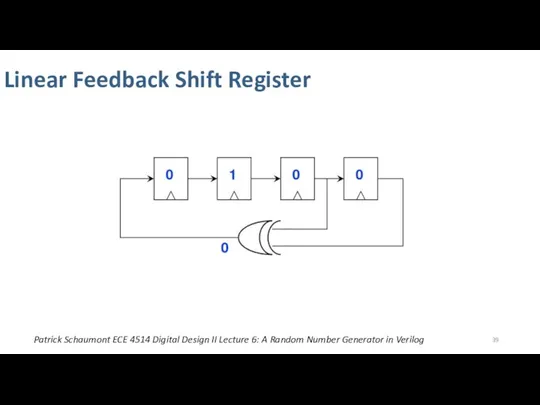

- 41. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

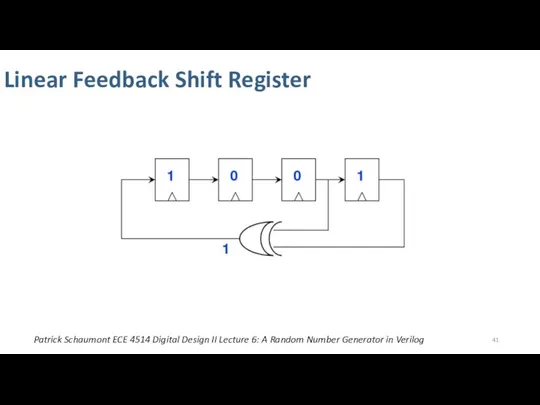

- 42. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

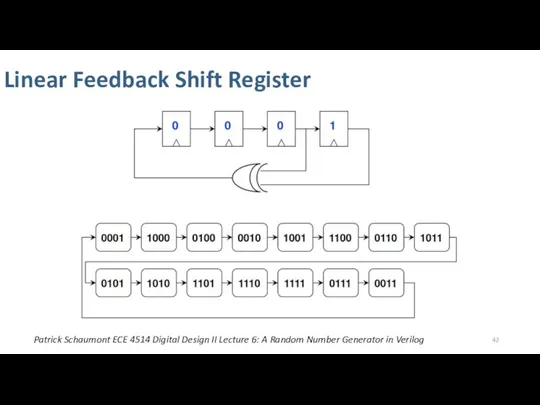

- 43. Linear Feedback Shift Register Patrick Schaumont ECE 4514 Digital Design II Lecture 6: A Random Number

- 45. Скачать презентацию

![Конечные автоматы. Verilog HDL module my_fsm ( … ); reg [1:0] STATE;](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1176605/slide-4.jpg)

![Упражнение: кодовый замок wire [3:0] key_db; sync_and_debounce # (.w (4), .depth (debounce_depth))](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1176605/slide-5.jpg)

![Упражнение: кодовый замок wire [3:0] out_reg; shift_register # (.w (4)) i_shift_reg (](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1176605/slide-6.jpg)

![Упражнение: кодовый замок wire [7:0] shift_strobe_count; counter # (8) i_shift_strobe_counter ( .clk](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1176605/slide-7.jpg)

Комнатные растения

Комнатные растения Правовой_режим_особо_охраняемых_тер_и_об

Правовой_режим_особо_охраняемых_тер_и_об Идеи для фотосессий

Идеи для фотосессий Канцерогенез и онкорезистентность

Канцерогенез и онкорезистентность Самобытность личности

Самобытность личности Искусство Жостова

Искусство Жостова У р а! Мы отправляемся в путешествие!

У р а! Мы отправляемся в путешествие! Dream Loft

Dream Loft (1917 - 1986)

(1917 - 1986) Эволюция автоматической коммутации

Эволюция автоматической коммутации Бюро находок: "Найдите букву З"

Бюро находок: "Найдите букву З" Суп, салат, пюре, котлеты Подают всегда в … По моей тарелке лодочка плывёт. Лодочку с едою отправляю в рот. Тарелке Ложка. - презентация

Суп, салат, пюре, котлеты Подают всегда в … По моей тарелке лодочка плывёт. Лодочку с едою отправляю в рот. Тарелке Ложка. - презентация Базисный учебный план НАЧАЛЬНОГО ОБЩЕГО ОБРАЗОВАНИЯ

Базисный учебный план НАЧАЛЬНОГО ОБЩЕГО ОБРАЗОВАНИЯ АКТУАЛЬНЫЕ ПРОБЛЕМЫ ДОУ ЛАРИН Михаил Васильевич, директор Всероссийского научно-исследовательского института докуме

АКТУАЛЬНЫЕ ПРОБЛЕМЫ ДОУ ЛАРИН Михаил Васильевич, директор Всероссийского научно-исследовательского института докуме Проектная работа “Почему компьютеры болеют?” ученицы 6 “А” класса Матийко Дарьи Учитель информатики: Ивченко Надежда Валерьев

Проектная работа “Почему компьютеры болеют?” ученицы 6 “А” класса Матийко Дарьи Учитель информатики: Ивченко Надежда Валерьев Бонусные опции

Бонусные опции ИНТЕЛТЕК ПЛЮС

ИНТЕЛТЕК ПЛЮС Построение объёма

Построение объёма Культурный ассимилятор. Португальцы VS Бразильцы

Культурный ассимилятор. Португальцы VS Бразильцы Презентация на тему Английская буржуазная революция и ее значение

Презентация на тему Английская буржуазная революция и ее значение Техника безопасности на занятиях гимнастикой. Основные группы мышц и способы их развития

Техника безопасности на занятиях гимнастикой. Основные группы мышц и способы их развития Блок системы взаимоотношений

Блок системы взаимоотношений Волнистый попугайчик – Любимый питомец в доме

Волнистый попугайчик – Любимый питомец в доме Красота человека. Разноцветная палитра

Красота человека. Разноцветная палитра Презентация на тему учимся быть пешеходами 1 класс

Презентация на тему учимся быть пешеходами 1 класс  German Doctor Exchange

German Doctor Exchange  Телевидение и Интернет: параллельные пересекаются!?

Телевидение и Интернет: параллельные пересекаются!? Networks and telecommunications

Networks and telecommunications