Содержание

- 2. Уровень 0: Логические и запоминающие элементы Логические элементы Сигналы: На вход можно подать потенциал логического нуля

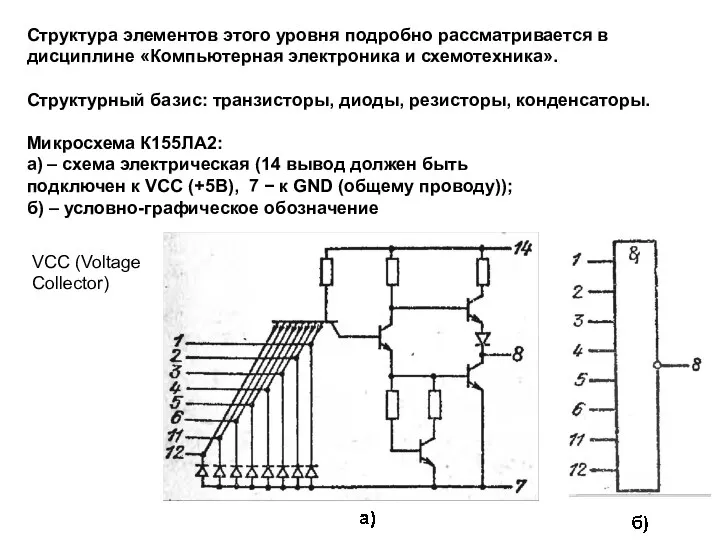

- 3. Структура элементов этого уровня подробно рассматривается в дисциплине «Компьютерная электроника и схемотехника». Структурный базис: транзисторы, диоды,

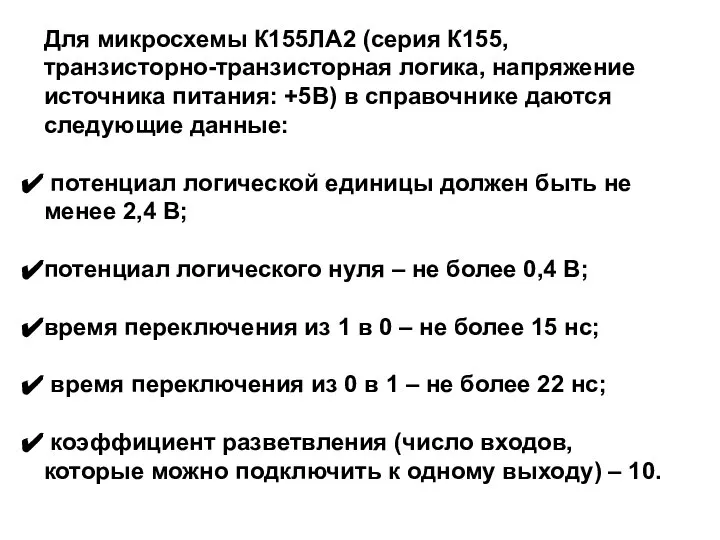

- 4. Для микросхемы К155ЛА2 (серия К155, транзисторно-транзисторная логика, напряжение источника питания: +5В) в справочнике даются следующие данные:

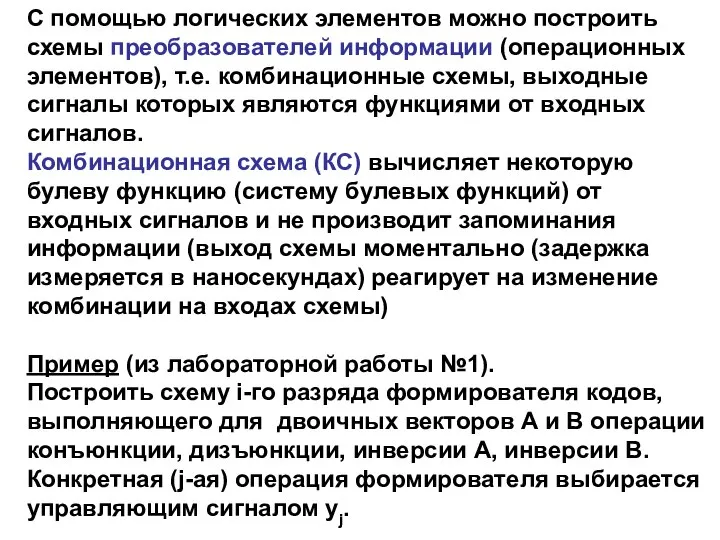

- 5. С помощью логических элементов можно построить схемы преобразователей информации (операционных элементов), т.е. комбинационные схемы, выходные сигналы

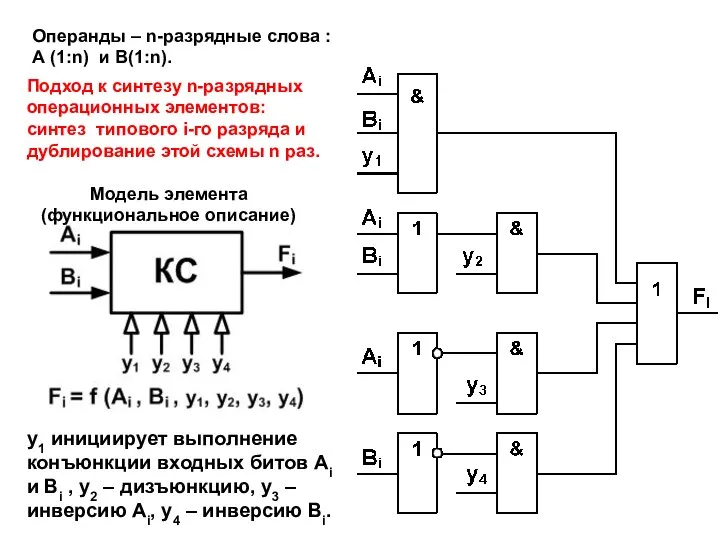

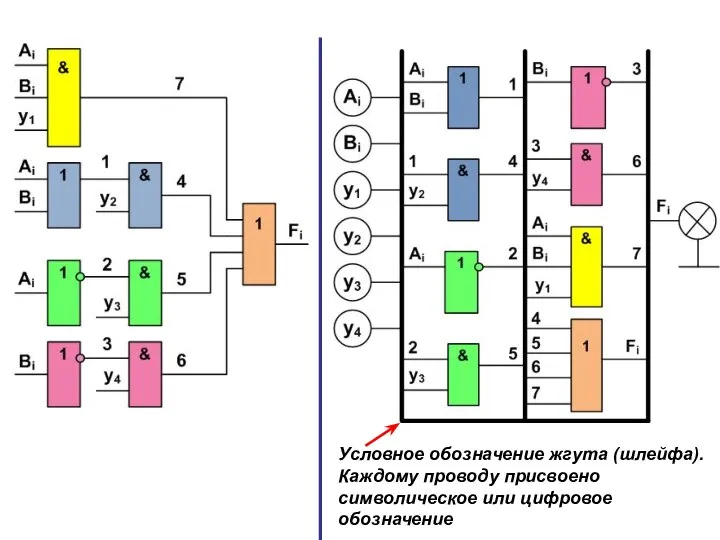

- 6. Операнды – n-разрядные слова : А (1:n) и B(1:n). Подход к синтезу n-разрядных операционных элементов: синтез

- 7. Жгут из проводов Шлейф из проводов

- 8. Условное обозначение жгута (шлейфа). Каждому проводу присвоено символическое или цифровое обозначение

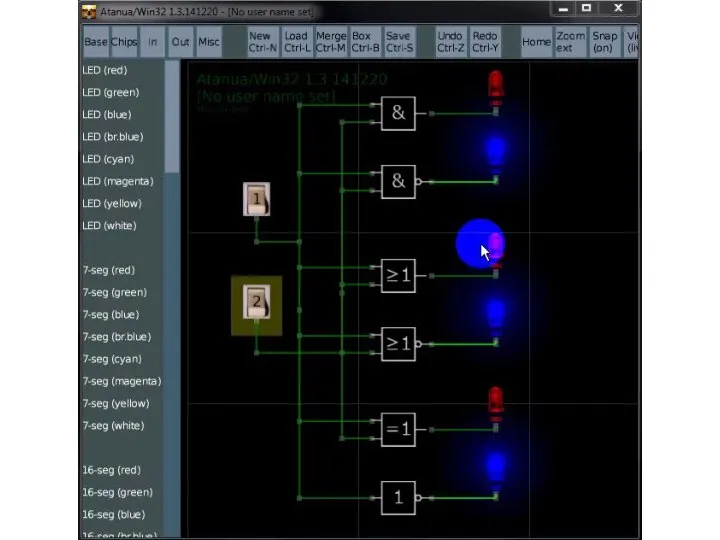

- 9. Тестирование схемы Тест – набор входных данных и соответствующий ему набор выходных данных. Совокупность тестов для

- 10. https://sol.gfxile.net/atanua/index.html Для тестирования электронных схем мы будем использовать простой , свободно распространяемый симулятор логики Atanua:

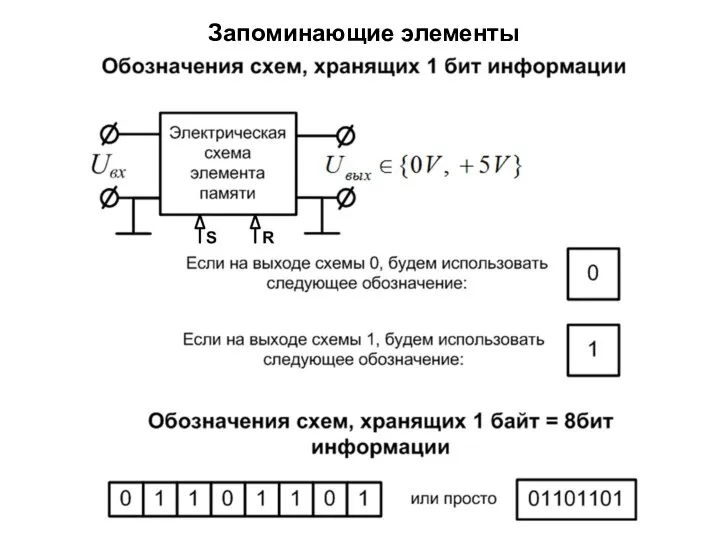

- 12. Запоминающие элементы

- 13. = 1*20+0*21+1*22+1+23+0*24+1*25+1*26= = 1+4+8+32+64=+109 Числа представляются в ЭВМ в двоичной системе счисления Представление данных

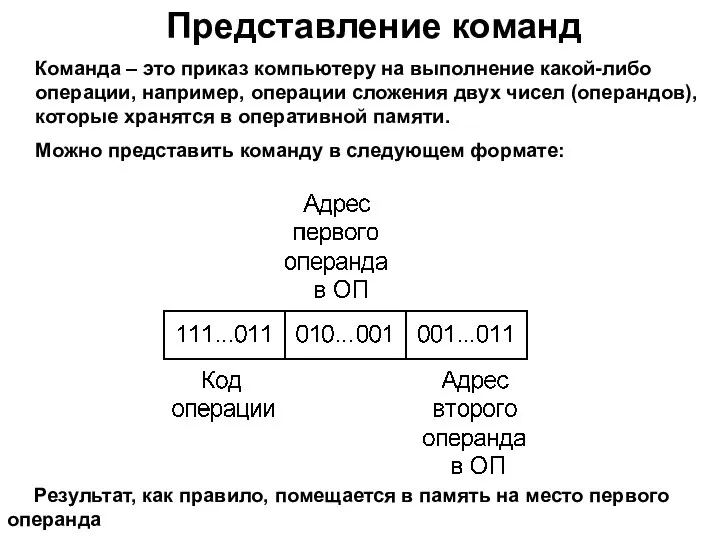

- 14. Представление команд Команда – это приказ компьютеру на выполнение какой-либо операции, например, операции сложения двух чисел

- 15. Терминология: Электрические схемы, хранящие 1 бит информации называют триггерами. Электрические схемы, хранящие n бит информации (n>1)

- 16. Асинхронный RS-триггер с раздельными входами а) – реализация в базисе ИЛИ-НЕ; б) – условно-графическое обозначение Таблица

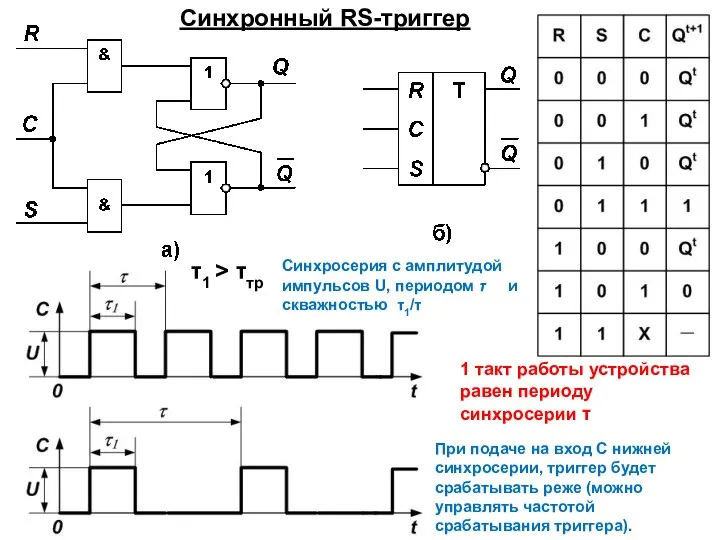

- 17. τ1 > τтр Синхронный RS-триггер 1 такт работы устройства равен периоду синхросерии τ При подаче на

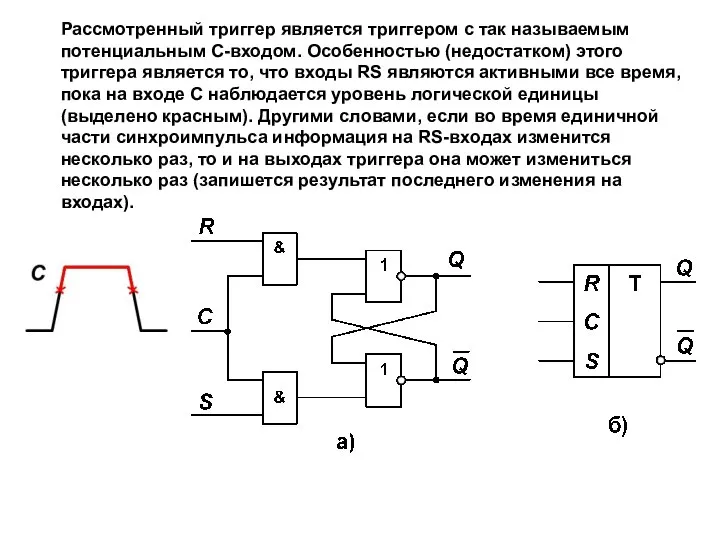

- 18. Рассмотренный триггер является триггером с так называемым потенциальным C-входом. Особенностью (недостатком) этого триггера является то, что

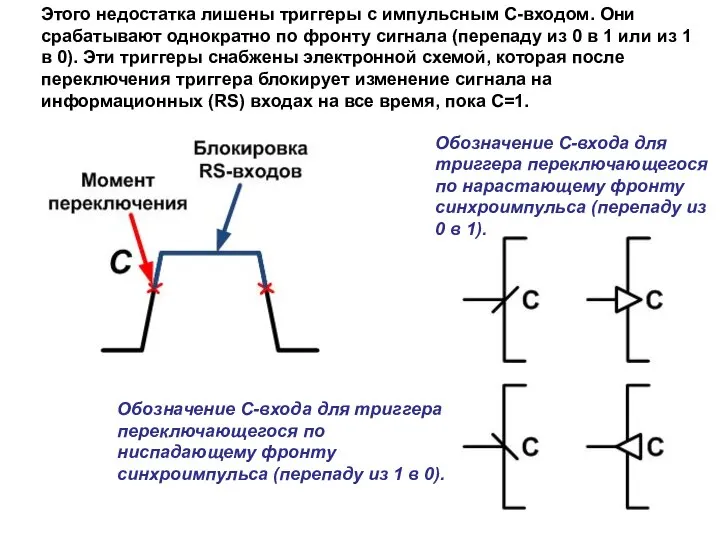

- 19. Этого недостатка лишены триггеры с импульсным C-входом. Они срабатывают однократно по фронту сигнала (перепаду из 0

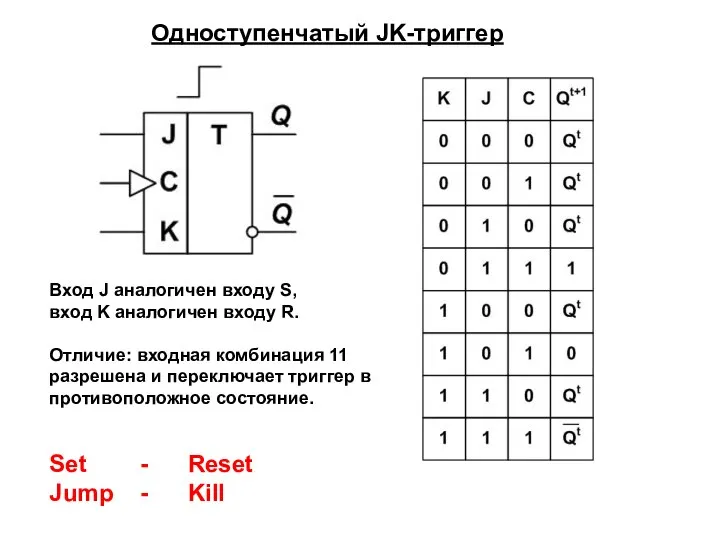

- 20. Одноступенчатый JK-триггер Вход J аналогичен входу S, вход K аналогичен входу R. Отличие: входная комбинация 11

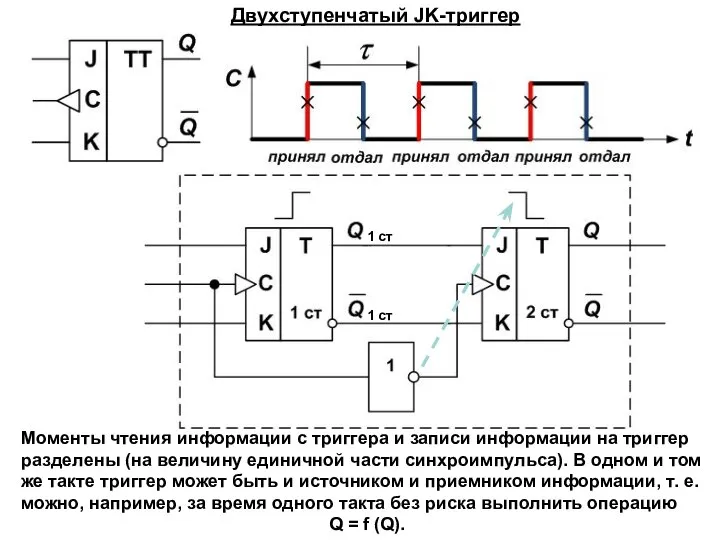

- 21. Двухступенчатый JK-триггер Моменты чтения информации с триггера и записи информации на триггер разделены (на величину единичной

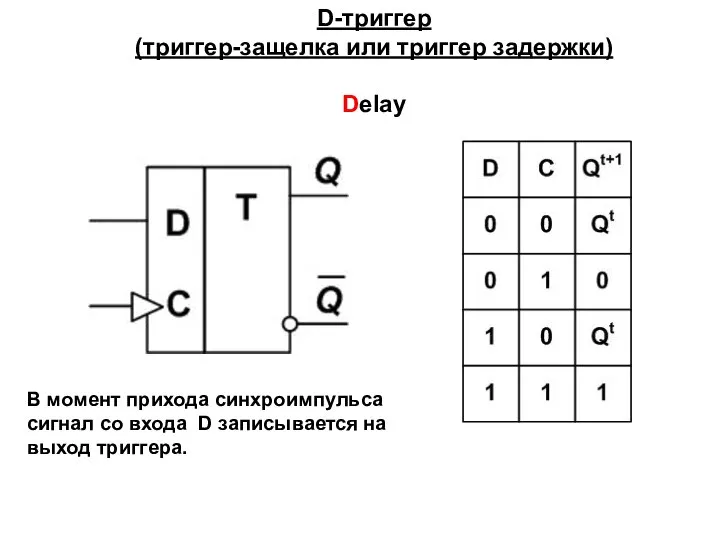

- 22. D-триггер (триггер-защелка или триггер задержки) Delay В момент прихода синхроимпульса сигнал со входа D записывается на

- 23. Микросхемы серии 74HC** 74HC112 – два двухступенчатых JK-триггера с установочными RS-входами (аналог – К155ТВ9)

- 24. 74HC74 – два D-триггера с установочными RS-входами (аналог – К155ТМ2)

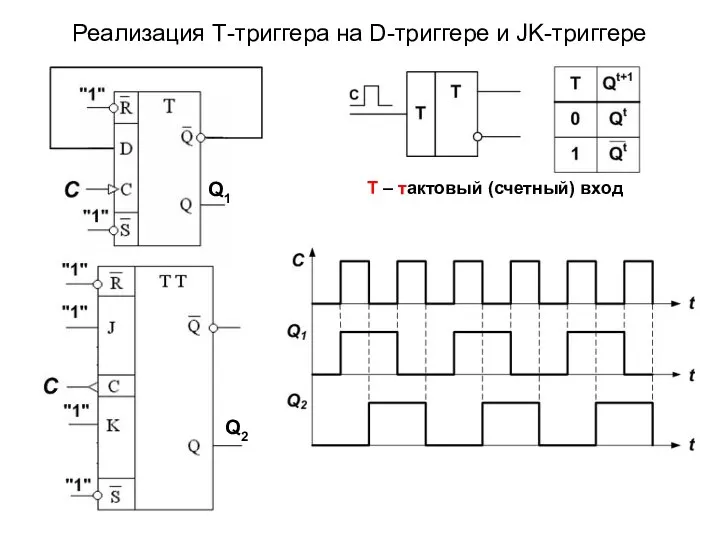

- 25. Реализация Т-триггера на D-триггере и JK-триггере Q1 Q2 Т – тактовый (счетный) вход

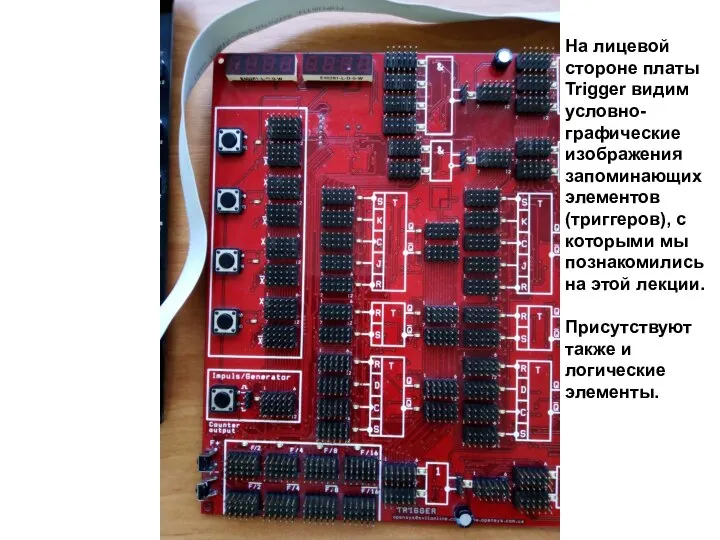

- 26. Для получения навыков проектирования, сборки и наладки схем будем использовать макет Logic-Trigger.

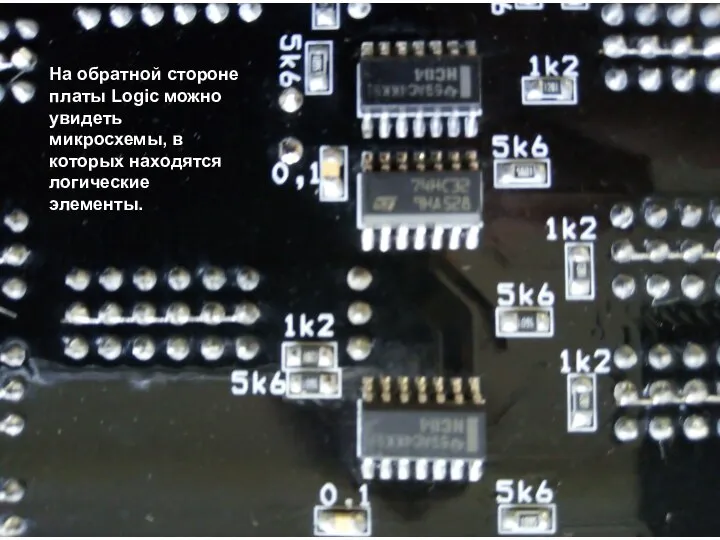

- 27. y На обратной стороне платы Logic можно увидеть микросхемы, в которых находятся логические элементы.

- 28. На лицевой стороне платы Trigger видим условно-графические изображения запоминающих элементов (триггеров), с которыми мы познакомились на

- 31. Скачать презентацию

Стандарт cXML в корпоративных приложениях электронной коммерции

Стандарт cXML в корпоративных приложениях электронной коммерции Натюрморт в фотографии

Натюрморт в фотографии Золотой век русской культуры. Литература. Живопись

Золотой век русской культуры. Литература. Живопись титул констатирующего

титул констатирующего Повесть о настоящем человеке

Повесть о настоящем человеке Выпускающая кафедра«Механика механизмов и машин» Заведующий кафедрой Шевченко Игорь Владимирович

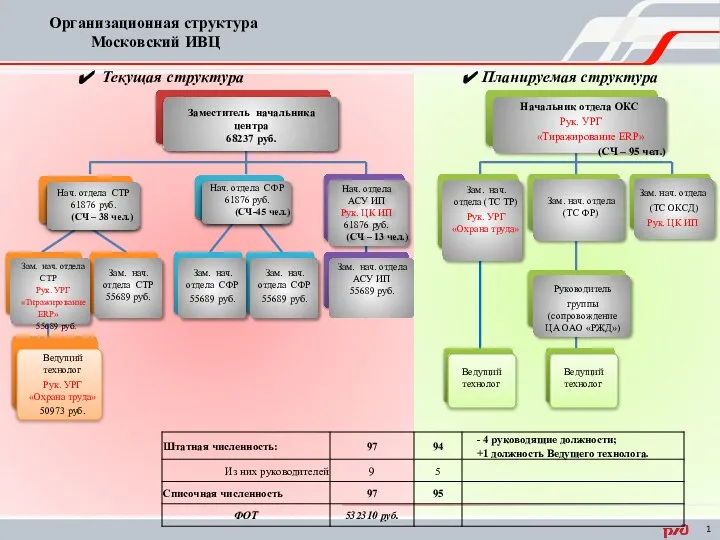

Выпускающая кафедра«Механика механизмов и машин» Заведующий кафедрой Шевченко Игорь Владимирович Организационная структура Московский ИВЦ

Организационная структура Московский ИВЦ День рождения Деда Мороза

День рождения Деда Мороза Поздравление с Новым годом

Поздравление с Новым годом Радиотехнические системы (РТС)

Радиотехнические системы (РТС) Презентация Microsoft PowerPoint [Автосохраненный]

Презентация Microsoft PowerPoint [Автосохраненный] Плюсы группы Т Плюс

Плюсы группы Т Плюс КВН – игра «В стране географов и географинь»

КВН – игра «В стране географов и географинь» Компьютерный кружок

Компьютерный кружок Изучение работы сварного соединения

Изучение работы сварного соединения  Осень… На улице холодно и сыро

Осень… На улице холодно и сыро Презентация на тему Познавательные способности

Презентация на тему Познавательные способности Башкирский государственный университет. Магистратура по социологии

Башкирский государственный университет. Магистратура по социологии Слово и время

Слово и время ИСПОЛЬЗОВАНИЕ МОБИЛЬНОГО КОМПЬЮТЕРНОГО КЛАССАВ УЧЕБНО-ВОСПИТАТЕЛЬНОМ ПРОЦЕССЕ МОУ СОШ 30

ИСПОЛЬЗОВАНИЕ МОБИЛЬНОГО КОМПЬЮТЕРНОГО КЛАССАВ УЧЕБНО-ВОСПИТАТЕЛЬНОМ ПРОЦЕССЕ МОУ СОШ 30 Презентация на тему Презентация "Буквы Уу Ээ"

Презентация на тему Презентация "Буквы Уу Ээ" Nature’s Sunshine Products

Nature’s Sunshine Products Православная молитва

Православная молитва ПСИХОЛОГИЧЕСКИЙ ВЕСТНИК

ПСИХОЛОГИЧЕСКИЙ ВЕСТНИК ИТОГИ РАБОТЫ ЗА 2011 ГОД

ИТОГИ РАБОТЫ ЗА 2011 ГОД Об утверждении положения о порядке реализации правотворческой инициативы граждан в муниципальном образовании Северодвинск

Об утверждении положения о порядке реализации правотворческой инициативы граждан в муниципальном образовании Северодвинск Орнамент

Орнамент Презентация на тему А нужен ли Калгон?

Презентация на тему А нужен ли Калгон?