Содержание

- 2. СБИС разработки МЦСТ Процессоры SPARC (RISC) 3-х поколений МЦСТ-R1000: 1ГГц, 4 ядра SPARC V9 Процессоры Эльбрус

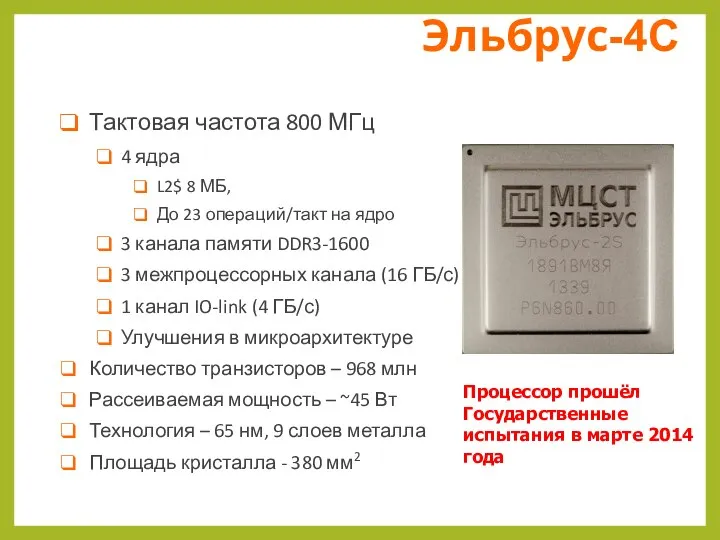

- 3. Процессор прошёл Государственные испытания в марте 2014 года Тактовая частота 800 МГц 4 ядра L2$ 8

- 4. Процессор завершил гос. испытания в 2014 году Тактовая частота 300 МГц, 2 ядра «Эльбрус» L2$ 2

- 5. КПИ Тактовая частота – 250 МГц 2 канала I/O (2 * 1 ГБ/с). Интерфейсы PCI Express

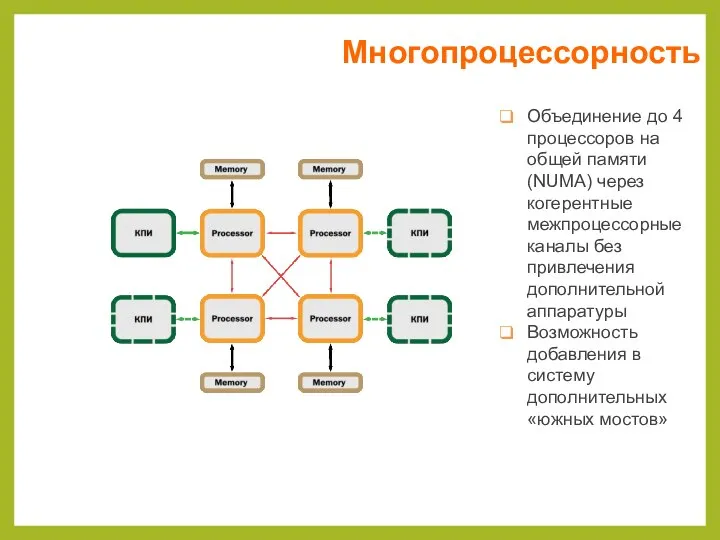

- 6. Многопроцессорность Объединение до 4 процессоров на общей памяти (NUMA) через когерентные межпроцессорные каналы без привлечения дополнительной

- 7. Структура м/п Эльбрус

- 8. Асинхронная предподкачка

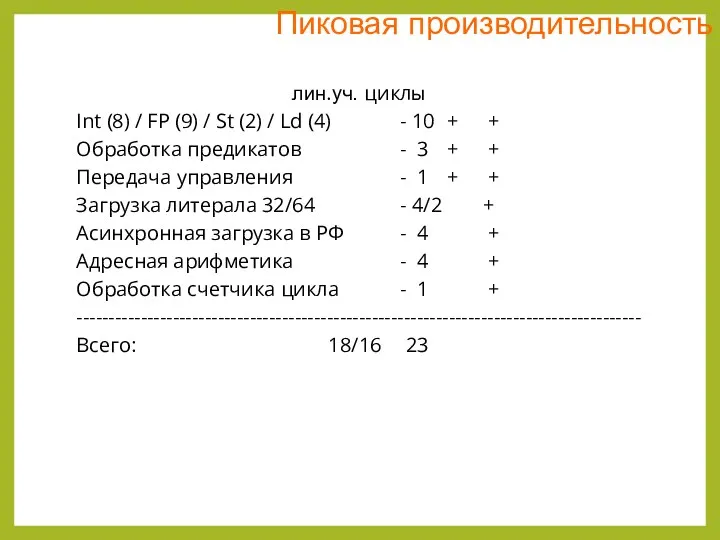

- 9. Пиковая производительность лин.уч. циклы Int (8) / FP (9) / St (2) / Ld (4) -

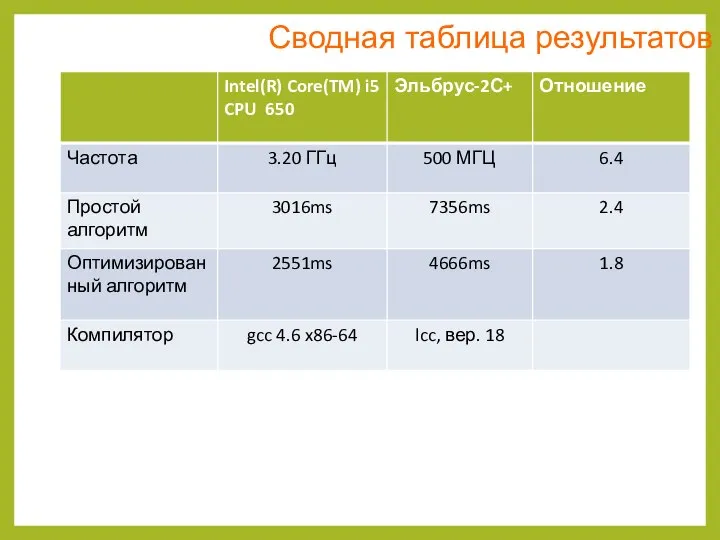

- 10. Сводная таблица результатов

- 11. ВК на базе МП Эльбрус

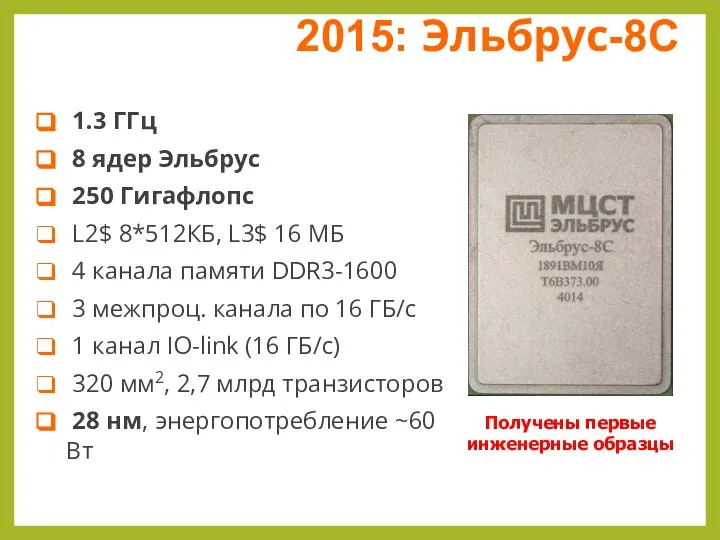

- 12. 2015: Эльбрус-8С 1.3 ГГц 8 ядер Эльбрус 250 Гигафлопс L2$ 8*512КБ, L3$ 16 МБ 4 канала

- 13. 2015: КПИ-2 1 канал IO-link (16 ГБ/с) PCI Express 2.0 x20 3 * Gigabit Ethernet 8

- 14. Сервер на базе четырёх процессоров Эльбрус-8С 4 процессора Эльбрус-8С Южный мост КПИ-2 Оперативная память до 256

- 15. 2014 2015 2016 2017 2018 2019 2020 2021 10 100 1000 Gflops SP TSMC Микрон Эльбрус-16С

- 16. Ошибки и уязвимости Распределение уязвимостей АСУ ТП по типам Отчёт «Безопасность промышленных систем в цифрах v2.1»,

- 17. Память приложения

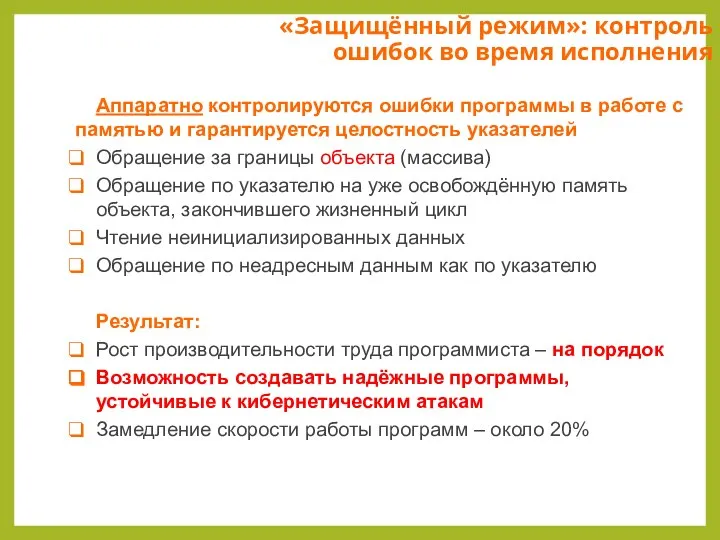

- 18. «Защищённый режим»: контроль ошибок во время исполнения Аппаратно контролируются ошибки программы в работе с памятью и

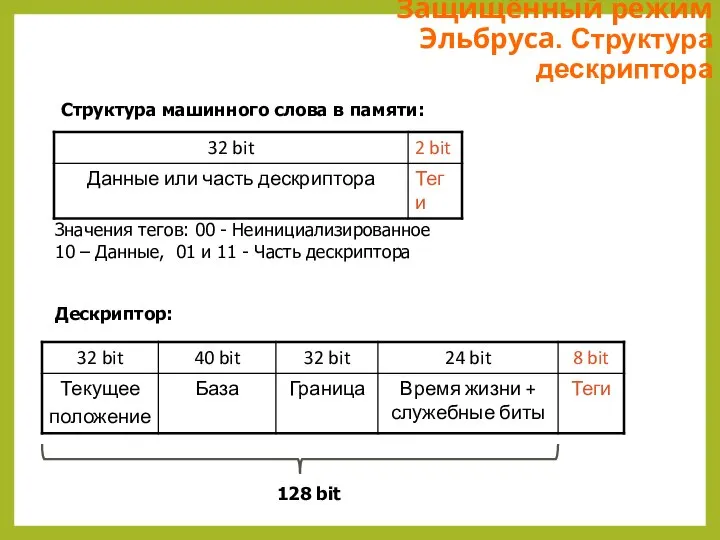

- 19. Защищённый режим Эльбруса. Структура дескриптора 128 bit Дескриптор: Значения тегов: 00 - Неинициализированное 10 – Данные,

- 20. Защищённый режим Эльбруса. Использование дескриптора

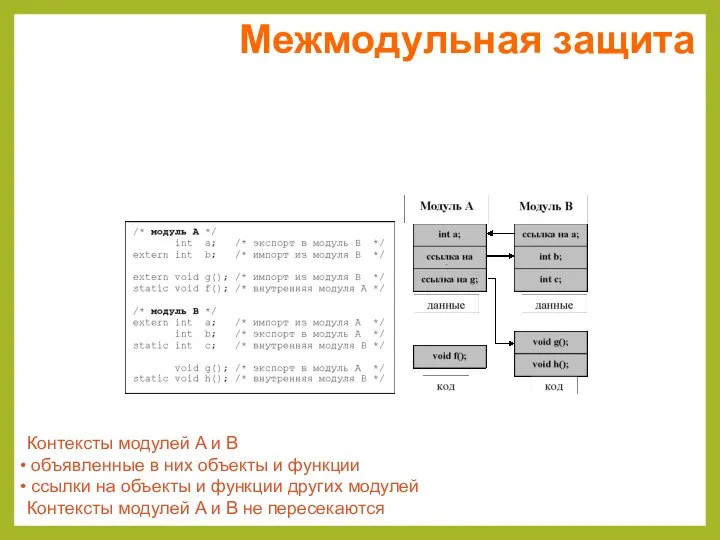

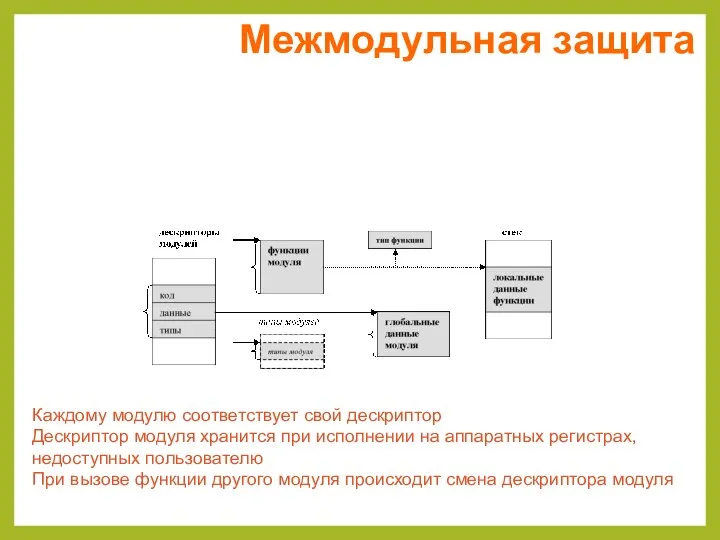

- 21. Контексты модулей A и B объявленные в них объекты и функции ссылки на объекты и функции

- 22. Каждому модулю соответствует свой дескриптор Дескриптор модуля хранится при исполнении на аппаратных регистрах, недоступных пользователю При

- 24. Скачать презентацию

Повышенный доход от облигаций: продвинутый курс

Повышенный доход от облигаций: продвинутый курс Игорь Северянин (Игорь Васильевич Лотарёв) 1887-1941

Игорь Северянин (Игорь Васильевич Лотарёв) 1887-1941 Особенности социально-экономического развития ведущих стран глобальной экономики в 1870-1913

Особенности социально-экономического развития ведущих стран глобальной экономики в 1870-1913 Восстановление Арала

Восстановление Арала Гражданские правоотношения

Гражданские правоотношения Лось - лесная корова, волк - хвост палкой

Лось - лесная корова, волк - хвост палкой ОКСЮМОРОН

ОКСЮМОРОН Отражение краткосрочных активов обязательств, доходов и расходов

Отражение краткосрочных активов обязательств, доходов и расходов  BI в облачных вычислениях. SQL Azure Reporting

BI в облачных вычислениях. SQL Azure Reporting Интересные свойства воды

Интересные свойства воды Стили мебели (часть 2)

Стили мебели (часть 2) Московский Кремль (2 класс)

Московский Кремль (2 класс) Presentations_ZS_2022-23

Presentations_ZS_2022-23 Проект «Интересное рисование»

Проект «Интересное рисование» Презентация на тему Объёмная снежинка

Презентация на тему Объёмная снежинка Кредит в США и России

Кредит в США и России ИСС Аюдар Инфо. Информационно-справочная система для бухгалтера коммерческой организации государственного учреждения

ИСС Аюдар Инфо. Информационно-справочная система для бухгалтера коммерческой организации государственного учреждения Психологія брехні та обману

Психологія брехні та обману Уход за одеждой

Уход за одеждой Экстренная помощь в гинекологии

Экстренная помощь в гинекологии  Полевые компьютеры

Полевые компьютеры Мордовские узоры

Мордовские узоры Кавказская война

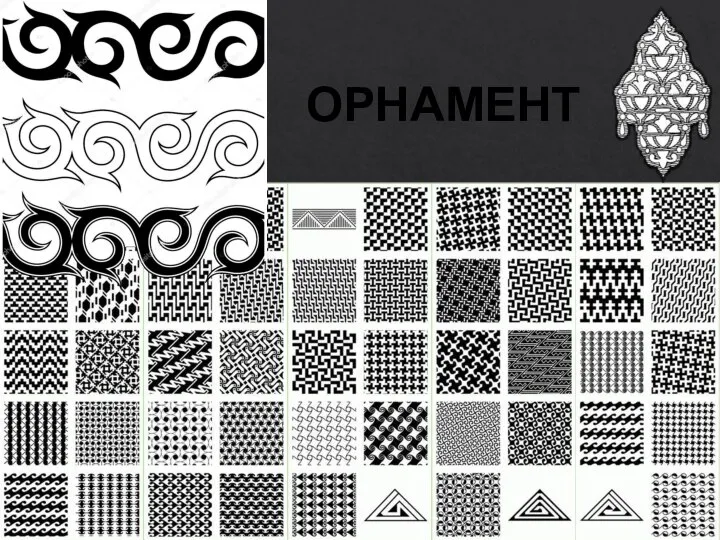

Кавказская война Орнамент: ленточный, сетчатый, композиционно-замкнутый

Орнамент: ленточный, сетчатый, композиционно-замкнутый Открытое акционерное общество «Шестая генерирующая компания оптового рынка электроэнергии» Финансовые и операционные итоги де

Открытое акционерное общество «Шестая генерирующая компания оптового рынка электроэнергии» Финансовые и операционные итоги де Династия Тургелей

Династия Тургелей Оружие нашей армии и противника в начале Великой Отечественной войны.

Оружие нашей армии и противника в начале Великой Отечественной войны. Практиканы АО Костанайский мелькомбинат

Практиканы АО Костанайский мелькомбинат