Содержание

- 2. Логическая ячейка FPGA Cyclone II Рис. 2 – Логическая ячейка FPGA Cyclone II

- 3. Логическая ячейка FPGA Cyclone II Рис. 3 – Логическая ячейка в нормальном режиме

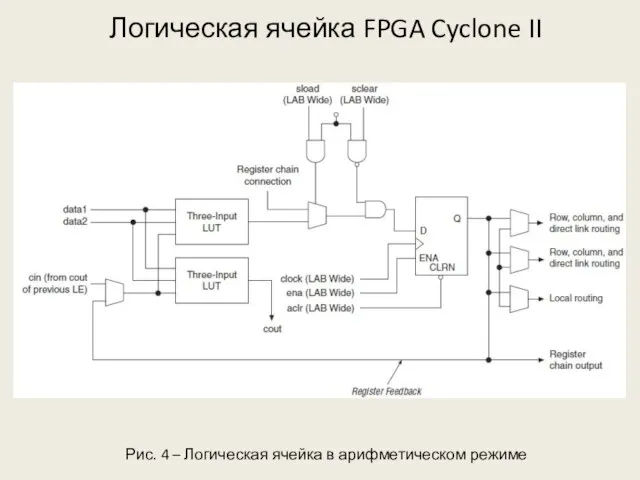

- 4. Логическая ячейка FPGA Cyclone II Рис. 4 – Логическая ячейка в арифметическом режиме

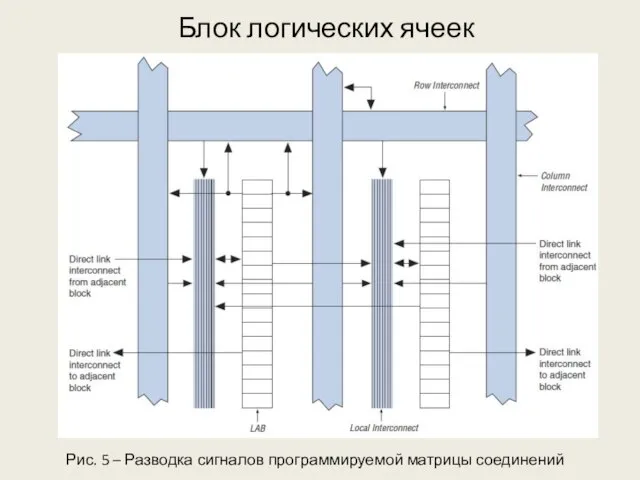

- 5. Блок логических ячеек Рис. 5 – Разводка сигналов программируемой матрицы соединений

- 6. Система синхронизации и PLL Рис.6 – Схема разводки синхросигнала по микросхеме

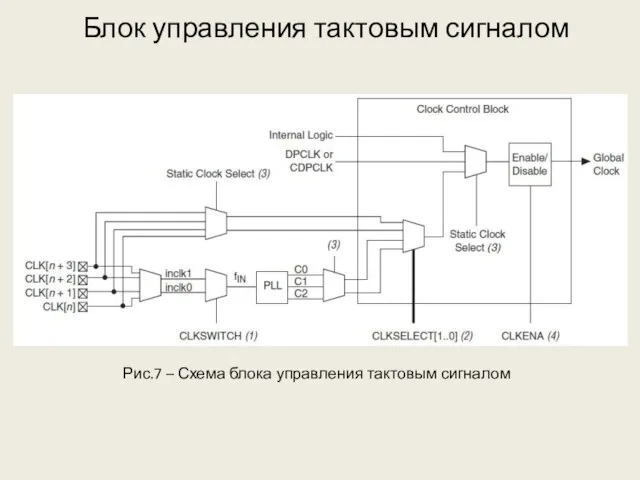

- 7. Блок управления тактовым сигналом Рис.7 – Схема блока управления тактовым сигналом

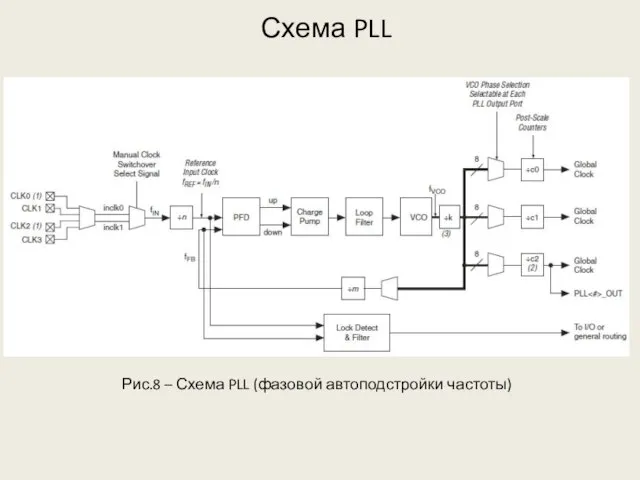

- 8. Схема PLL Рис.8 – Схема PLL (фазовой автоподстройки частоты)

- 9. Встроенные блоки памяти M4K Рис.9 – Подключение блоков памяти к внутренним сигналам

- 10. Встроенный умножитель Рис.10 – Схема встроенных умножителей

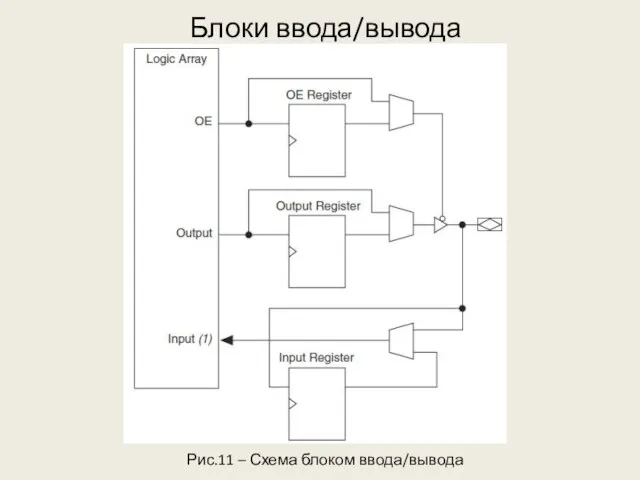

- 11. Блоки ввода/вывода Рис.11 – Схема блоком ввода/вывода

- 12. Банки блоков ввода/вывода Рис.12 – Размещение банков блоков ввода/вывода

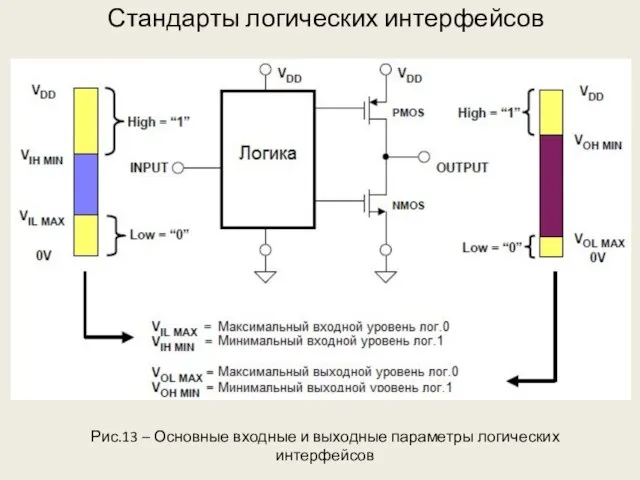

- 13. Стандарты логических интерфейсов Рис.13 – Основные входные и выходные параметры логических интерфейсов

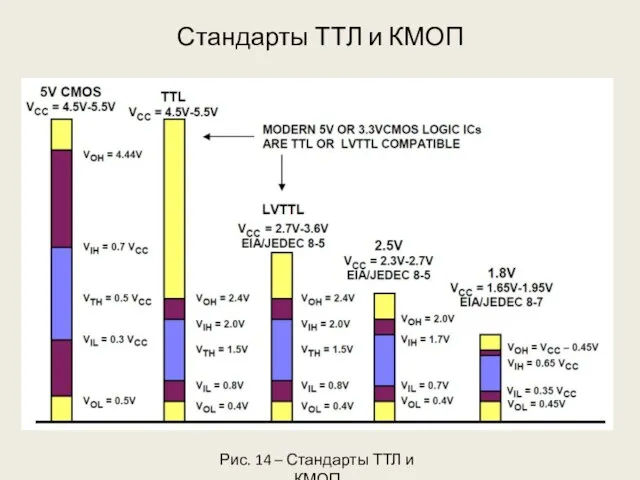

- 14. Стандарты ТТЛ и КМОП Рис. 14 – Стандарты ТТЛ и КМОП

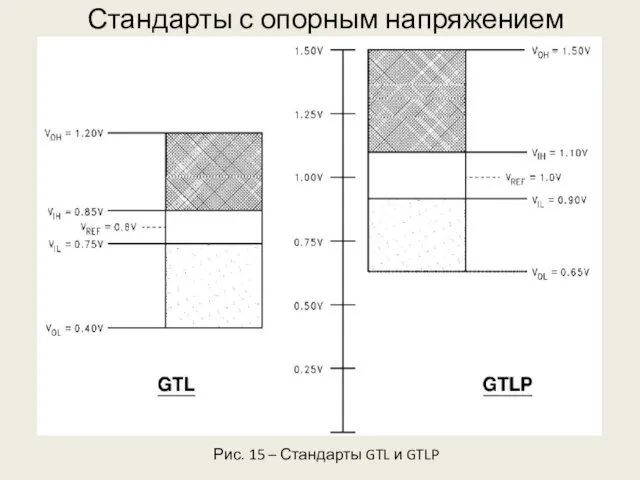

- 15. Стандарты с опорным напряжением Рис. 15 – Стандарты GTL и GTLP

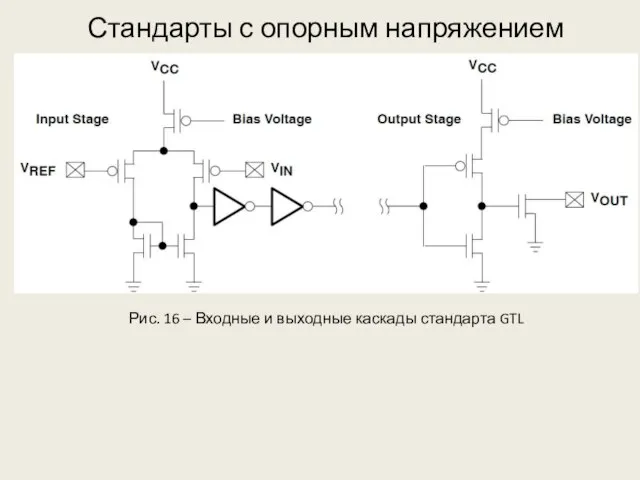

- 16. Стандарты с опорным напряжением Рис. 16 – Входные и выходные каскады стандарта GTL

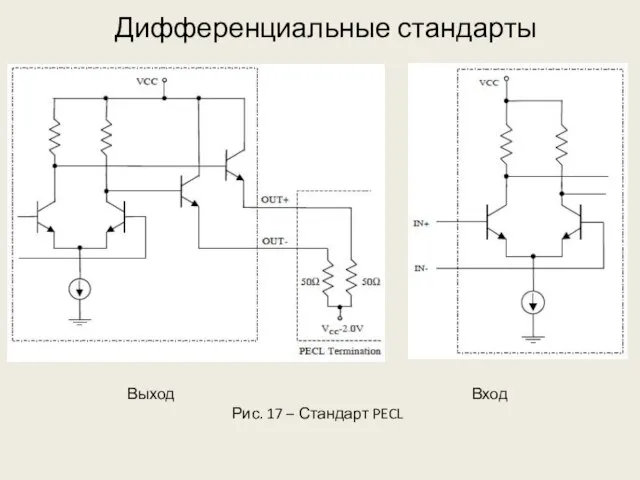

- 17. Дифференциальные стандарты Выход Вход Рис. 17 – Стандарт PECL

- 18. Дифференциальные стандарты Рис. 18 – Соединение приемника и передатчика PECL

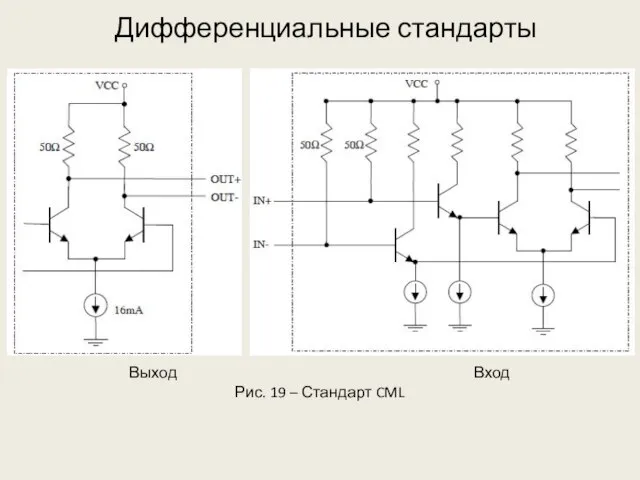

- 19. Дифференциальные стандарты Выход Вход Рис. 19 – Стандарт CML

- 21. Скачать презентацию

Мои права. Имею право…

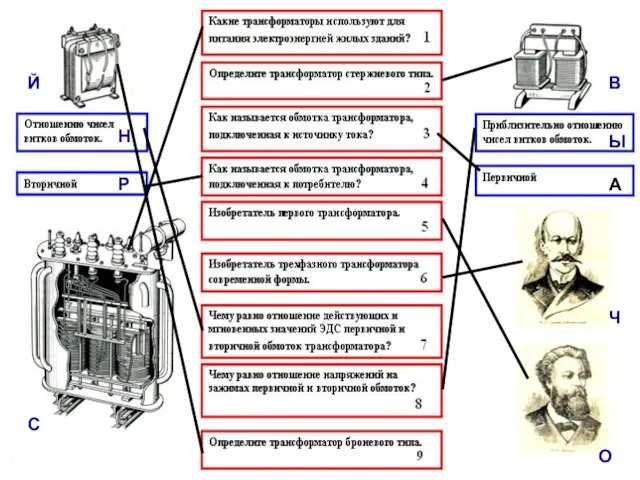

Мои права. Имею право… С В АР О Ч Н Ы Й. Сварочный трансформатор Цель: повторить устройство трансформатора; выяснить в чем особенность сварочного трансфор

С В АР О Ч Н Ы Й. Сварочный трансформатор Цель: повторить устройство трансформатора; выяснить в чем особенность сварочного трансфор ЭМОЦИИ И ЗДОРОВЬЕ

ЭМОЦИИ И ЗДОРОВЬЕ Java Enterprise обучение, работа, перспективы

Java Enterprise обучение, работа, перспективы Временное жилище летом

Временное жилище летом Немного о себе

Немного о себе 1 июня - День защиты детей

1 июня - День защиты детей Procrastination and intellectual level

Procrastination and intellectual level Социальное партнерство в сфере воспитания

Социальное партнерство в сфере воспитания Законы и другие нормативно-правовые акты по организации безопасности в условиях ЧС

Законы и другие нормативно-правовые акты по организации безопасности в условиях ЧС Квартирная проводка

Квартирная проводка Информационная политика Правительства Кировской области февраль 2010

Информационная политика Правительства Кировской области февраль 2010 Устройство и содержание бесстыкового пути ОАО РЖД

Устройство и содержание бесстыкового пути ОАО РЖД OOO «Пандора Аутленд» – ваш проводник в мире техники

OOO «Пандора Аутленд» – ваш проводник в мире техники Уникальный летний культурно-исторический лагерь Ұлы дала жастары

Уникальный летний культурно-исторический лагерь Ұлы дала жастары Профессиональная компетентность педагога

Профессиональная компетентность педагога Предложение на комплексную поставку оборудования и выполнение работ (EPC) по проекту строительства обогатительной фабрики

Предложение на комплексную поставку оборудования и выполнение работ (EPC) по проекту строительства обогатительной фабрики ЦО №1748 «Вертикаль»

ЦО №1748 «Вертикаль» Методические рекомендациипо использованию метода проектовдля изучения темы«Виды рекламной фотосъемки»

Методические рекомендациипо использованию метода проектовдля изучения темы«Виды рекламной фотосъемки» О

О J’aime et je n’aime pas...

J’aime et je n’aime pas... Николай Васильеви ч Гоголь (1809 — 1852)

Николай Васильеви ч Гоголь (1809 — 1852)  Вкусные украшения для праздника

Вкусные украшения для праздника Вознесенская райгосадминистрация

Вознесенская райгосадминистрация Светодиодные светильники

Светодиодные светильники Стратегия развития современных технологий мобильной связи на Дальнем Востоке и в Восточной Сибири

Стратегия развития современных технологий мобильной связи на Дальнем Востоке и в Восточной Сибири Презентация на тему Степень с целым показателем 8 класс

Презентация на тему Степень с целым показателем 8 класс  Путь к моей мечте

Путь к моей мечте