Содержание

- 2. Постановка задач: Как компьютер выполняет арифметические действия? Как устроен его «ум»? Как компьютер запоминает информацию? Какова

- 3. ПОЛУСУММАТОР И в двоичной системе счисления и в алгебре логики информация представлена в виде двоичных кодов.

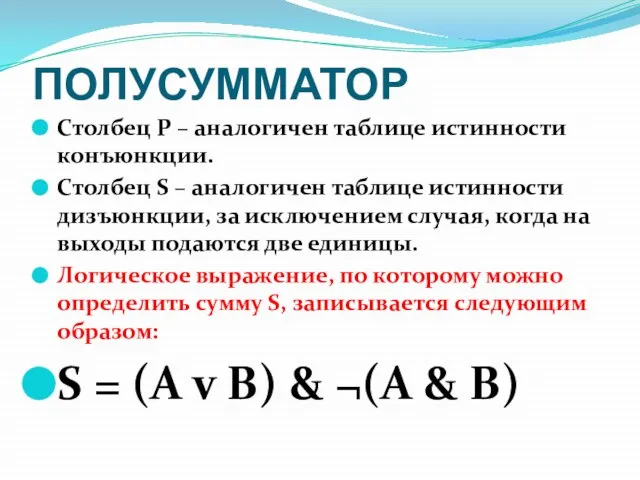

- 4. ПОЛУСУММАТОР Столбец P – аналогичен таблице истинности конъюнкции. Столбец S – аналогичен таблице истинности дизъюнкции, за

- 5. ПОЛУСУММАТОР Построим к этому логическому выражению логическую схему: Полученная нами схема выполняет сложение двоичных одноразрядных чисел

- 6. СУММАТОР Более «умным» является устройство, которое при сложении учитывает перенос из младшего разряда. Называется оно полный

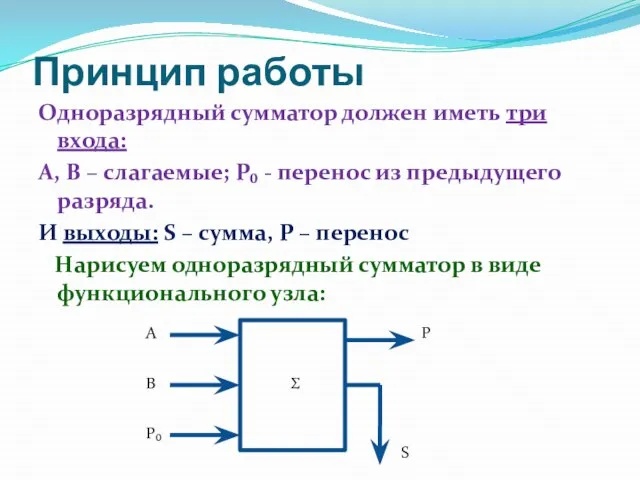

- 7. Принцип работы Одноразрядный сумматор должен иметь три входа: А, В – слагаемые; Р₀ - перенос из

- 8. Многоразрядный сумматор Но процессор, как правило складывает многоразрядные двоичные числа. Для того, чтобы вычислить сумму n-разрядных

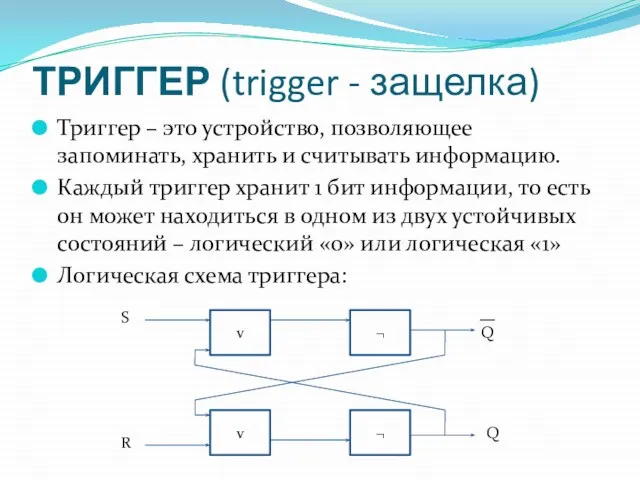

- 9. ТРИГГЕР (trigger - защелка) Триггер – это устройство, позволяющее запоминать, хранить и считывать информацию. Каждый триггер

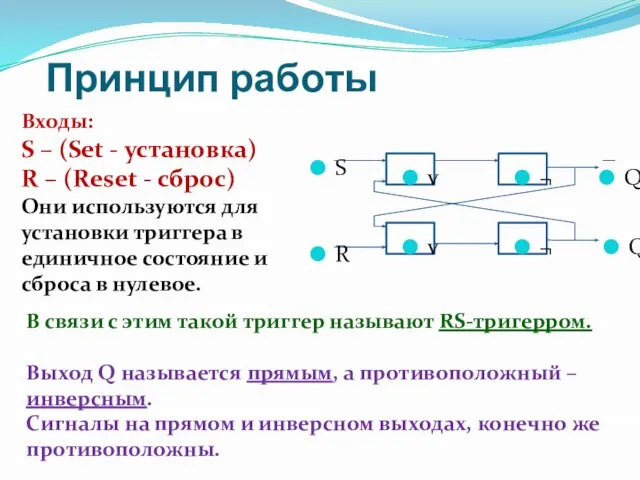

- 10. Принцип работы Входы: S – (Set - установка) R – (Reset - сброс) Они используются для

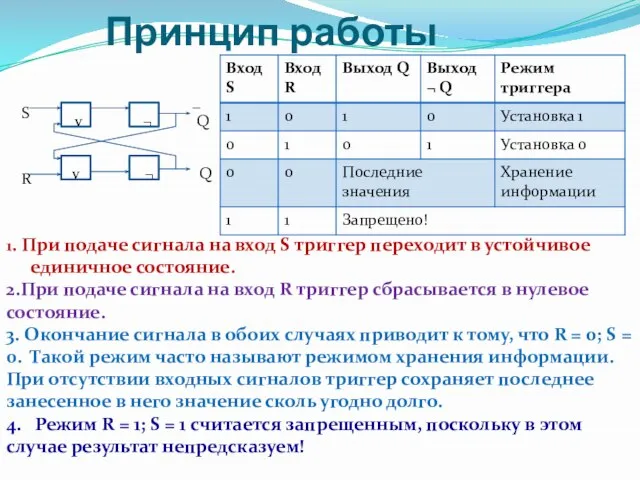

- 11. Принцип работы 1. При подаче сигнала на вход S триггер переходит в устойчивое единичное состояние. 2.При

- 12. РЕГИСТР Так как триггер может хранить только 1 бит информации, то несколько триггеров объединяют вместе. Полученное

- 14. Скачать презентацию

МАРКЕТИНГ

МАРКЕТИНГ Химия в медицине

Химия в медицине 0006d06c-2b7ab0fb

0006d06c-2b7ab0fb Орёл на горе, перо на орле.Гора под орлом,орёл под пером.

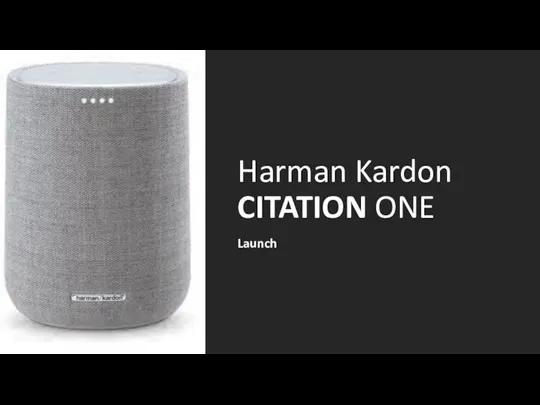

Орёл на горе, перо на орле.Гора под орлом,орёл под пером. Citation One бриф (002)

Citation One бриф (002) Средняя линия трапеции

Средняя линия трапеции Транспортные запасы

Транспортные запасы Архитектура и дизайн

Архитектура и дизайн Презентация на тему Политическая мысль древнего востока

Презентация на тему Политическая мысль древнего востока  Prezentatsia___po_Istorii_Uratkina_Mikhaila____4

Prezentatsia___po_Istorii_Uratkina_Mikhaila____4 Материнские платы

Материнские платы Click to edit Master title style Click to edit Master subtitle style

Click to edit Master title style Click to edit Master subtitle style  - программастратегического назначения

- программастратегического назначения Аз, буки, веди (из истории русского алфавита)

Аз, буки, веди (из истории русского алфавита) Презентация на тему БИОЛОГИЯ РАСТЕНИЯ

Презентация на тему БИОЛОГИЯ РАСТЕНИЯ  Презентация на тему Гравитация

Презентация на тему Гравитация Презентация на тему Welcome to Australia

Презентация на тему Welcome to Australia  Презентация школьной библиотеки

Презентация школьной библиотеки The National Parks in Great Britain

The National Parks in Great Britain Традиции, парадигмы и споры в теории международных отношений

Традиции, парадигмы и споры в теории международных отношений Применение механизма Совместного Осуществления Киотского Протокола для организации финансирования проекта по использованию др

Применение механизма Совместного Осуществления Киотского Протокола для организации финансирования проекта по использованию др Театральный коллектив Маски

Театральный коллектив Маски Биография Чарльза Дарвина

Биография Чарльза Дарвина Аппликация «Собачка»

Аппликация «Собачка» Пираньи. Речные монстры

Пираньи. Речные монстры Понятие информации, 10 кл. Семакин ФГОС

Понятие информации, 10 кл. Семакин ФГОС АвтоВАЗ. История завода

АвтоВАЗ. История завода Становись партнером и зарабатывай с продажи билетов

Становись партнером и зарабатывай с продажи билетов