Содержание

- 2. RISC-V-это бесплатная и открытая ISA, открывающая новую эру инноваций процессоров благодаря открытому стандартному. RISC-V ISA обеспечивает

- 3. Спецификация доступна для свободного и бесплатного использования, включая коммерческие реализации непосредственно в кремнии или конфигурировании ПЛИС.

- 11. Микроконтроллеры, выпущенные в 2020 году: ONiO: ONiO.zero (16/32 бита, 1 кБ ПЗУ, 2 кБ ОЗУ, 8/16/32

- 12. IP-ядра[править | править код] Ряд компаний предлагают готовые блоки IP-ядер на базе архитектуры RISC-V, среди них:

- 15. 64-битное ядро RISC-V с 32-мя целочисленными регистрами (I расширение) Целочисленное умножение и деление (M расширение). Атомарные

- 25. Скачать презентацию

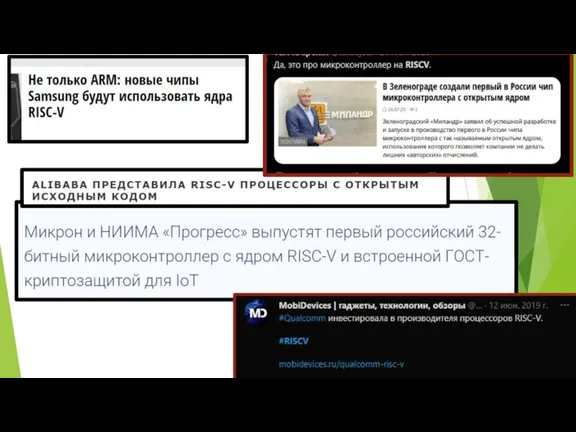

Слайд 2RISC-V-это бесплатная и открытая ISA, открывающая новую эру инноваций процессоров благодаря открытому

RISC-V-это бесплатная и открытая ISA, открывающая новую эру инноваций процессоров благодаря открытому

стандартному. RISC-V ISA обеспечивает новый уровень свободной, расширяемой программной и аппаратной свободы в архитектуре, прокладывая путь для следующих 50 лет вычислительного дизайна и инноваций.

Слайд 3Спецификация доступна для свободного и бесплатного использования, включая коммерческие реализации непосредственно в кремнии или

Спецификация доступна для свободного и бесплатного использования, включая коммерческие реализации непосредственно в кремнии или

конфигурировании ПЛИС. Имеет встроенные возможности для расширения списка команд и подходит для широкого круга применений.

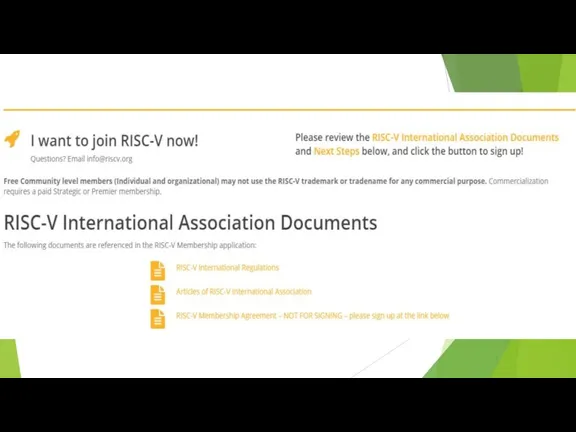

Создана в 2010 году исследователями из отделения информатики Калифорнийского университета в Беркли при непосредственном участии Дэвида Паттерсона[2][3]. Для развития и продвижения RISC-V в 2015 году создан международный фонд RISC-V[4] и ассоциация со штаб-квартирой в Цюрихе[5]; с 2018 года RISC-V Foundation работает в тесном партнёрстве с The Linux Foundation.

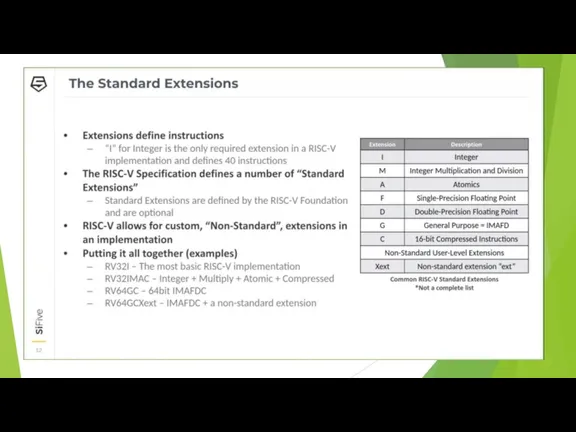

Стандарт RISC-V определяет сравнительно небольшое число стандартных инструкций, около 50 штук, многие из которых были типичны ещё для ранних RISC-I 1980 года. Стандартные расширения (M, A, F и D) расширяют набор на 53 инструкции, сжатый формат C определяет 34 команды. Используется 6 типов кодирования инструкций (форматов).

Создана в 2010 году исследователями из отделения информатики Калифорнийского университета в Беркли при непосредственном участии Дэвида Паттерсона[2][3]. Для развития и продвижения RISC-V в 2015 году создан международный фонд RISC-V[4] и ассоциация со штаб-квартирой в Цюрихе[5]; с 2018 года RISC-V Foundation работает в тесном партнёрстве с The Linux Foundation.

Стандарт RISC-V определяет сравнительно небольшое число стандартных инструкций, около 50 штук, многие из которых были типичны ещё для ранних RISC-I 1980 года. Стандартные расширения (M, A, F и D) расширяют набор на 53 инструкции, сжатый формат C определяет 34 команды. Используется 6 типов кодирования инструкций (форматов).

Слайд 11Микроконтроллеры, выпущенные в 2020 году:

ONiO: ONiO.zero (16/32 бита, 1 кБ ПЗУ, 2

Микроконтроллеры, выпущенные в 2020 году:

ONiO: ONiO.zero (16/32 бита, 1 кБ ПЗУ, 2

кБ ОЗУ, 8/16/32 кБ ППЗУ, 1-24 МГц, 0,36-1,44 Вт, встроенный радиоэлектро генератор на 800/900/1800/1900/2400 МГц) BLE, 802.15.4 UWB[44][45]

WCH: CH32V103 (32 бита, 10/20КБ ОЗУ, 32/64 КБ ППЗУ, до 80 МГц, корпуса LQFP48, QFN48 или LQFP64)[46] универсальный контроллер с USB 2.0, SPI, I2C, GPIO, USART, TouchKey, RTC, TIM, ADC

Миландр: К1986ВК025 (32-битное ядро BМ-310S CloudBEAR, ОЗУ 112 Кбайт, ППЗУ 256+8 Кбайт, ПЗУ 16 Кбайт, 60 МГц, сопроцессоров для шифров «Кузнечик», «Магма» и AES, корпус QFN88 10 х 10 мм)

Espressif: ESP32-C3 (32-битное ядро RV32IMC, 400 Кбайт SRAM, 384 Кбайт ПЗУ, 160 МГц, Wi-Fi, Bluetooth LE 5.0, по контактам совместим с ESP8266)[47]

Bouffalo Lab: BL602 и BL604 (32-битный, динамическая частота от 1 МГц до 192 МГц, 276 КБ SRAM, 128 КБ ПЗУ, Wi-Fi, Bluetooth LE)[48]

Cmsemicon: ANT32RV56xx (ядро RV32EC, 48 МГц, 32+8 Кбайт SRAM, 64 Кбайт)[49]

WCH: CH32V103 (32 бита, 10/20КБ ОЗУ, 32/64 КБ ППЗУ, до 80 МГц, корпуса LQFP48, QFN48 или LQFP64)[46] универсальный контроллер с USB 2.0, SPI, I2C, GPIO, USART, TouchKey, RTC, TIM, ADC

Миландр: К1986ВК025 (32-битное ядро BМ-310S CloudBEAR, ОЗУ 112 Кбайт, ППЗУ 256+8 Кбайт, ПЗУ 16 Кбайт, 60 МГц, сопроцессоров для шифров «Кузнечик», «Магма» и AES, корпус QFN88 10 х 10 мм)

Espressif: ESP32-C3 (32-битное ядро RV32IMC, 400 Кбайт SRAM, 384 Кбайт ПЗУ, 160 МГц, Wi-Fi, Bluetooth LE 5.0, по контактам совместим с ESP8266)[47]

Bouffalo Lab: BL602 и BL604 (32-битный, динамическая частота от 1 МГц до 192 МГц, 276 КБ SRAM, 128 КБ ПЗУ, Wi-Fi, Bluetooth LE)[48]

Cmsemicon: ANT32RV56xx (ядро RV32EC, 48 МГц, 32+8 Кбайт SRAM, 64 Кбайт)[49]

Слайд 12IP-ядра[править | править код]

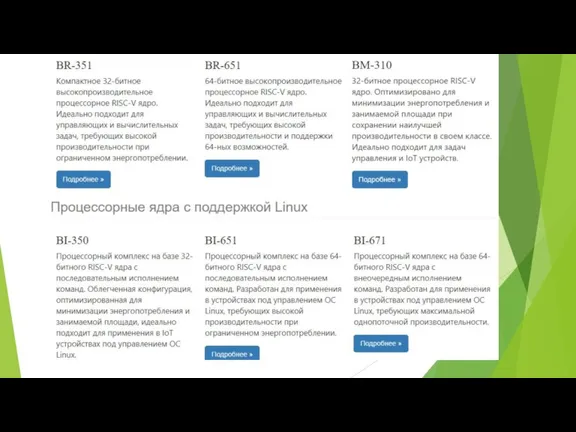

Ряд компаний предлагают готовые блоки IP-ядер на базе архитектуры RISC-V, среди них:

ECHX1 —

IP-ядра[править | править код]

Ряд компаний предлагают готовые блоки IP-ядер на базе архитектуры RISC-V, среди них:

ECHX1 —

![IP-ядра[править | править код] Ряд компаний предлагают готовые блоки IP-ядер на базе](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1146900/slide-11.jpg)

компания Western Digital (США),

Rocket — Калифорнийский университет в Беркли и компания SiFive (США),

ORCA — компания Vectorblox (Канада),

PULPino — Высшая техническая школа Цюриха (Швейцария) и Болонский университет (Италия),

Hummingbird E200 — компания Nuclei System Technology (Китай),

AndeStar V5 — компания Andes Technology (Тайвань)[15]),

Shakti — Индийский технологический институт в Мадрасе (Индия),

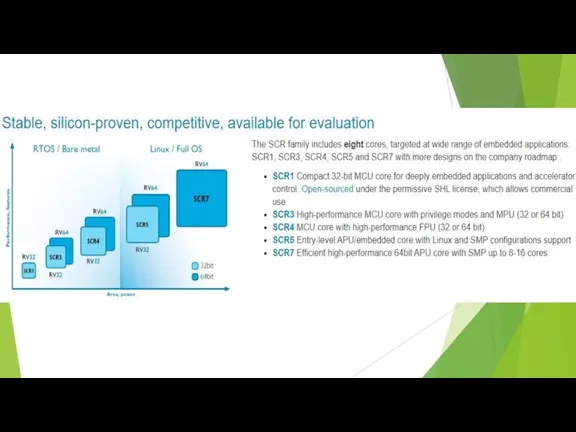

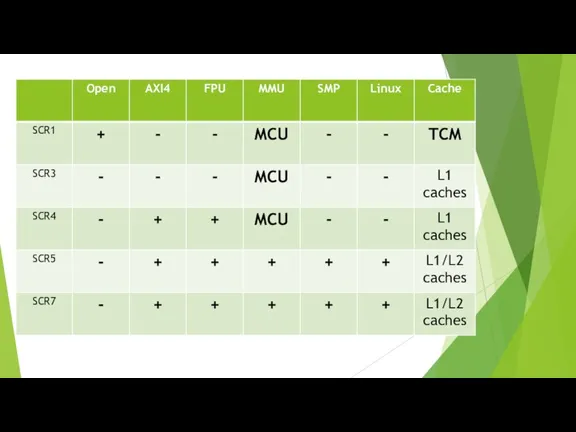

BM-310, BI-350, BI-651, BI-671 — компания Клаудбеар (Россия),

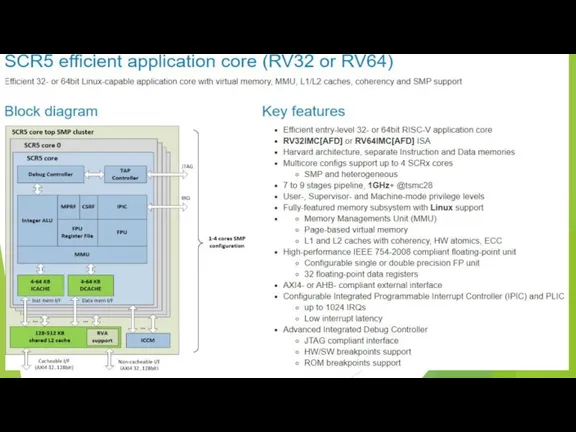

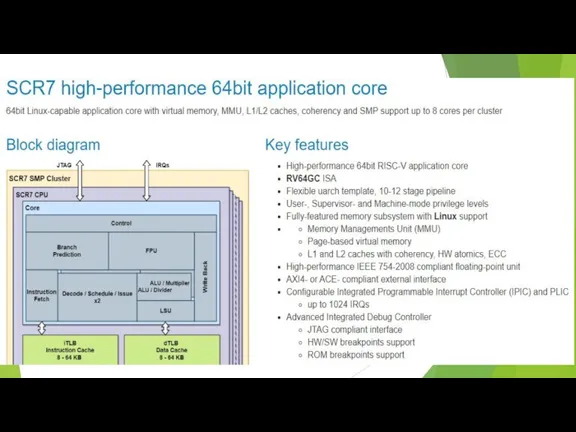

Семейство SCR компании Синтакор (Россия)[16].

Rocket — Калифорнийский университет в Беркли и компания SiFive (США),

ORCA — компания Vectorblox (Канада),

PULPino — Высшая техническая школа Цюриха (Швейцария) и Болонский университет (Италия),

Hummingbird E200 — компания Nuclei System Technology (Китай),

AndeStar V5 — компания Andes Technology (Тайвань)[15]),

Shakti — Индийский технологический институт в Мадрасе (Индия),

BM-310, BI-350, BI-651, BI-671 — компания Клаудбеар (Россия),

Семейство SCR компании Синтакор (Россия)[16].

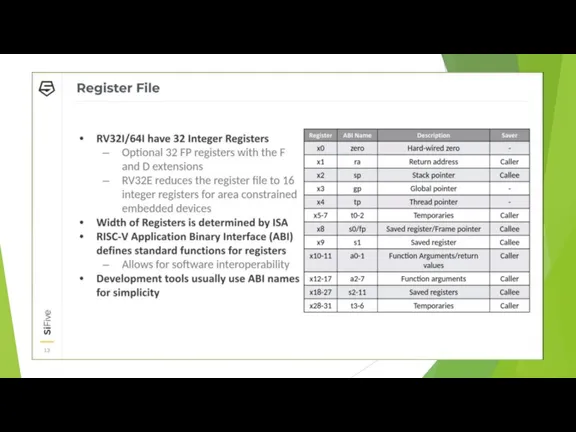

Слайд 1564-битное ядро RISC-V с 32-мя целочисленными регистрами (I расширение)

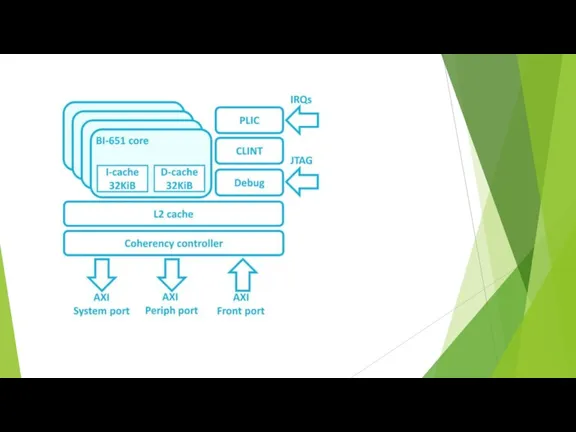

Целочисленное умножение и деление

64-битное ядро RISC-V с 32-мя целочисленными регистрами (I расширение)

Целочисленное умножение и деление

(M расширение). Атомарные операции (A расширение)

16-битные инструкции для увеличения плотности кода (C расширение)

IEEE 754-2008 совместимые вычисления с плавающей запятой (F+D расширения)

Исполнение до 2-х инструкций в такт. До 4-х ядер в комплексе

Machine, Supervisor и User уровни привилегированности

9-ти стадийный конвейер с последовательным исполнением команд

Предсказание переходов: BTB, BHT, RAS. Sv39 режим виртуальной памяти

32 КБ 8-канальный L1 кэш инструкций. 32 КБ 8-канальный L1 кэш данных. Интегрированный 1-2 МБ L2 кэш

Прерывания:

Platform Level Interrupt Controller (PLIC): 127 прерываний с 8-ю уровнями приоритета

Multi-Core Local Interruptor (CLINT): таймер и программные прерывания

Контроль доступа к физической памяти

Интегрированный контроллер отладки с поддержкой аппаратных точек останова

AXI интерфейс к системной шине. AXI интерфейс к периферийным блокам.AXI порт для когерентного доступа ускорителей

Производительность: 2.5 DMIPS/МГц, 5.0 CoreMark/МГц, 3.18 SPEC2006 INT/ГГц

Частота: 1 ГГц (TSMC, 40нм G, при наихудших условиях),1.2 ГГц (TSMC, 28нм HPC+, при наихудших условиях)

16-битные инструкции для увеличения плотности кода (C расширение)

IEEE 754-2008 совместимые вычисления с плавающей запятой (F+D расширения)

Исполнение до 2-х инструкций в такт. До 4-х ядер в комплексе

Machine, Supervisor и User уровни привилегированности

9-ти стадийный конвейер с последовательным исполнением команд

Предсказание переходов: BTB, BHT, RAS. Sv39 режим виртуальной памяти

32 КБ 8-канальный L1 кэш инструкций. 32 КБ 8-канальный L1 кэш данных. Интегрированный 1-2 МБ L2 кэш

Прерывания:

Platform Level Interrupt Controller (PLIC): 127 прерываний с 8-ю уровнями приоритета

Multi-Core Local Interruptor (CLINT): таймер и программные прерывания

Контроль доступа к физической памяти

Интегрированный контроллер отладки с поддержкой аппаратных точек останова

AXI интерфейс к системной шине. AXI интерфейс к периферийным блокам.AXI порт для когерентного доступа ускорителей

Производительность: 2.5 DMIPS/МГц, 5.0 CoreMark/МГц, 3.18 SPEC2006 INT/ГГц

Частота: 1 ГГц (TSMC, 40нм G, при наихудших условиях),1.2 ГГц (TSMC, 28нм HPC+, при наихудших условиях)

- Предыдущая

Спец. военный Вестник газеты Земля России № 31Следующая -

Что такое творческий проект

День матери

День матери ALTAI_STATE_UNIVERSITY

ALTAI_STATE_UNIVERSITY Карьера

Карьера Спорт в борьбе со СПИДом

Спорт в борьбе со СПИДом Презентация по родному русскому языку _Во что одевались в старину_, 1 урок

Презентация по родному русскому языку _Во что одевались в старину_, 1 урок Презентация на тему Птицеводство

Презентация на тему Птицеводство  Деятельностный подход. Методологические функции деятельности

Деятельностный подход. Методологические функции деятельности Подсистема «Судебное делопроизводство» Программный комплекс “Судебно-арбитражное делопроизводство”

Подсистема «Судебное делопроизводство» Программный комплекс “Судебно-арбитражное делопроизводство” Девиантное поведение

Девиантное поведение Памятники деревянного зодчества в Марийском крае.

Памятники деревянного зодчества в Марийском крае. Презентация на тему Символика Древнего Египта

Презентация на тему Символика Древнего Египта Презентация на тему Паразитизм

Презентация на тему Паразитизм Числительные в Английском Языке

Числительные в Английском Языке Презентация на тему Обобщение знаний о падежах

Презентация на тему Обобщение знаний о падежах  Коллективизация сельского хозяйства в СССР

Коллективизация сельского хозяйства в СССР Презентация на тему День науки 1 класс

Презентация на тему День науки 1 класс Деньги и их функции. Инфляция и ее виды. Денежно-кредитная политика государства

Деньги и их функции. Инфляция и ее виды. Денежно-кредитная политика государства Финансовое планирование в организации. Тема 9

Финансовое планирование в организации. Тема 9 Растения

Растения Презентация на тему Пакистан

Презентация на тему Пакистан Как найти свою сильную сторону и развить творческое мышление

Как найти свою сильную сторону и развить творческое мышление Новые ниши и быстроразвивающиеся сегменты Интернет-торговли Никита Алферов Руководитель системы Метамаркет, - презентация

Новые ниши и быстроразвивающиеся сегменты Интернет-торговли Никита Алферов Руководитель системы Метамаркет, - презентация Природные условия Ярославской области

Природные условия Ярославской области Презентация на тему Парад Победы в истории Отечества и моей семьи

Презентация на тему Парад Победы в истории Отечества и моей семьи Conjugación

Conjugación Цель Укрепление корпоративной культуры и традиций лицея, содружества и единства поколений выпускников, лицеистов и педагогов

Цель Укрепление корпоративной культуры и традиций лицея, содружества и единства поколений выпускников, лицеистов и педагогов Реализация национального проекта в сфере здравоохранения в Санкт-Петербурге

Реализация национального проекта в сфере здравоохранения в Санкт-Петербурге Добро пожаловать в Ибис Ярославль Центр!

Добро пожаловать в Ибис Ярославль Центр!