Слайд 2Рассматриваемые процессоры

Intel Itanium 2

Intel Core 2 Duo

IBM Cell

Слайд 3Неявный и явный параллелизмы

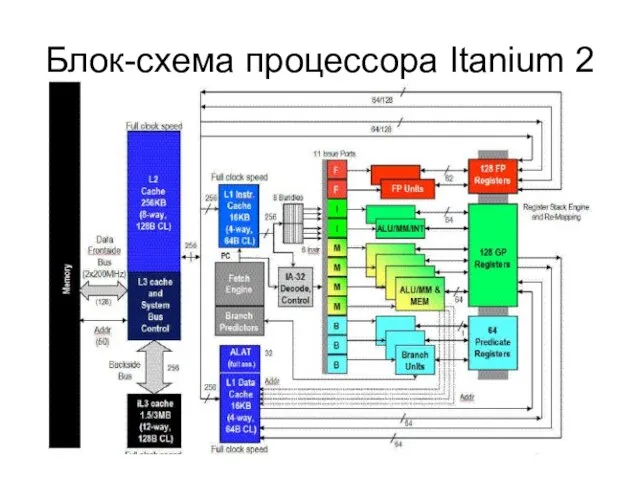

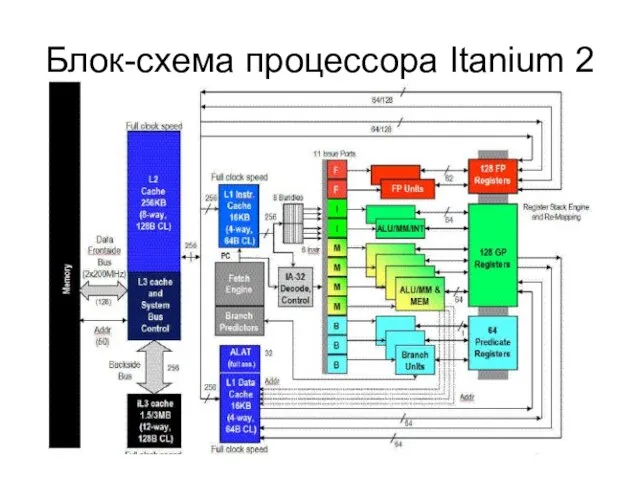

Слайд 4Блок-схема процессора Itanium 2

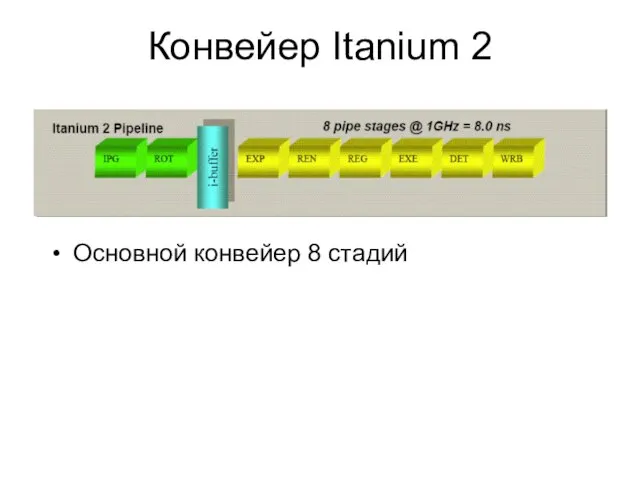

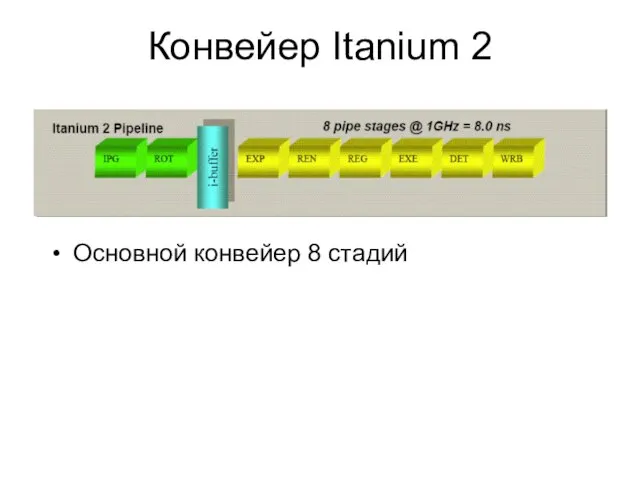

Слайд 6Конвейер Itanium 2

Основной конвейер 8 стадий

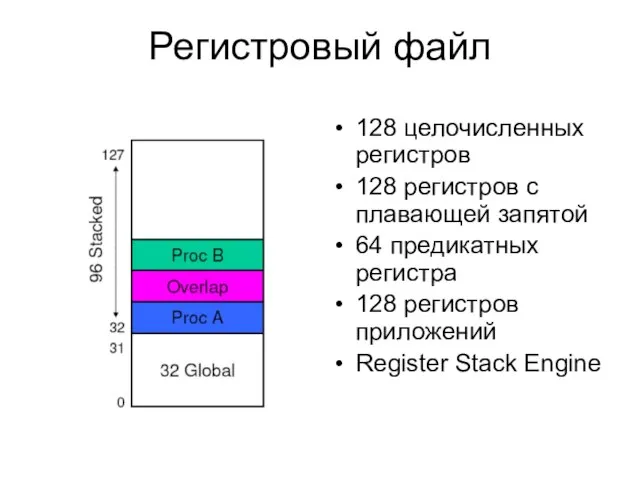

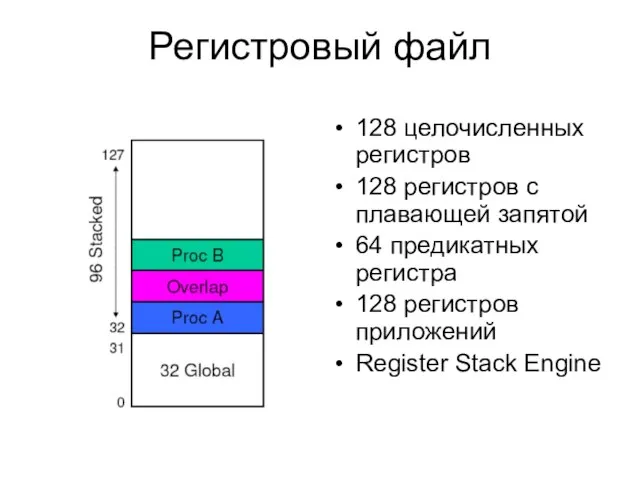

Слайд 7Регистровый файл

128 целочисленных регистров

128 регистров с плавающей запятой

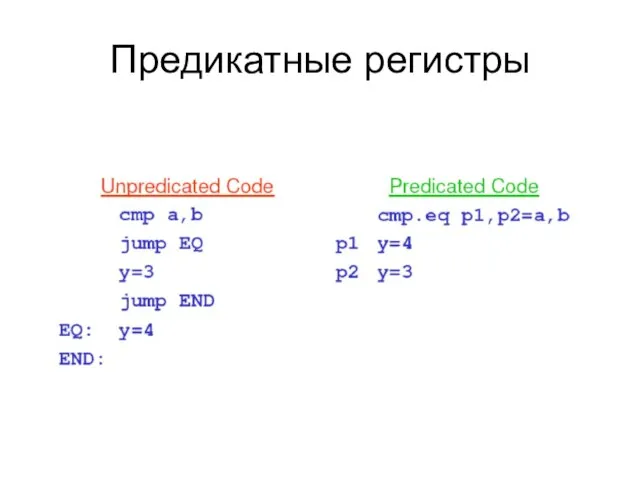

64 предикатных регистра

128 регистров приложений

Register

Stack Engine

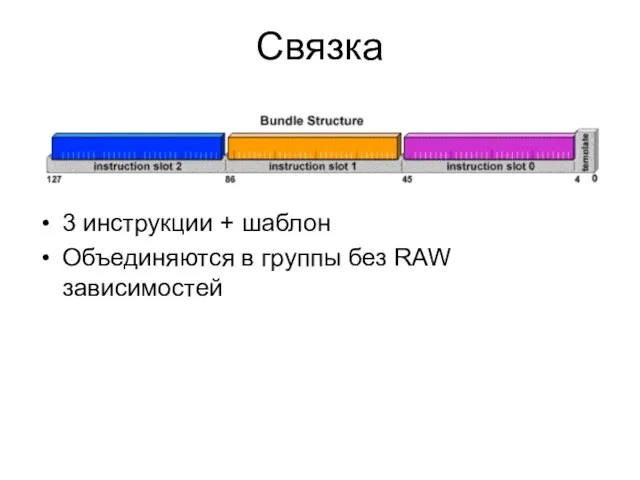

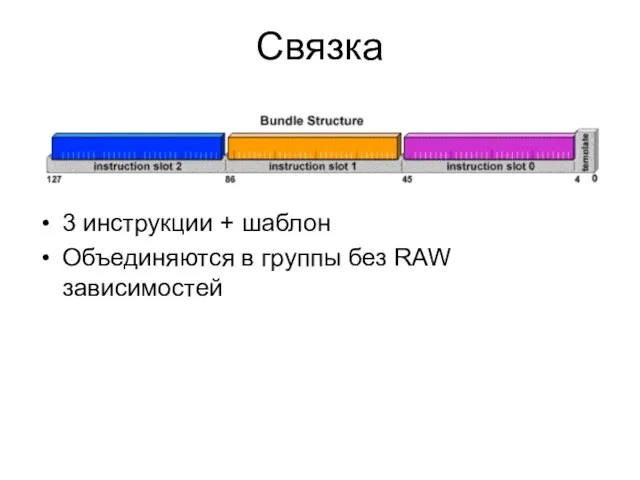

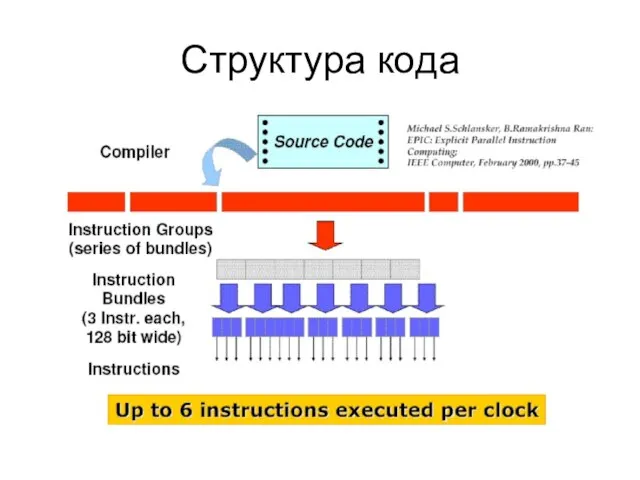

Слайд 8Связка

3 инструкции + шаблон

Объединяются в группы без RAW зависимостей

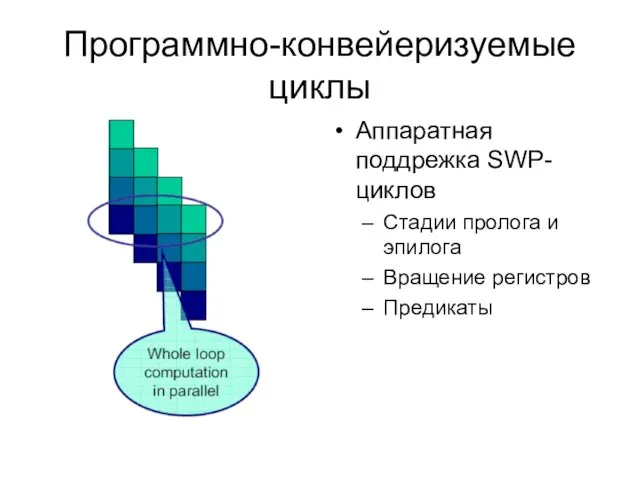

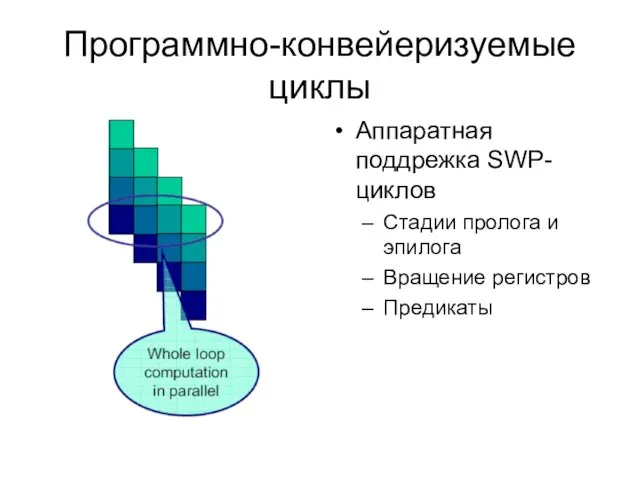

Слайд 11Программно-конвейеризуемые циклы

Аппаратная поддрежка SWP-циклов

Стадии пролога и эпилога

Вращение регистров

Предикаты

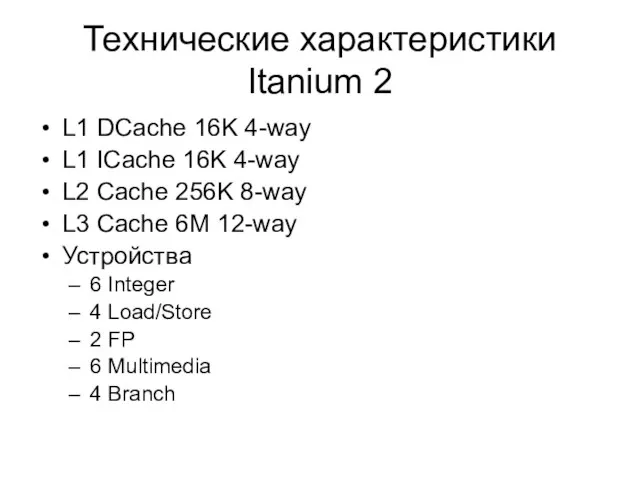

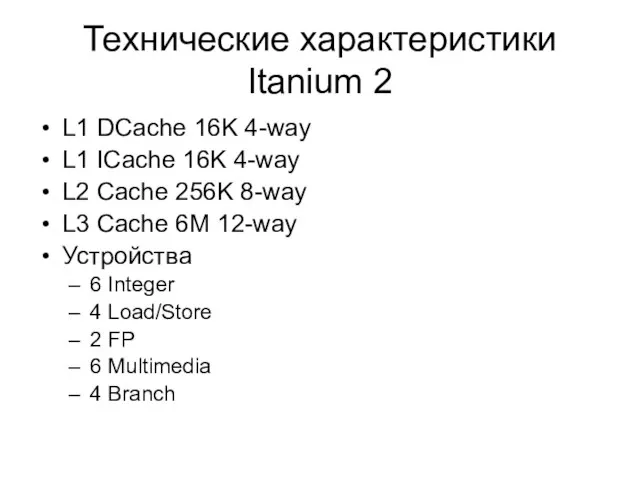

Слайд 13Технические характеристики Itanium 2

L1 DCache 16K 4-way

L1 ICache 16K 4-way

L2 Cache 256K

8-way

L3 Cache 6M 12-way

Устройства

6 Integer

4 Load/Store

2 FP

6 Multimedia

4 Branch

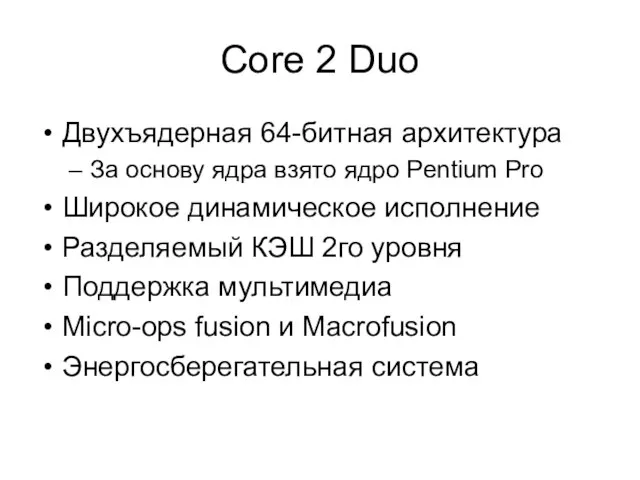

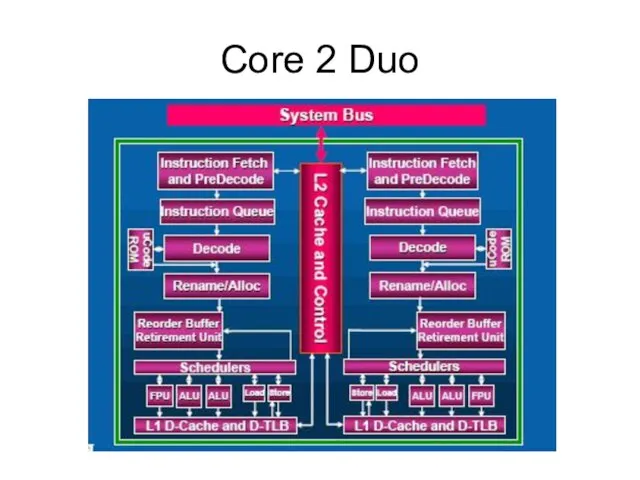

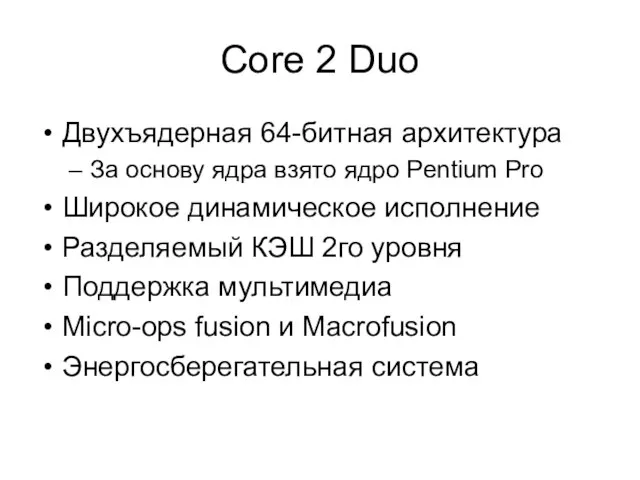

Слайд 15Core 2 Duo

Двухъядерная 64-битная архитектура

За основу ядра взято ядро Pentium Pro

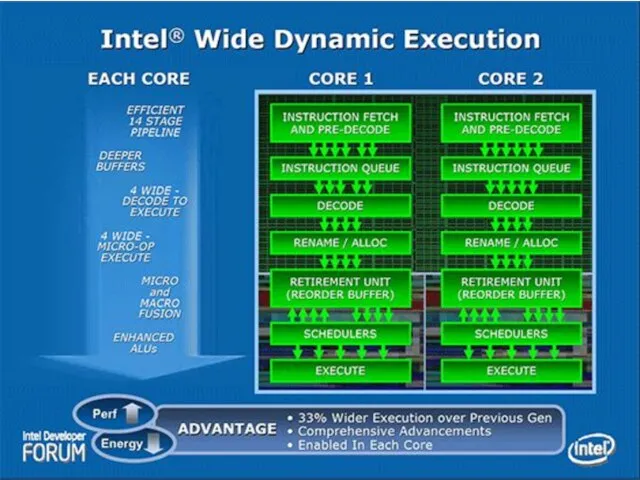

Широкое динамическое

исполнение

Разделяемый КЭШ 2го уровня

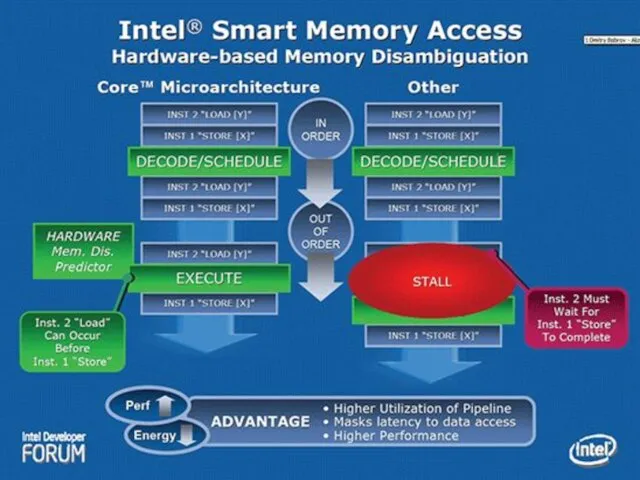

Поддержка мультимедиа

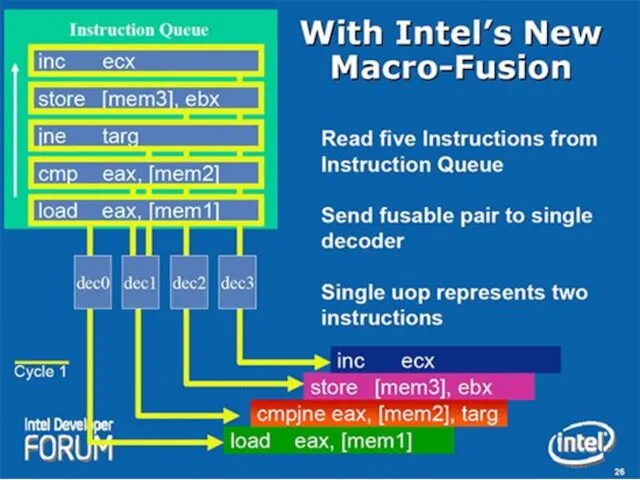

Micro-ops fusion и Macrofusion

Энергосберегательная система

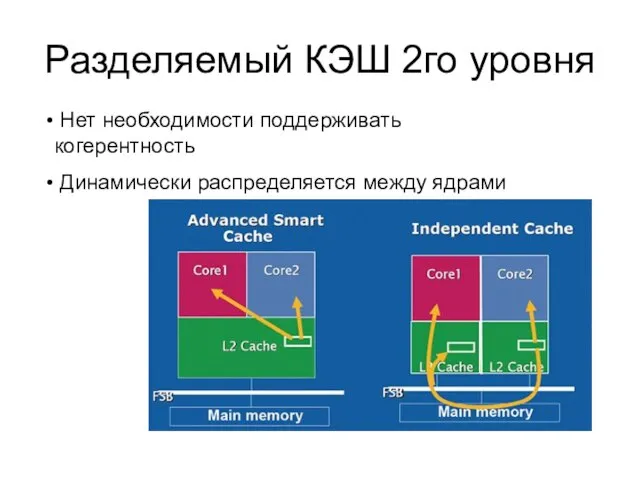

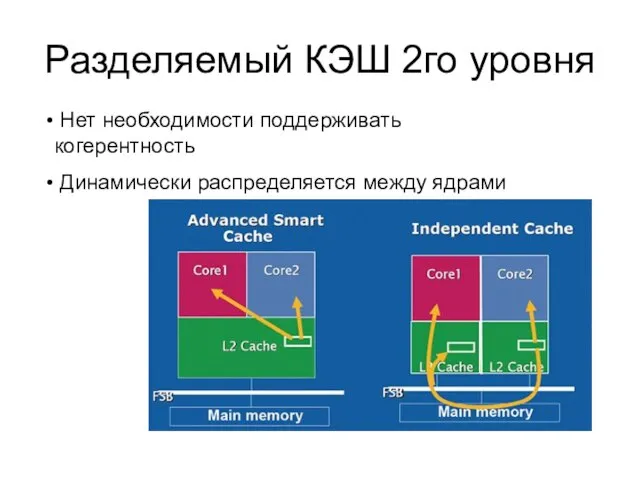

Слайд 18Разделяемый КЭШ 2го уровня

Нет необходимости поддерживать когерентность

Динамически распределяется между ядрами

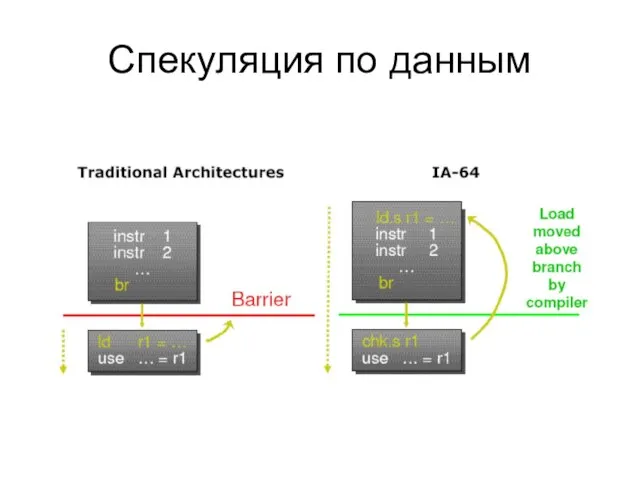

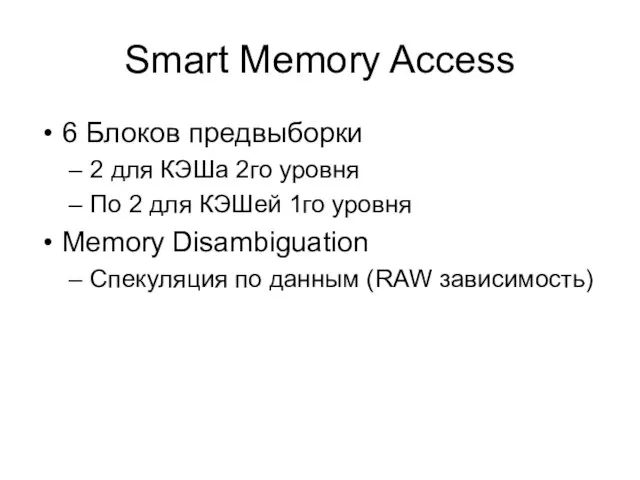

Слайд 19Smart Memory Access

6 Блоков предвыборки

2 для КЭШа 2го уровня

По 2 для КЭШей

1го уровня

Memory Disambiguation

Спекуляция по данным (RAW зависимость)

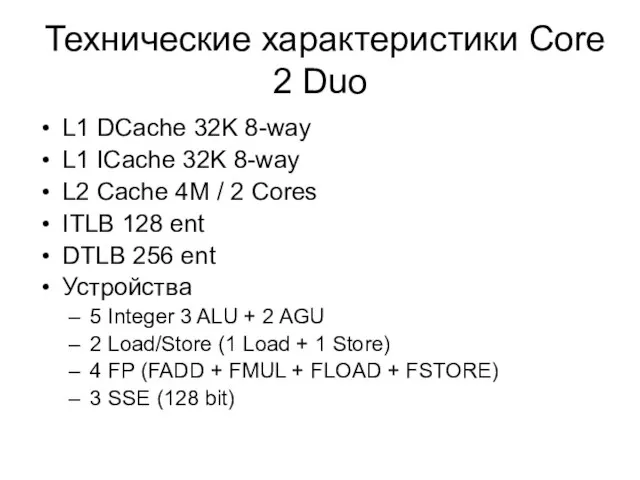

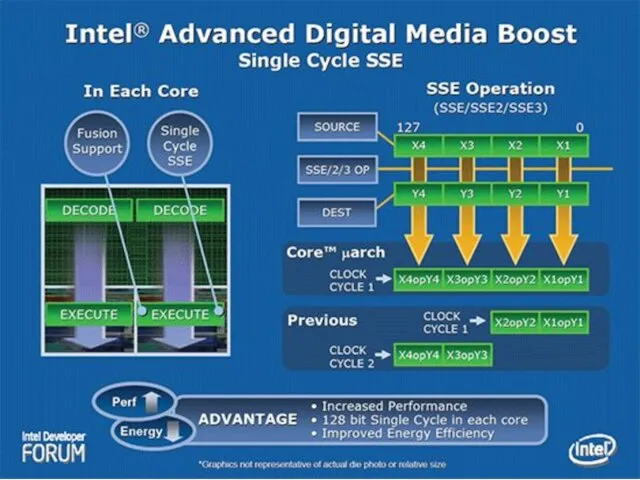

Слайд 22Технические характеристики Core 2 Duo

L1 DCache 32K 8-way

L1 ICache 32K 8-way

L2 Cache

4M / 2 Cores

ITLB 128 ent

DTLB 256 ent

Устройства

5 Integer 3 ALU + 2 AGU

2 Load/Store (1 Load + 1 Store)

4 FP (FADD + FMUL + FLOAD + FSTORE)

3 SSE (128 bit)

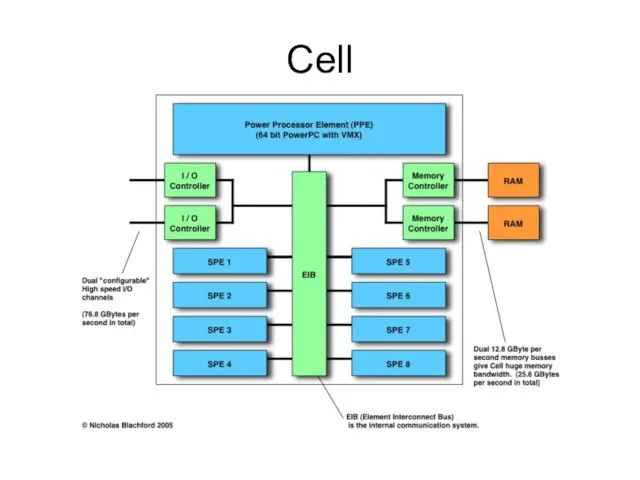

Слайд 24Cell

Главный процессорный элемент

Упорядоченное исполнение

Поддержка работы с двумя потоками

8 синергетических процессорных элементов

Ядро на

основе 286 архитектуры

Поддержка векторных вычислений 128 бит

Отсутствие КЭШей

Локальная память 256 Кбайт с прямым доступом

Шина ввода вывода

Пропускная способность 76,8 Гбайт/с

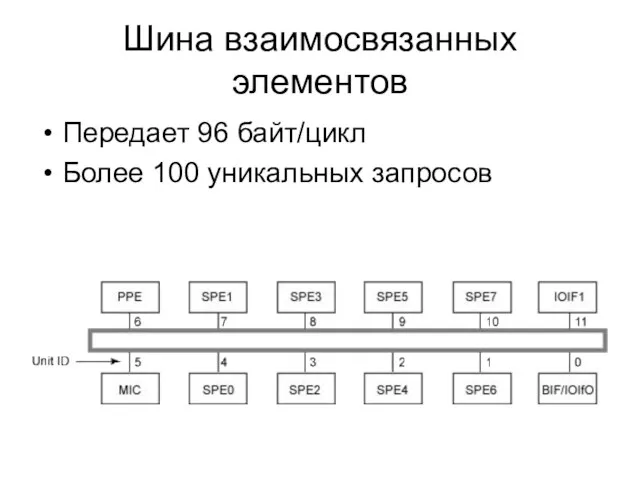

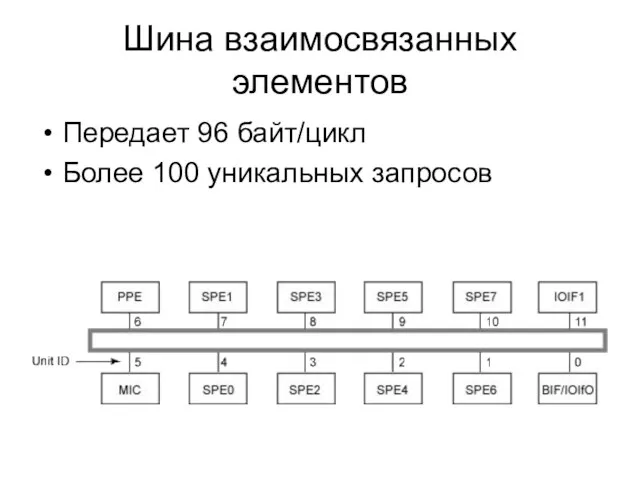

Слайд 25Шина взаимосвязанных элементов

Передает 96 байт/цикл

Более 100 уникальных запросов

Слайд 26Power Processor Element

Два 64-битных ядра на основе архитектуры POWER

Упорядоченное исполнение комманд

Поддержка SMT

(многопоточность)

КЭШ

1го уровня: 32+32 Кбайт

2го уровня: 512 Кбайт

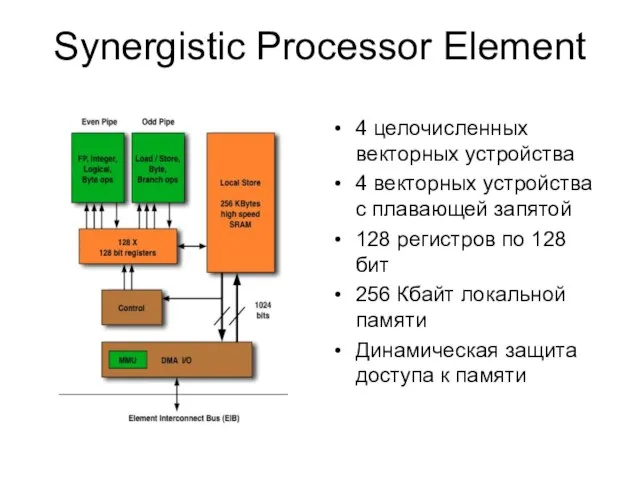

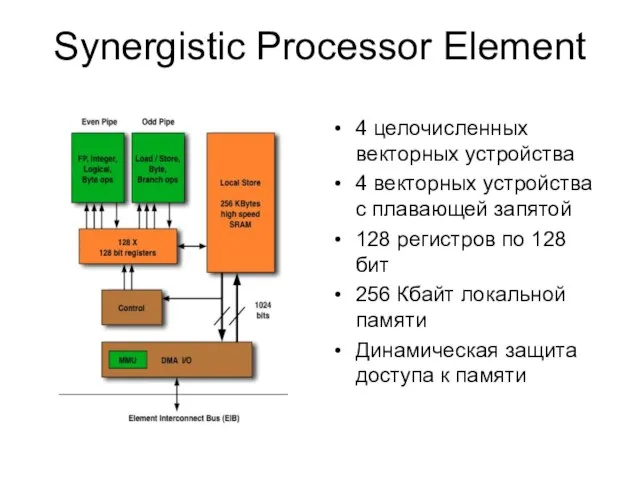

Слайд 27Synergistic Processor Element

4 целочисленных векторных устройства

4 векторных устройства с плавающей запятой

128

регистров по 128 бит

256 Кбайт локальной памяти

Динамическая защита доступа к памяти

Слайд 28Производительность Cell

(для 4GHz)

256 GFLOPS с плавающей запятой

256 GOPS целочисленная арифметика

25 GFLOPS с

плавающей запятой двойной точности

Ислам. Тест

Ислам. Тест Концепция структурных преобразований радиоэлектронной промышленности оборонно-промышленного комплекса

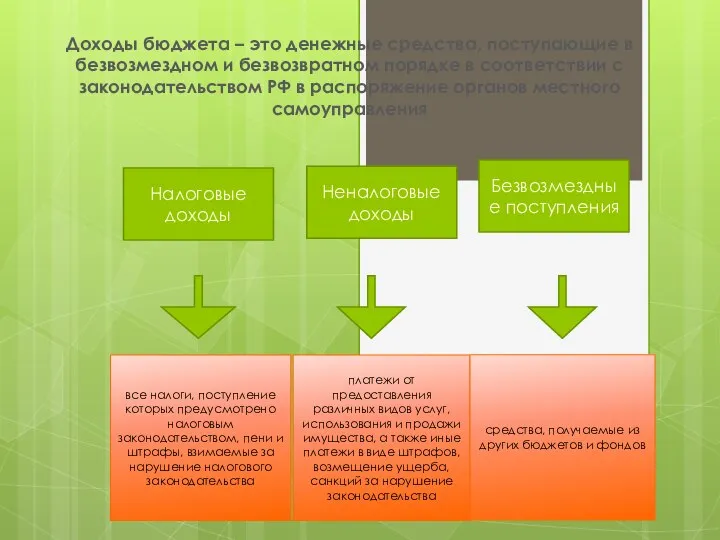

Концепция структурных преобразований радиоэлектронной промышленности оборонно-промышленного комплекса Доходы бюджета Чугунаевского сельского поселения

Доходы бюджета Чугунаевского сельского поселения Деды Морозы в разных странах

Деды Морозы в разных странах Презентация на тему Дорожное движение, безопасность участников дорожного движения (5 класс)

Презентация на тему Дорожное движение, безопасность участников дорожного движения (5 класс) Конкурсная программа «Мы должны быть бережливыми!»

Конкурсная программа «Мы должны быть бережливыми!» Галерея помещиков Мёртвые души

Галерея помещиков Мёртвые души Искусство второй половины XX века.Ташизм, абстрактный экспрессионизм

Искусство второй половины XX века.Ташизм, абстрактный экспрессионизм Производство ферментных препаратов

Производство ферментных препаратов  Общая физическая подготовка

Общая физическая подготовка Придаточные предложения места

Придаточные предложения места Main changes Tudors

Main changes Tudors Сертификация (ап)

Сертификация (ап) Презентация к уроку русского языка в 6 классе по теме Прилагательное как часть речи Составитель: Падалко Татьяна Викторовна

Презентация к уроку русского языка в 6 классе по теме Прилагательное как часть речи Составитель: Падалко Татьяна Викторовна  Презентация на тему Характер

Презентация на тему Характер Организация и нормативно-правовое обеспечение государственной (итоговой) аттестации выпускников 9-х классов в 2009-2010 учебном

Организация и нормативно-правовое обеспечение государственной (итоговой) аттестации выпускников 9-х классов в 2009-2010 учебном  Александр Сергеевич Пушкин

Александр Сергеевич Пушкин Ответственность директоров и контролирующего лица

Ответственность директоров и контролирующего лица Организация внеурочной деятельности при реализации федерального государственного образовательного стандарта начального общего

Организация внеурочной деятельности при реализации федерального государственного образовательного стандарта начального общего Презентация на тему Загадки с подвохом

Презентация на тему Загадки с подвохом Век XVIII в истории России

Век XVIII в истории России Законы и нормативно-правовые акты по организации безопасности по условиям РСЧС

Законы и нормативно-правовые акты по организации безопасности по условиям РСЧС БОРТОВАЯ АНАЛИТИЧЕСКАЯ СИСТЕМА УПРАВЛЕНИЯ РИСКАМИ ПОЛЕТА САМОЛЕТА

БОРТОВАЯ АНАЛИТИЧЕСКАЯ СИСТЕМА УПРАВЛЕНИЯ РИСКАМИ ПОЛЕТА САМОЛЕТА ИМИДЖ КАК ФАКТОР КОНКУРЕНТОСПОСОБНОСТИ ВЫСШЕГО УЧЕБНОГО ЗАВЕДЕНИЯ

ИМИДЖ КАК ФАКТОР КОНКУРЕНТОСПОСОБНОСТИ ВЫСШЕГО УЧЕБНОГО ЗАВЕДЕНИЯ Формы ДНК

Формы ДНК Инфекционный перитонит кошек

Инфекционный перитонит кошек Правила выплат нуждающимся в поддержке семьям на детей от 3 до 7 лет

Правила выплат нуждающимся в поддержке семьям на детей от 3 до 7 лет S-Иерархия и атрибуты маршрутов

S-Иерархия и атрибуты маршрутов