Содержание

- 2. Логические основы ЭВМ Базовые функциональные элементы ЭВМ (вентили) Основные логические схемы

- 3. Вентили Логический элемент - электронное устройство, на входах и выходах которого сигнал может иметь только один

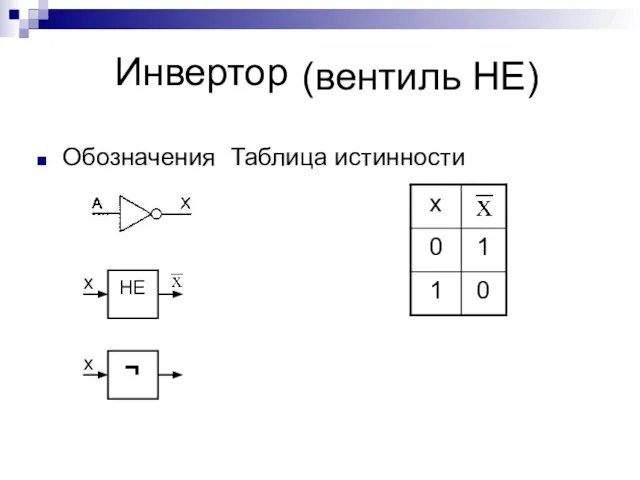

- 4. Инвертор Обозначения Таблица истинности (вентиль НЕ)

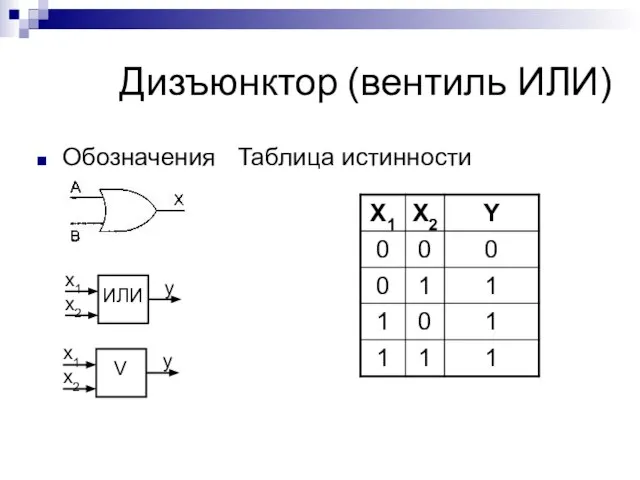

- 5. Дизъюнктор Обозначения Таблица истинности (вентиль ИЛИ)

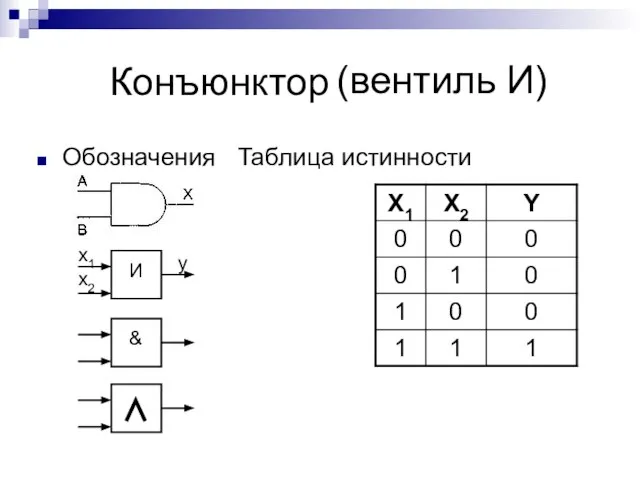

- 6. Конъюнктор Обозначения Таблица истинности (вентиль И)

- 7. Вентили НЕ-И и НЕ-ИЛИ Обозначение Таблица истинности НЕ-И НЕ-ИЛИ

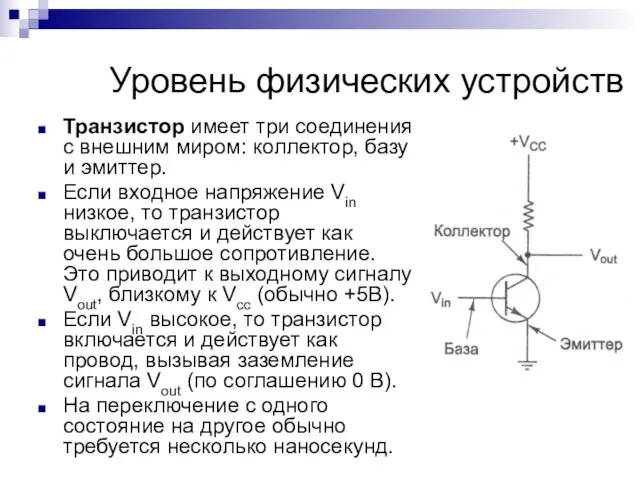

- 8. Уровень физических устройств Транзистор имеет три соединения с внешним миром: коллектор, базу и эмиттер. Если входное

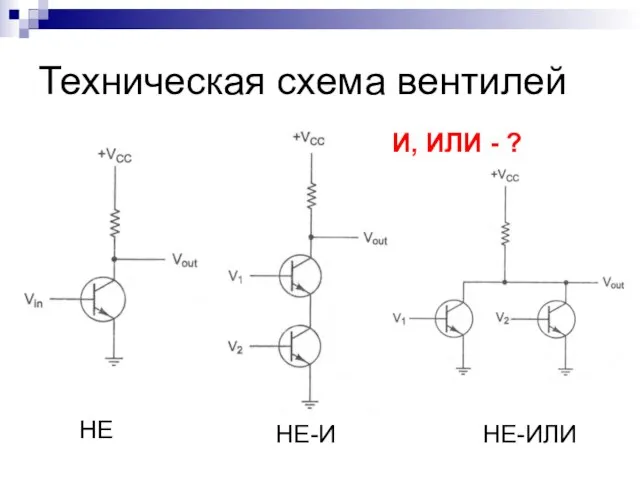

- 9. Техническая схема вентилей НЕ И, ИЛИ - ? НЕ-И НЕ-ИЛИ

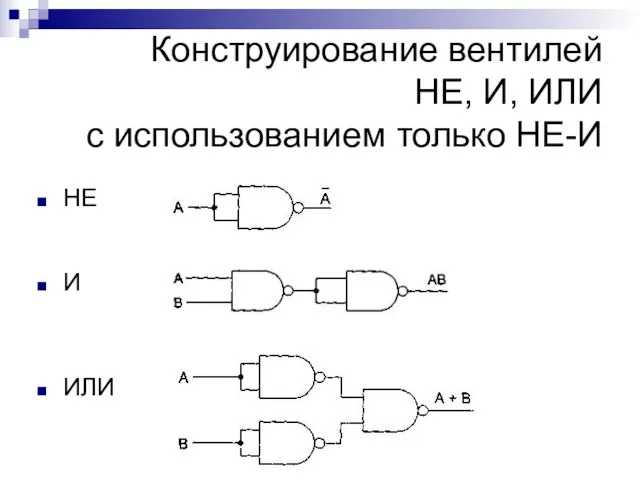

- 10. Конструирование вентилей НЕ, И, ИЛИ с использованием только НЕ-И НЕ И ИЛИ

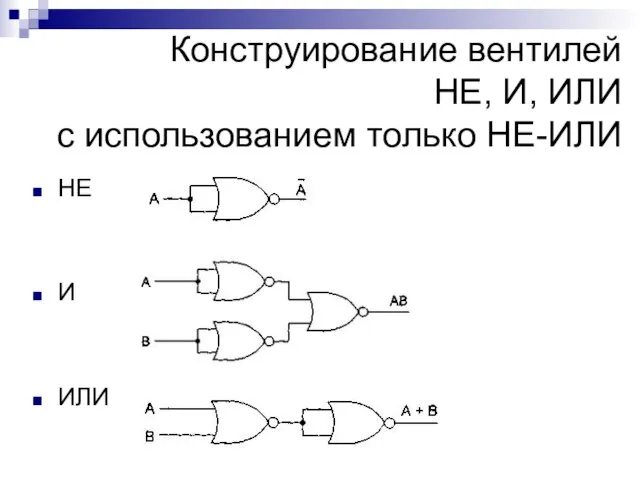

- 11. Конструирование вентилей НЕ, И, ИЛИ с использованием только НЕ-ИЛИ НЕ И ИЛИ

- 12. Логический синтез схем Одноразрядный двоичный полусумматор Полный одноразрядный сумматор Полный многоразрядный сумматор Дешифратор Триггер

- 13. Как реализовать схему Составить таблицу истинности для данной функции Обеспечить инверторы, чтобы порождать инверсии для каждого

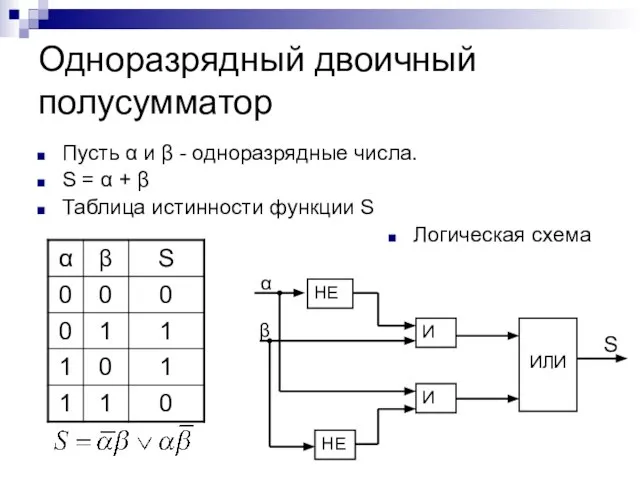

- 14. Одноразрядный двоичный полусумматор Пусть α и β - одноразрядные числа. S = α + β Таблица

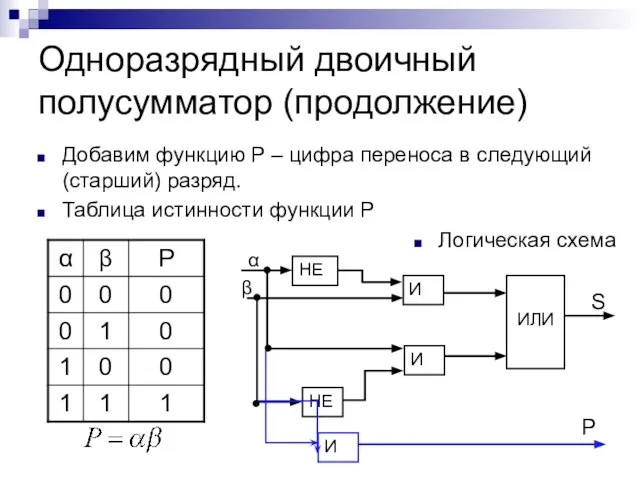

- 15. Одноразрядный двоичный полусумматор (продолжение) Добавим функцию P – цифра переноса в следующий (старший) разряд. Таблица истинности

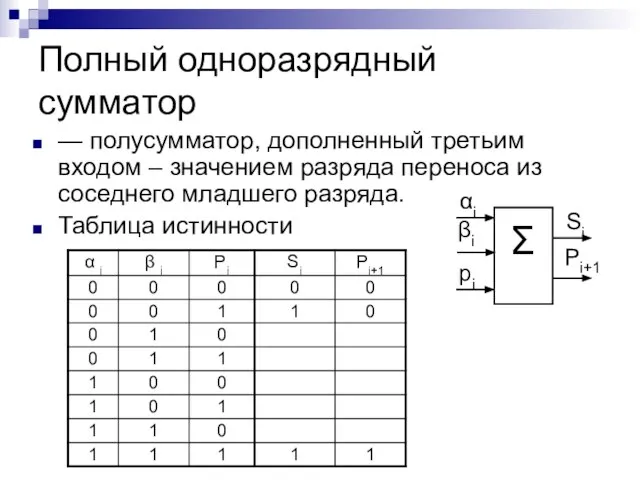

- 16. Полный одноразрядный сумматор — полусумматор, дополненный третьим входом – значением разряда переноса из соседнего младшего разряда.

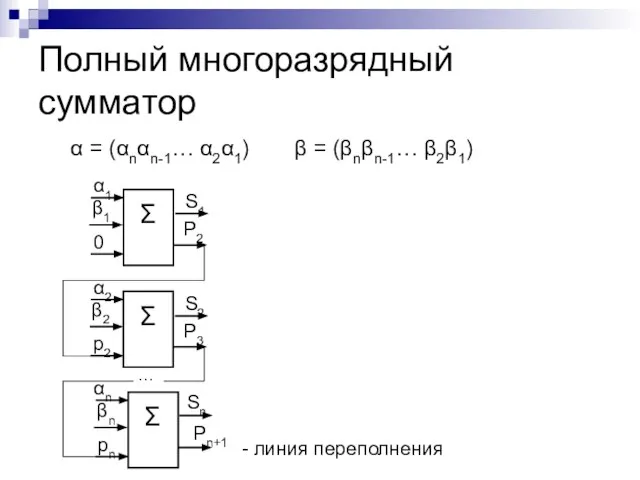

- 17. Полный многоразрядный сумматор β1 0 P2 S1 Σ α1 β2 p2 P3 S2 Σ α2 βn

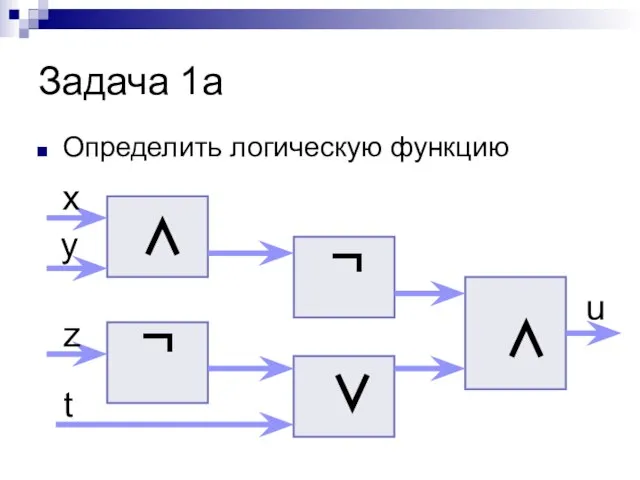

- 18. Задача 1а Определить логическую функцию

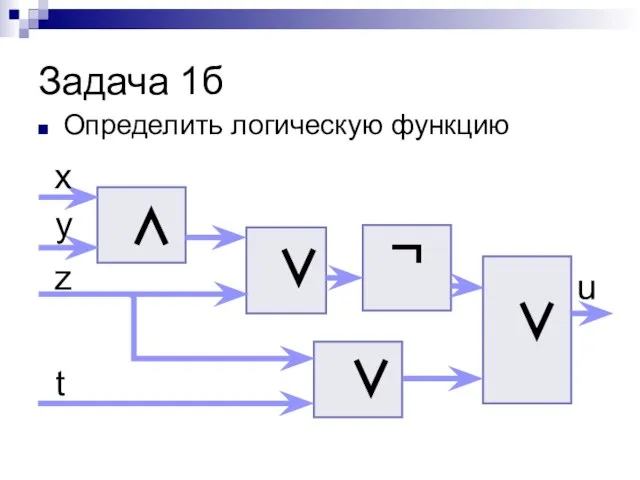

- 19. Задача 1б Определить логическую функцию ∧

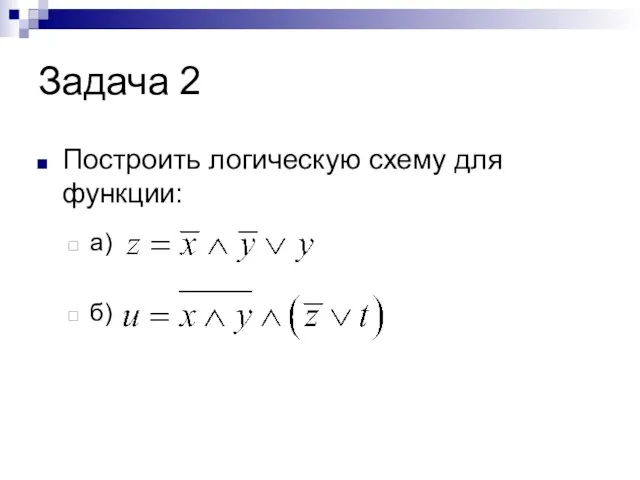

- 20. Задача 2 Построить логическую схему для функции: а) б)

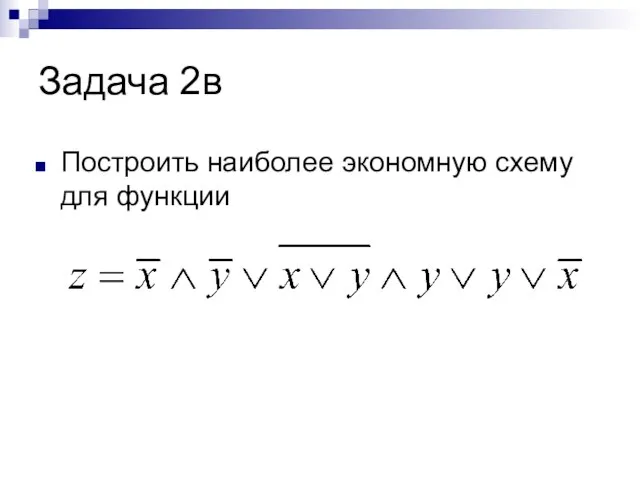

- 21. Задача 2в Построить наиболее экономную схему для функции

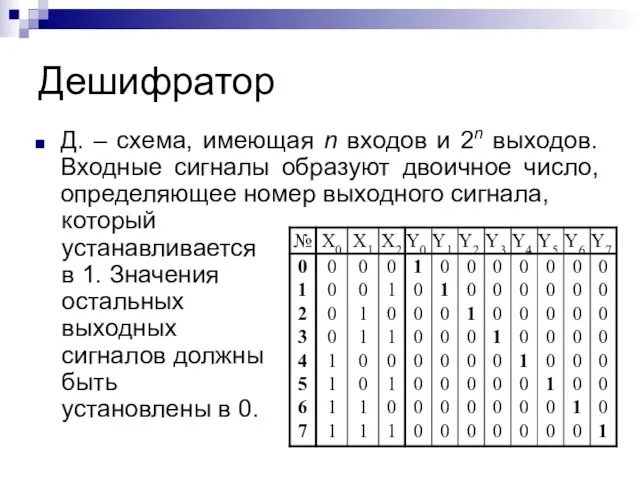

- 22. Дешифратор Д. – схема, имеющая n входов и 2n выходов. Входные сигналы образуют двоичное число, определяющее

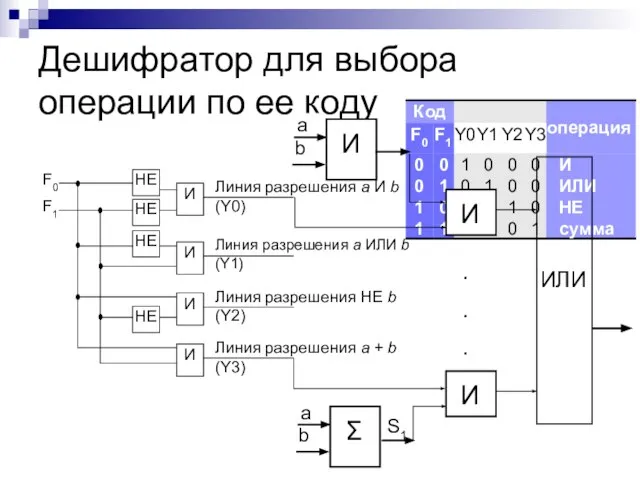

- 23. Дешифратор для выбора операции по ее коду b S1 Σ a И b И a И

- 24. Дешифратор для выбора ячейки памяти по ее адресу

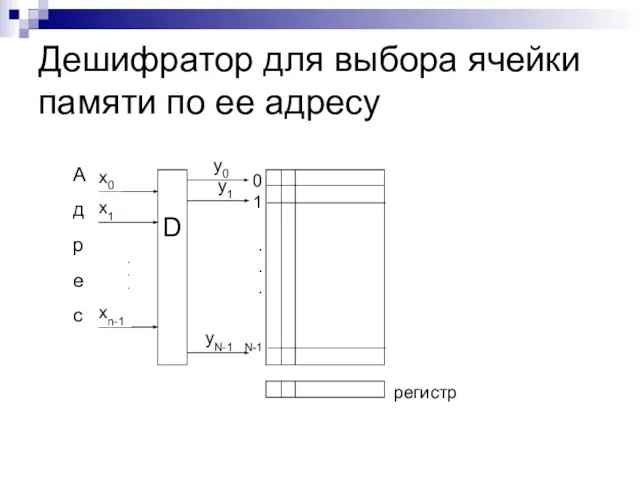

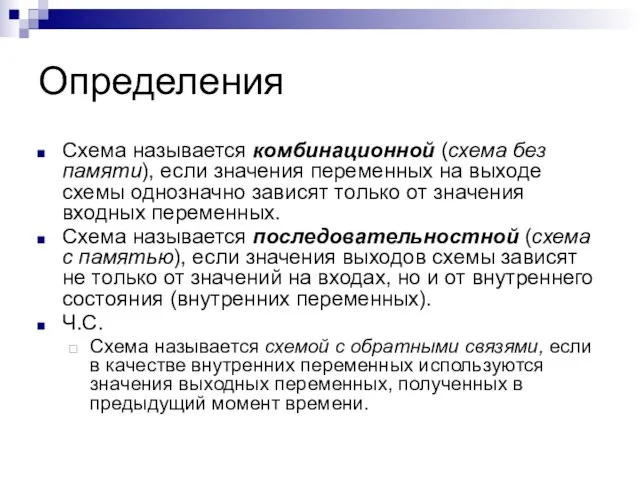

- 25. Определения Схема называется комбинационной (схема без памяти), если значения переменных на выходе схемы однозначно зависят только

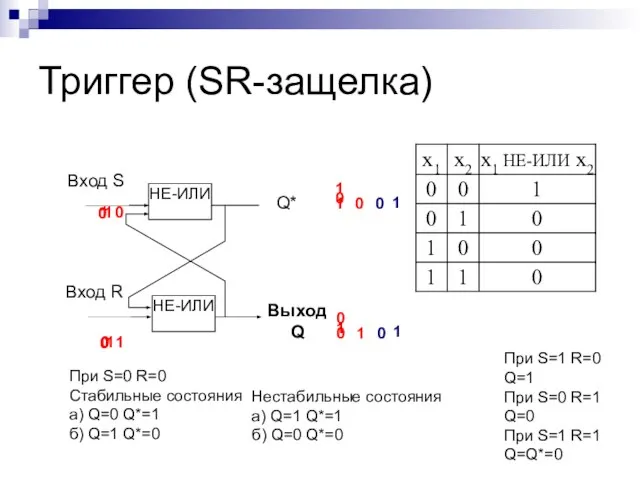

- 26. Триггер (SR-защелка) 1 0 0 0 0 1 0 0 1 1 1 0 0 1

- 28. Скачать презентацию

Семинар Диаграмма Fe-C

Семинар Диаграмма Fe-C На пожаре

На пожаре Презентация на тему Алтайские горы

Презентация на тему Алтайские горы “Зачем” и “почему” в выборе тренинговых программ для корпоративного обучения

“Зачем” и “почему” в выборе тренинговых программ для корпоративного обучения Личностный опросник ТОП-ЮНИТ:Тест как комплексное решение для диагностики менеджерских качеств

Личностный опросник ТОП-ЮНИТ:Тест как комплексное решение для диагностики менеджерских качеств Писатели-юбиляры 2011 года

Писатели-юбиляры 2011 года К вопросу о качестве общего образования:

К вопросу о качестве общего образования: Организация книжных выставок - это наука или искусство!?

Организация книжных выставок - это наука или искусство!? 0805

0805 Подготовка обучающихся с ограниченными возможностями здоровья к демонстрационному экзамену по компетенции Поварское дело

Подготовка обучающихся с ограниченными возможностями здоровья к демонстрационному экзамену по компетенции Поварское дело Таблицы по Теории организации

Таблицы по Теории организации Проблемы и критерии дифференциации уголовно-процессуальной формы _

Проблемы и критерии дифференциации уголовно-процессуальной формы _ Онлайн–консультация адвоката Хромых Ларисы Георгиевны по вопросам кредитных обязательств по невероятно низкой цене

Онлайн–консультация адвоката Хромых Ларисы Георгиевны по вопросам кредитных обязательств по невероятно низкой цене Фірмовий стиль компаній

Фірмовий стиль компаній Верность долгу

Верность долгу Русский язык и культура речи. Виртуальная выставка

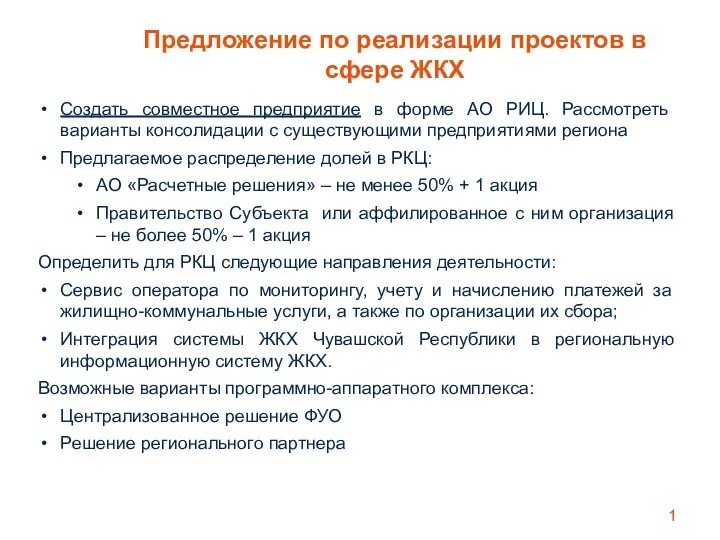

Русский язык и культура речи. Виртуальная выставка Предложение по реализации проектов в сфере ЖКХ

Предложение по реализации проектов в сфере ЖКХ Ополнительная платная образовательная услуга по социально-коммуникативному развитию Песочная терапия

Ополнительная платная образовательная услуга по социально-коммуникативному развитию Песочная терапия Презентация на тему Формирование Земли

Презентация на тему Формирование Земли  Церковь, государство и общество. Основные институты церковного права в период формирования централизованного государства.

Церковь, государство и общество. Основные институты церковного права в период формирования централизованного государства.  Проектная деятельность в образовании: история и современность

Проектная деятельность в образовании: история и современность Презентация на тему Ткани животных и растений

Презентация на тему Ткани животных и растений Основные направления деятельности Союза Российских Пивоваровна 2007-2009 гг.

Основные направления деятельности Союза Российских Пивоваровна 2007-2009 гг. Исследование и разработка методов цифровой обработки сигналов в авиации

Исследование и разработка методов цифровой обработки сигналов в авиации  Слагаемые успеха в бизнесе

Слагаемые успеха в бизнесе Поощрения и наказания в воспитании детей

Поощрения и наказания в воспитании детей Способы изменения внутренней энергии тела

Способы изменения внутренней энергии тела Как предотвратить образование угрей

Как предотвратить образование угрей