Слайд 2Организация функционирования ЭВМ с магистральной архитектурой

Комплект интегральных схем, из которых состоит ЭВМ,

называется микропроцессорным комплектом (МК)

В состав МК входят: системный таймер, микропроцессор (МП), сопроцессоры, контроллер прерываний, контроллер прямого доступа к памяти (ПДП), контроллеры устройств ввода-вывода и др.

Слайд 3Организация функционирования ЭВМ с магистральной архитектурой

Все устройства ЭВМ делятся на центральные и

периферийные.

Центральные устройства полностью электронные, периферийные могут быть либо электронными, либо электромеханическими с электронным правлением.

Слайд 4Организация функционирования ЭВМ с магистральной архитектурой

В центральных устройствах основным узлом, связывающим микропроцессорный

комплект в единое целое, является системная магистраль. Она состоит из трех узлов, называемых шинами:

шина данных (ШД)

шина адресов (ША)

шина управления (ШУ).

Слайд 5Организация функционирования ЭВМ с магистральной архитектурой

Количество проводников в шине называется разрядностью (шириной)

шины.

Для ША ширина равна 20 - 64, что обеспечивает прямую адресацию 220-264 устройств или ячеек памяти.

ШД имеет ширину 8-64, обеспечивая параллельную передачу от одного до восьми байт.

Ширина ШУ зависит от типа ЦП и определяется числом управляющих сигналов.

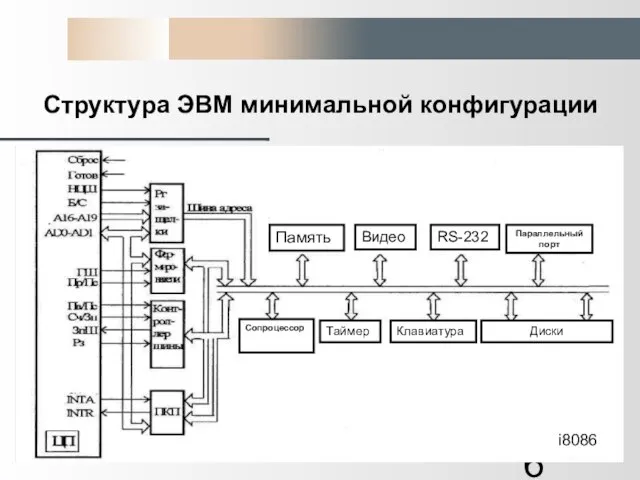

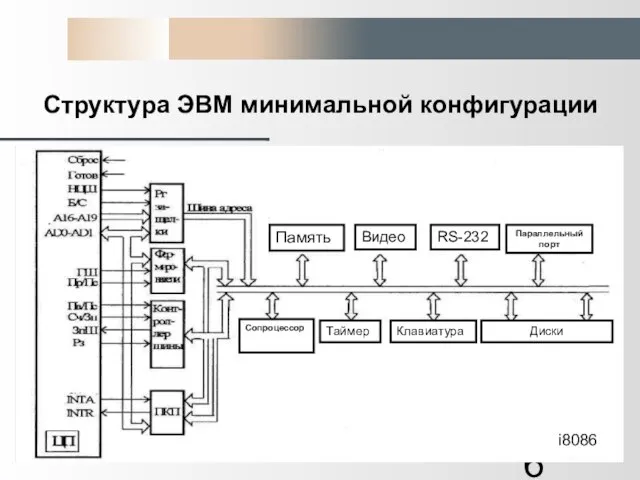

Слайд 6Структура ЭВМ минимальной конфигурации

i8086

Память

Видео

RS-232

Параллельный порт

Сопроцессор

Таймер

Клавиатура

Диски

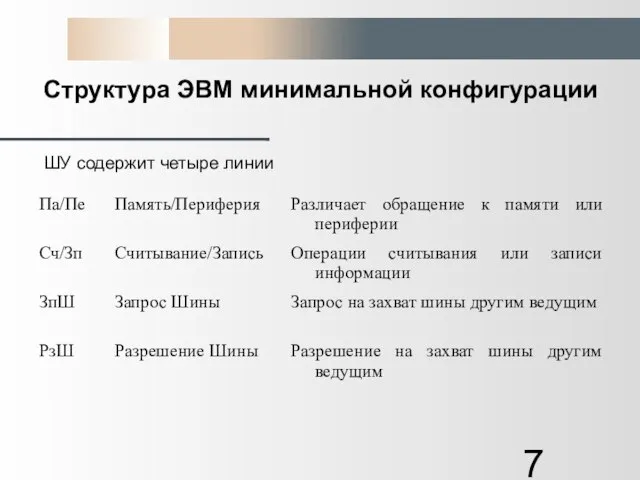

Слайд 7Структура ЭВМ минимальной конфигурации

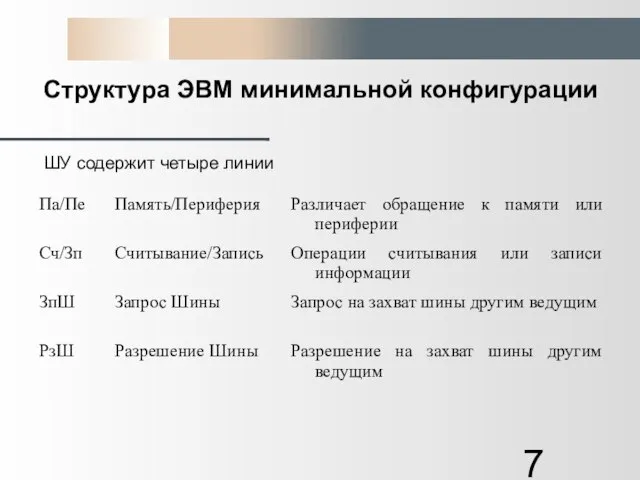

ШУ содержит четыре линии

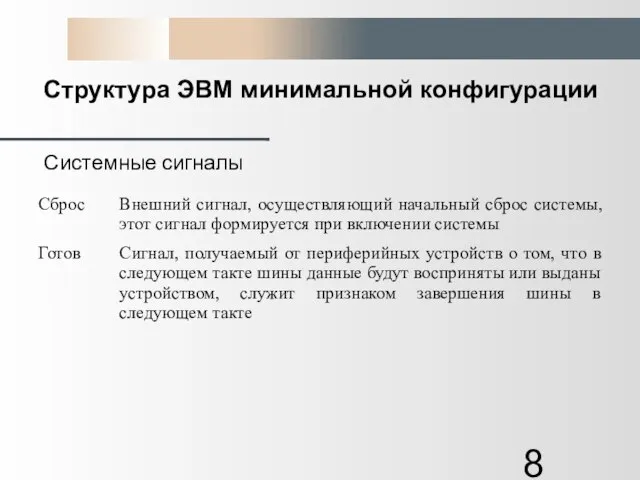

Слайд 8Структура ЭВМ минимальной конфигурации

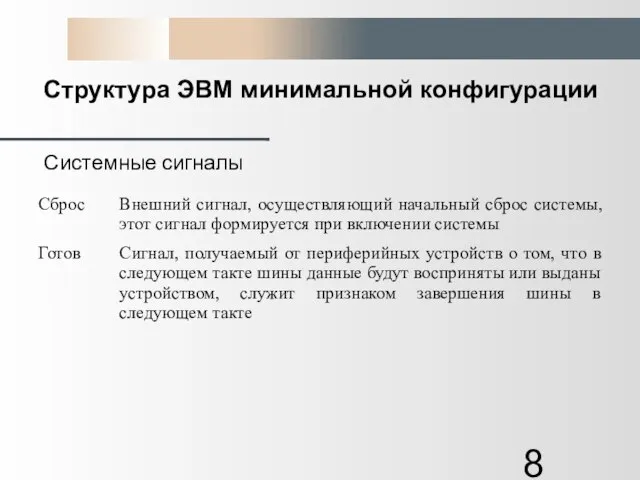

Системные сигналы

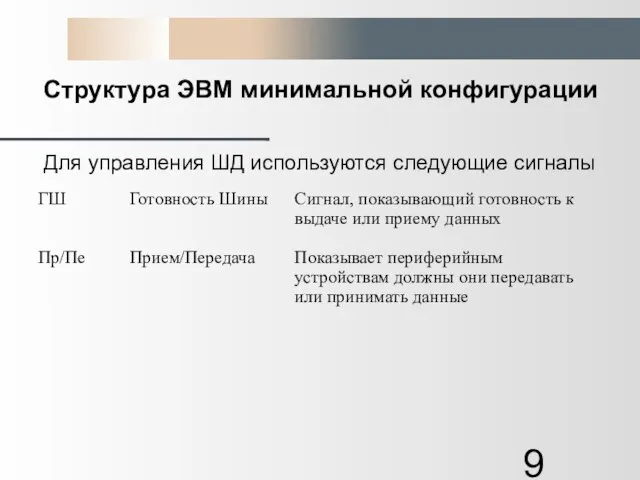

Слайд 9Структура ЭВМ минимальной конфигурации

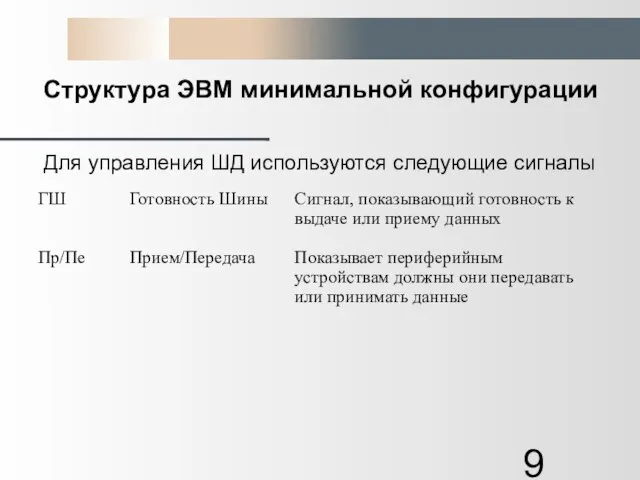

Для управления ШД используются следующие сигналы

Слайд 10Структура ЭВМ минимальной конфигурации

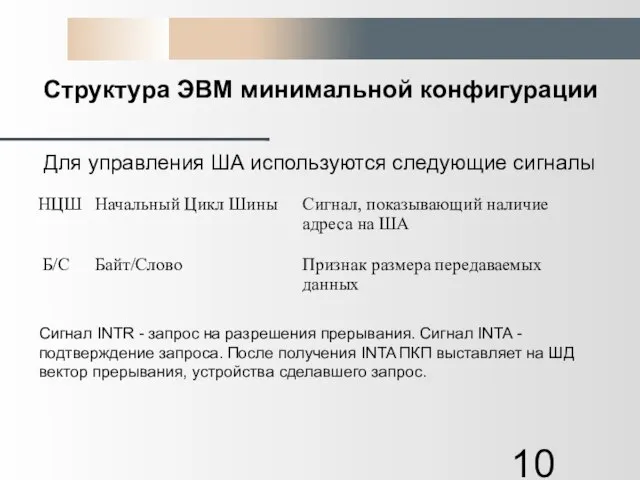

Для управления ША используются следующие сигналы

Сигнал INTR -

запрос на разрешения прерывания. Сигнал INTA - подтверждение запроса. После получения INTA ПКП выставляет на ШД вектор прерывания, устройства сделавшего запрос.

Слайд 11Цикл работы и стандарты системной шины

СШ синхронизирована сигналами тактового генератора процессора.

Цикл шины состоит из нескольких тактов: четырёх обязательных тактов (Т1 - Т4) и бесконечного числа тактов ожидания (Т0).

Когда процессор готов инициировать цикл шины, он в такте Т1 выдаёт сигнал НЦШ и сигналы, определяющие вид информации (Б/С), адресат (Па/Пе), вид данных (Б/С), режимы (Сч/Зп) и (Пр/Пе) и выставляет на выводы адреса адрес порта периферийного устройства или ячейки памяти.

Слайд 12Цикл работы и стандарты системной шины

В конце такта регистры защёлки фиксируют

адрес и он снимается с контактов адреса ЦП.

Во втором такте устанавливается сигнал ГШ, разрешающая работу формирователей.

В третьем такте, если периферийные устройства или память могут принять/передать информацию, то данные помещаются на шину. Если к моменту Т3 ЦП не получил от устройства сигнал Готов, он вводит между тактами Т3 и Т4 такты ожидания Т0 до получения сигнала Готов.

В начале четвёртого такта данные принимаются/передаются ЦП, снимаются сигналы ГШ и Пр/Пе и цикл СШ заканчивается.

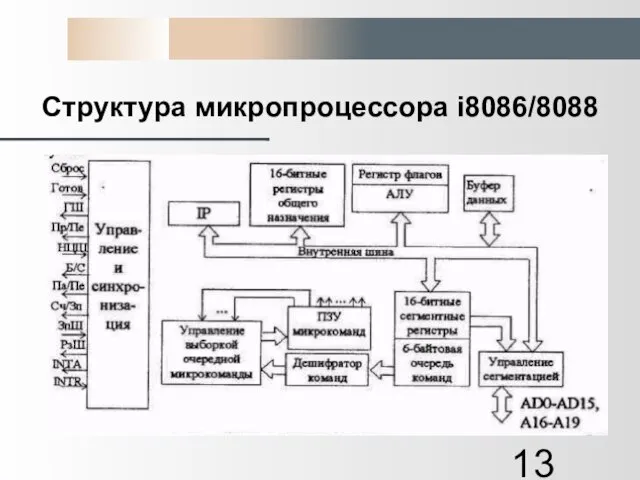

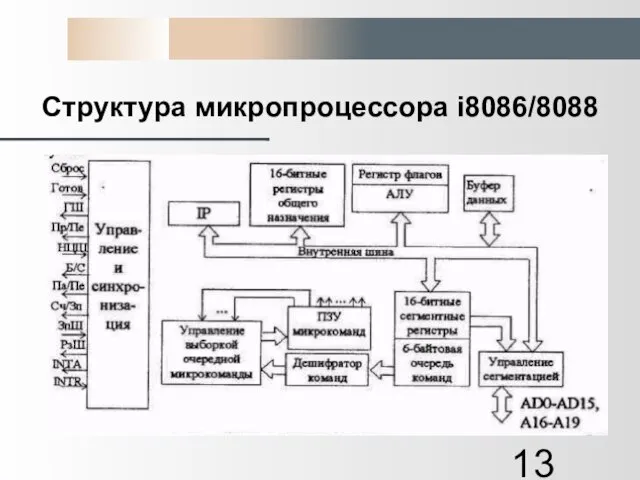

Слайд 13Структура микропроцессора i8086/8088

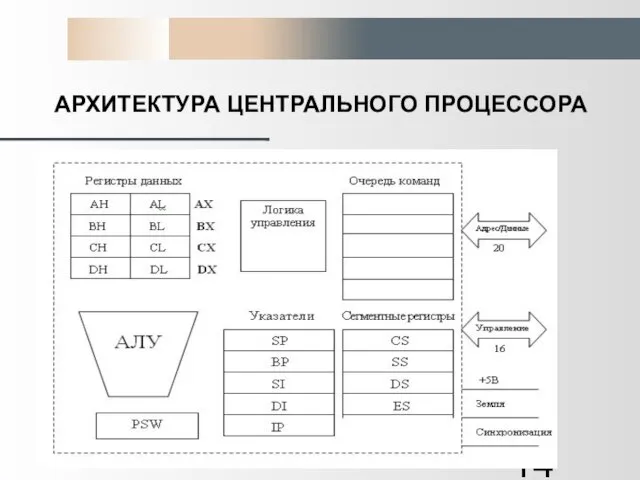

Слайд 14АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Слайд 15АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

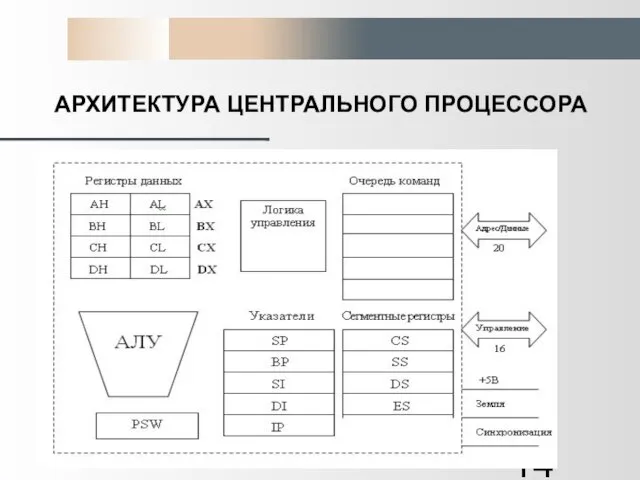

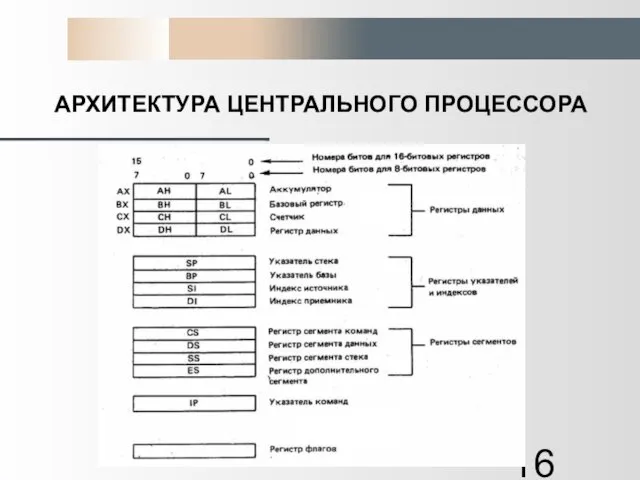

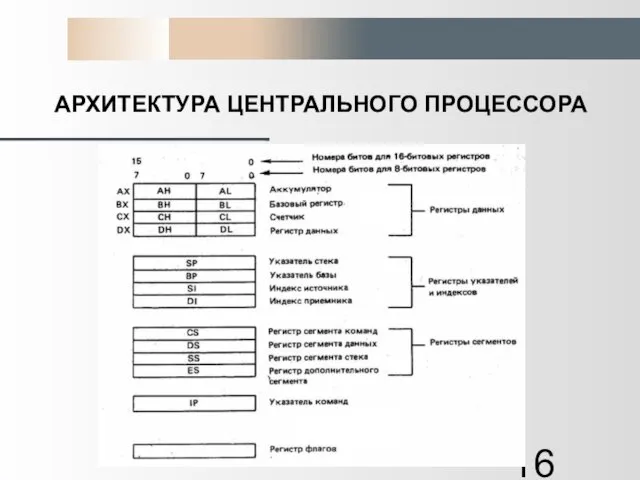

Внутри микропроцессора информация содержится в группе 16-битовых элементов, называемых регистрами.

Всего он имеет 14 регистров:

12 регистров данных и адресов и в дополнение к ним указатель команд (регистр адреса команд) и регистр состояния (регистр флагов).

Можно подразделить 12 регистров данных и адресов на три группы по четыре регистра, а именно на регистры данных, регистры указателей и индексов и регистры сегментов.

Слайд 16АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

Слайд 17Регистры данных

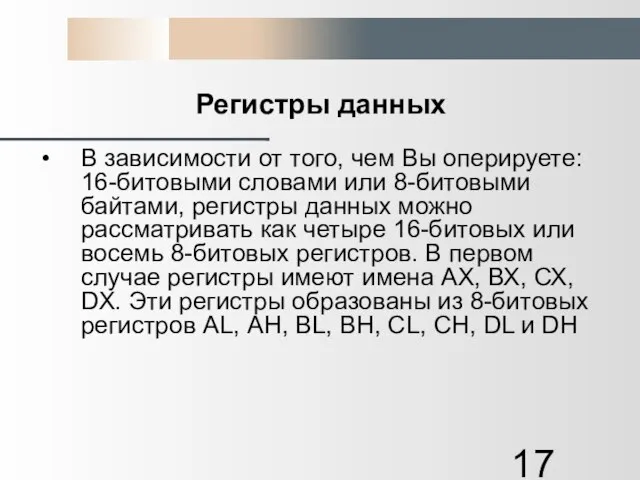

В зависимости от того, чем Вы оперируете: 16-битовыми словами или 8-битовыми

байтами, регистры данных можно рассматривать как четыре 16-битовых или восемь 8-битовых регистров. В первом случае регистры имеют имена АХ, ВХ, СХ, DX. Эти регистры образованы из 8-битовых регистров AL, АН, BL, BH, CL, СН, DL и DH

Слайд 18Регистры данных

Регистр АХ, аккумулятор (accumulator), используется при умножении и делении слов, в

операциях ввода-вывода и в некоторых операциях над строками.

Регистр AL используется при выполнении аналогичных операций над байтами, а также при преобразовании десятичных чисел и выполнении над ними арифметических операций.

Регистр АН используется при умножении и делении байтов.

Слайд 19Регистры данных

Регистр ВХ, базовый регистр (base register), часто используется при адресации данных

в памяти.

Регистр СХ, счетчик (count register), используется как счетчик числа повторений цикла и в качестве номера позиции элемента данных при операциях над строками.

Регистр CL используется как счетчик при операциях сдвига и циклического сдвига на несколько битов.

Регистр DX, регистр данных (data register), используется при умножении и делении слов. Кроме того, в операциях ввода-вывода он используется как номер порта.

Слайд 20Регистры сегментов

Регистр сегмента команд CS (code segment) указывает на сегмент, содержащий текущую

исполняемую программу. Для вычисления адреса следующей исполняемой команды микропроцессор добавляет к содержимому регистра CS содержимое указателя команд IP.

Регистр сегмента стека SS (stack segment) указывает на текущий сегмент стека. Стек представляет собой область памяти, используемую для временного хранения данных и адресов. Микропроцессор 8088 использует стек для хранения адреса возврата из текущей подпрограммы, но стек можно использовать также для восстановления содержимого регистров, изменяемых при работе программы.

Слайд 21Регистры сегментов

Регистр сегмента данных DS (data segment) указывает на текущий сегмент данных,

обычно содержащий используемые в программе переменные.

Регистр дополнительного сегмента ES (extra segment) указывает на текущий дополнительный сегмент, который используется при выполнении операций над строками.

Слайд 22Регистры указателей и индексов

Для вычисления адреса команды в сегменте команд микропроцессор извлекает

номер блока памяти из регистра CS, а смещение - из регистра IP.

Для доступа к сегменту данных микропроцессор извлекает номер блока из регистра DS, а смещение - из регистра ВХ или индексного регистра (SI или DI).

Для доступа к сегменту стека микропроцессор извлекает номер блока из регистра SS, а смещение - из регистра указателя (SP или ВР).

Выбирая номер блока из регистра ES, микропроцессор может также получить доступ к дополнительному сегменту.

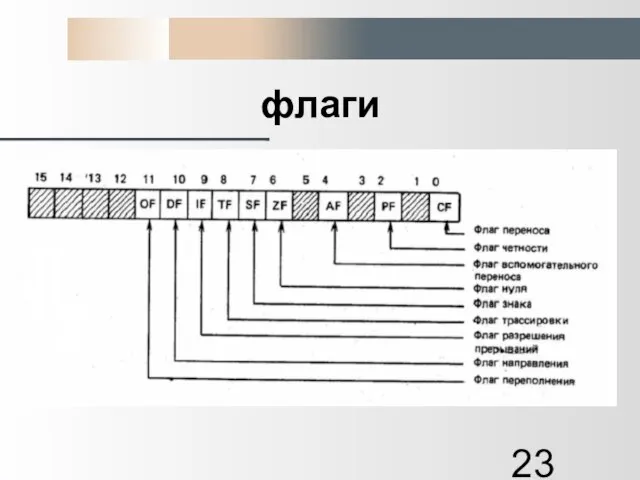

Слайд 24флаги

В 16-битовом регистре флагов фиксируется информация о текущем состоянии дел, которая может

помочь программе принять решение. Шесть битов регистра служат для хранения состояний, а три других могут быть использованы для программного управлений режимом работы микропроцессора

Слайд 25флаги

1. Бит 0, флаг переноса CF (carry flag), равен 1, если произошел

перенос единицы при сложении или заем единицы при вычитании. В противном случае он равен нулю. Кроме того, CF содержит значение бита, который при сдвиге или циклическом сдвиге регистра или ячейки памяти вышел за их границы, и отражает результат операции сравнения. Наконец, CF служит индикатором результата умножения.

Слайд 26флаги

2. Бит 2, флаг четности PF (parity flag), равен 1, если в

результате операции получено число с четным числом единиц в его битах. В противном случае он равен нулю. Флаг РF в основном используется в операциях обмена данными.

Слайд 27флаги

3. Бит 4, вспомогательный флаг переноса AF (auxiliary carry flag), аналогичен флагу

CF, только контролирует перенос или заем для третьего бита данных. Полезен при выполнении операций над упакованными десятичными числами.

4. Бит 6 флаг нуля ZF (zero flag), равен 1, если в результате операции получен нуль; ненулевой результат сбрасывает ZF в нуль.

Слайд 28флаги

5. Бит 7, флаг знака SF (sign flag), имеет значение только при

операциях над числами со знаком. Флаг SF равен 1, если в результате арифметической или логической операции, сдвига или циклического сдвига получено отрицательное число. В противном случае он равен нулю.

Слайд 29флаги

6. Бит 8, флаг трассировки TF (trap flag), разрешает микропроцессору исполнять программу

"по шагам" и используется при отладке программ.

7. Бит 9, флаг прерывания IF (interrupt enable flag), разрешает микропроцессору реагировать на прерывания от внешних устройств. Сбрасывание IF в нуль заставляет микропроцессор игнорировать прерывания до тех пор, пока IF не станет равным 1.

Слайд 30флаги

8. Бит 10, флаг направления DF (direction flag), заставляет микропроцессор уменьшать на

единицу (DF = 1) или увеличивать на единицу (DF = 0) регистр(ы) индекса после выполнения команды для работы со строками. Если DF = 0, то микропроцессор будет обрабатывать строку "слева направо" (от младших адресов к старшим). Если DF = 1, то обработка пойдет в обратном направлении (от старших адресов к младшим или справа налево).

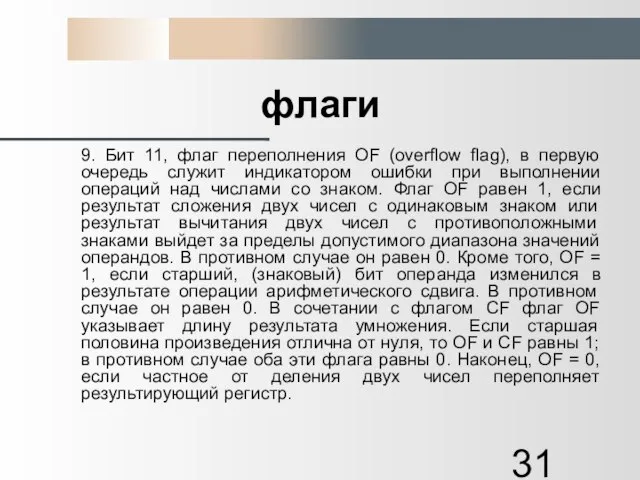

Слайд 31флаги

9. Бит 11, флаг переполнения OF (overflow flag), в первую очередь служит

индикатором ошибки при выполнении операций над числами со знаком. Флаг OF равен 1, если результат сложения двух чисел с одинаковым знаком или результат вычитания двух чисел с противоположными знаками выйдет за пределы допустимого диапазона значений операндов. В противном случае он равен 0. Кроме того, OF = 1, если старший, (знаковый) бит операнда изменился в результате операции арифметического сдвига. В противном случае он равен 0. В сочетании с флагом CF флаг OF указывает длину результата умножения. Если старшая половина произведения отлична от нуля, то OF и CF равны 1; в противном случае оба эти флага равны 0. Наконец, OF = 0, если частное от деления двух чисел переполняет результирующий регистр.

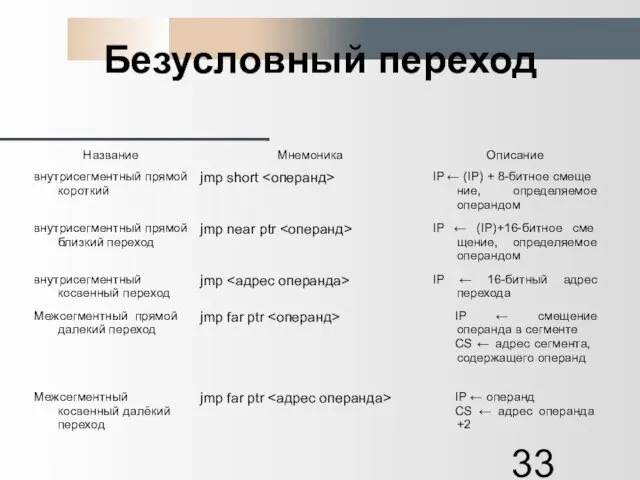

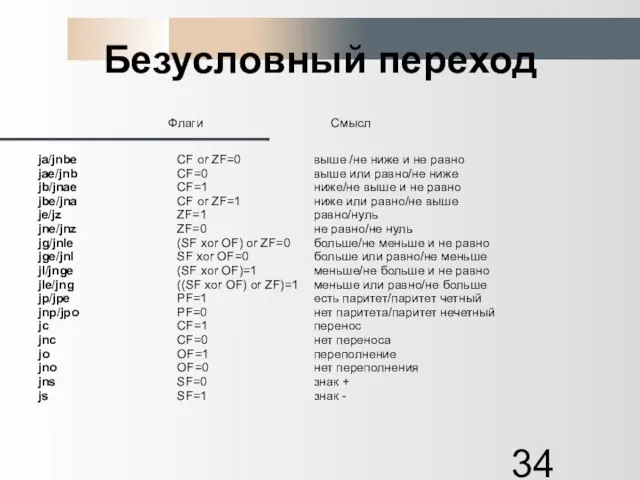

Слайд 32Безусловный переход

jmp [< тип > ptr ] операнд.

<тип> - тип перехода short

![Безусловный переход jmp [ ptr ] операнд. - тип перехода short (короткий)](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/312133/slide-31.jpg)

(короткий) – смещение 127 байтов вперёд или 128 байтов назад, near (близкий) – смещение в пределах сегмента (64 Кбайта), far (дальний) – в любой сегмент с любым смещением.

ptr – приставка, которую можно перевести как указанный в.

Если тип не задан, по умолчанию принимается near.

Слайд 35Циклы

loop[<условие повторения цикла>] <метка короткого перехода>

Инструкция loop использует содержимое регистра СХ как

![Циклы loop[ ] Инструкция loop использует содержимое регистра СХ как счетчик повторений](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/312133/slide-34.jpg)

счетчик повторений цикла. Команда loop уменьшает содержимое регистра СХ на 1 и передает управление по адресу, определяемому меткой перехода, если содержимое СХ ≠ 0, в противном случае выполняется следующая за LOOP инструкция.

Добавление к инструкции loop <условие повторения цикла> позволяет ввести дополнительные логические условия на повторение цикла:

loope/loopz – повторять, пока ноль;

loopne/loopnz – повторять, пока не ноль.

Слайд 36Пример

Дан массив из десяти слов, содержащих целые числа. Требуется найти максимальное значение

в массиве.

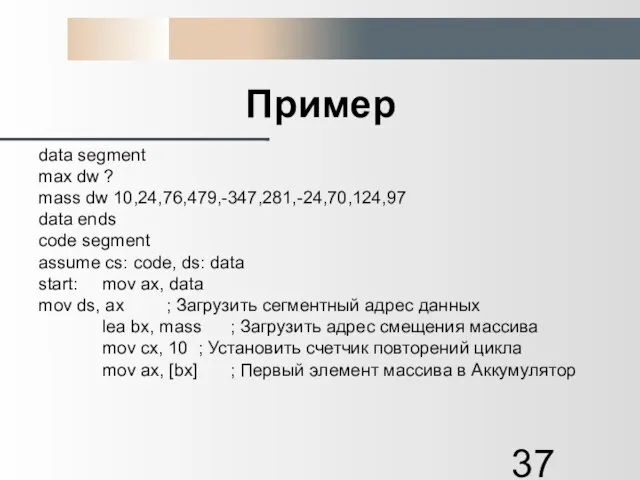

Слайд 37Пример

data segment

max dw ?

mass dw 10,24,76,479,-347,281,-24,70,124,97

data ends

code segment

assume cs: code, ds: data

start:

mov ax, data

mov ds, ax ; Загрузить сегментный адрес данных

lea bx, mass ; Загрузить адрес смещения массива

mov cx, 10 ; Установить счетчик повторений цикла

mov ax, [bx] ; Первый элемент массива в Аккумулятор

![Безусловный переход jmp [ ptr ] операнд. - тип перехода short (короткий)](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/312133/slide-31.jpg)

![Циклы loop[ ] Инструкция loop использует содержимое регистра СХ как счетчик повторений](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/312133/slide-34.jpg)

Взаимодействие семьи и школы

Взаимодействие семьи и школы ООО «НТЦ Энергосервис» Компания ООО «НТЦ Энергосервис»была организована в 2007 году и на сегодняшний день готова предложить своим к

ООО «НТЦ Энергосервис» Компания ООО «НТЦ Энергосервис»была организована в 2007 году и на сегодняшний день готова предложить своим к Презентация на тему Идеальный учитель глазами детей

Презентация на тему Идеальный учитель глазами детей Чёрная магия поисковой оптимизации и её разоблачение Дмитрий Федорук Разработчик, группа поискового спама

Чёрная магия поисковой оптимизации и её разоблачение Дмитрий Федорук Разработчик, группа поискового спама  Презентация на тему Система и модель работы с детьми младшего и старшего дошкольного возраста по ознакомлению с правилами дорожно

Презентация на тему Система и модель работы с детьми младшего и старшего дошкольного возраста по ознакомлению с правилами дорожно Школьная жизнь, 2019 г

Школьная жизнь, 2019 г Обоснование выбора компетенции

Обоснование выбора компетенции Гражданское общество и правовое государство, 10 класс

Гражданское общество и правовое государство, 10 класс Ценовая политика кондитерской фабрики Белогорье и направления ее совершенствования

Ценовая политика кондитерской фабрики Белогорье и направления ее совершенствования I love bananas. What do you usually have for your breakfast?

I love bananas. What do you usually have for your breakfast? Презентация на тему слово и словосочетание

Презентация на тему слово и словосочетание  Храм Ники Аптерос

Храм Ники Аптерос Презентация на тему Рекреационные ресурсы мира

Презентация на тему Рекреационные ресурсы мира Глобальные процессы в современном мире

Глобальные процессы в современном мире Приветствие. Демонстрация возможности

Приветствие. Демонстрация возможности Практика. Основы дизайна. Макетирование

Практика. Основы дизайна. Макетирование РАЗВИТИЕ КЛЮЧЕВЫХ КОМПЕТЕНЦИЙ НА УРОКАХ МАТЕМАТИКИ через самостоятельную работу учащихся

РАЗВИТИЕ КЛЮЧЕВЫХ КОМПЕТЕНЦИЙ НА УРОКАХ МАТЕМАТИКИ через самостоятельную работу учащихся Презентация на тему Отто Евстафьевич Коцебу

Презентация на тему Отто Евстафьевич Коцебу  Презентация на тему Вознесенский Андрей Андреевич

Презентация на тему Вознесенский Андрей Андреевич Аналіз використання трудових ресурсів і витрат на оплату праці

Аналіз використання трудових ресурсів і витрат на оплату праці Проектно-ориентированное обучение

Проектно-ориентированное обучение Dark Matter

Dark Matter Рисунки Кучеровой Ксении, 13 лет

Рисунки Кучеровой Ксении, 13 лет Венгерский академический танец

Венгерский академический танец Выполнила: Григорьева Ирина

Выполнила: Григорьева Ирина Основные теории личности: часть 1

Основные теории личности: часть 1 Что я знаю о музеях. Викторина

Что я знаю о музеях. Викторина Саба районы Шынар авылы

Саба районы Шынар авылы