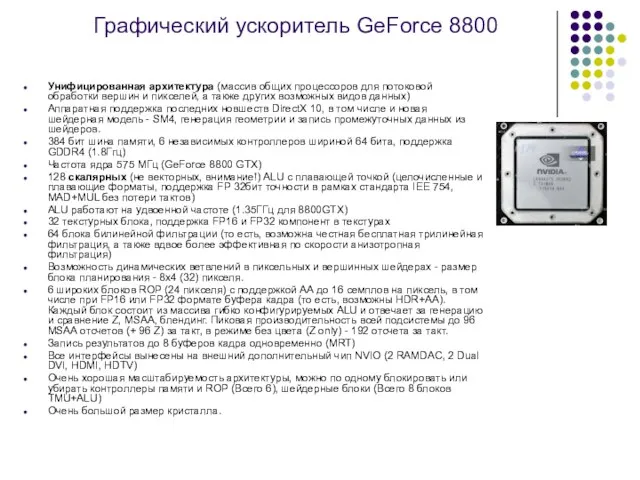

Слайд 16Графический ускоритель GeForce 8800

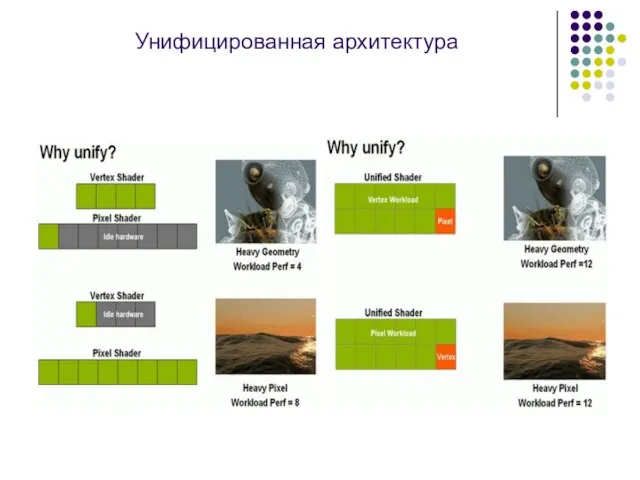

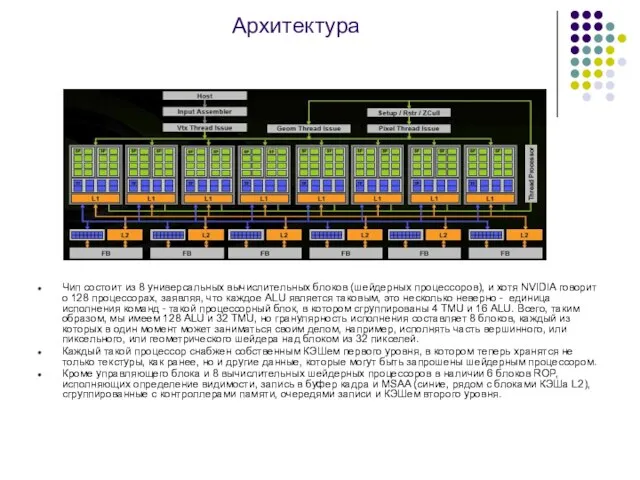

Унифицированная архитектура (массив общих процессоров для потоковой обработки вершин

и пикселей, а также других возможных видов данных)

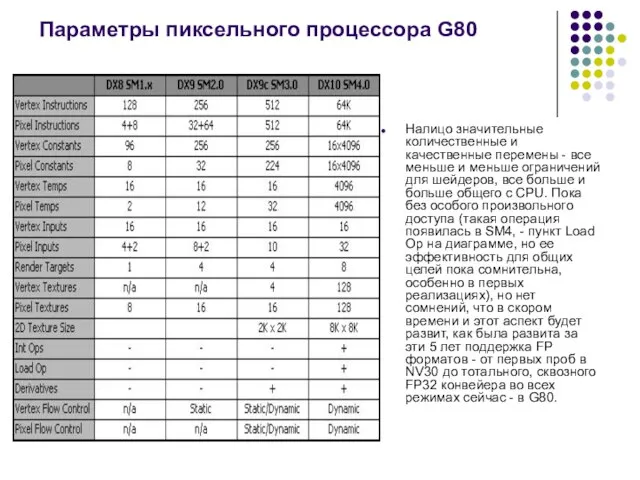

Аппаратная поддержка последних новшеств DirectX 10, в том числе и новая шейдерная модель - SM4, генерация геометрии и запись промежуточных данных из шейдеров.

384 бит шина памяти, 6 независимых контроллеров шириной 64 бита, поддержка GDDR4 (1.8Ггц)

Частота ядра 575 МГц (GeForce 8800 GTX)

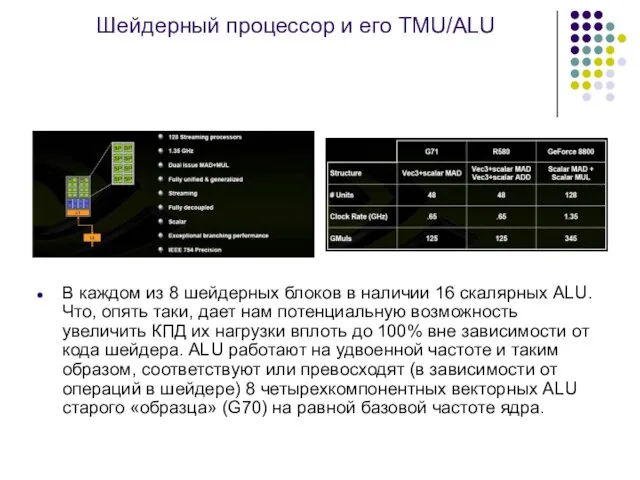

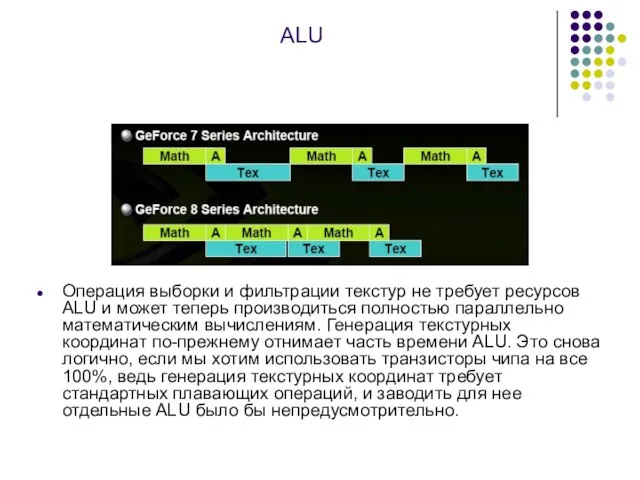

128 скалярных (не векторных, внимание!) ALU с плавающей точкой (целочисленные и плавающие форматы, поддержка FP 32бит точности в рамках стандарта IEE 754, MAD+MUL без потери тактов)

ALU работают на удвоенной частоте (1.35ГГц для 8800GTX)

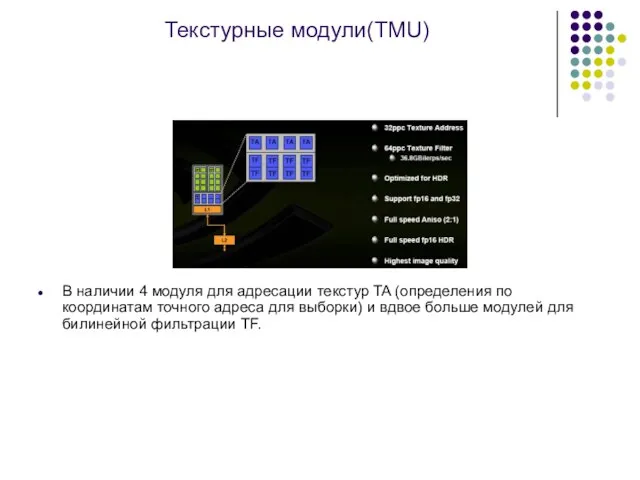

32 текстурных блока, поддержка FP16 и FP32 компонент в текстурах

64 блока билинейной фильтрации (то есть, возможна честная бесплатная трилинейная фильтрация, а также вдвое более эффективная по скорости анизотропная фильтрация)

Возможность динамических ветвлений в пиксельных и вершинных шейдерах - размер блока планирования - 8х4 (32) пикселя.

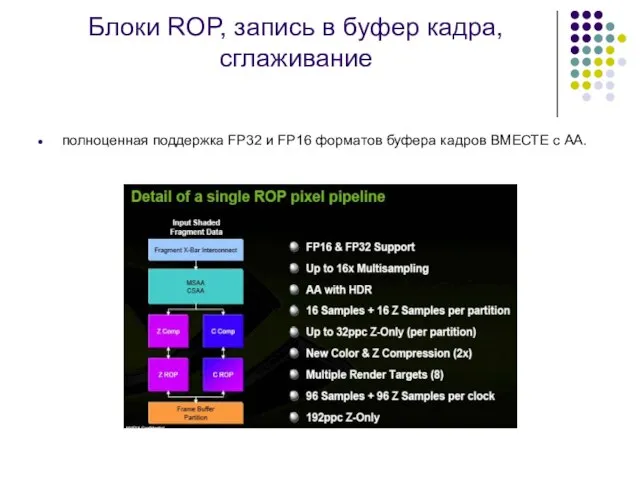

6 широких блоков ROP (24 пикселя) c поддержкой AA до 16 семплов на пиксель, в том числе при FP16 или FP32 формате буфера кадра (то есть, возможны HDR+AA). Каждый блок состоит из массива гибко конфигурируемых ALU и отвечает за генерацию и сравнение Z, MSAA, блендинг. Пиковая производительность всей подсистемы до 96 MSAA отсчетов (+ 96 Z) за такт, в режиме без цвета (Z only) - 192 отсчета за такт.

Запись результатов до 8 буферов кадра одновременно (MRT)

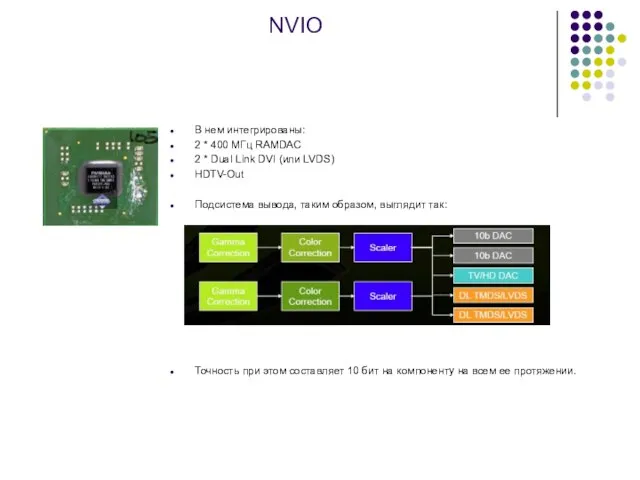

Все интерфейсы вынесены на внешний дополнительный чип NVIO (2 RAMDAC, 2 Dual DVI, HDMI, HDTV)

Очень хорошая масштабируемость архитектуры, можно по одному блокировать или убирать контроллеры памяти и ROP (Всего 6), шейдерные блоки (Всего 8 блоков TMU+ALU)

Очень большой размер кристалла.

Кроссворд «Армия»

Кроссворд «Армия» От мечты к открытию. Женщины в науке

От мечты к открытию. Женщины в науке «И снизу лед…»

«И снизу лед…» Треугольник

Треугольник Прием письменного деления многозначных чисел на однозначное число

Прием письменного деления многозначных чисел на однозначное число Сервисное локомотивное депо Чита

Сервисное локомотивное депо Чита Презентация на тему Додекаэдр

Презентация на тему Додекаэдр  Преимущества инвестирования в Республику Беларусь

Преимущества инвестирования в Республику Беларусь Понятия и виды экологического вреда и способы его возмещения

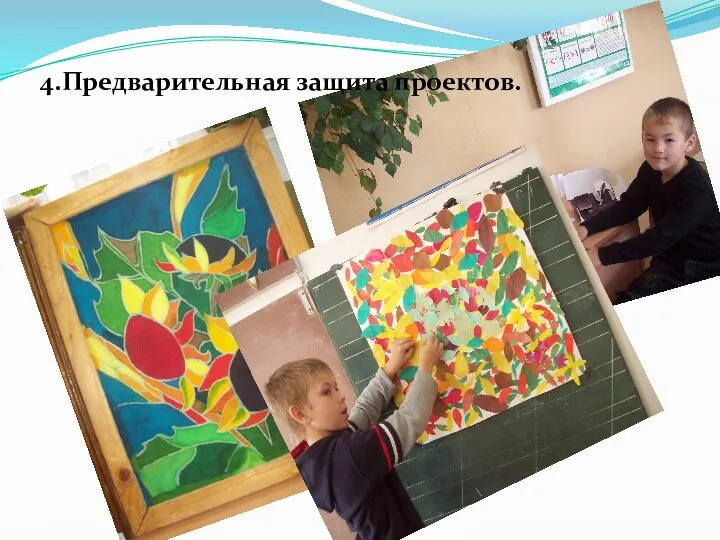

Понятия и виды экологического вреда и способы его возмещения Предварительная защита проектов

Предварительная защита проектов Цветовой круг. Домашнее задание по живописи для 1 класса ДПОП Живопись

Цветовой круг. Домашнее задание по живописи для 1 класса ДПОП Живопись Пифагор

Пифагор Школьно-родительская конференция

Школьно-родительская конференция Применение инноваций в международном налогообложении

Применение инноваций в международном налогообложении Уральский экономический район

Уральский экономический район Экзотический туризм и тропические болезни

Экзотический туризм и тропические болезни Модель Митчелла-Агле-Вуда

Модель Митчелла-Агле-Вуда Психическое развитие в подростковом возрасте

Психическое развитие в подростковом возрасте Флористика

Флористика Теория Элит

Теория Элит Готический костюм

Готический костюм Собор Парижской Богоматери

Собор Парижской Богоматери  Презентация на тему Характер

Презентация на тему Характер НТР и мировое хозяйство

НТР и мировое хозяйство Религия во время великой отечественной войны

Религия во время великой отечественной войны Трудности перевода

Трудности перевода СРАВНИТЕЛЬНЫЙ АНАЛИЗ новый федеральный закон России и правовые нормы ЕС Europeaid 119637/C/SV/RU

СРАВНИТЕЛЬНЫЙ АНАЛИЗ новый федеральный закон России и правовые нормы ЕС Europeaid 119637/C/SV/RU Кафедра органической химии

Кафедра органической химии