Содержание

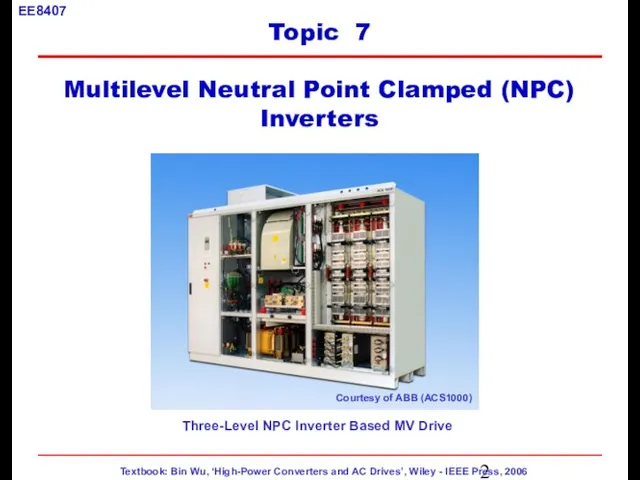

- 2. Three-Level NPC Inverter Based MV Drive Topic 7 Multilevel Neutral Point Clamped (NPC) Inverters Courtesy of

- 3. Lecture Topics Three-level NPC Inverter Space Vector Modulation Neutral Point Voltage Control High-level NPC Inverters Multilevel

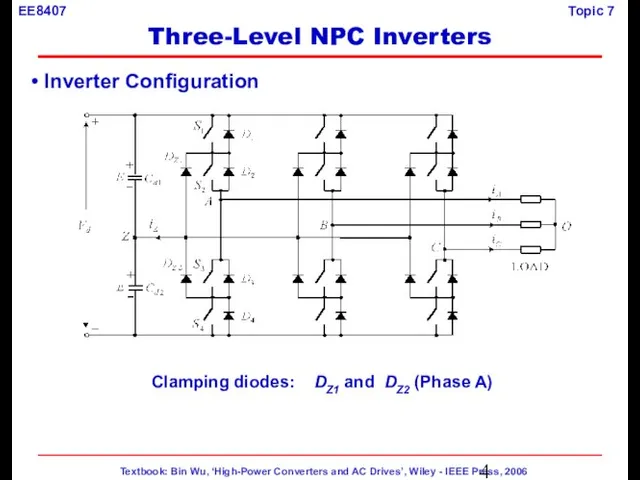

- 4. Inverter Configuration Clamping diodes: DZ1 and DZ2 (Phase A) Three-Level NPC Inverters

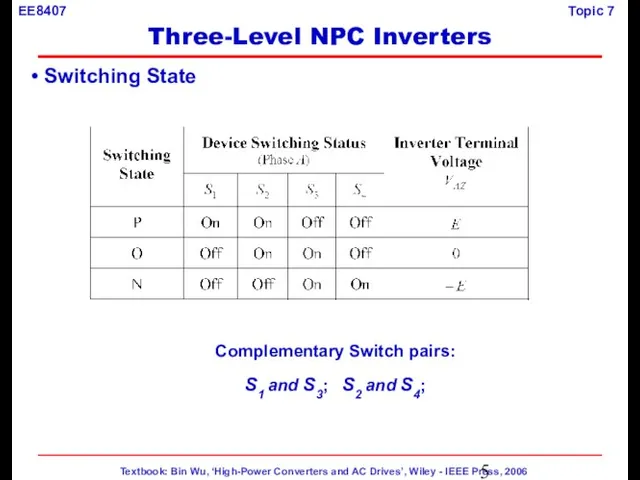

- 5. Switching State Complementary Switch pairs: S1 and S3; S2 and S4; Three-Level NPC Inverters

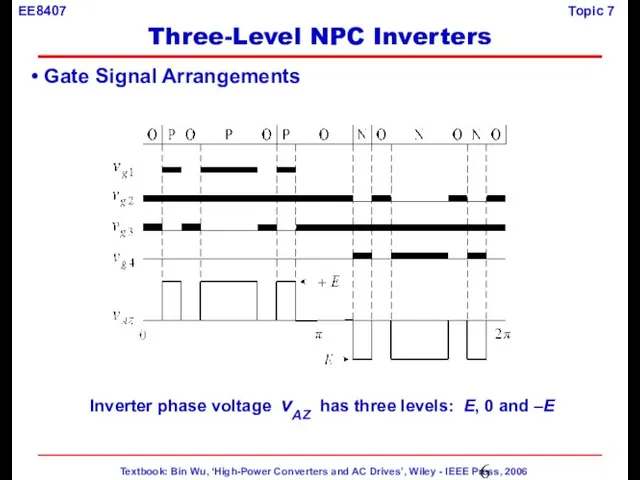

- 6. Gate Signal Arrangements Inverter phase voltage vAZ has three levels: E, 0 and –E Three-Level NPC

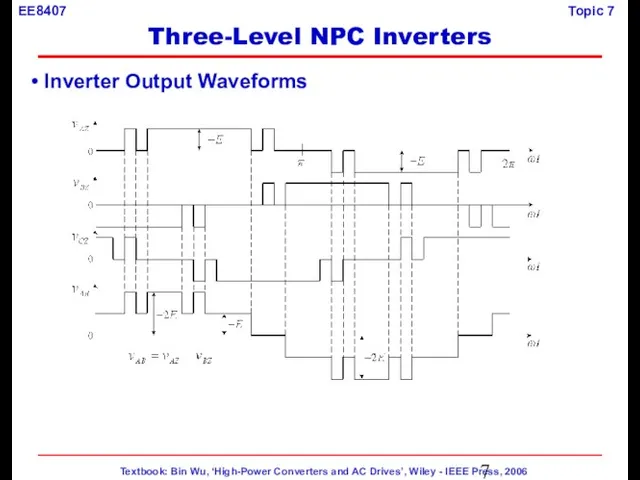

- 7. Inverter Output Waveforms Three-Level NPC Inverters

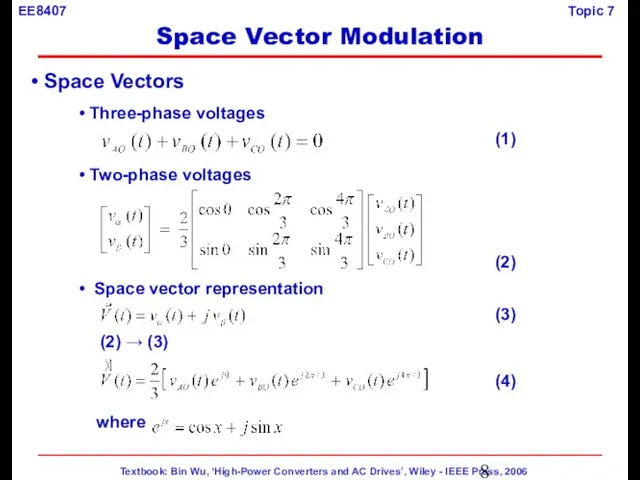

- 8. Space Vectors Three-phase voltages Two-phase voltages Space vector representation (2) → (3) where (3) (1) (2)

- 9. Switching state [POO] → on-state switches: Phase A: upper two switches [P] Phase B: middle two

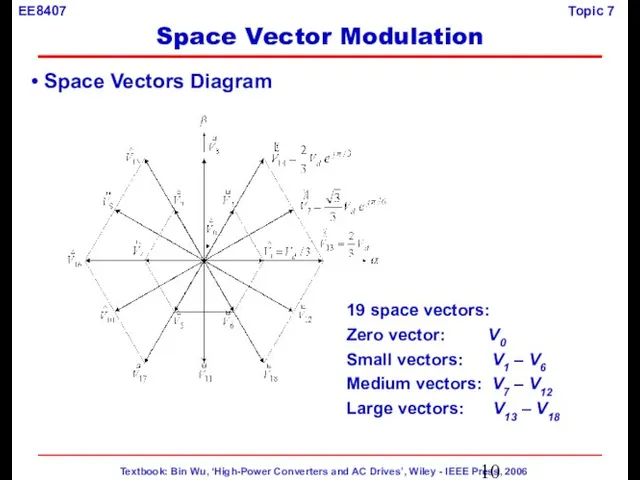

- 10. Space Vectors Diagram 19 space vectors: Zero vector: V0 Small vectors: V1 – V6 Medium vectors:

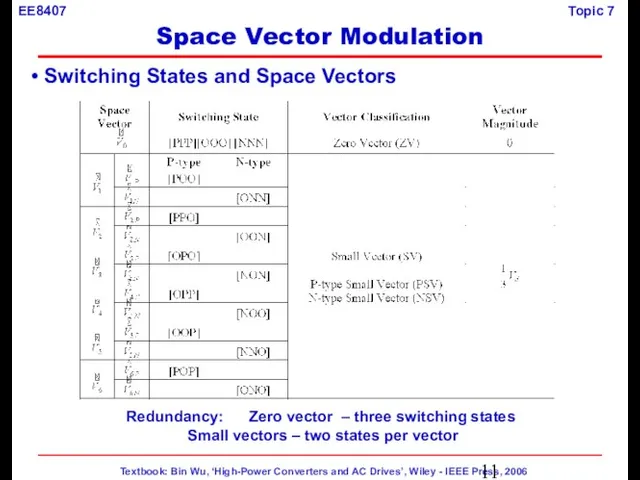

- 11. Switching States and Space Vectors Redundancy: Zero vector – three switching states Small vectors – two

- 12. No redundant switching states for medium or large vectors Switching States and Space Vectors Space Vector

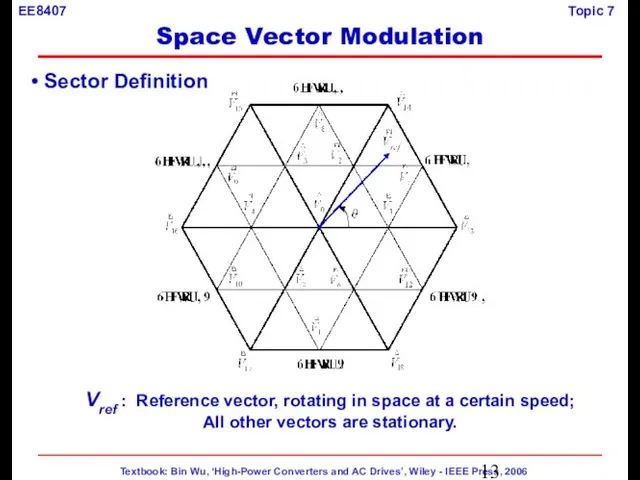

- 13. Sector Definition Vref : Reference vector, rotating in space at a certain speed; All other vectors

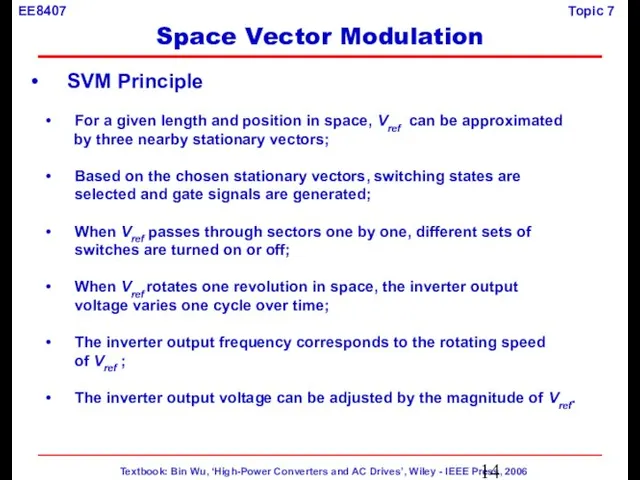

- 14. SVM Principle For a given length and position in space, Vref can be approximated by three

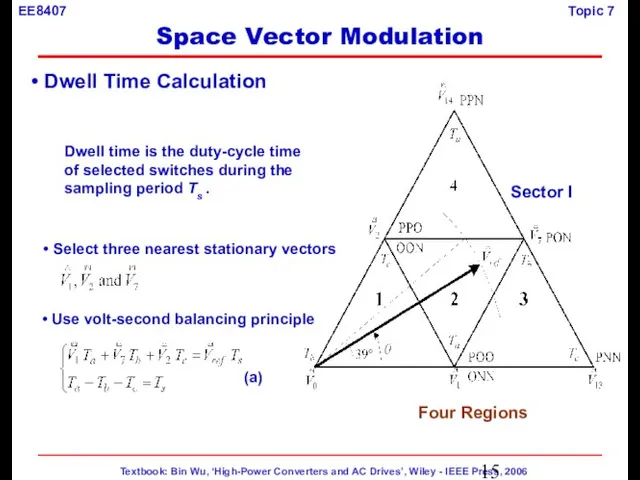

- 15. Dwell Time Calculation Use volt-second balancing principle Select three nearest stationary vectors Sector I Four Regions

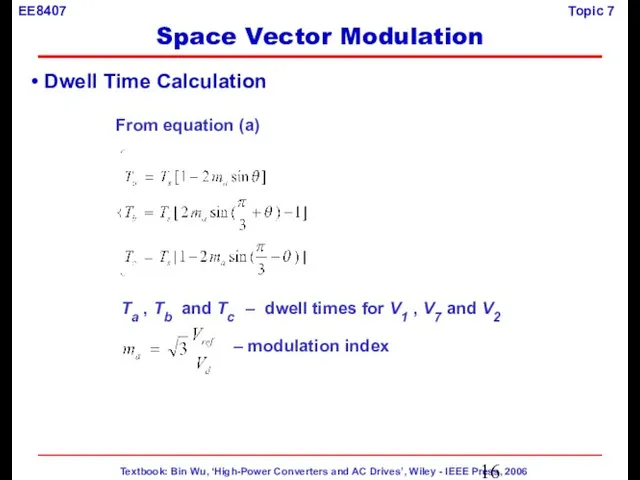

- 16. Dwell Time Calculation Ta , Tb and Tc – dwell times for V1 , V7 and

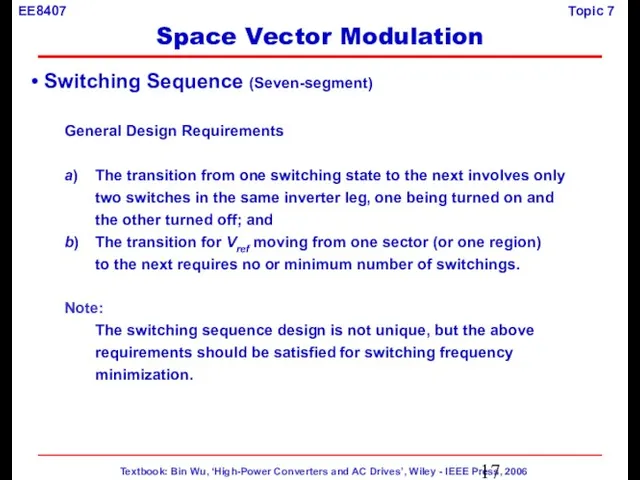

- 17. Switching Sequence (Seven-segment) General Design Requirements a) The transition from one switching state to the next

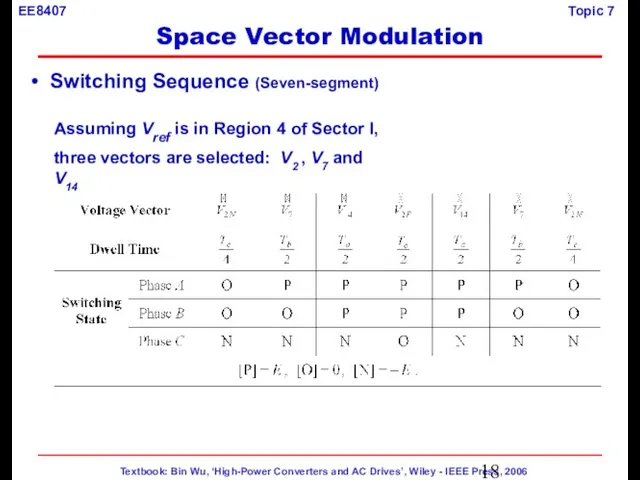

- 18. Switching Sequence (Seven-segment) Assuming Vref is in Region 4 of Sector I, three vectors are selected:

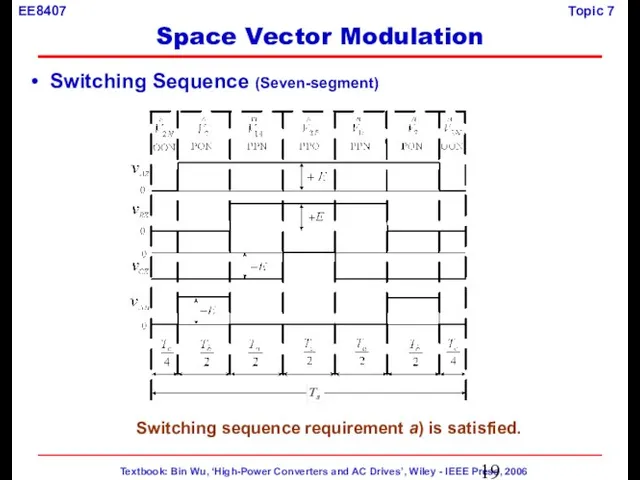

- 19. Switching Sequence (Seven-segment) Switching sequence requirement a) is satisfied. Space Vector Modulation

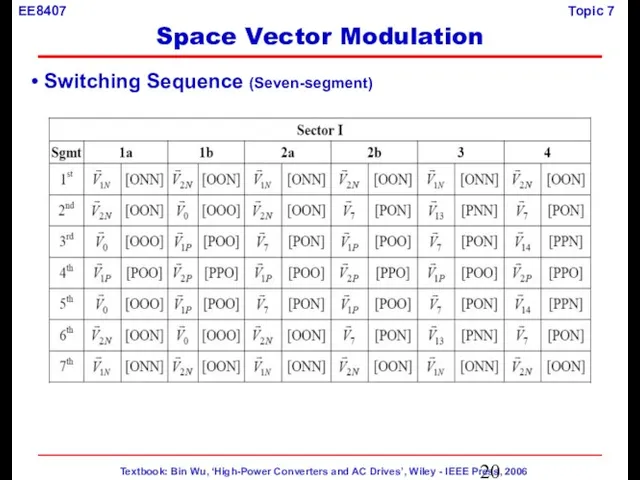

- 20. Switching Sequence (Seven-segment) Space Vector Modulation

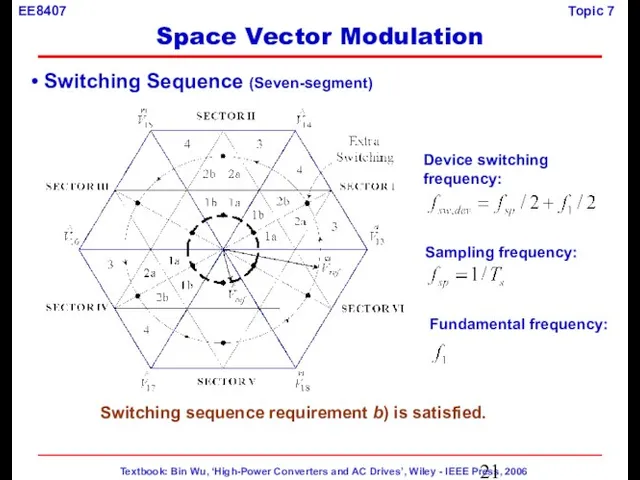

- 21. Switching Sequence (Seven-segment) Switching sequence requirement b) is satisfied. Device switching frequency: Sampling frequency: Fundamental frequency:

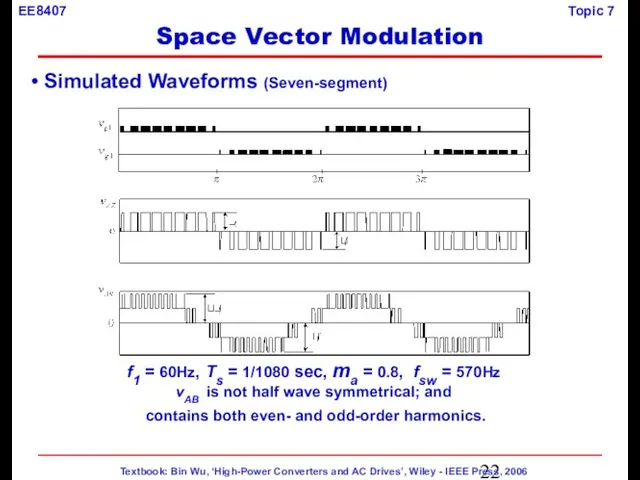

- 22. Simulated Waveforms (Seven-segment) f1 = 60Hz, Ts = 1/1080 sec, ma = 0.8, fsw = 570Hz

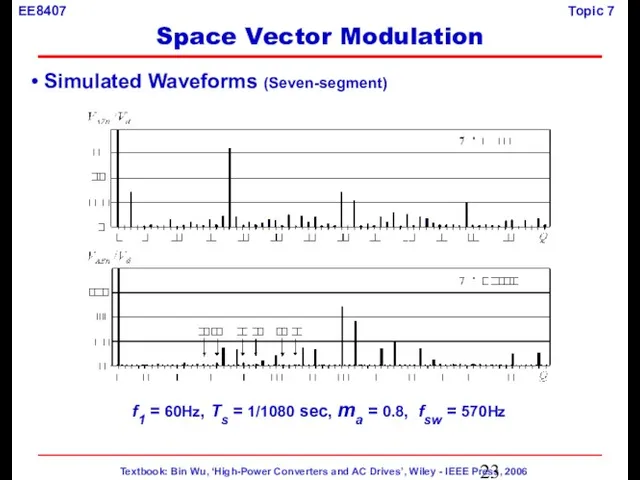

- 23. Simulated Waveforms (Seven-segment) f1 = 60Hz, Ts = 1/1080 sec, ma = 0.8, fsw = 570Hz

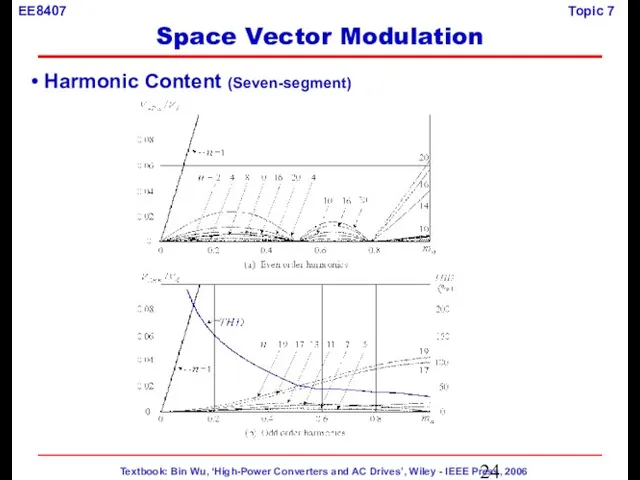

- 24. Harmonic Content (Seven-segment) Space Vector Modulation

- 25. Laboratory Prototype at Ryerson Space Vector Modulation

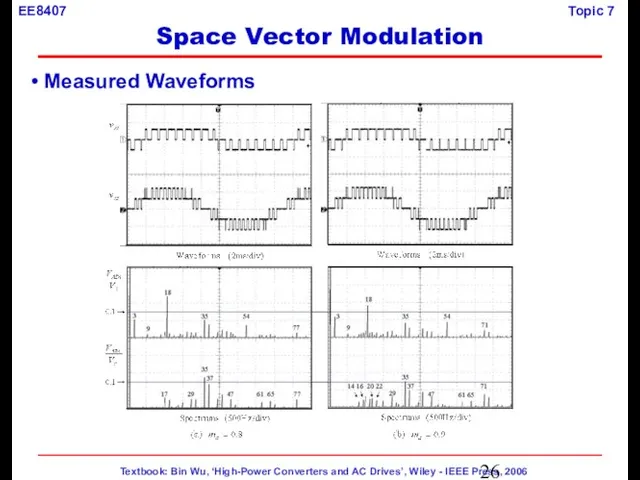

- 26. Measured Waveforms Space Vector Modulation

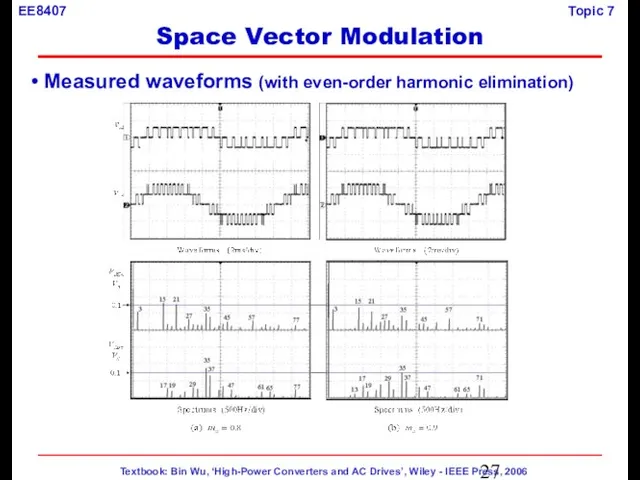

- 27. Measured waveforms (with even-order harmonic elimination) Space Vector Modulation

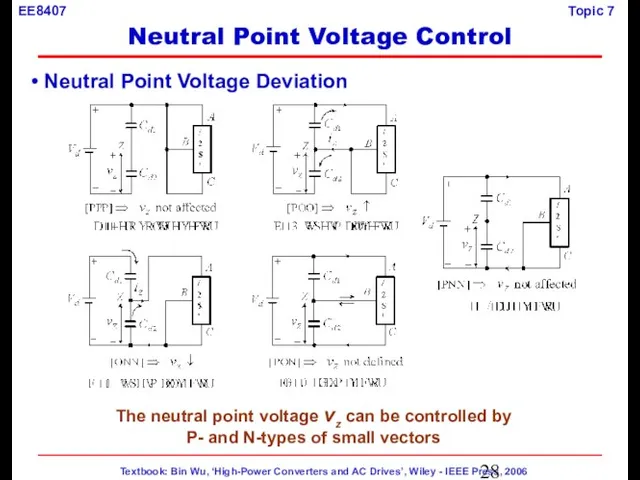

- 28. Neutral Point Voltage Deviation The neutral point voltage vz can be controlled by P- and N-types

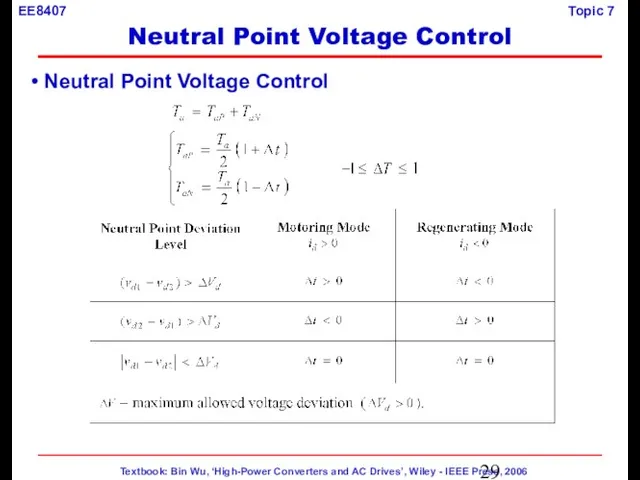

- 29. Neutral Point Voltage Control Neutral Point Voltage Control

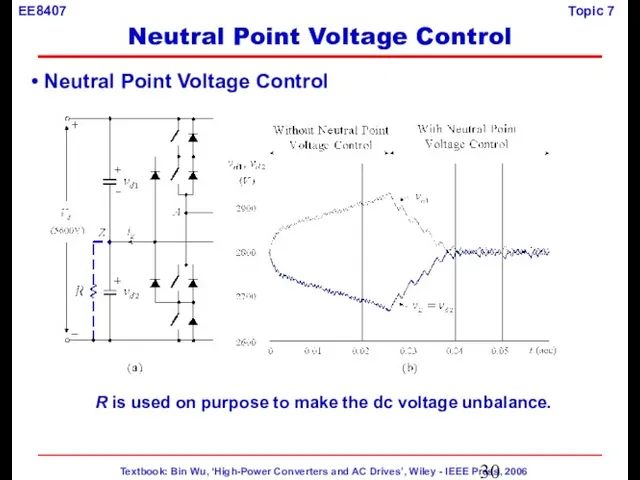

- 30. Neutral Point Voltage Control R is used on purpose to make the dc voltage unbalance. Neutral

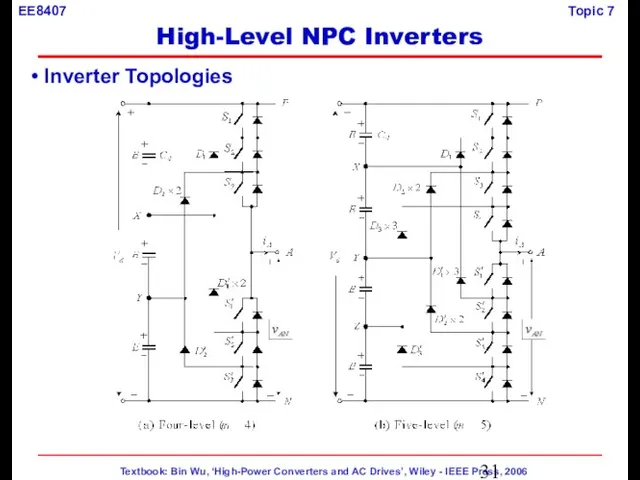

- 31. Inverter Topologies High-Level NPC Inverters

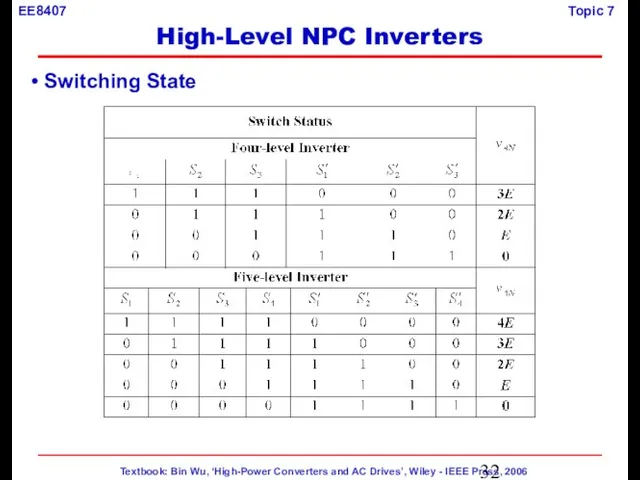

- 32. Switching State High-Level NPC Inverters

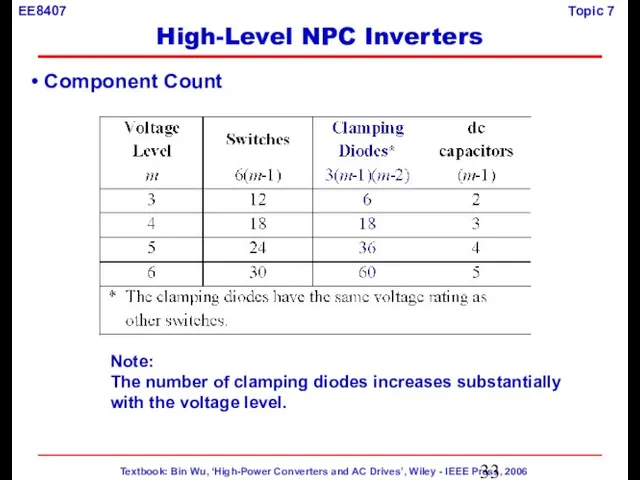

- 33. Component Count Note: The number of clamping diodes increases substantially with the voltage level. High-Level NPC

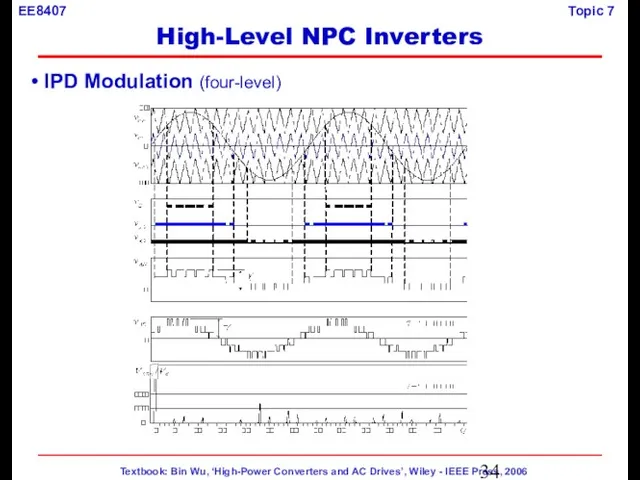

- 34. IPD Modulation (four-level) High-Level NPC Inverters

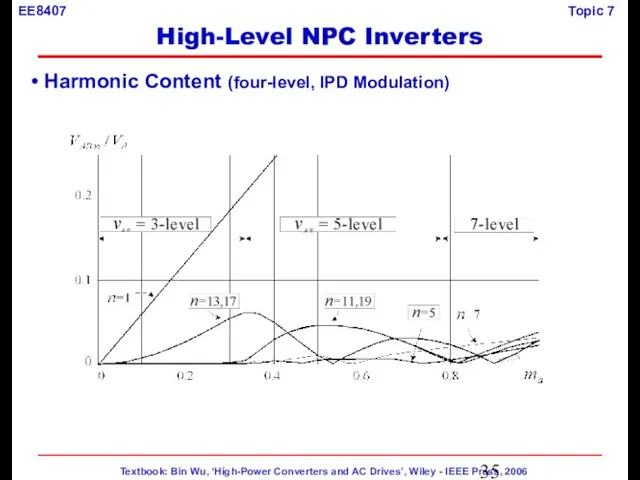

- 35. Harmonic Content (four-level, IPD Modulation) High-Level NPC Inverters

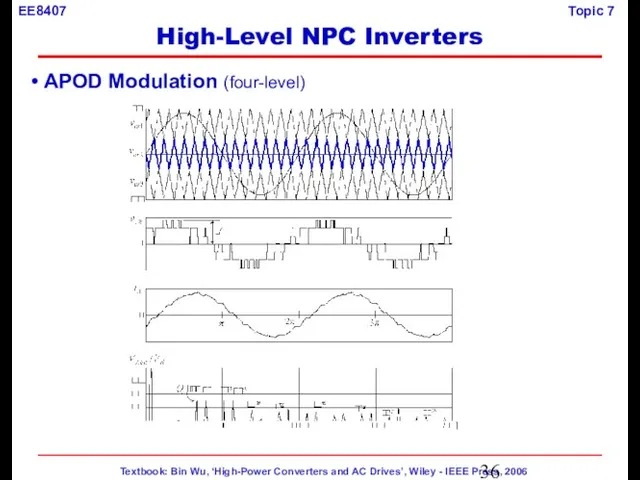

- 36. APOD Modulation (four-level) High-Level NPC Inverters

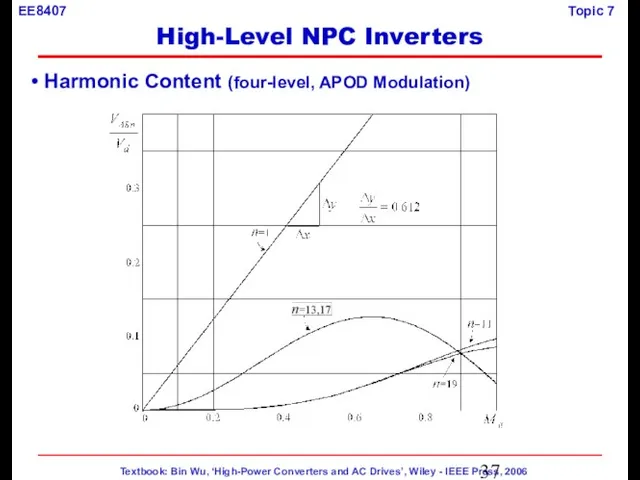

- 37. Harmonic Content (four-level, APOD Modulation) High-Level NPC Inverters

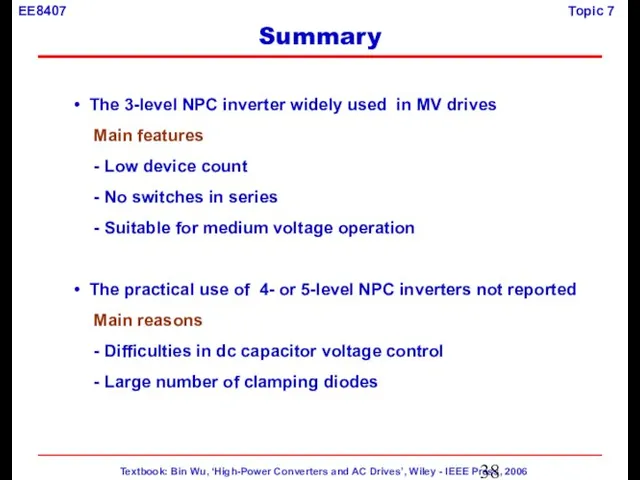

- 38. The 3-level NPC inverter widely used in MV drives Main features - Low device count -

- 40. Скачать презентацию

![Switching state [POO] → on-state switches: Phase A: upper two switches [P]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/381591/slide-8.jpg)

Помогите маме

Помогите маме Опыт строительства мини-метанольных установок на газовом месторождении

Опыт строительства мини-метанольных установок на газовом месторождении Урок как форма повышения профессионального мастерства учителя

Урок как форма повышения профессионального мастерства учителя Размещение и миграции населения, их виды

Размещение и миграции населения, их виды Glasgow’s History

Glasgow’s History Танковая армия РФ. История создания

Танковая армия РФ. История создания Поселок Шексна

Поселок Шексна «Новые интернет-решения в сфере ипотечного кредитования»

«Новые интернет-решения в сфере ипотечного кредитования» What Do We Wear?

What Do We Wear? АВТОМАТИЗИРОВАННЫЙ УЧЕТ АРХИВНЫХ ДОКУМЕНТОВ

АВТОМАТИЗИРОВАННЫЙ УЧЕТ АРХИВНЫХ ДОКУМЕНТОВ Исследование крови под темнопольным микроскопом

Исследование крови под темнопольным микроскопом Правила по технике безопасности

Правила по технике безопасности Любовь в творчестве И.А. Бунина

Любовь в творчестве И.А. Бунина Презентация на тему Архитектура средневекового города

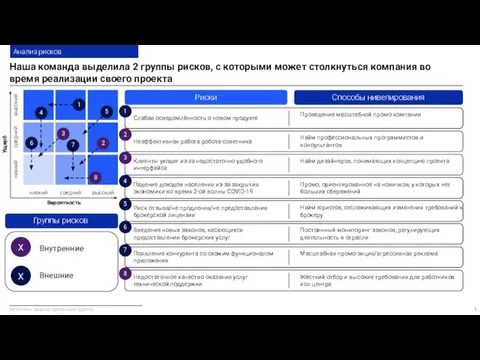

Презентация на тему Архитектура средневекового города  Диаграмма Ганта и Матрица рисков

Диаграмма Ганта и Матрица рисков Презентация на тему Молочная промышленность России

Презентация на тему Молочная промышленность России  Организация работы Муниципальных библиотек г.Перми в условиях Федерального Закона №152-ФЗ «О персональных данных»

Организация работы Муниципальных библиотек г.Перми в условиях Федерального Закона №152-ФЗ «О персональных данных»  { Смутное время 1598-1613 гг. и его последствия Великий Новгород и Шведское королевство. - презентация

{ Смутное время 1598-1613 гг. и его последствия Великий Новгород и Шведское королевство. - презентация Основа тактики игры в волейбол

Основа тактики игры в волейбол История профсоюзного движения. Знаковые события

История профсоюзного движения. Знаковые события Интернет- адрес http:// model.vscc.ac.ru _______________________________________________ ЭКСПЕРТНАЯ ОБУЧАЮЩАЯ СИСТЕМА Модель управления учебным курсом на

Интернет- адрес http:// model.vscc.ac.ru _______________________________________________ ЭКСПЕРТНАЯ ОБУЧАЮЩАЯ СИСТЕМА Модель управления учебным курсом на Эффективная защита женщин и детей от домашнего насилия

Эффективная защита женщин и детей от домашнего насилия Экспрессионизм. Мировая культура ХХ века

Экспрессионизм. Мировая культура ХХ века Опустынивание

Опустынивание Проблемы духовно-нравственного воспитания подрастающего поколения в современной России

Проблемы духовно-нравственного воспитания подрастающего поколения в современной России Презентация на тему Внутреннее строение рыб

Презентация на тему Внутреннее строение рыб  О развитии инфраструктуры поддержки субъектов малого и среднего предпринимательства в Ставропольском крае

О развитии инфраструктуры поддержки субъектов малого и среднего предпринимательства в Ставропольском крае 7 кл. Урок 2. История Таблицы (1)

7 кл. Урок 2. История Таблицы (1)