Содержание

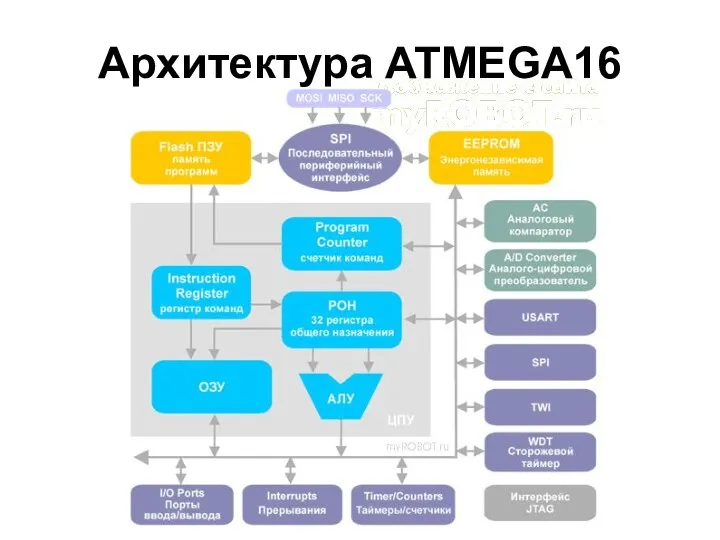

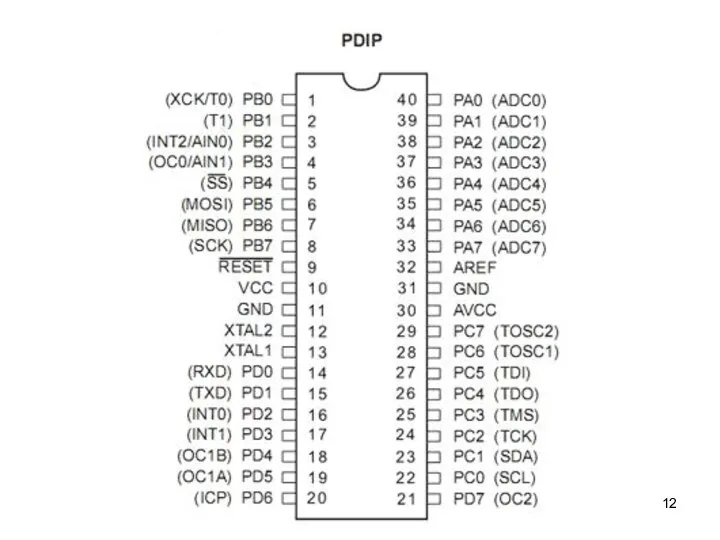

- 2. Архитектура ATMEGA16

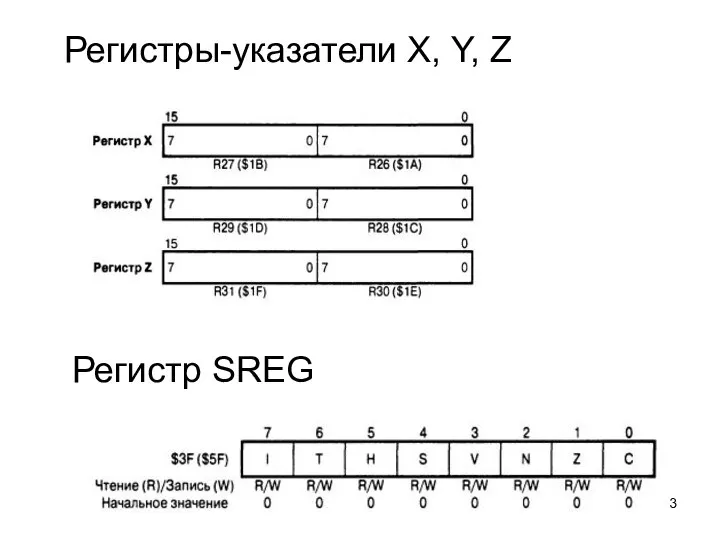

- 3. Регистры-указатели X, Y, Z Регистр SREG

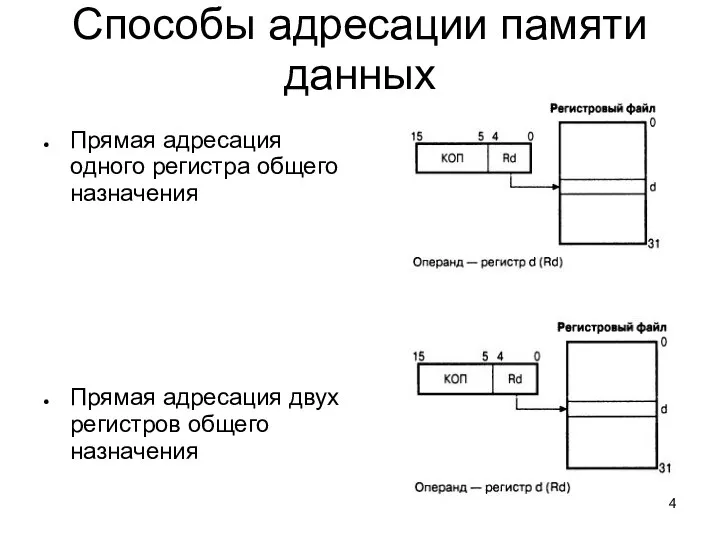

- 4. Способы адресации памяти данных Прямая адресация одного регистра общего назначения Прямая адресация двух регистров общего назначения

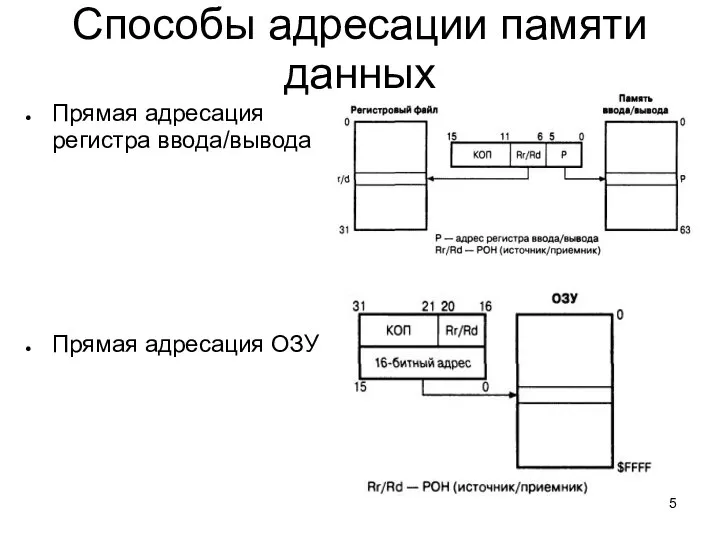

- 5. Способы адресации памяти данных Прямая адресация регистра ввода/вывода Прямая адресация ОЗУ

- 6. Простая косвенная адресация Относительная косвенная адресация Способы адресации памяти данных

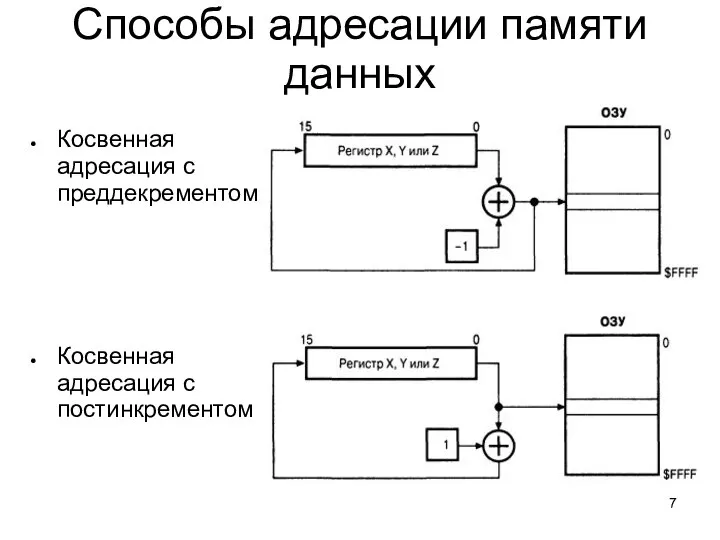

- 7. Косвенная адресация с преддекрементом Косвенная адресация с постинкрементом Способы адресации памяти данных

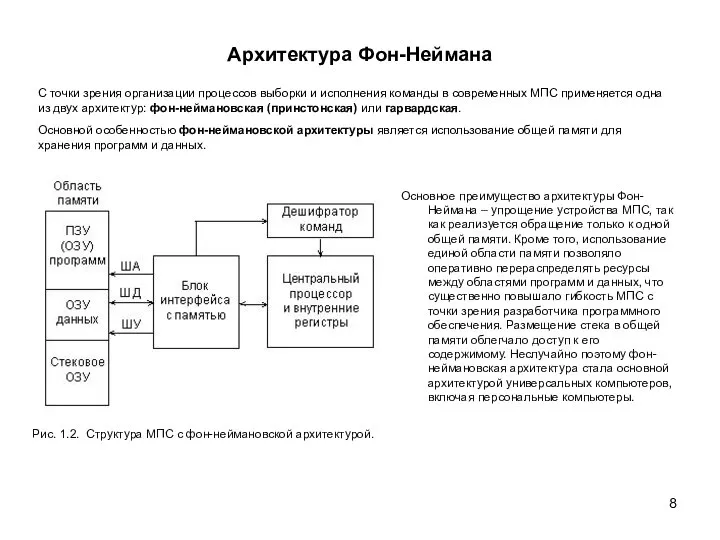

- 8. Архитектура Фон-Неймана С точки зрения организации процессов выборки и исполнения команды в современных МПС применяется одна

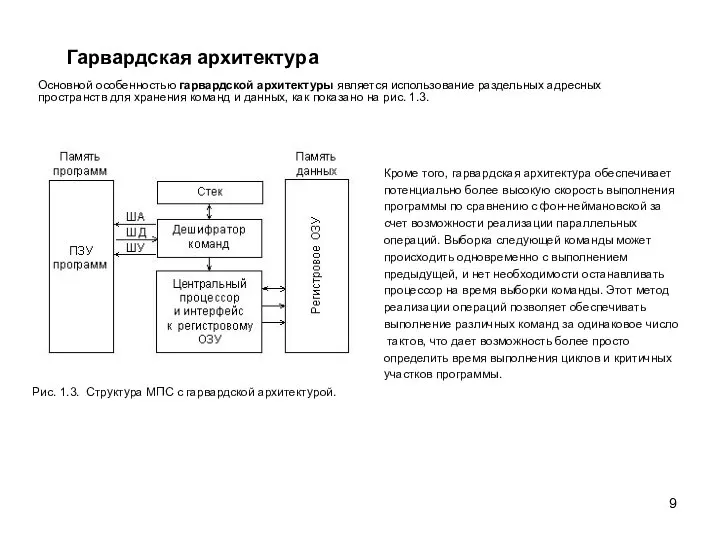

- 9. Гарвардская архитектура Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных,

- 10. Архитектура с общей шиной Так же эти два типа архитектуры различаются по количеству используемых шин, и

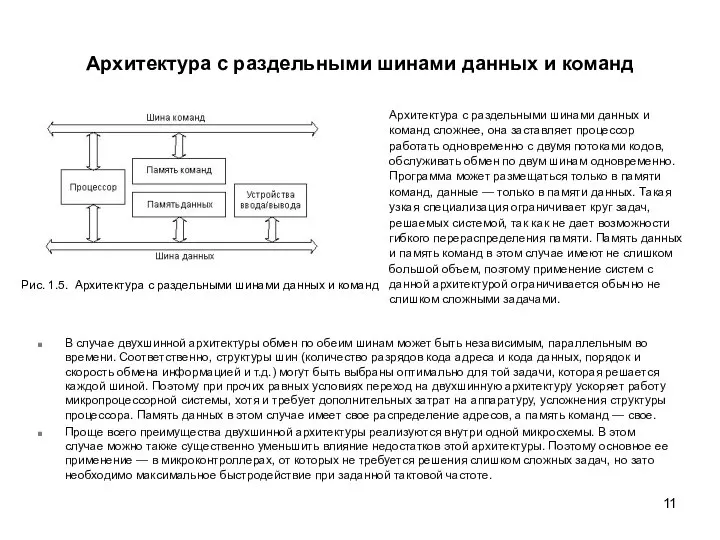

- 11. Архитектура с раздельными шинами данных и команд Рис. 1.5. Архитектура с раздельными шинами данных и команд

- 13. Таблица векторов прерывания

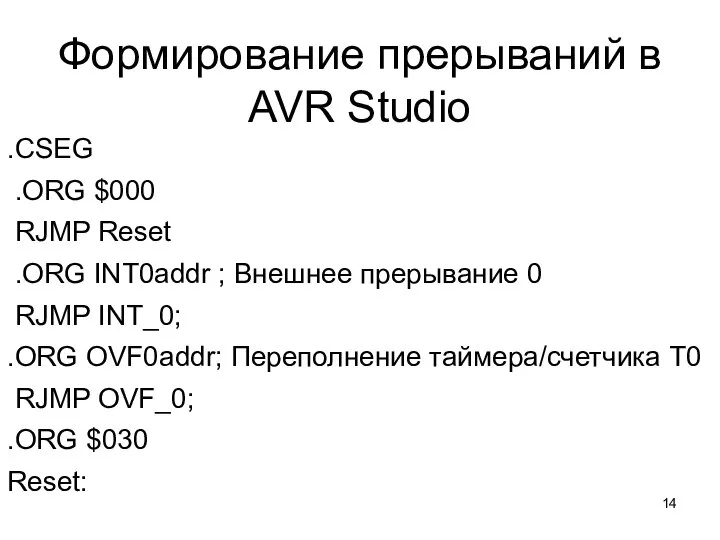

- 14. Формирование прерываний в AVR Studio .CSEG .ORG $000 RJMP Reset .ORG INT0addr ; Внешнее прерывание 0

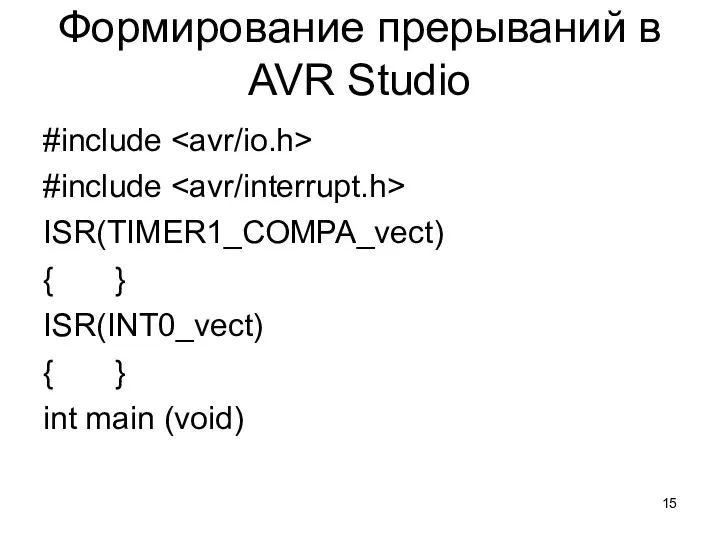

- 15. #include #include ISR(TIMER1_COMPA_vect) { } ISR(INT0_vect) { } int main (void) Формирование прерываний в AVR Studio

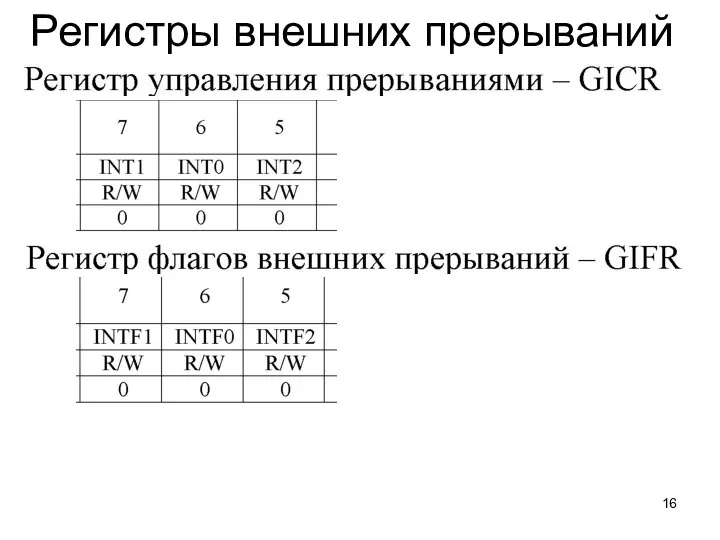

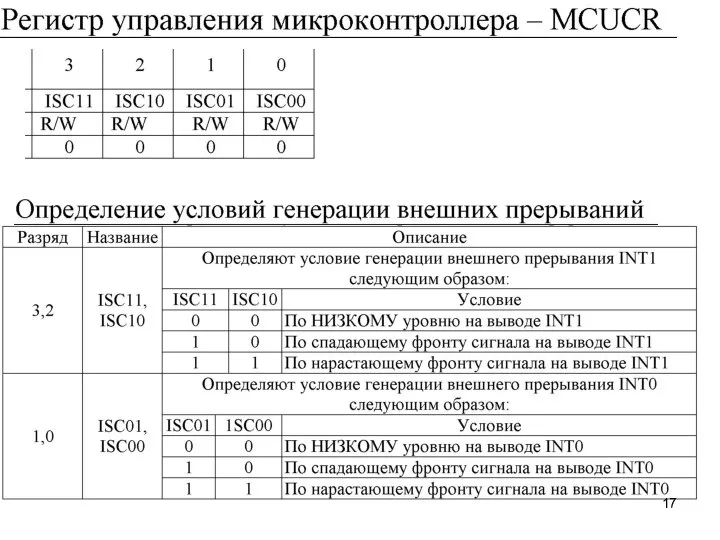

- 16. Регистры внешних прерываний

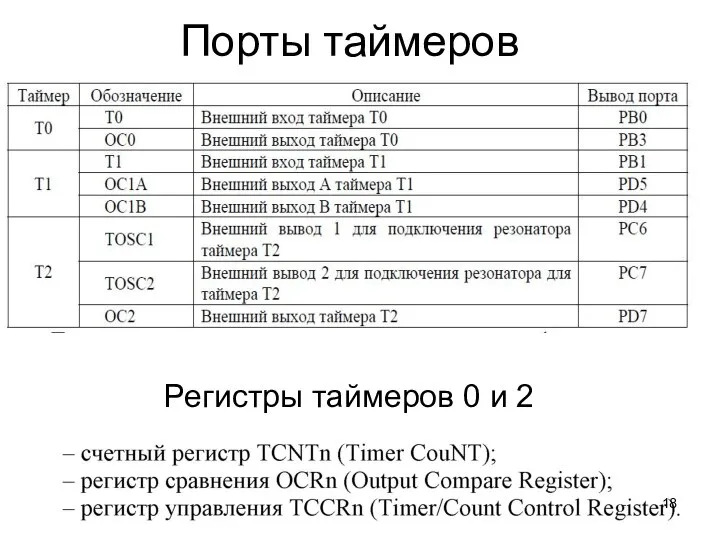

- 18. Порты таймеров Регистры таймеров 0 и 2

- 19. Режимы работы таймеров

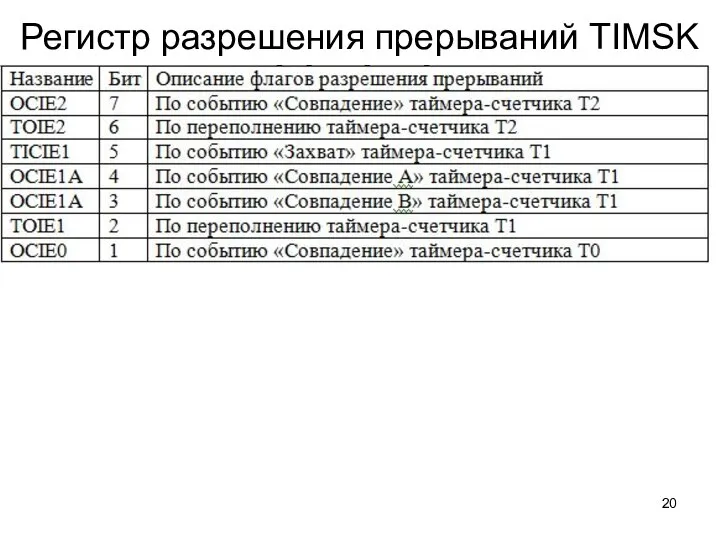

- 20. Регистр разрешения прерываний TIMSK

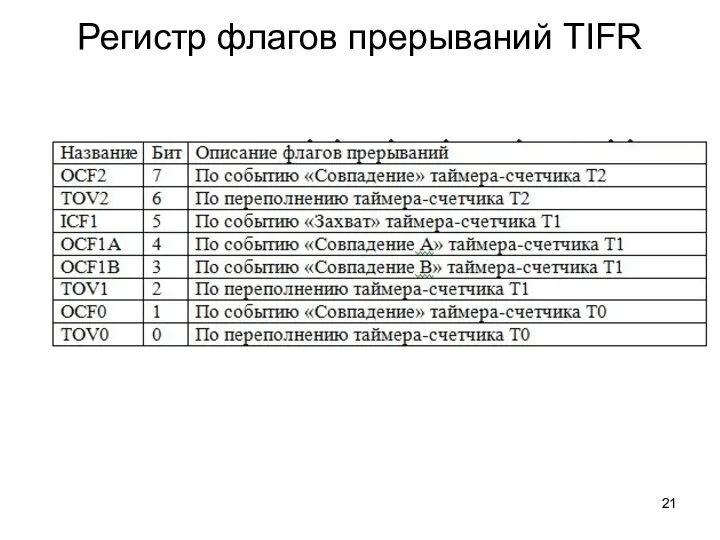

- 21. Регистр флагов прерываний TIFR

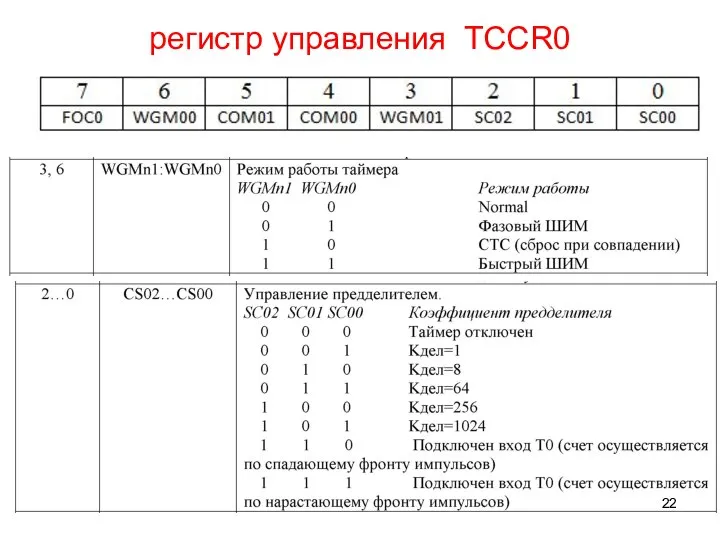

- 22. регистр управления TCCR0

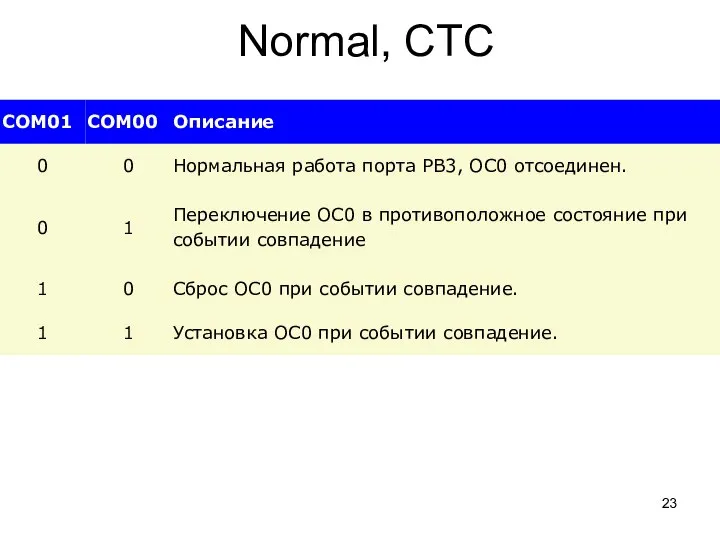

- 23. Normal, CTC

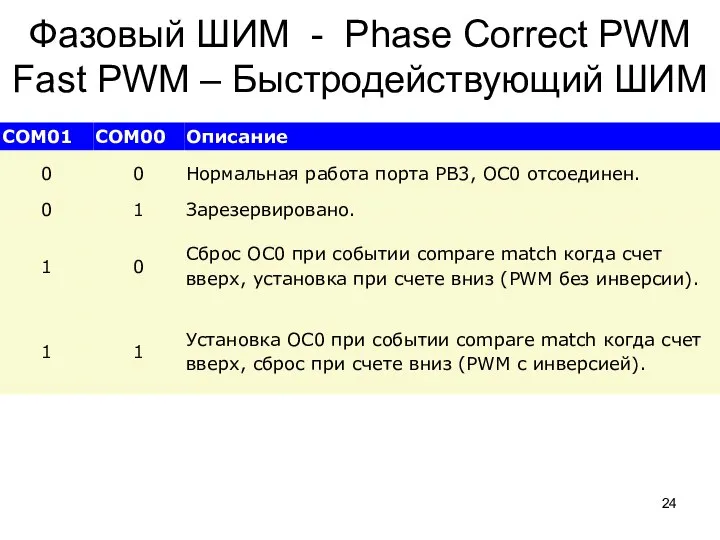

- 24. Фазовый ШИМ - Phase Correct PWM Fast PWM – Быстродействующий ШИМ

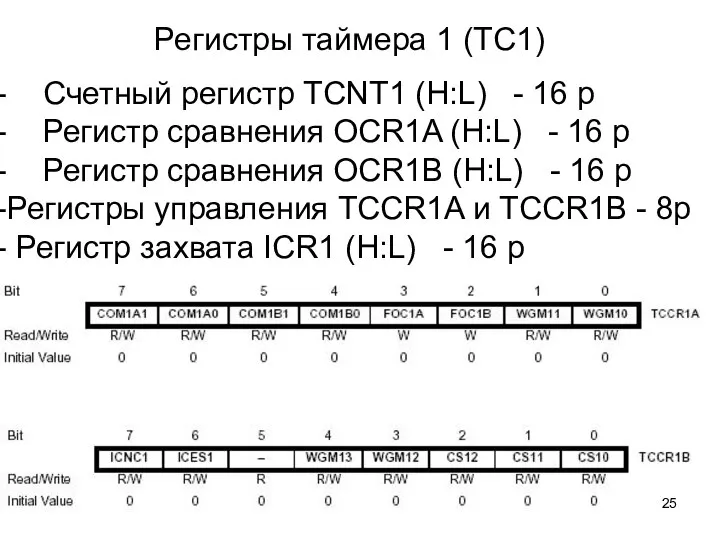

- 25. Регистры таймера 1 (TC1) Счетный регистр TCNT1 (H:L) - 16 p Регистр сравнения OCR1A (H:L) -

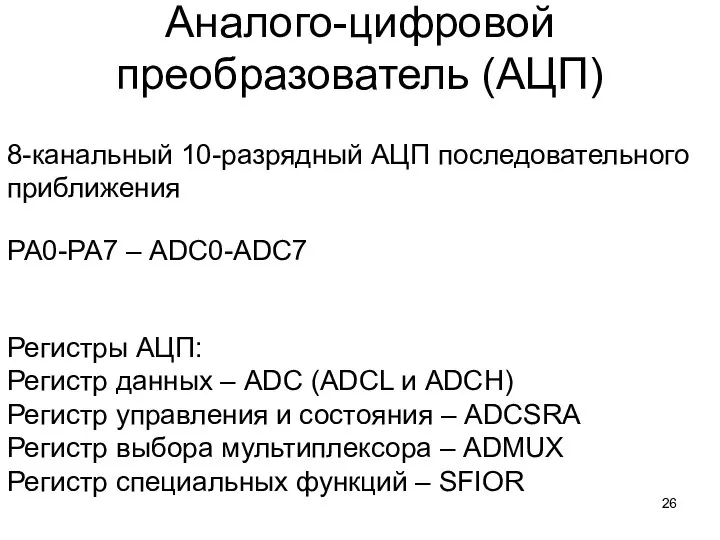

- 26. Аналого-цифровой преобразователь (АЦП) 8-канальный 10-разрядный АЦП последовательного приближения РА0-РА7 – ADC0-ADC7 Регистры АЦП: Регистр данных –

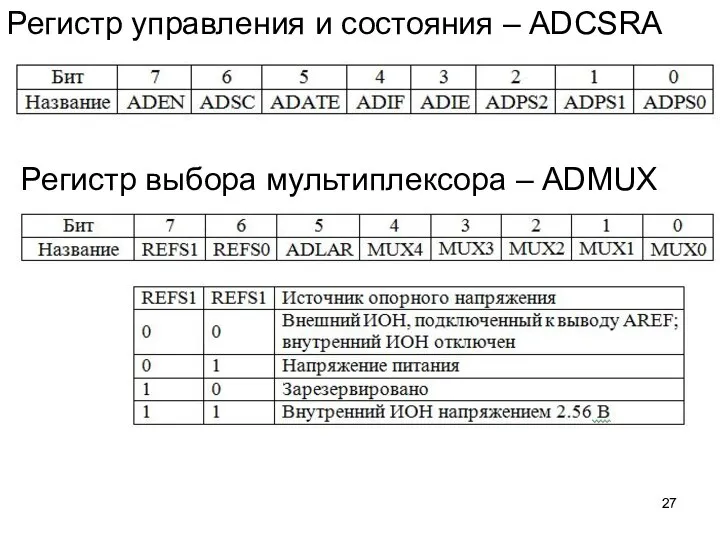

- 27. Регистр управления и состояния – ADCSRА Регистр выбора мультиплексора – ADMUX

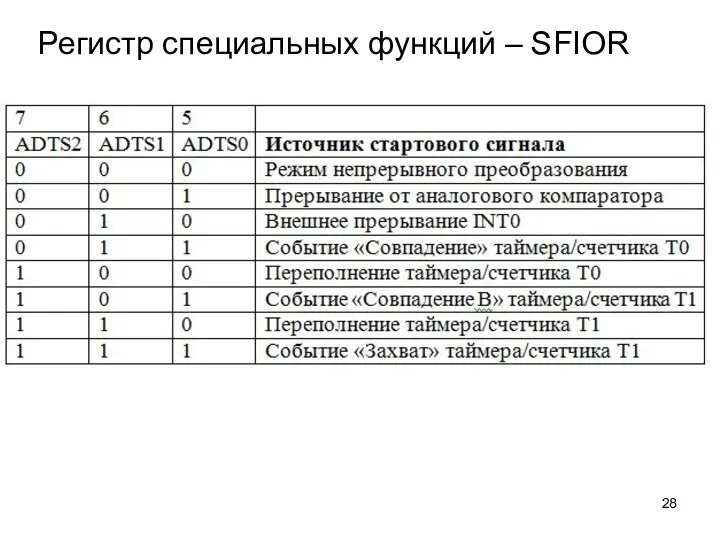

- 28. Регистр специальных функций – SFIOR

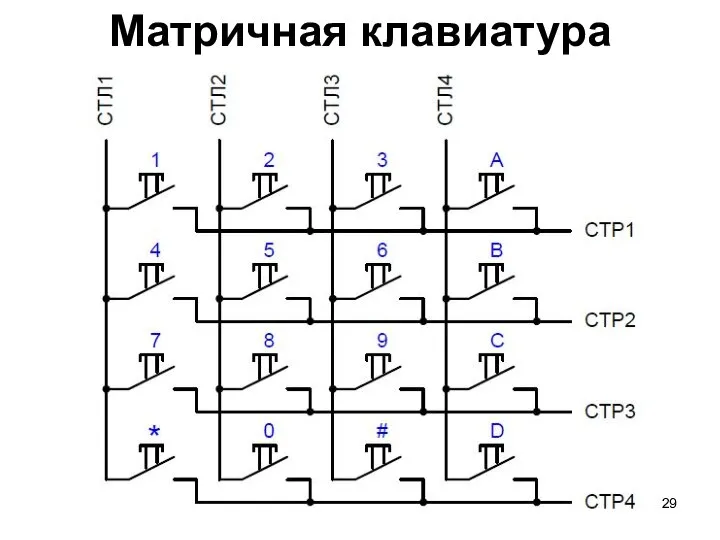

- 29. Матричная клавиатура

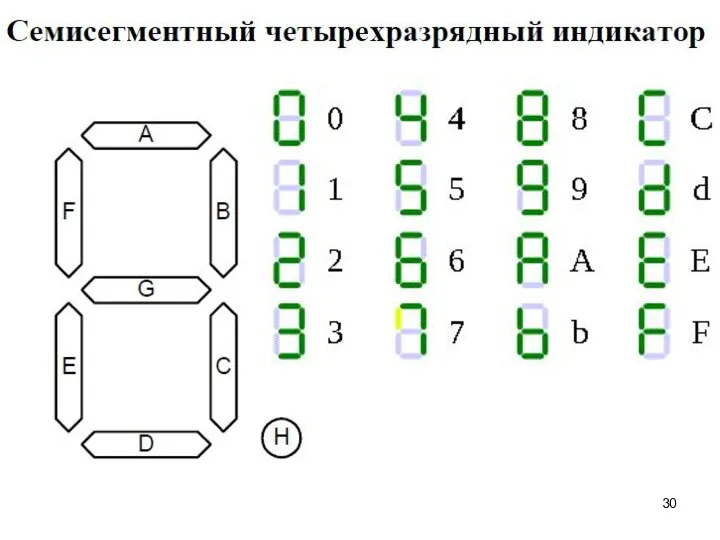

- 31. Схемы включения светодиодов

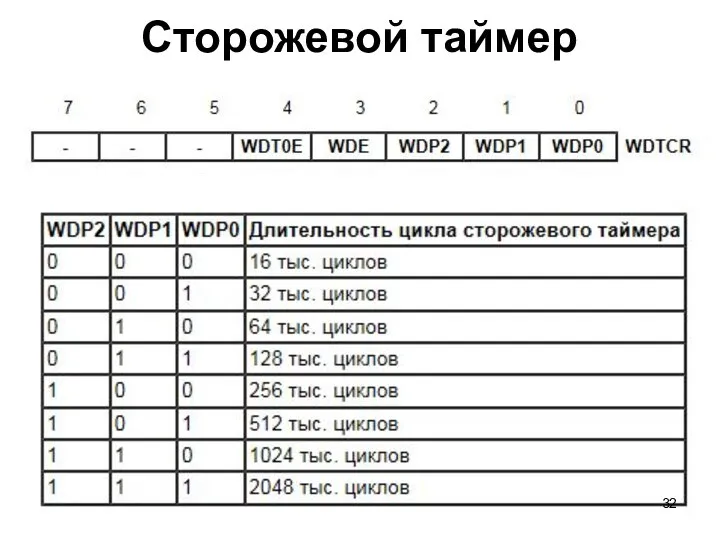

- 32. Сторожевой таймер

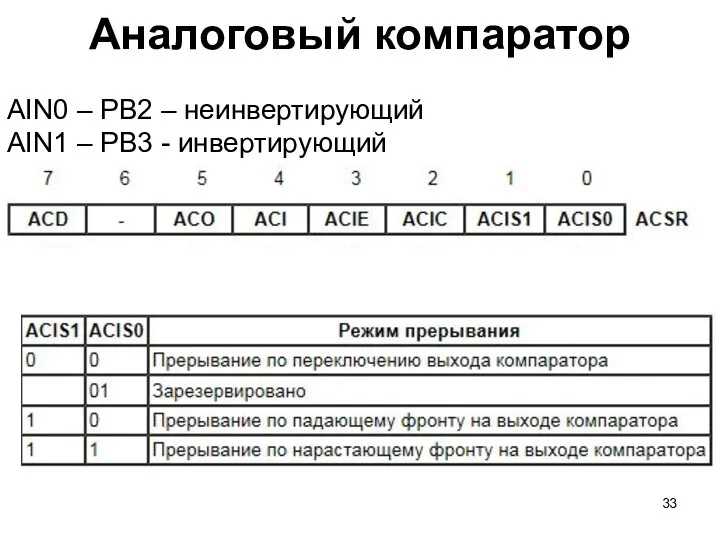

- 33. Аналоговый компаратор AIN0 – PB2 – неинвертирующий AIN1 – PB3 - инвертирующий

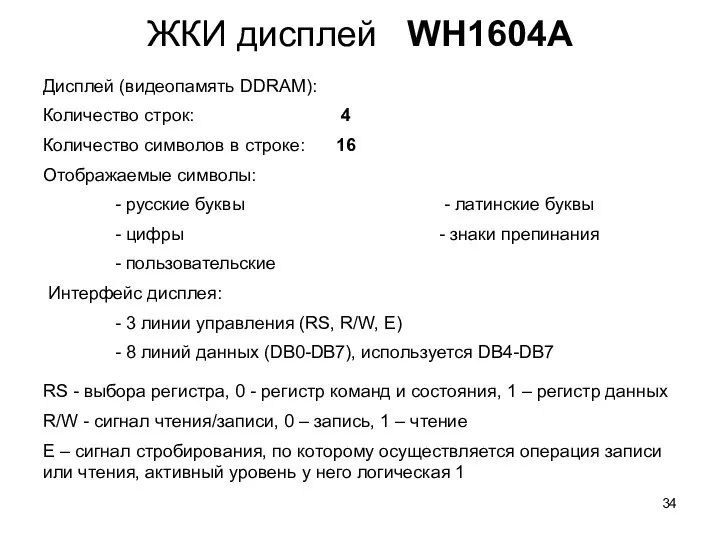

- 34. ЖКИ дисплей WH1604A Дисплей (видеопамять DDRAM): Количество строк: 4 Количество символов в строке: 16 Отображаемые символы:

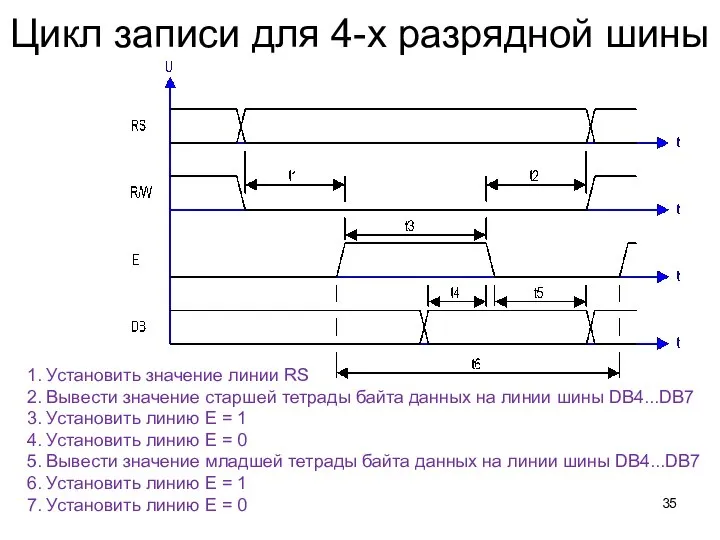

- 35. Цикл записи для 4-х разрядной шины 1. Установить значение линии RS 2. Вывести значение старшей тетрады

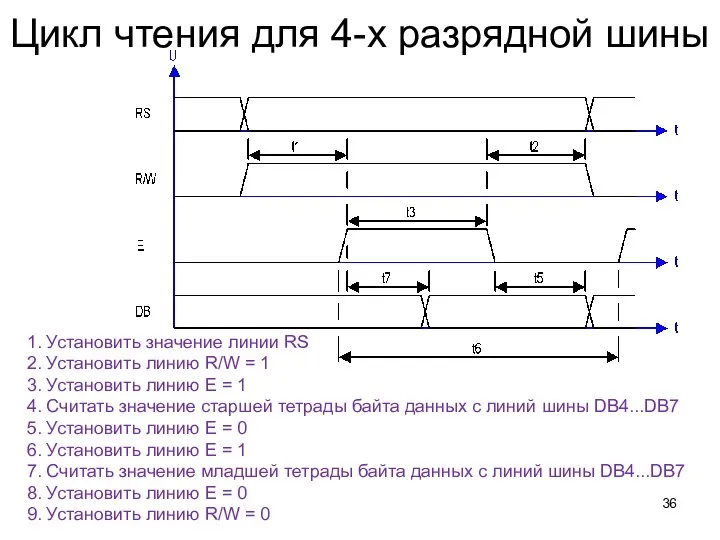

- 36. Цикл чтения для 4-х разрядной шины 1. Установить значение линии RS 2. Установить линию R/W =

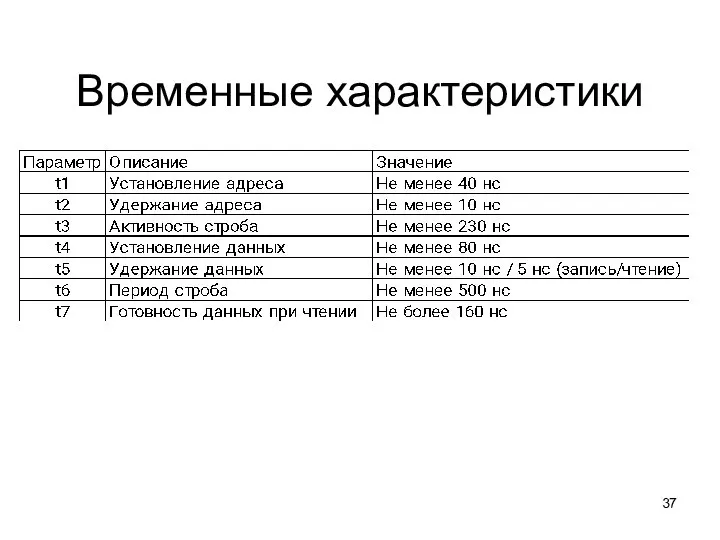

- 37. Временные характеристики

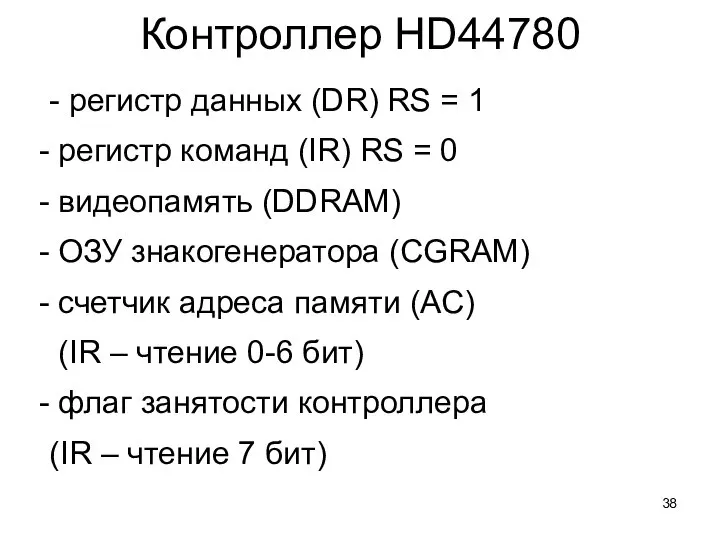

- 38. Контроллер HD44780 - регистр данных (DR) RS = 1 регистр команд (IR) RS = 0 видеопамять

- 39. регистр команд

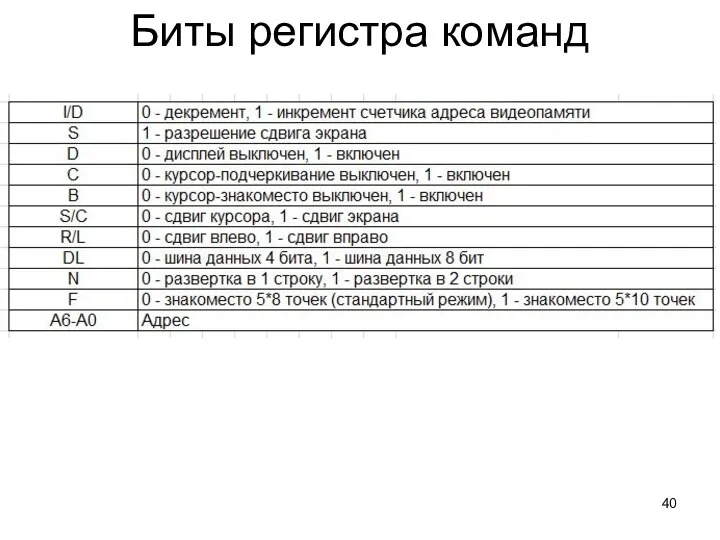

- 40. Биты регистра команд

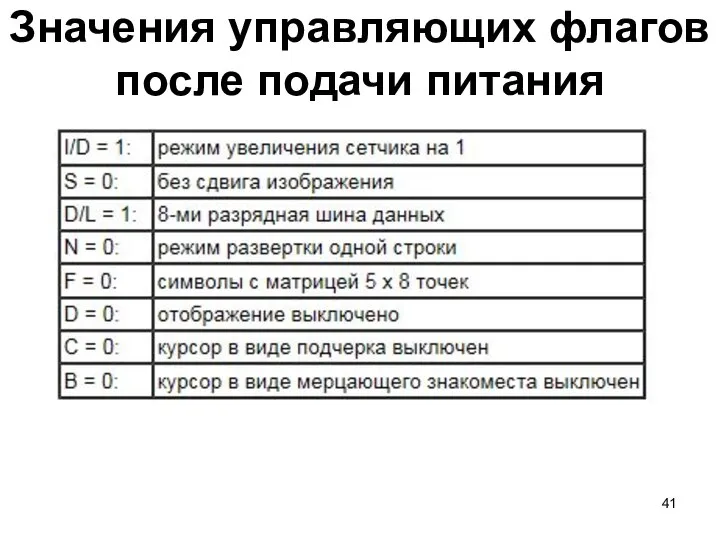

- 41. Значения управляющих флагов после подачи питания

- 42. Пользовательские символы

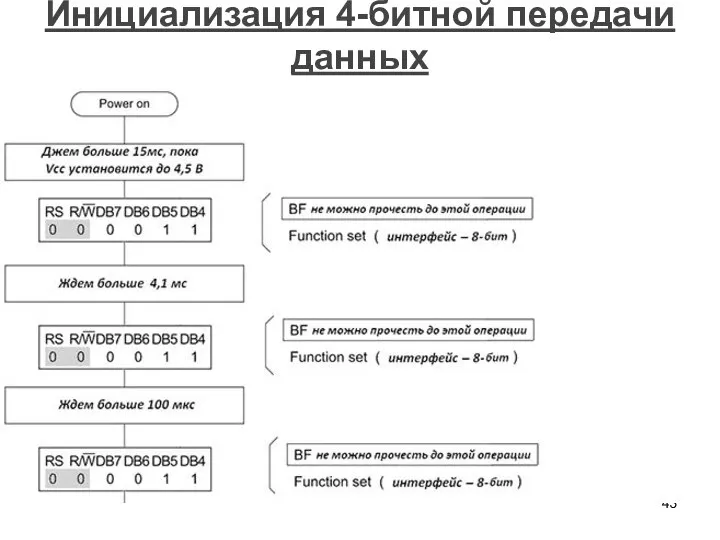

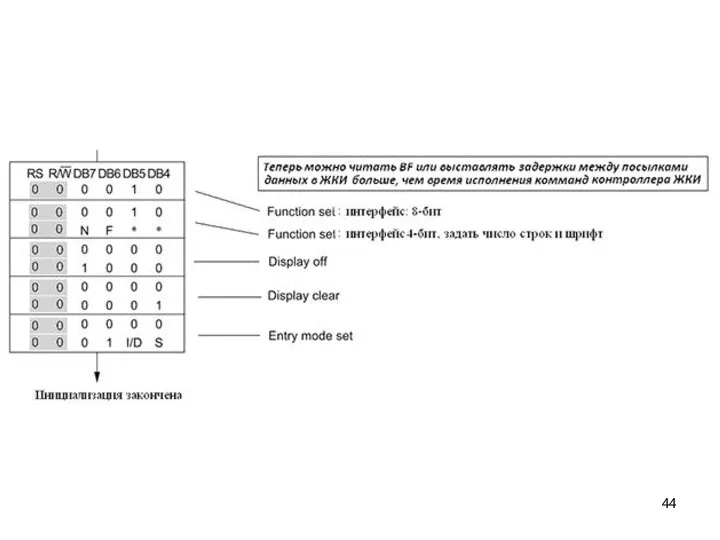

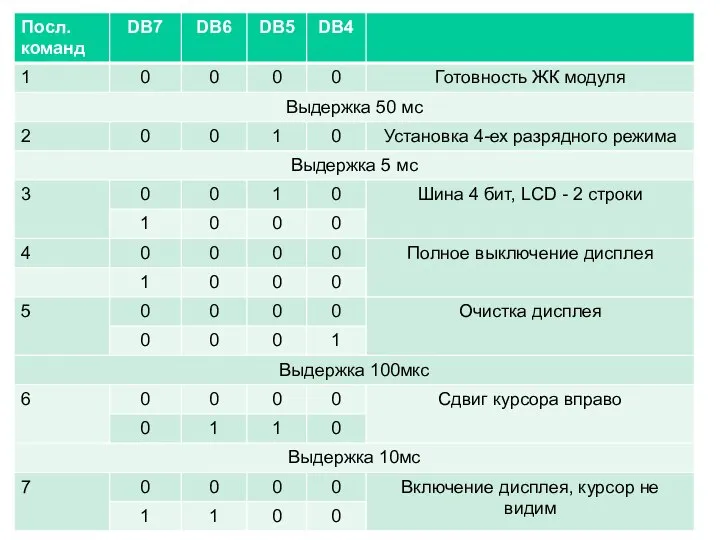

- 43. Инициализация 4-битной передачи данных

- 47. Скачать презентацию

Презентация на тему Рыбы Внутреннее строение

Презентация на тему Рыбы Внутреннее строение Презентация на тему Дмитрий Наркисович Мамин-Сибиряк 1852 - 1912

Презентация на тему Дмитрий Наркисович Мамин-Сибиряк 1852 - 1912  INTONATION and it’s functions

INTONATION and it’s functions Жизнь и творчество Марины Цветаевой

Жизнь и творчество Марины Цветаевой Стратегия развития аграрной отрасли в Пермском крае

Стратегия развития аграрной отрасли в Пермском крае Настоящее в пьесе. Ермолай Лопахин

Настоящее в пьесе. Ермолай Лопахин Воздушная перспектива

Воздушная перспектива Рисунки к дипломной работе. Шаблон

Рисунки к дипломной работе. Шаблон Некоторые проблемы современного российского рынка ценных бумаг Модульный курс для аспирантов 1-го года обучения

Некоторые проблемы современного российского рынка ценных бумаг Модульный курс для аспирантов 1-го года обучения ТЕХНОЛОГИЯ РАЗВИТИЯ КРИТИЧЕСКОГО МЫШЛЕНИЯ Семинар № 5

ТЕХНОЛОГИЯ РАЗВИТИЯ КРИТИЧЕСКОГО МЫШЛЕНИЯ Семинар № 5 Презентация на тему Презентация к игре «Брейн ринг» по истории

Презентация на тему Презентация к игре «Брейн ринг» по истории  «…»создание региональной сети малых отелей премиум классаСуворов Т.А.2011 год.

«…»создание региональной сети малых отелей премиум классаСуворов Т.А.2011 год. Презентация на тему история Крымской войны

Презентация на тему история Крымской войны  Сценарий номера самбо

Сценарий номера самбо Глобальные проблемы

Глобальные проблемы “Практика внедрения международного стандарта ISО 14001 в ОАО “Концерн Стирол”

“Практика внедрения международного стандарта ISО 14001 в ОАО “Концерн Стирол” С праздником девчонки!

С праздником девчонки! «Подготовка отчета некоммерческой организацией» Ведущие семинара: Совейко Алена Николаевна - специалист отдела по делам некомме

«Подготовка отчета некоммерческой организацией» Ведущие семинара: Совейко Алена Николаевна - специалист отдела по делам некомме Преступление и правонарушение. Виды преступлений

Преступление и правонарушение. Виды преступлений Презентация на тему Основные режимы нераспространения оружия массового поражения

Презентация на тему Основные режимы нераспространения оружия массового поражения  Кодекс педагогической этики

Кодекс педагогической этики Положение о портфолио педагогических работниковобразовательных учреждений, учреждений образования Мурманской области, проход

Положение о портфолио педагогических работниковобразовательных учреждений, учреждений образования Мурманской области, проход Профессиональная деятельность учителя технологии МОУ «Кукмаринская средняя общеобразовательная школа»

Профессиональная деятельность учителя технологии МОУ «Кукмаринская средняя общеобразовательная школа»  Проблемы привлечения судей к дисциплинарной ответственности

Проблемы привлечения судей к дисциплинарной ответственности Применение водогазового воздействия на залежь с целью увеличения КИН

Применение водогазового воздействия на залежь с целью увеличения КИН Доломит – экономично, экологично, технологично

Доломит – экономично, экологично, технологично Муниципальный автоматизированный комплекс «МАК»Размещение заказов города Нижний Тагил с 01.07.2011 запущен в промышленную эксплуат

Муниципальный автоматизированный комплекс «МАК»Размещение заказов города Нижний Тагил с 01.07.2011 запущен в промышленную эксплуат Презентация на тему Планета Венера

Презентация на тему Планета Венера