Содержание

- 2. Верхний уровень состоит из внутренних регистров процессора. Они выполнены по той же технологии, что и сам

- 3. В процессе кэширования строк оперативной памяти в кэше центрального процессора при каждом неудачном обращении к кэш-памяти

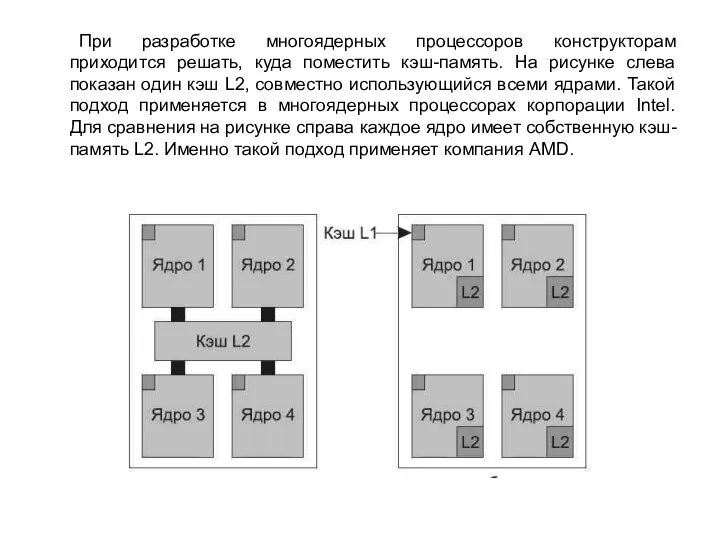

- 4. При разработке многоядерных процессоров конструкторам приходится решать, куда поместить кэш-память. На рисунке слева показан один кэш

- 5. Следующей в иерархии идет оперативная память. Это главная рабочая область системы памяти машины. Оперативную память часто

- 6. Существуют также другие разновидности энергонезависимой памяти, которые в отличие от ПЗУ могут стираться и перезаписываться, —

- 7. Еще одна разновидность памяти — CMOS-память, которая является энергозависимой. Во многих компьютерах CMOS-память используется для хранения

- 8. Шины По мере увеличения скорости работы процессоров и памяти возможности единой шины по обеспечению всех процессов

- 11. У этой системы имеется множество шин (например, шина кэш-памяти, шина памяти, а также шины PCIe, PCI,

- 12. Архитектура параллельной шины, подобная той, что используется в PCI, предполагает отправку каждого слова данных по нескольким

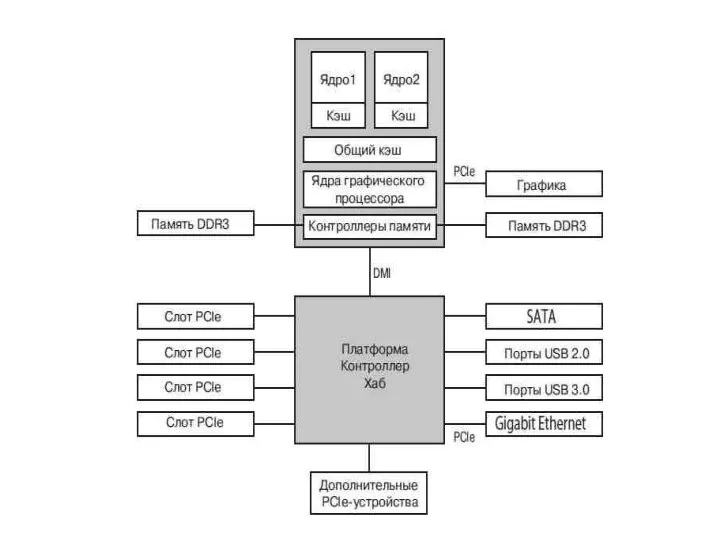

- 13. В данной конфигурации центральный процессор общается с памятью через быструю шину DDR3, со внешним графическим устройством

- 14. Шина USB (Universal Serial Bus — универсальная последовательная шина) была первоначально разработана для подключения к компьютеру

- 15. SCSI (Small Computer System Interface — интерфейс малых вычислительных систем) является высокоскоростной шиной, предназначенной для высокопроизводительных

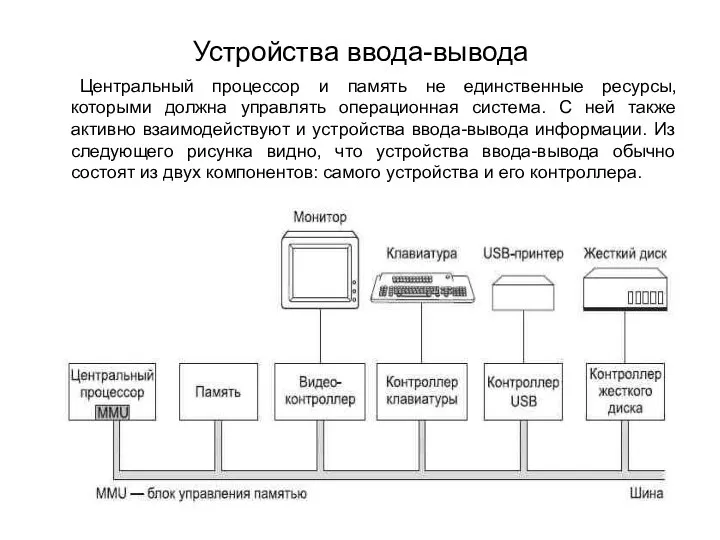

- 16. Устройства ввода-вывода Центральный процессор и память не единственные ресурсы, которыми должна управлять операционная система. С ней

- 17. Контроллер представляет собой микросхему или набор микросхем, которые управляют устройством на физическом уровне. Он принимает от

- 18. Так как все типы контроллеров отличаются друг от друга, для управления ими требуется различное программное обеспечение.

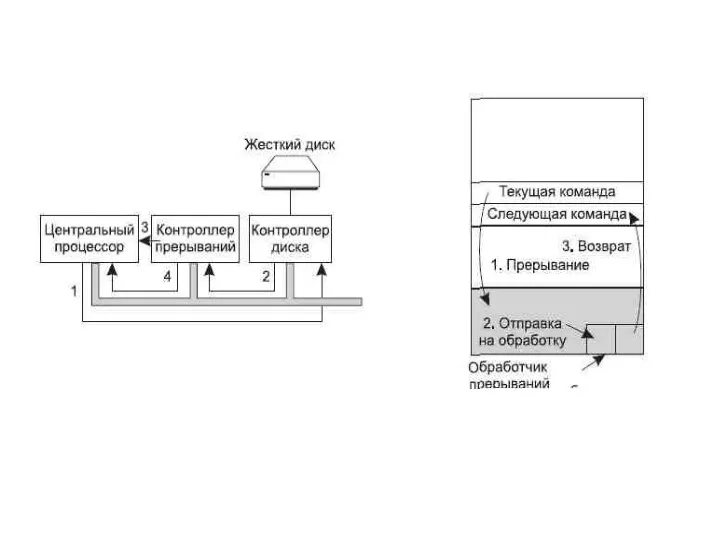

- 19. Второй способ заключается в том, что драйвер запускает устройство и просит его выдать прерывание по окончании

- 21. На первом этапе драйвер передает команду контроллеру, записывая информацию в его регистры. Затем контроллер запускает само

- 22. Когда обработчик прерываний (являющийся частью драйвера устройства, выдающего запрос на прерывание) начинает свою работу, он извлекает

- 23. Прерывания часто происходят в очень неподходящие моменты, например во время работы обработчика другого прерывания. Поэтому центральный

- 25. Скачать презентацию

Слайд 2 Верхний уровень состоит из внутренних регистров процессора. Они выполнены по той же

Верхний уровень состоит из внутренних регистров процессора. Они выполнены по той же

Затем следует кэш-память, которая управляется главным образом аппаратурой. Оперативная память разделяется на кэш-строки, обычно по 64 байт, с адресами от 0 до 63 в кэш-строке 0, адресами от 64 до 127 в кэш-строке 1 и т. д. Наиболее интенсивно используемые кэш-строки оперативной памяти сохраняются в высокоскоростной кэшпамяти, находящейся внутри процессора или очень близко к нему. Когда программе нужно считать слово из памяти, аппаратура кэша проверяет, нет ли нужной строки в кэш-памяти. Если строка в ней имеется, то происходит результативное обращение к кэш-памяти, запрос удовлетворяется за счет кэш-памяти без отправки запроса по шине к оперативной памяти. Обычно результативное обращение к кэшу занимает по времени два такта. Отсутствие слова в кэш-памяти вынуждает обращаться к оперативной памяти, что приводит к существенной потере времени. Кэш-память из-за своей высокой стоимости ограничена в объеме. Некоторые машины имеют два или даже три уровня кэша, причем каждый из последующих медленнее и объемнее предыдущего.

Слайд 3 В процессе кэширования строк оперативной памяти в кэше центрального процессора при каждом

В процессе кэширования строк оперативной памяти в кэше центрального процессора при каждом

Многие современные процессоры имеют сразу два уровня кэш-памяти. Первый уровень, или кэш L1, всегда является частью самого процессора и обычно подает декодированные команды в процессорный механизм исполнения команд. У многих процессоров есть и второй кэш L1 для тех слов данных, которые используются особенно интенсивно. Обычно каждый из кэшей L1 имеет объем 16 Кбайт. Вдобавок к этому кэшу процессоры часто оснащаются вторым уровнем кэш-памяти, который называется кэш L2 и содержит несколько мегабайт недавно использованных слов памяти. Различия между кэш-памятью L1 и L2 заключаются во временной диаграмме. Доступ к кэшу первого уровня осуществляется без задержек, а доступ к кэшу второго уровня требует задержки в один или два такта.

Слайд 4 При разработке многоядерных процессоров конструкторам приходится решать, куда поместить кэш-память. На рисунке

При разработке многоядерных процессоров конструкторам приходится решать, куда поместить кэш-память. На рисунке

Слайд 5 Следующей в иерархии идет оперативная память. Это главная рабочая область системы памяти

Следующей в иерархии идет оперативная память. Это главная рабочая область системы памяти

Дополнительно к оперативной памяти многие компьютеры оснащены небольшой по объему неизменяемой памятью с произвольным доступом — постоянным запоминающим устройством (ПЗУ), оно же память, предназначенная только для чтения (Read Only Memory (ROM)). В отличие от ОЗУ она не утрачивает своего содержимого при отключении питания, то есть является энергонезависимой. ПЗУ программируется на предприятии-изготовителе и впоследствии не подлежит изменению. Эта разновидность памяти характеризуется высоким быстродействием и дешевизной. На некоторых компьютерах в ПЗУ размещается начальный загрузчик, используемый для их запуска. Такой же памятью, предназначенной для осуществления низкоуровневого управления устройством, оснащаются некоторые контроллеры ввода-вывода.

Слайд 6 Существуют также другие разновидности энергонезависимой памяти, которые в отличие от ПЗУ могут

Существуют также другие разновидности энергонезависимой памяти, которые в отличие от ПЗУ могут

Флеш-память также обычно используется как носитель информации в портативных электронных устройствах.. По быстродействию флеш-память занимает промежуточное положение между ОЗУ и диском. Также, в отличие от дисковой памяти, если флеш-память стирается или перезаписывается слишком часто, она приходит в негодность.

Слайд 7 Еще одна разновидность памяти — CMOS-память, которая является энергозависимой. Во многих компьютерах

Еще одна разновидность памяти — CMOS-память, которая является энергозависимой. Во многих компьютерах

Слайд 8Шины

По мере увеличения скорости работы процессоров и памяти возможности единой шины по

Шины

По мере увеличения скорости работы процессоров и памяти возможности единой шины по

Слайд 11 У этой системы имеется множество шин (например, шина кэш-памяти, шина памяти, а

У этой системы имеется множество шин (например, шина кэш-памяти, шина памяти, а

Шина PCIe была придумана Intel в качестве преемницы более старой шины PCI, которая в свою очередь пришла на замену исходной шине ISA (Industry Standard Architecture — стандартная промышленная архитектура). Благодаря возможности передавать данные со скоростью в десятки гигабит в секунду шина PCIe работает намного быстрее своих предшественниц. Она сильно отличается от них и по своей природе. Вплоть до ее создания в 2004 году большинство шин были параллельными и совместно используемыми. Архитектура шин совместного использования означает, что для передачи данных разными устройствами используются одни и те же проводники. Таким образом, когда данные для передачи имеются сразу у нескольких устройств, для определения устройства, которому будет позволено использовать шину, требуется арбитр. В отличие от этого шина PCIe использует выделенные непосредственные соединения типа «точка — точка».

Слайд 12 Архитектура параллельной шины, подобная той, что используется в PCI, предполагает отправку каждого

Архитектура параллельной шины, подобная той, что используется в PCI, предполагает отправку каждого

Слайд 13 В данной конфигурации центральный процессор общается с памятью через быструю шину DDR3,

В данной конфигурации центральный процессор общается с памятью через быструю шину DDR3,

Слайд 14 Шина USB (Universal Serial Bus — универсальная последовательная шина) была первоначально разработана

Шина USB (Universal Serial Bus — универсальная последовательная шина) была первоначально разработана

USB является централизованной шиной, в которой главное (корневое) устройство опрашивает устройства ввода-вывода каждую миллисекунду, чтобы узнать, есть ли у них данные для передачи. Стандарт USB 1.0 мог обеспечить совокупную скорость передачи данных 12 Мбит/с, в USB 2.0 скорость была поднята до 480 Мбит/с, а пиковая скорость в USB 3.0 составила никак не меньше 5 Гбит/с. Любое USB-устройство может быть подключено к компьютеру и приступить к работе немедленно, не требуя его перезагрузки.

Слайд 15 SCSI (Small Computer System Interface — интерфейс малых вычислительных систем) является высокоскоростной

SCSI (Small Computer System Interface — интерфейс малых вычислительных систем) является высокоскоростной

Слайд 16Устройства ввода-вывода

Центральный процессор и память не единственные ресурсы, которыми должна управлять операционная

Устройства ввода-вывода

Центральный процессор и память не единственные ресурсы, которыми должна управлять операционная

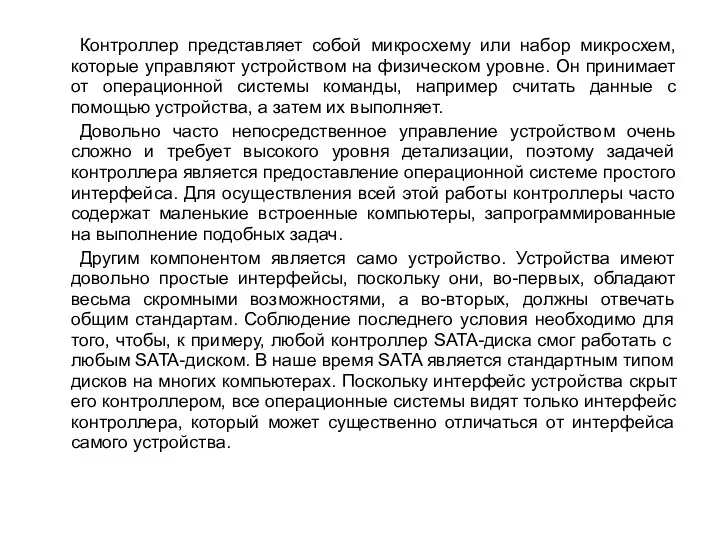

Слайд 17 Контроллер представляет собой микросхему или набор микросхем, которые управляют устройством на физическом

Контроллер представляет собой микросхему или набор микросхем, которые управляют устройством на физическом

Довольно часто непосредственное управление устройством очень сложно и требует высокого уровня детализации, поэтому задачей контроллера является предоставление операционной системе простого интерфейса. Для осуществления всей этой работы контроллеры часто содержат маленькие встроенные компьютеры, запрограммированные на выполнение подобных задач.

Другим компонентом является само устройство. Устройства имеют довольно простые интерфейсы, поскольку они, во-первых, обладают весьма скромными возможностями, а во-вторых, должны отвечать общим стандартам. Соблюдение последнего условия необходимо для того, чтобы, к примеру, любой контроллер SATA-диска смог работать с любым SATA-диском. В наше время SATA является стандартным типом дисков на многих компьютерах. Поскольку интерфейс устройства скрыт его контроллером, все операционные системы видят только интерфейс контроллера, который может существенно отличаться от интерфейса самого устройства.

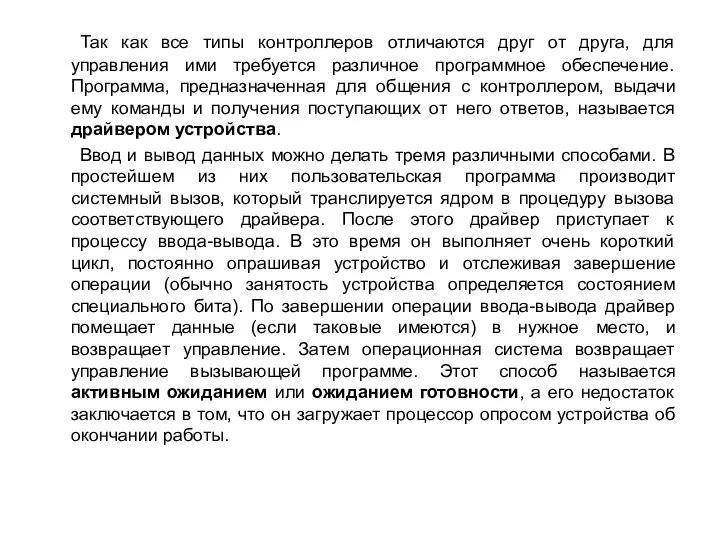

Слайд 18 Так как все типы контроллеров отличаются друг от друга, для управления ими

Так как все типы контроллеров отличаются друг от друга, для управления ими

Ввод и вывод данных можно делать тремя различными способами. В простейшем из них пользовательская программа производит системный вызов, который транслируется ядром в процедуру вызова соответствующего драйвера. После этого драйвер приступает к процессу ввода-вывода. В это время он выполняет очень короткий цикл, постоянно опрашивая устройство и отслеживая завершение операции (обычно занятость устройства определяется состоянием специального бита). По завершении операции ввода-вывода драйвер помещает данные (если таковые имеются) в нужное место, и возвращает управление. Затем операционная система возвращает управление вызывающей программе. Этот способ называется активным ожиданием или ожиданием готовности, а его недостаток заключается в том, что он загружает процессор опросом устройства об окончании работы.

Слайд 19 Второй способ заключается в том, что драйвер запускает устройство и просит его

Второй способ заключается в том, что драйвер запускает устройство и просит его

Прерывания играют очень важную роль в работе операционной системы, поэтому рассмотрим их более подробно. На рисунке внизу показан процесс ввода-вывода.

Слайд 21 На первом этапе драйвер передает команду контроллеру, записывая информацию в его регистры.

На первом этапе драйвер передает команду контроллеру, записывая информацию в его регистры.

Как только центральный процессор решит принять прерывание, содержимое счетчика команд и слова состояния программы помещаются, как правило, в текущий стек и процессор переключается в режим ядра. Номер устройства может быть использован как индекс части памяти, используемой для поиска адреса обработчика прерываний данного устройства. Эта часть памяти называется вектором прерываний.

Слайд 22 Когда обработчик прерываний (являющийся частью драйвера устройства, выдающего запрос на прерывание) начинает

Когда обработчик прерываний (являющийся частью драйвера устройства, выдающего запрос на прерывание) начинает

При третьем способе ввода-вывода используется специальный контроллер прямого доступа к памяти (Direct Memory Access (DMA)), который может управлять потоком битов между оперативной памятью и некоторыми контроллерами без постоянного вмешательства центрального процессора. Центральный процессор осуществляет настройку контроллера DMA, сообщая ему, сколько байтов следует передать, какое устройство и адреса памяти задействовать и в каком направлении передать данные, а затем дает ему возможность действовать самостоятельно. Когда контроллер DMA завершает работу, он выдает запрос на прерывание, который обрабатывается в ранее рассмотренном порядке.

Слайд 23 Прерывания часто происходят в очень неподходящие моменты, например во время работы обработчика

Прерывания часто происходят в очень неподходящие моменты, например во время работы обработчика

Развитие творческих способностей как средство самореализации личности

Развитие творческих способностей как средство самореализации личности Проекты1

Проекты1 Презентация на тему Международные экономические связи

Презентация на тему Международные экономические связи Бабушкин сундук. Тест-игра для проверки знаний учащихся по теме Традиционный русский народный костюм

Бабушкин сундук. Тест-игра для проверки знаний учащихся по теме Традиционный русский народный костюм Презентация на тему Мезоамерика

Презентация на тему Мезоамерика  Производство культур Рапс Основные направления использования

Производство культур Рапс Основные направления использования Маркшейдерская документация горного предприятия

Маркшейдерская документация горного предприятия Классификация СОТС, применяемых при резании металлов

Классификация СОТС, применяемых при резании металлов Коммуникативный подход при изучении английского языка

Коммуникативный подход при изучении английского языка Mery per sempre il siciliano

Mery per sempre il siciliano Галактика МПР – Мониторинг Показателей Региона

Галактика МПР – Мониторинг Показателей Региона ТЕХНИКА ДЛЯ ПРОИЗВОДСТВА НАТУРАЛЬНЫХ СОКОВ И НЕКТАРОВ

ТЕХНИКА ДЛЯ ПРОИЗВОДСТВА НАТУРАЛЬНЫХ СОКОВ И НЕКТАРОВ Вершки и корешки

Вершки и корешки Контакт - центр Хеликс

Контакт - центр Хеликс Вакуумная техника

Вакуумная техника living_room_acoustics_llrevit

living_room_acoustics_llrevit Catalogue. Assembly, commissioning, start up, after-sales service

Catalogue. Assembly, commissioning, start up, after-sales service НАЧАЛО ВЕЛИКОЙ ОТЕЧЕСТВЕННОЙ ВОЙНЫ

НАЧАЛО ВЕЛИКОЙ ОТЕЧЕСТВЕННОЙ ВОЙНЫ Реклама на сайте Dirty.ru для украинских рекламодателей

Реклама на сайте Dirty.ru для украинских рекламодателей Физиология активности Н. А. Бернштейна

Физиология активности Н. А. Бернштейна Main categories of morality

Main categories of morality  Мадураи. Город одного храма

Мадураи. Город одного храма Волонтерские образовательные проекты для школьников на примере Зимней Пущинской Школы. - презентация

Волонтерские образовательные проекты для школьников на примере Зимней Пущинской Школы. - презентация Исследовательская работа по теме: «Биоиндикация загрязнения воздуха по комплексу признаков сосны обыкновенной

Исследовательская работа по теме: «Биоиндикация загрязнения воздуха по комплексу признаков сосны обыкновенной Березовский районный архив

Березовский районный архив Сгущенное молоко с банановым вкусом

Сгущенное молоко с банановым вкусом Урок – сказка.

Урок – сказка. Бизнес-проект Татлым

Бизнес-проект Татлым