Содержание

- 2. Основные черты CISC-архитектур В основе архитектуры CISC (Complex Instruction Set Computer) лежит эффективное использование памяти и

- 3. Большое число машинных команд, некоторые из которых семантически нагружены аналогично операторам ЯВУ и выполняются за много

- 4. Проблемы и недостатки CISC-архитектур Усложнение набора команд и аппаратной реализации с каждым новым поколением компьютеров. Различным

- 5. Идея RISC-архитектуры Основная идея RISC-архитектуры состояла в том, что последовательность простых команд, давая тот же результат,

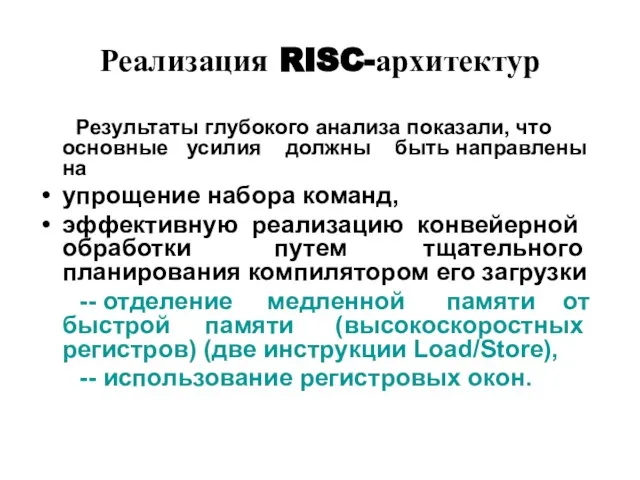

- 6. Реализация RISC-архитектур Результаты глубокого анализа показали, что основные усилия должны быть направлены на упрощение набора команд,

- 7. Два способа оптимального использования регистров Программный способ. Аппаратный способ.

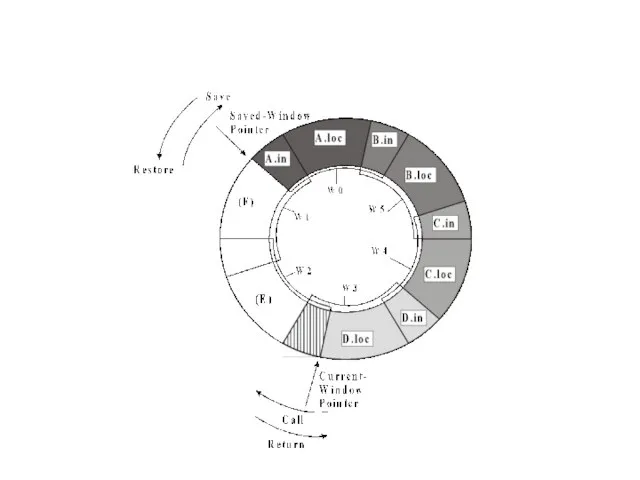

- 8. Аппаратный способ

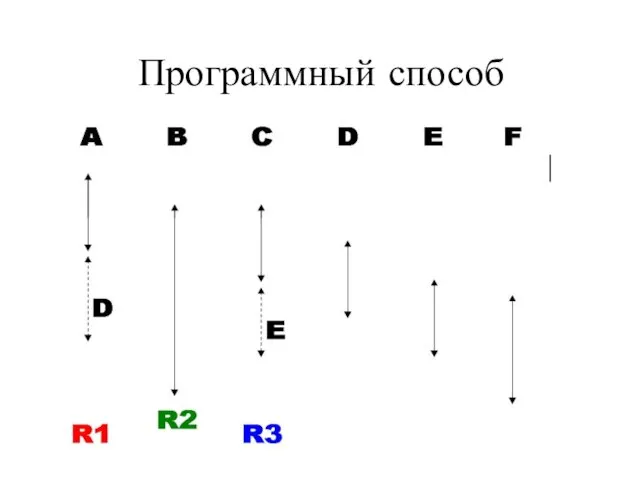

- 10. Программный способ

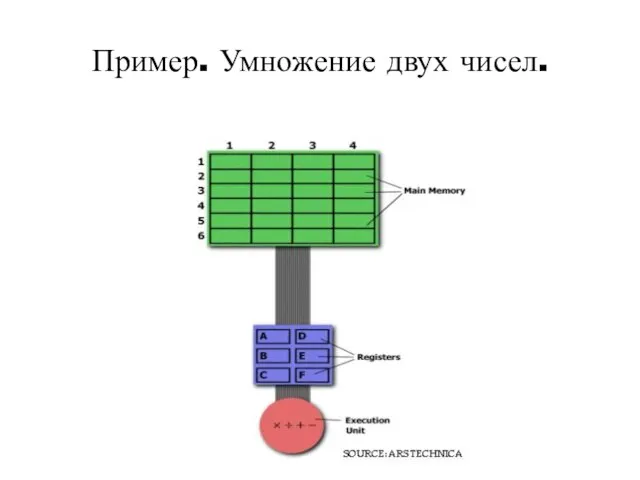

- 12. Пример. Умножение двух чисел.

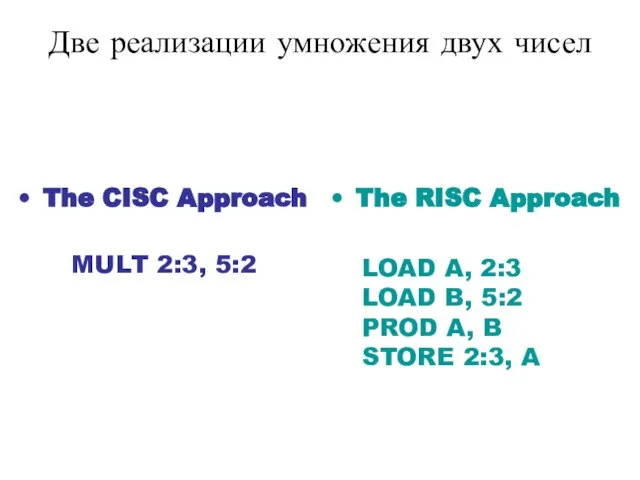

- 13. Две реализации умножения двух чисел The CISC Approach The RISC Approach MULT 2:3, 5:2 LOAD A,

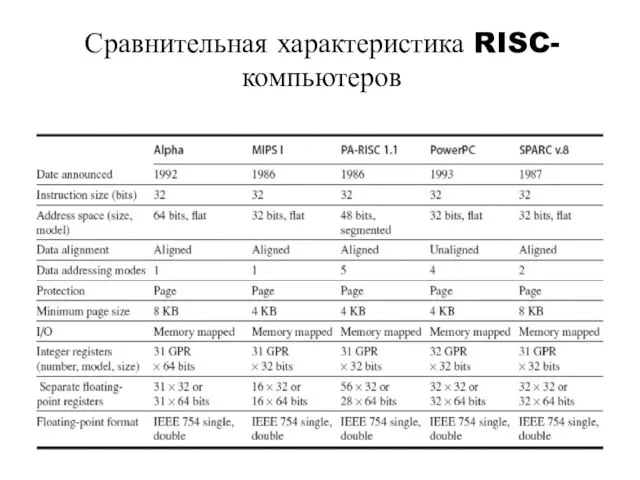

- 14. Сравнительная характеристика RISC-компьютеров

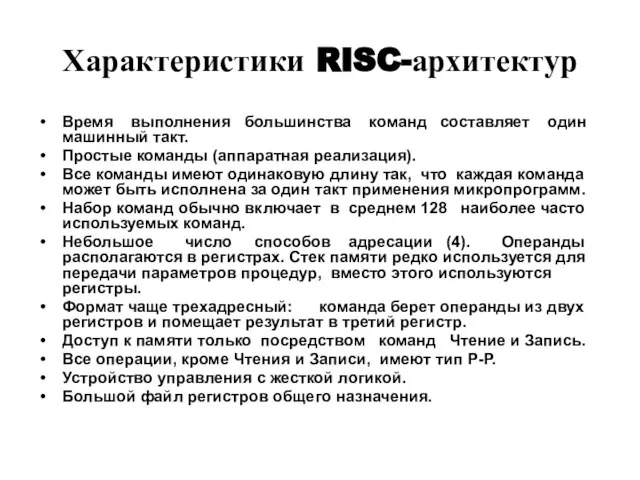

- 15. Характеристики RISC-архитектур Время выполнения большинства команд составляет один машинный такт. Простые команды (аппаратная реализация). Все команды

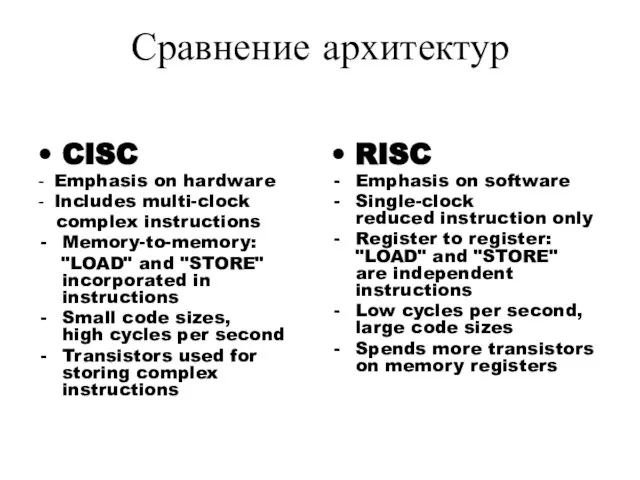

- 16. Сравнение архитектур CISC - Emphasis on hardware - Includes multi-clock complex instructions Memory-to-memory: "LOAD" and "STORE"

- 18. Скачать презентацию

Денежные переводы физических лиц: состояние и тенденции развития (на примере ПАО Сбербанк)

Денежные переводы физических лиц: состояние и тенденции развития (на примере ПАО Сбербанк) Особенности истории информатики

Особенности истории информатики Мотивирование топ-менеджеров в банковской сфере: подходы и инструменты

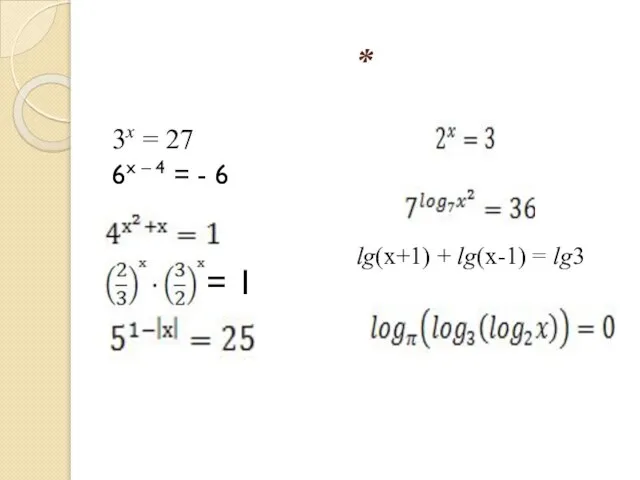

Мотивирование топ-менеджеров в банковской сфере: подходы и инструменты = 1

= 1 Изустная среда мордовского села

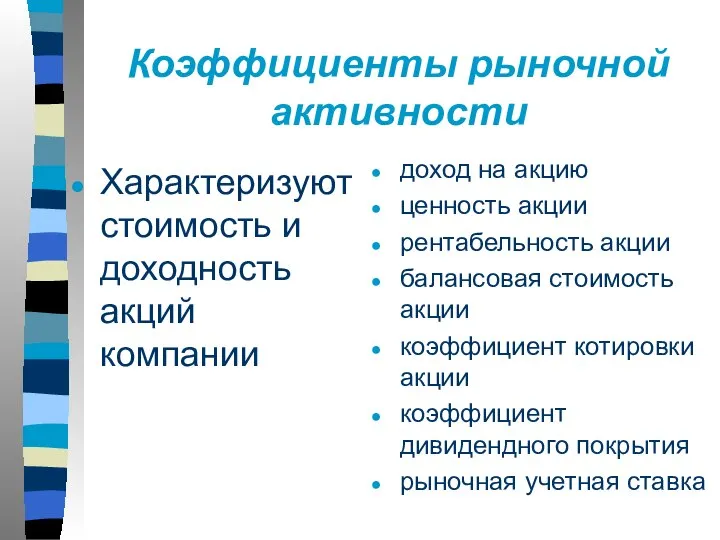

Изустная среда мордовского села Показатели рыночной активности

Показатели рыночной активности Выхухоль. Красная книга

Выхухоль. Красная книга Обработка текстовой и графической информации. Создаём комбинированный документ

Обработка текстовой и графической информации. Создаём комбинированный документ Телевидение: я выбираю или меня выбирают. Автор и руководитель проекта: Симонова Ольга Владимировна 2004 год

Телевидение: я выбираю или меня выбирают. Автор и руководитель проекта: Симонова Ольга Владимировна 2004 год Что я сделаю, чтобы доверенный мне магазин стал лучшим на рынке

Что я сделаю, чтобы доверенный мне магазин стал лучшим на рынке Туалетная вода для мужчин Faberlic Intense

Туалетная вода для мужчин Faberlic Intense Межпроцедурные анализы и оптимизации

Межпроцедурные анализы и оптимизации Внешняя политика СССР в 1930-е гг. и накануне Великой Отечественной войны

Внешняя политика СССР в 1930-е гг. и накануне Великой Отечественной войны Урок 3 Человек и Бог в православии-повторение

Урок 3 Человек и Бог в православии-повторение 17 век

17 век ПЕРЕГОВОРЫ

ПЕРЕГОВОРЫ Изготовление вечернего платья

Изготовление вечернего платья Теорiя iгор

Теорiя iгор  Презентация на тему Роль гормонов в обмене веществ, росте и развитии организма биология 8 класс

Презентация на тему Роль гормонов в обмене веществ, росте и развитии организма биология 8 класс аня хочет санчо панчо

аня хочет санчо панчо Создание таблиц в Microsoft Word

Создание таблиц в Microsoft Word Teenagers’ society problems

Teenagers’ society problems Воля познавать

Воля познавать Любимое блюдо моей семьи

Любимое блюдо моей семьи Ладья. Урок №8

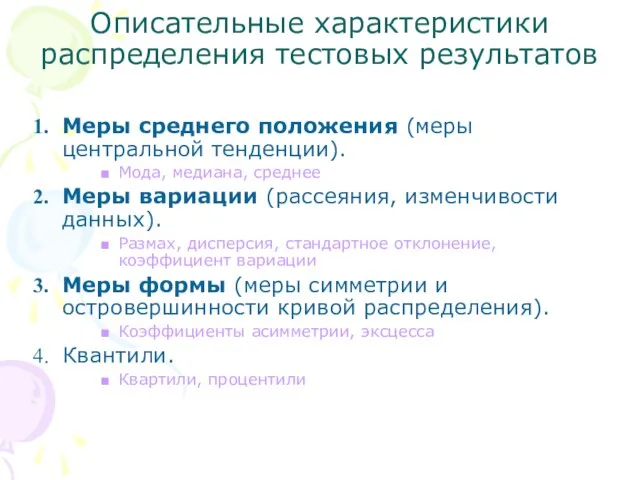

Ладья. Урок №8 Описательные характеристики распределения тестовых результатов

Описательные характеристики распределения тестовых результатов Презентация на тему Одиночество

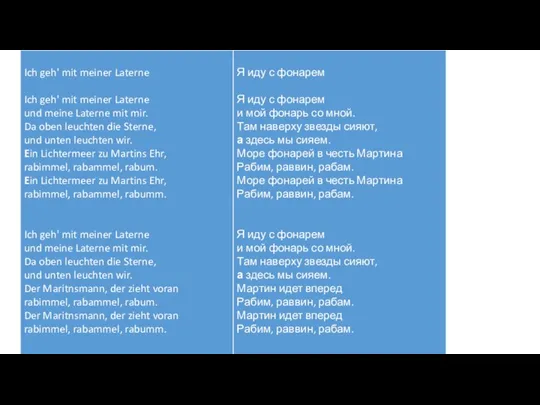

Презентация на тему Одиночество Ich gehe mit meine Laterne

Ich gehe mit meine Laterne