Содержание

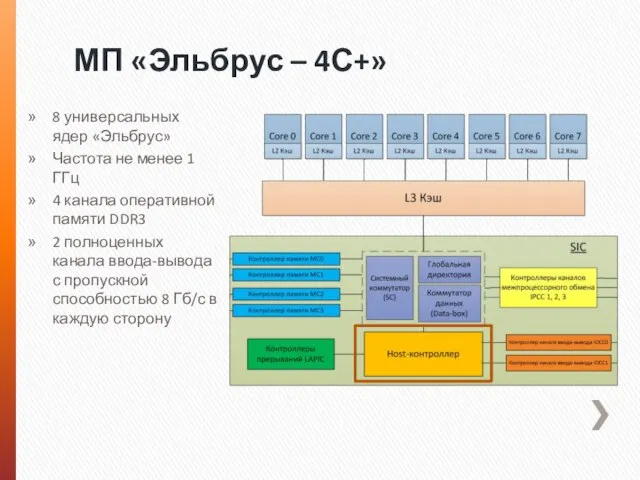

- 2. МП «Эльбрус – 4С+» 8 универсальных ядер «Эльбрус» Частота не менее 1 ГГц 4 канала оперативной

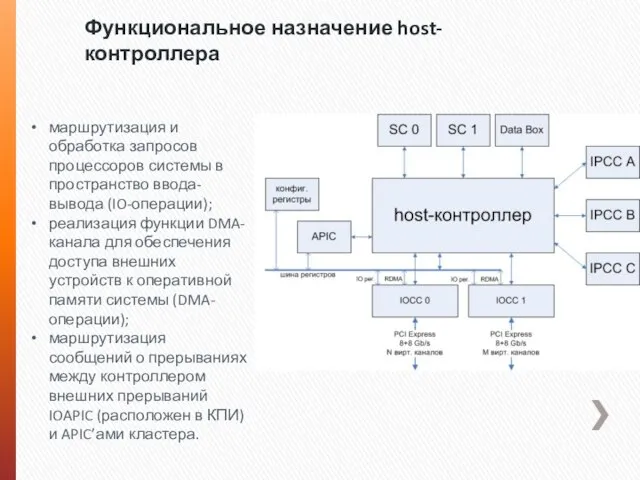

- 3. Функциональное назначение host-контроллера маршрутизация и обработка запросов процессоров системы в пространство ввода-вывода (IO-операции); реализация функции DMA-канала

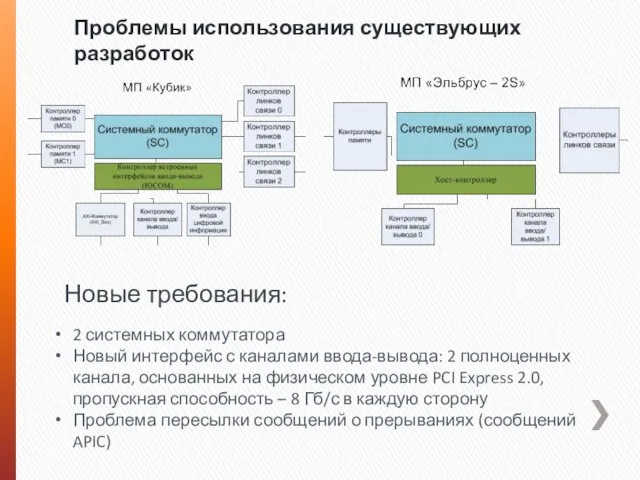

- 4. Проблемы использования существующих разработок 2 системных коммутатора Новый интерфейс с каналами ввода-вывода: 2 полноценных канала, основанных

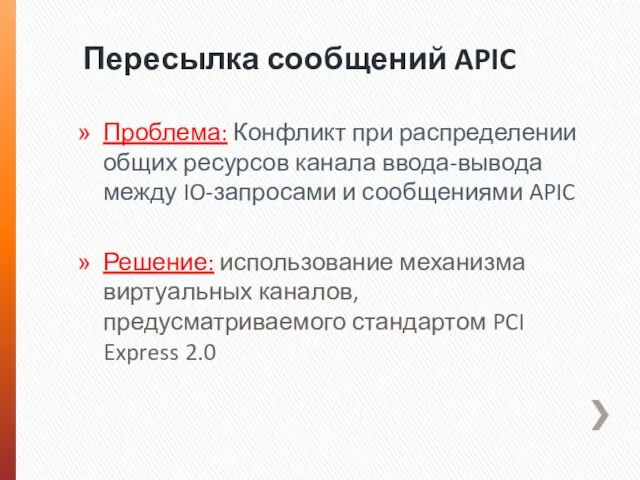

- 5. Пересылка сообщений APIC Проблема: Конфликт при распределении общих ресурсов канала ввода-вывода между IO-запросами и сообщениями APIC

- 6. Цель работы Требования: Обеспечить эффективное взаимодействие host-контроллера с двумя каналами ввода-вывода Реализовать обработку запросов в пространство

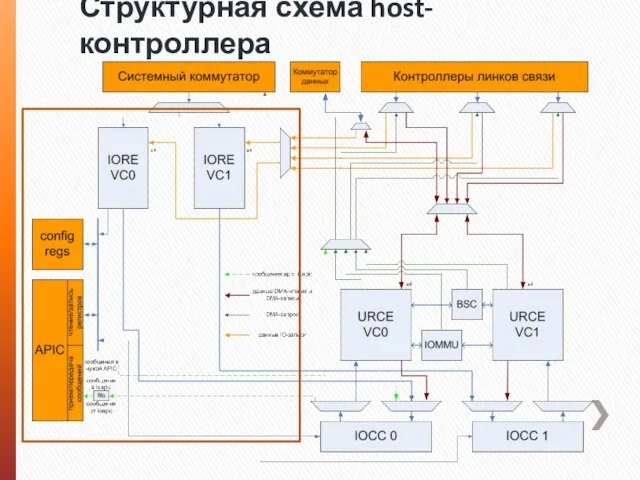

- 7. Структурная схема host-контроллера

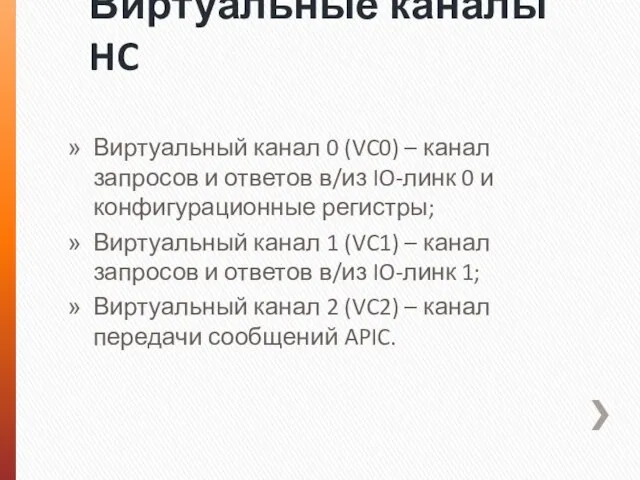

- 8. Виртуальные каналы HC Виртуальный канал 0 (VC0) – канал запросов и ответов в/из IO-линк 0 и

- 9. Структурная схема обработчика IO-запросов (IORE) Запросы в конфигурационные регистры SIC, расположенные в IO Box, конфигурационные регистры

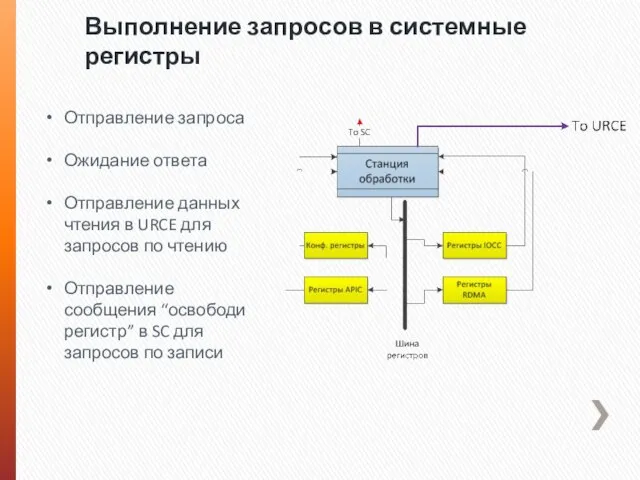

- 10. Выполнение запросов в системные регистры Отправление запроса Ожидание ответа Отправление данных чтения в URCE для запросов

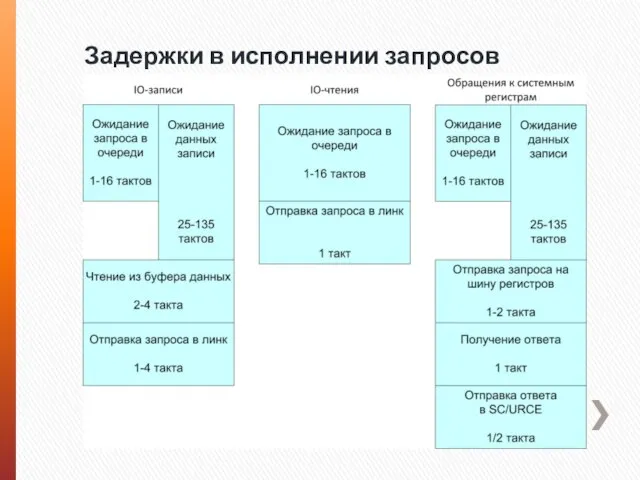

- 11. Задержки в исполнении запросов

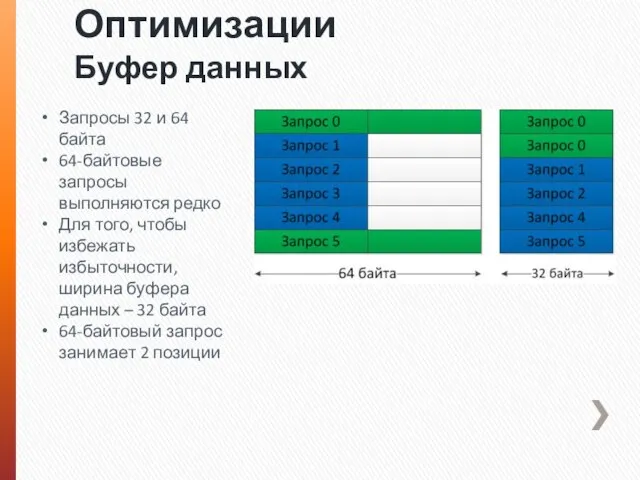

- 12. Оптимизации Буфер данных Запросы 32 и 64 байта 64-байтовые запросы выполняются редко Для того, чтобы избежать

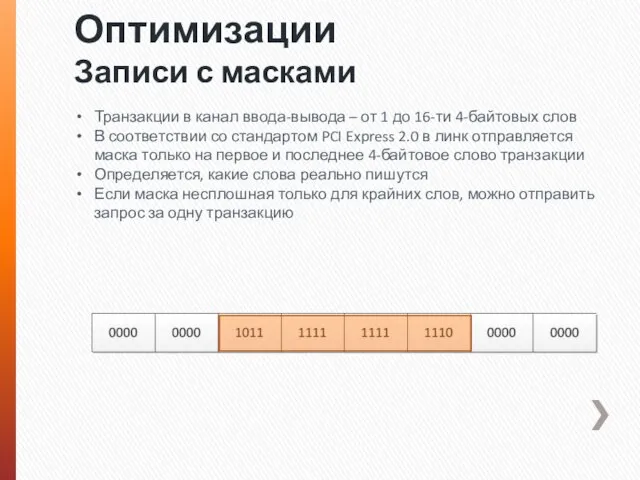

- 13. Оптимизации Записи с масками Транзакции в канал ввода-вывода – от 1 до 16-ти 4-байтовых слов В

- 14. Результаты Разработано Verilog-описание устройства, обеспечивающего эффективное взаимодействие процессоров с двумя каналами ввода-вывода и контроллером прерываний APIC

- 16. Скачать презентацию

Реактивный двигатель ,

Реактивный двигатель , Проблемы и перспективы «дачной амнистии»: взгляд экспертов

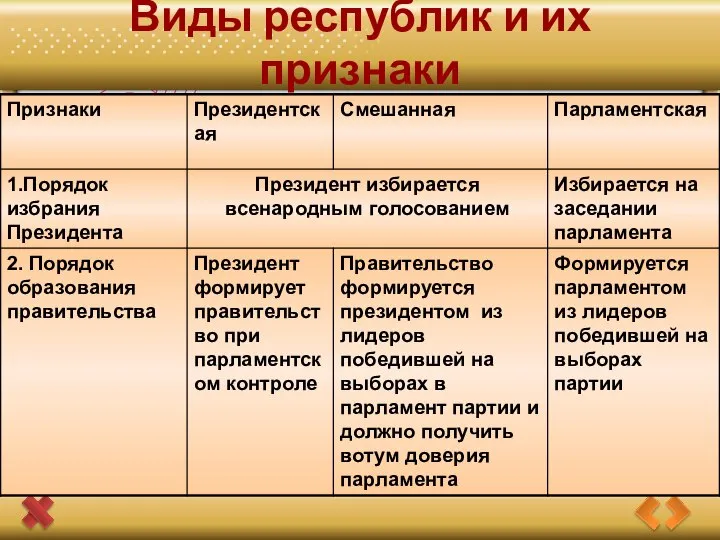

Проблемы и перспективы «дачной амнистии»: взгляд экспертов Государство, его признаки и формы

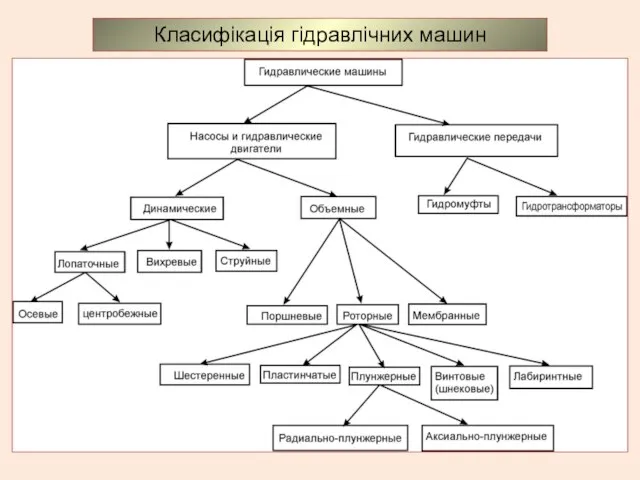

Государство, его признаки и формы Класифікація гідравлічних машин

Класифікація гідравлічних машин Образы в социальной рекламе

Образы в социальной рекламе Турция

Турция К ВОПРОСУ О РЕГИОНАЛЬНОМ ТЕЛЕМЕДИЦИНСКОМ ЦЕНТРЕСАНКТ-ПЕТЕРБУРГА(ТМЦ СПБ)

К ВОПРОСУ О РЕГИОНАЛЬНОМ ТЕЛЕМЕДИЦИНСКОМ ЦЕНТРЕСАНКТ-ПЕТЕРБУРГА(ТМЦ СПБ) Ежегодно команда юношей принимает участиев межрегиональных соревнованиях среди кадетских корпусов, православных гимназий, дет

Ежегодно команда юношей принимает участиев межрегиональных соревнованиях среди кадетских корпусов, православных гимназий, дет одготовка специалистов для работы с лицами с ОВЗ в Норвегии

одготовка специалистов для работы с лицами с ОВЗ в Норвегии Применение анкерного крепления и хим. упрочнения кровли в условиях Ярегского месторождения

Применение анкерного крепления и хим. упрочнения кровли в условиях Ярегского месторождения Путешествие в город огород

Путешествие в город огород Презентация на тему Духовная жизнь

Презентация на тему Духовная жизнь Питание растений

Питание растений Нормативно-правовые основы и финансово-хозяйственные механизмы перехода на новую систему финансирования

Нормативно-правовые основы и финансово-хозяйственные механизмы перехода на новую систему финансирования Спорт — это здорово

Спорт — это здорово Лев Николаевич Толстой

Лев Николаевич Толстой Prince2 - структурированный метод управления проектами в социальной сфере

Prince2 - структурированный метод управления проектами в социальной сфере Кайнозойская эра

Кайнозойская эра Все профессии важны, с математикой дружны

Все профессии важны, с математикой дружны Физиология, биохимия микроорганизмов (прокариотов: бактерий, эукариотов: простейших, грибов, вирусов)

Физиология, биохимия микроорганизмов (прокариотов: бактерий, эукариотов: простейших, грибов, вирусов) Парад Профессий - ХХI век. Автор Сохибкулова Марина

Парад Профессий - ХХI век. Автор Сохибкулова Марина Trinkgeld für azubis

Trinkgeld für azubis Семинар FCI для судей IGP

Семинар FCI для судей IGP Многогранники

Многогранники Чем интересны музеи

Чем интересны музеи "Пожарные

"Пожарные ОПТИМИЗАЦИЯ ШКОЛЬНОГО САЙТА

ОПТИМИЗАЦИЯ ШКОЛЬНОГО САЙТА к 8 марта с музыкой

к 8 марта с музыкой