Слайд 2Базовые таймеры TIM6 и TIM7

•16-битовый суммирующий счётчик с автоматической перезагрузкой;

•16-битовый предварительный делитель

частоты (прескалер) с программируемым коэффициентом деления от 1 до 65636 включительно;

• прерывания по переполнению.

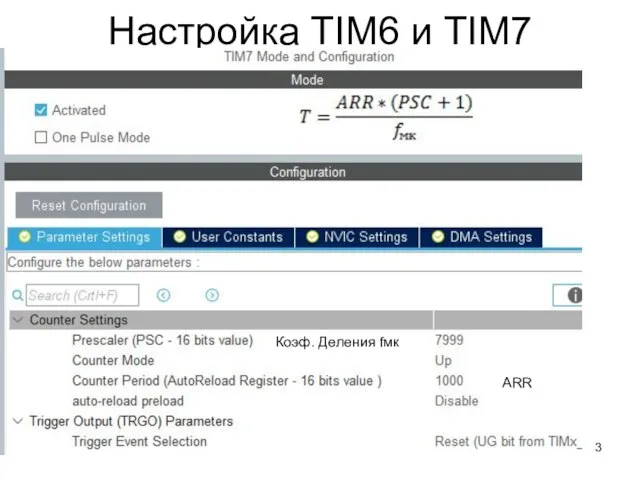

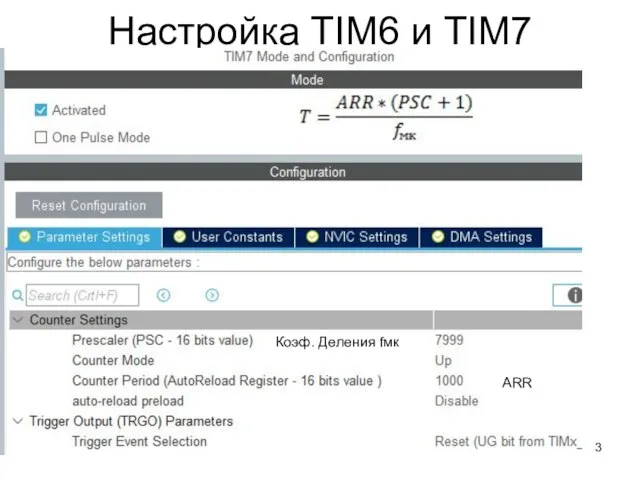

Слайд 3Настройка TIM6 и TIM7

Коэф. Деления fмк

ARR

Слайд 4Регистры таймеров TIM6 и TIM7

•TIMx_CNT (Counter Register) – счетный регистр;

•TIMx_PSC (Prescaler Register)

- регистр предделителя; определяет коэффициент деления k=TIMx_PSC+1;

•TIMx_ARR (Auto-Reload Register) - регистр авто-перезагрузки; когда значение в счётчике достигает величины, записанной в этом регистре, следующий импульс сбрасывает счётчик в 0, при этом генерируется сигнал переполнения счётчика, который используется как update event - событие обновления. Если в TIMx_ARR записано значение 0, то счётчик таймера останавливается.

Содержимое счетного регистра, регистра автоматической перезагрузки и регистр предделителя программно доступны для чтения и записи в любой момент.

Слайд 5Регистры таймеров TIM6 и TIM7

•TIMx_CR1 (TIM6&TIM7 control register 1) - TIM_CR1_CEN –

запуск таймера

• TIMx_DIER (TIM6&TIM7 DMA/Interrupt enable register) –

UIE (Update interrupt enable) - Бит разрешения генерации прерывания от таймера по событию обновления.

• TIMx_SR (TIM6&TIM7 status register) - TIM_SR_UIF – флаг прерывания при переполнении таймера.

Дискретное (цифровое) представление различной информации

Дискретное (цифровое) представление различной информации Трансляция со смартфона

Трансляция со смартфона Табличные информационные модели. Моделирование и формализация

Табличные информационные модели. Моделирование и формализация Обработка числовой информации

Обработка числовой информации Накопление теоретической информации

Накопление теоретической информации Работа с двумерными массивами

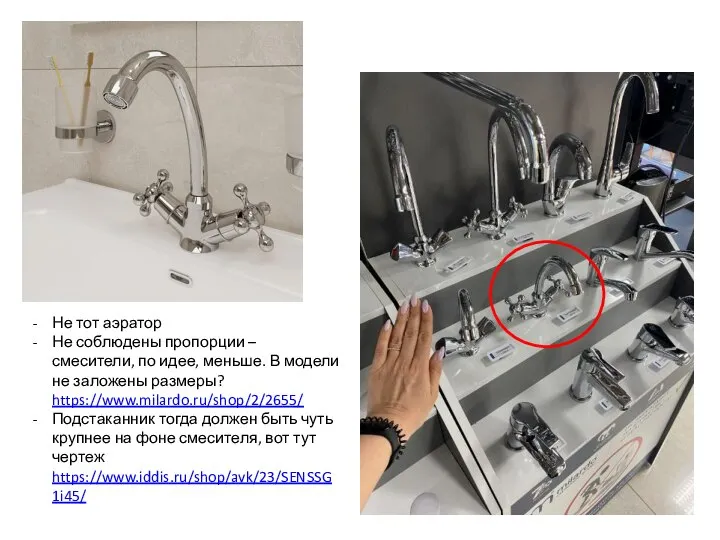

Работа с двумерными массивами Смеситель для умывальника Helic. Правки на сайте

Смеситель для умывальника Helic. Правки на сайте Единая система мониторинга производственной системы (ЕСМПС)

Единая система мониторинга производственной системы (ЕСМПС) Формат фигуры

Формат фигуры Подготовка к ЕГЭ по обществознанию, работа с заданиями В-5. Дифференциация в социальной информации фактов и мнений

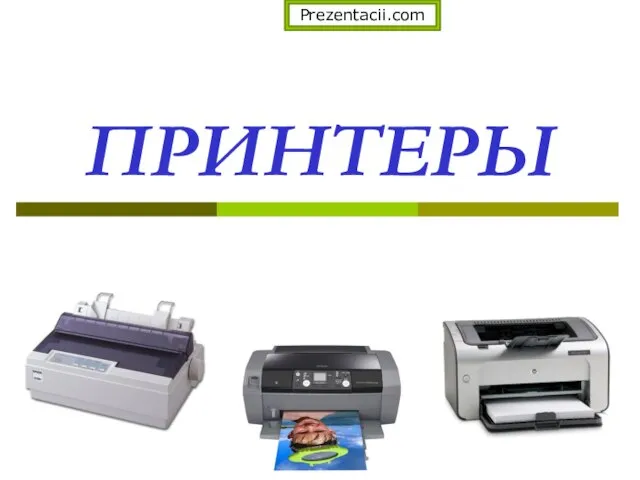

Подготовка к ЕГЭ по обществознанию, работа с заданиями В-5. Дифференциация в социальной информации фактов и мнений Презентация на тему Принтеры

Презентация на тему Принтеры  Установка Ubuntu

Установка Ubuntu Презентация на тему Графический редактор Paint

Презентация на тему Графический редактор Paint  1665510556917__cxho3q

1665510556917__cxho3q Канал https://www.youtube.com/wat ch?v=FhMOcFGyQas&t=20s

Канал https://www.youtube.com/wat ch?v=FhMOcFGyQas&t=20s Специфика лендов

Специфика лендов Аббревиатура как нестандартный способ онлай-общения

Аббревиатура как нестандартный способ онлай-общения Диаграммы классов и состояний

Диаграммы классов и состояний Кто такие ларнаки?

Кто такие ларнаки? Gimp. Удаление лишних деталей с фотографии. Создание терминатора

Gimp. Удаление лишних деталей с фотографии. Создание терминатора Медиаграмотность: предмет изучения, роль в современном мире

Медиаграмотность: предмет изучения, роль в современном мире Microsoft Office. Краткая характеристика изученных программ

Microsoft Office. Краткая характеристика изученных программ Multiplayer Gaming

Multiplayer Gaming Алгоритм и его свойства

Алгоритм и его свойства Interacting With Invisible Objects

Interacting With Invisible Objects Проект онлайн турнира по CS:GO “Cyber stalker”

Проект онлайн турнира по CS:GO “Cyber stalker” Алгоритмизация, как условие автоматизации

Алгоритмизация, как условие автоматизации Операционная система. Программное обеспечение

Операционная система. Программное обеспечение