Содержание

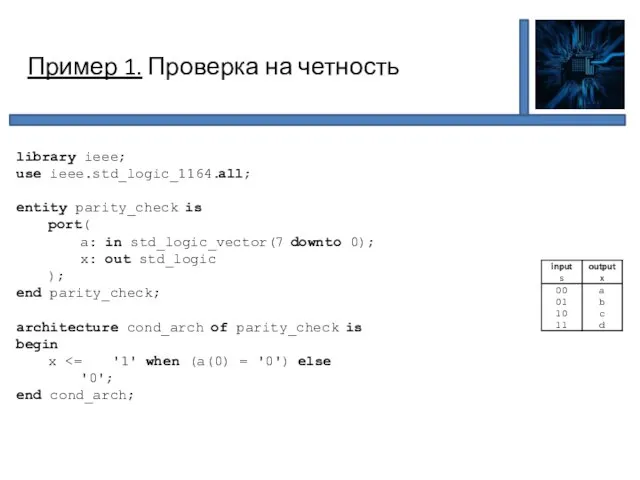

- 2. Пример 1. Проверка на четность library ieee; use ieee.std_logic_1164.all; entity parity_check is port( a: in std_logic_vector(7

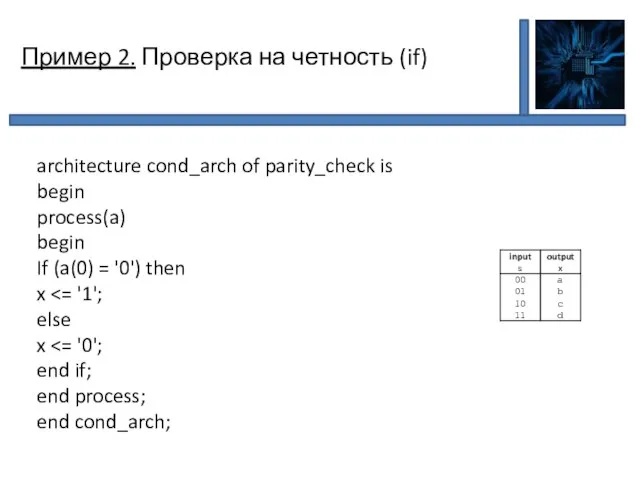

- 3. Пример 2. Проверка на четность (if) architecture cond_arch of parity_check is begin process(a) begin If (a(0)

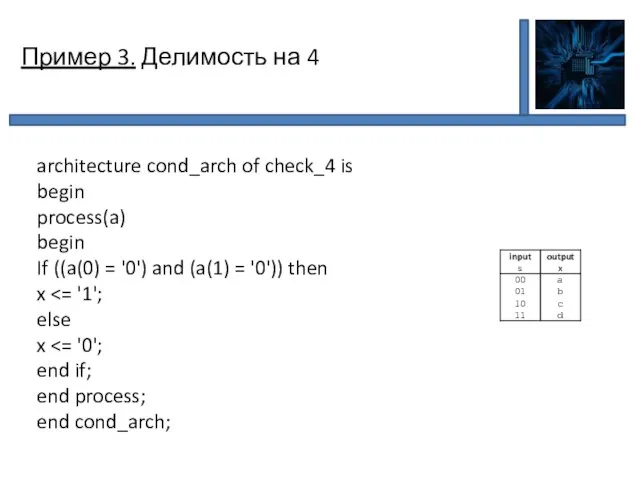

- 4. Пример 3. Делимость на 4 architecture cond_arch of check_4 is begin process(a) begin If ((a(0) =

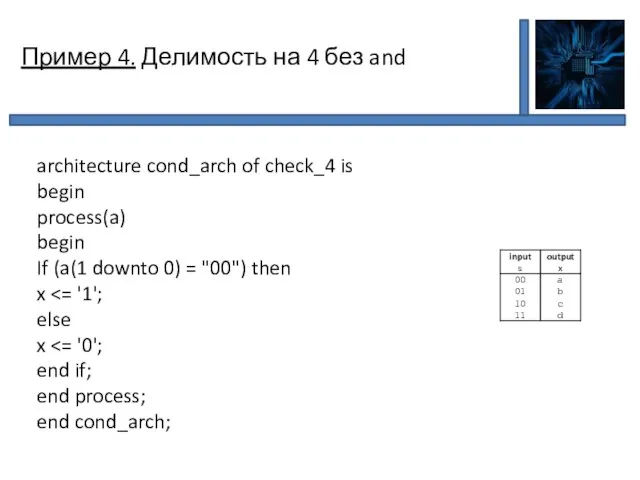

- 5. Пример 4. Делимость на 4 без and architecture cond_arch of check_4 is begin process(a) begin If

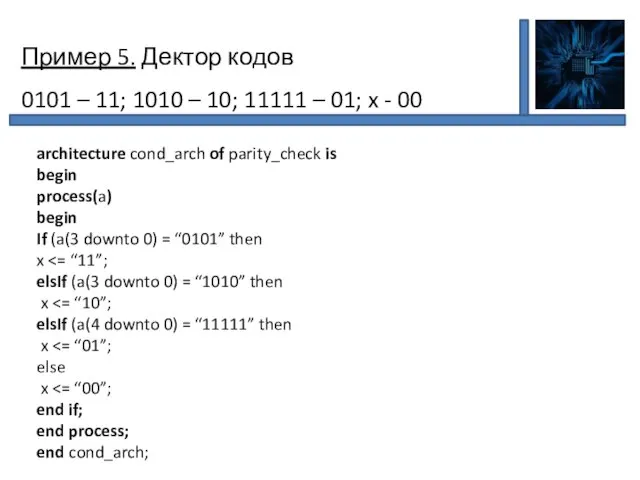

- 6. Пример 5. Дектор кодов 0101 – 11; 1010 – 10; 11111 – 01; x - 00

- 8. Скачать презентацию

Тестирование ПО. Типы тестирования

Тестирование ПО. Типы тестирования Муниципальное образовательное учреждение «Октябрьская средняя общеобразовательная школа» Работу выполнила: ученица 9 класса

Муниципальное образовательное учреждение «Октябрьская средняя общеобразовательная школа» Работу выполнила: ученица 9 класса Термины которые должен знать любой прохацкер

Термины которые должен знать любой прохацкер Продвижение сайта

Продвижение сайта Domini Games. Стратегия 2021-2025

Domini Games. Стратегия 2021-2025 Алгоритмы и структуры данных

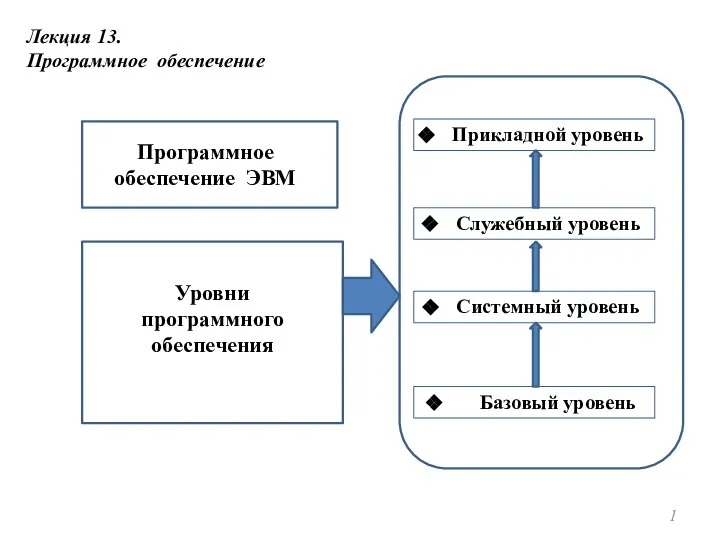

Алгоритмы и структуры данных Программное обеспечение

Программное обеспечение Розробка інформаційної системи для обліку та продажу програмних продуктів

Розробка інформаційної системи для обліку та продажу програмних продуктів История возникновения методологии IDEF0

История возникновения методологии IDEF0 ООО АЙВИС. Вашу рекламу видно и слышно

ООО АЙВИС. Вашу рекламу видно и слышно Вечеринка ситхов – лучшая группа в Вк

Вечеринка ситхов – лучшая группа в Вк Отчет за сентябрь @aramake.ru

Отчет за сентябрь @aramake.ru Отправить сообщения на электронный адрес на темы Электронная почта

Отправить сообщения на электронный адрес на темы Электронная почта Поиск записей в табличной базе данных с помощью фильтров

Поиск записей в табличной базе данных с помощью фильтров Бесплатное обучение торговле на рынке Форекс

Бесплатное обучение торговле на рынке Форекс Programing C

Programing C Приложение ментального счета Mental score. Проект

Приложение ментального счета Mental score. Проект Современные методы аналитики данных в СМИ (1)6

Современные методы аналитики данных в СМИ (1)6 Разграничение прав доступа в локальной сети сети

Разграничение прав доступа в локальной сети сети История развития вычислительной техники (часть 1)

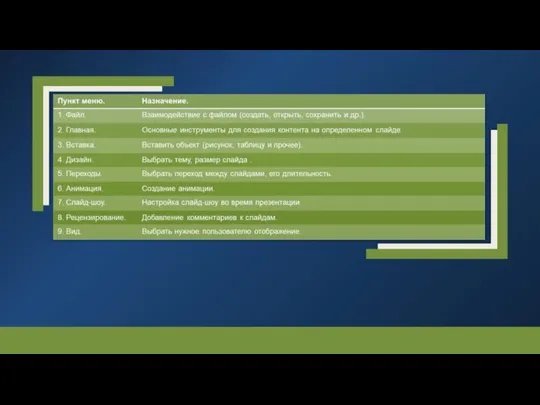

История развития вычислительной техники (часть 1) Пункт меню. Назначение

Пункт меню. Назначение ТЗ на создание сайта СМ

ТЗ на создание сайта СМ Информационная безопасность детей в Интернете

Информационная безопасность детей в Интернете Мошенничество в интернете

Мошенничество в интернете Безопасность личного пространства (соцсети)

Безопасность личного пространства (соцсети) Передача информации

Передача информации Презентация без названия

Презентация без названия Разновидности объектов и их классификация

Разновидности объектов и их классификация