Содержание

- 2. СБИС разработки МЦСТ Процессоры SPARC (RISC) 3-х поколений МЦСТ-R1000: 1ГГц, 4 ядра SPARC V9 Процессоры Эльбрус

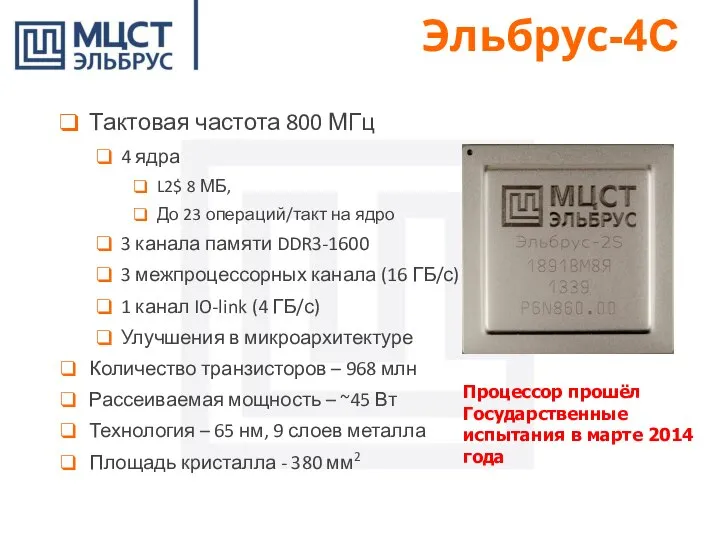

- 3. Процессор прошёл Государственные испытания в марте 2014 года Тактовая частота 800 МГц 4 ядра L2$ 8

- 4. Процессор завершил гос. испытания в 2014 году Тактовая частота 300 МГц, 2 ядра «Эльбрус» L2$ 2

- 5. КПИ Тактовая частота – 250 МГц 2 канала I/O (2 * 1 ГБ/с). Интерфейсы PCI Express

- 6. Многопроцессорность Объединение до 4 процессоров на общей памяти (NUMA) через когерентные межпроцессорные каналы без привлечения дополнительной

- 7. Структура м/п Эльбрус

- 8. Асинхронная предподкачка

- 9. Пиковая производительность лин.уч. циклы Int (8) / FP (9) / St (2) / Ld (4) -

- 10. Сводная таблица результатов

- 11. ВК на базе МП Эльбрус

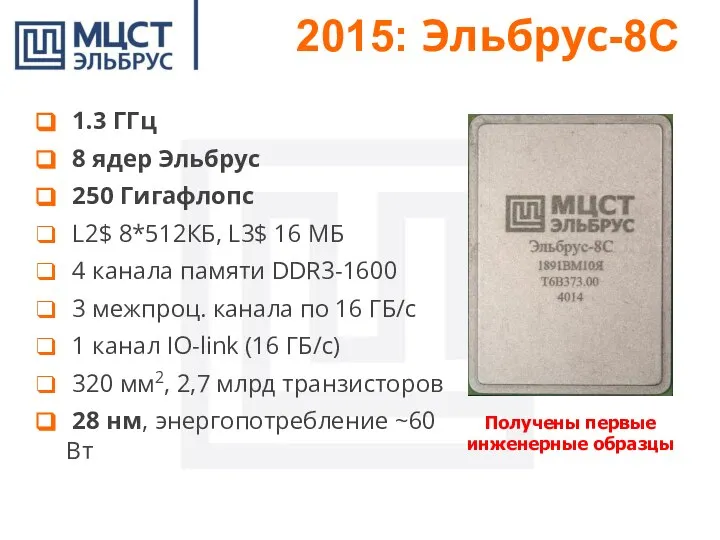

- 12. 2015: Эльбрус-8С 1.3 ГГц 8 ядер Эльбрус 250 Гигафлопс L2$ 8*512КБ, L3$ 16 МБ 4 канала

- 13. 2015: КПИ-2 1 канал IO-link (16 ГБ/с) PCI Express 2.0 x20 3 * Gigabit Ethernet 8

- 14. Сервер на базе четырёх процессоров Эльбрус-8С 4 процессора Эльбрус-8С Южный мост КПИ-2 Оперативная память до 256

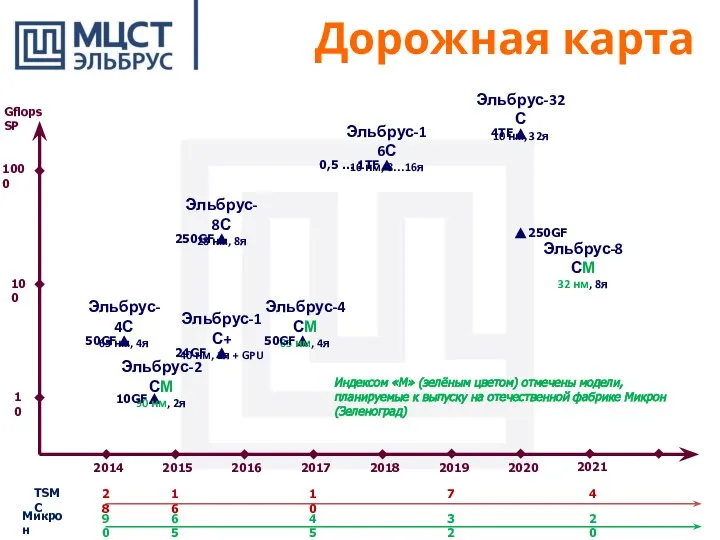

- 15. 2014 2015 2016 2017 2018 2019 2020 2021 10 100 1000 Gflops SP TSMC Микрон Эльбрус-16С

- 16. Ошибки и уязвимости Распределение уязвимостей АСУ ТП по типам Отчёт «Безопасность промышленных систем в цифрах v2.1»,

- 17. Память приложения

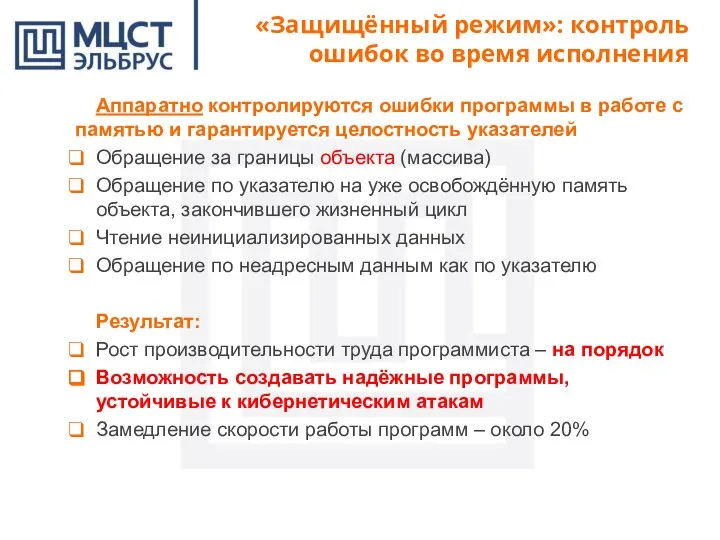

- 18. «Защищённый режим»: контроль ошибок во время исполнения Аппаратно контролируются ошибки программы в работе с памятью и

- 19. Защищённый режим Эльбруса. Структура дескриптора 128 bit Дескриптор: Значения тегов: 00 - Неинициализированное 10 – Данные,

- 20. Защищённый режим Эльбруса. Использование дескриптора

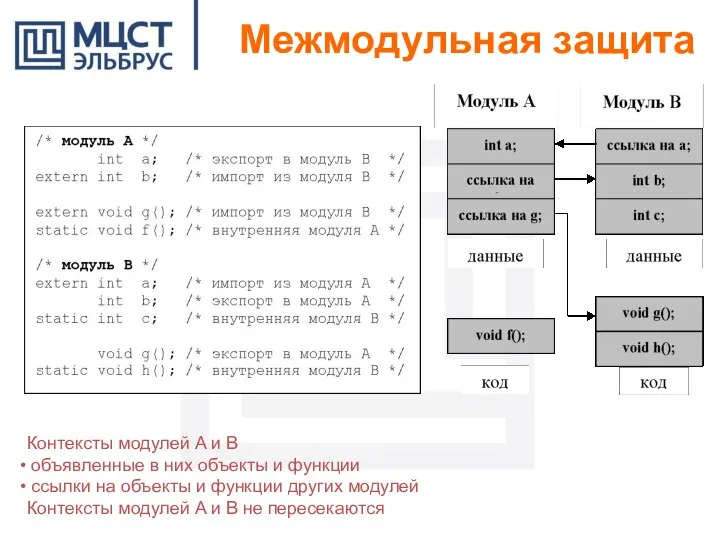

- 21. Контексты модулей A и B объявленные в них объекты и функции ссылки на объекты и функции

- 22. Каждому модулю соответствует свой дескриптор Дескриптор модуля хранится при исполнении на аппаратных регистрах, недоступных пользователю При

- 24. Скачать презентацию

Части тела

Части тела Системный блок

Системный блок Изменения в налоговом законодательстве осенняя сессия 2011 г.

Изменения в налоговом законодательстве осенняя сессия 2011 г. ИВАШУТИН ДМИТРИЙ АЛЕКСАНДРОВИЧ

ИВАШУТИН ДМИТРИЙ АЛЕКСАНДРОВИЧ #Шашники - школа аниматора Young

#Шашники - школа аниматора Young Презентация на тему Формирование у детей представлений о здоровом образе жизни

Презентация на тему Формирование у детей представлений о здоровом образе жизни «Об итогах работы с одаренными детьми на муниципальном и региональном уровнях в 2011 году и направлениях работы в 2012 году».

«Об итогах работы с одаренными детьми на муниципальном и региональном уровнях в 2011 году и направлениях работы в 2012 году». Управление кадрами на предприятии

Управление кадрами на предприятии Основные элементы стиля

Основные элементы стиля УП ОПИ. Нормы и допуски содержания стрелочных переводов

УП ОПИ. Нормы и допуски содержания стрелочных переводов Имя существительное как часть речи

Имя существительное как часть речи Студия танцев Natrube. Бизнес-идея

Студия танцев Natrube. Бизнес-идея ЭЛЕКТРОННЫЙ МУНИЦИПАЛИТЕТ

ЭЛЕКТРОННЫЙ МУНИЦИПАЛИТЕТ Конкурс Политехнического музея «Часы и время»

Конкурс Политехнического музея «Часы и время» Види статистичних звітів

Види статистичних звітів ВОДА-ИСТОЧНИК ЖИЗНИ НА НАШЕЙ ПЛАНЕТЕ. СВОЙСТВА ВОДЫ

ВОДА-ИСТОЧНИК ЖИЗНИ НА НАШЕЙ ПЛАНЕТЕ. СВОЙСТВА ВОДЫ Баскетбол

Баскетбол Здороваемся

Здороваемся Совещание с грузоотправителями Калининградской железной дороги

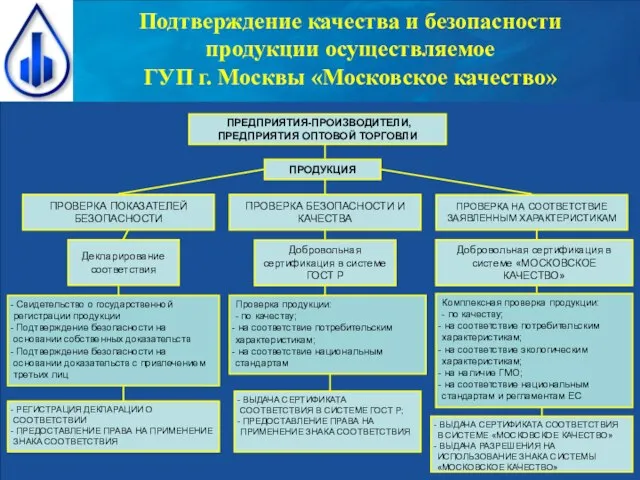

Совещание с грузоотправителями Калининградской железной дороги Подтверждение качества и безопасности продукции осуществляемое ГУП г. Москвы «Московское качество»

Подтверждение качества и безопасности продукции осуществляемое ГУП г. Москвы «Московское качество» Политическая система

Политическая система Человек и закон. Правонарушения

Человек и закон. Правонарушения 20161219_svoystva_vody

20161219_svoystva_vody Специфика организации и проведения культурно-досугового мероприятия для молодежи Ночь в библиотеке

Специфика организации и проведения культурно-досугового мероприятия для молодежи Ночь в библиотеке Шаблон презентации для конференции

Шаблон презентации для конференции 1494606997_prezentaciya-ane-matveevoy-14-gr.pptx

1494606997_prezentaciya-ane-matveevoy-14-gr.pptx Здоровье и ЗОЖ

Здоровье и ЗОЖ Урок по ОРКСЭ, модуль Основы православной культуры. Заповеди

Урок по ОРКСЭ, модуль Основы православной культуры. Заповеди