Содержание

- 2. Процессор и память: Команды и данные CPU RAM

- 3. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора

- 4. Процессор и память: Команды и данные CPU Регистры КЭШ 1го уровня КЭШ 2го уровня Оперативная память

- 5. Виртуальная память Виртуальный адрес Реальный адрес Таблица страниц в ОЗУ Процессор

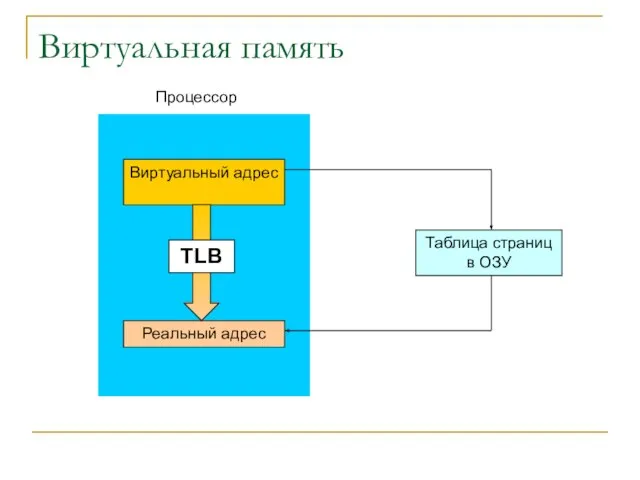

- 6. Виртуальная память Виртуальный адрес Реальный адрес Таблица страниц в ОЗУ Процессор TLB

- 7. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора

- 8. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

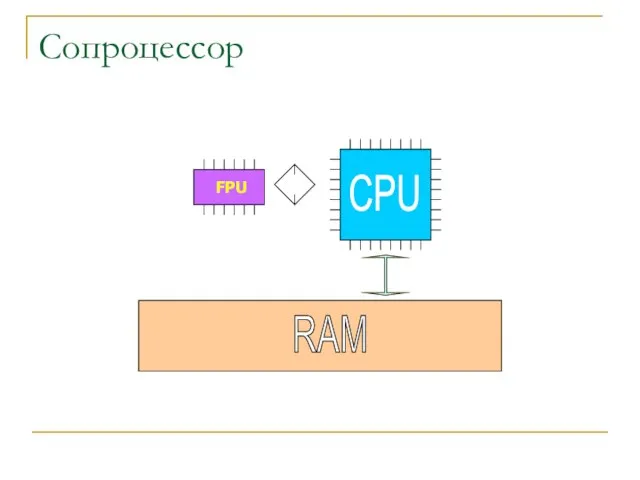

- 9. Сопроцессор FPU CPU RAM

- 10. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

- 11. Конвейер команд 1 2 1 2 1 2 1 2 1 2 Ступени Выборка команды Декодирование

- 12. Конвейер команд 1 2 3 4 5 6 1 2 3 4 5 6 1 2

- 13. Конвейер: Условные ветвления Конвейер ? Проблема: Условные переходы

- 14. Конвейер: Условные ветвления Конвейер ?* Проблема: Условные переходы Решения: Спекулятивное исполнение с предсказанием переходов Использование условных

- 15. Конвейер: Условные ветвления Конвейер Проблема: Условные переходы Решения: Спекулятивное исполнение с предсказанием переходов Использование условных команд

- 16. Конвейер: Условные ветвления Конвейер Проблема: Условные переходы Решения: Спекулятивное исполнение с предсказанием переходов Использование условных команд

- 17. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

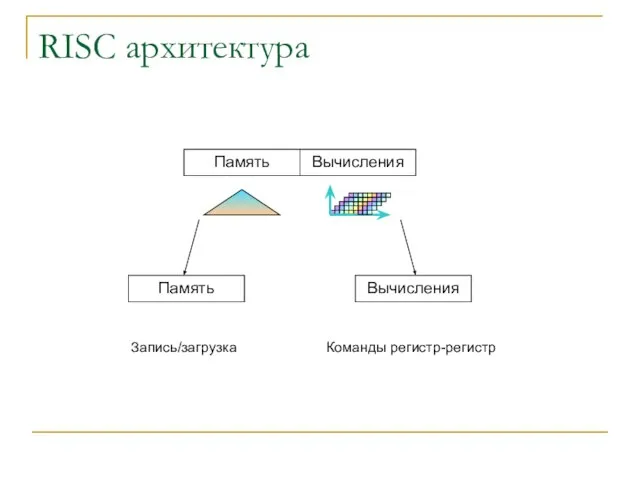

- 18. RISC архитектура Память Вычисления Память Вычисления Запись/загрузка Команды регистр-регистр

- 19. CISC Большое количество команд Много типов данных Различная длина инструкций Небольшое количество регистров Ориентация на процессор

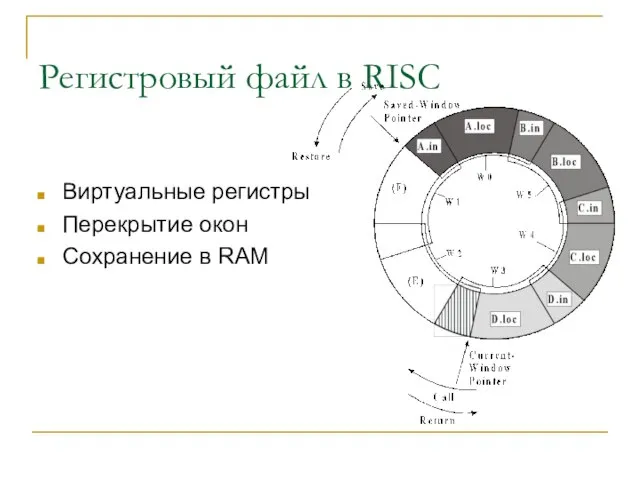

- 20. Регистровый файл в RISC Виртуальные регистры Перекрытие окон Сохранение в RAM

- 21. Пути усовершенствования быстродействия Улучшение доступа к памяти Увеличение производительности процессора Дополнительные устройства Конвейеризация Упрощение команд Параллелизм

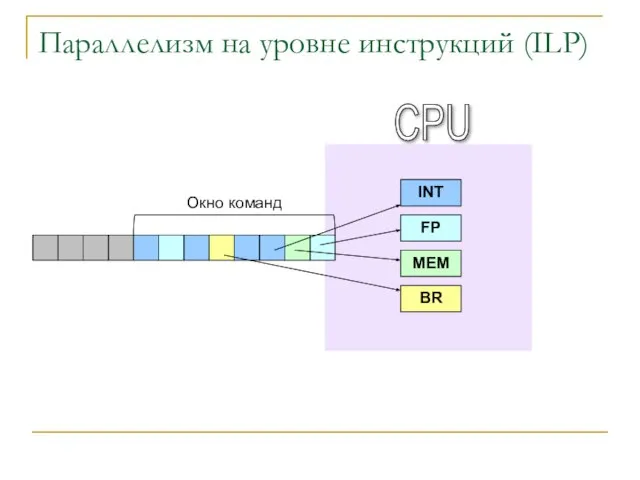

- 22. Параллелизм на уровне инструкций (ILP) INT FP MEM BR Окно команд CPU

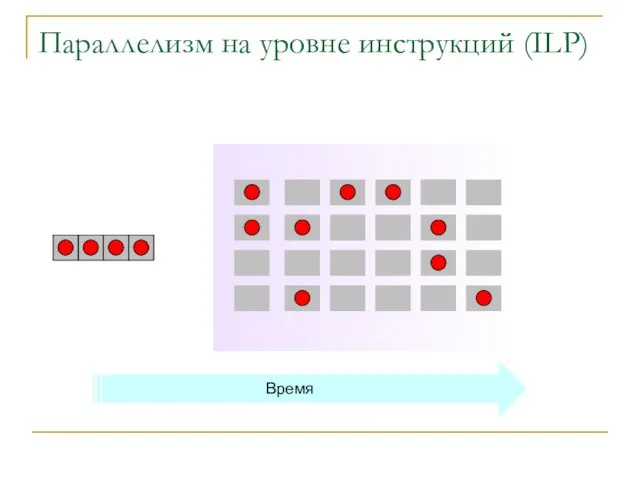

- 23. Параллелизм на уровне инструкций (ILP) Время

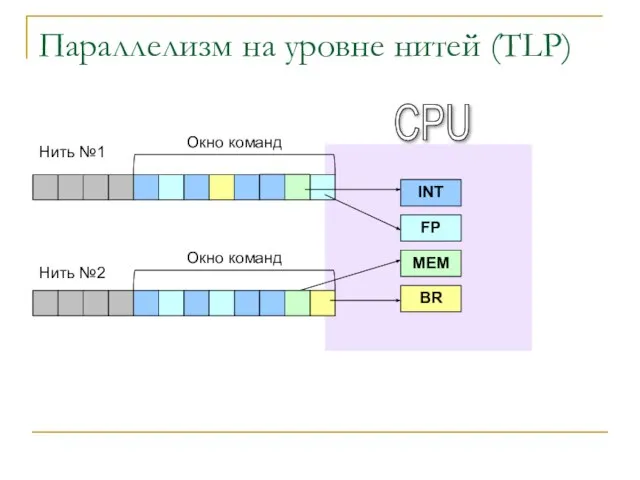

- 24. Параллелизм на уровне нитей (TLP) INT FP MEM BR Окно команд CPU Окно команд Нить №1

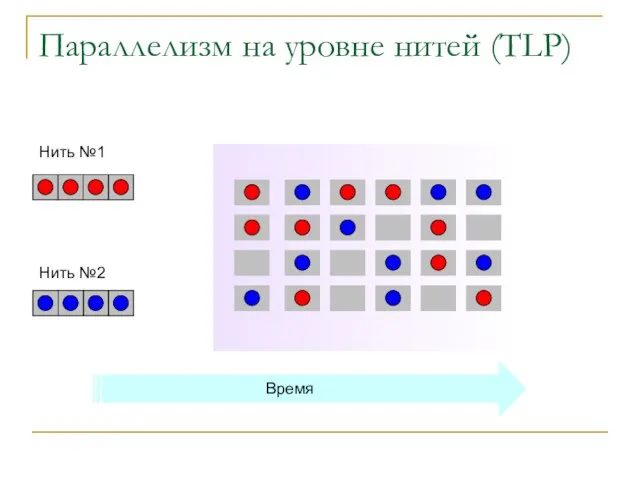

- 25. Параллелизм на уровне нитей (TLP) Время Нить №1 Нить №2

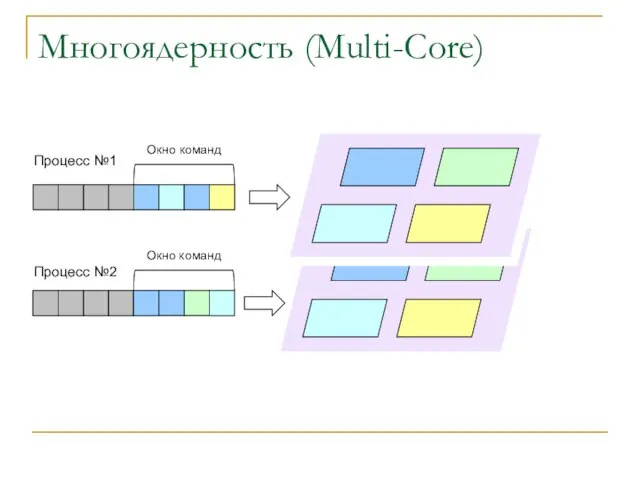

- 26. Многоядерность (Multi-Core) Окно команд Окно команд Процесс №1 Процесс №2

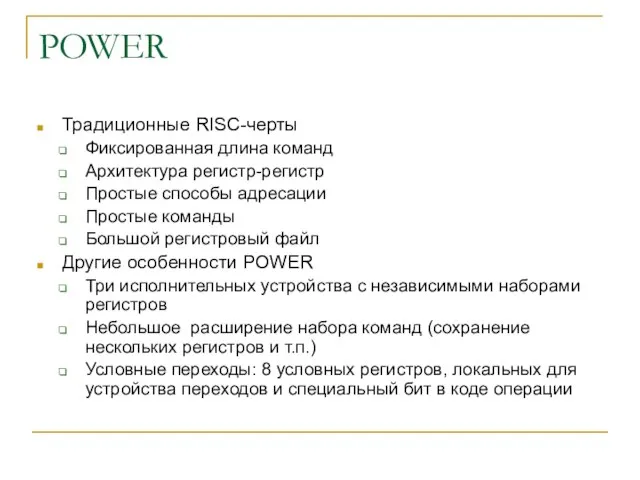

- 27. POWER Традиционные RISC-черты Фиксированная длина команд Архитектура регистр-регистр Простые способы адресации Простые команды Большой регистровый файл

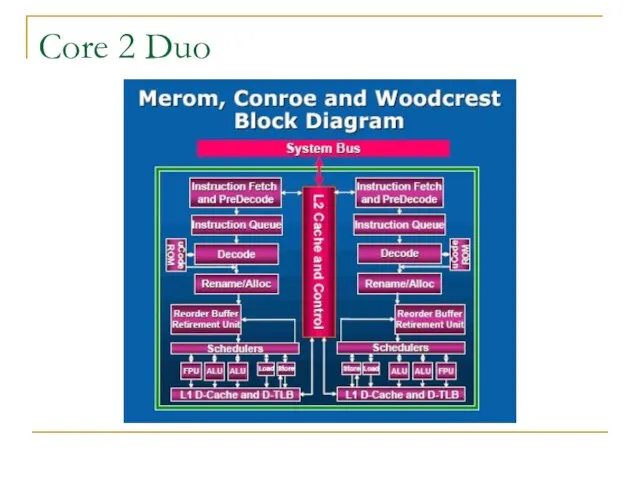

- 28. Core 2 Duo

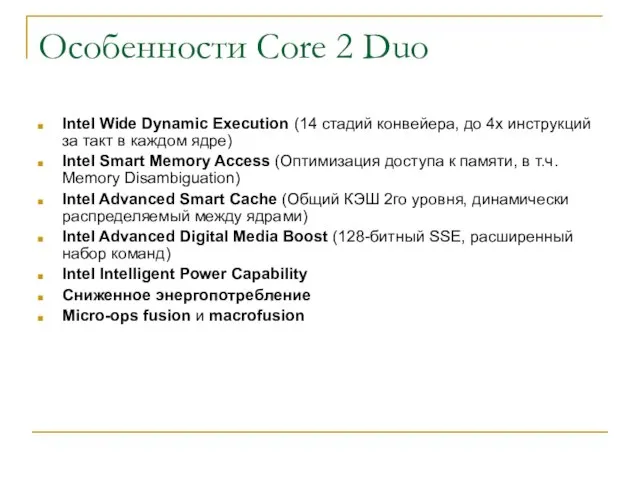

- 29. Особенности Core 2 Duo Intel Wide Dynamic Execution (14 стадий конвейера, до 4х инструкций за такт

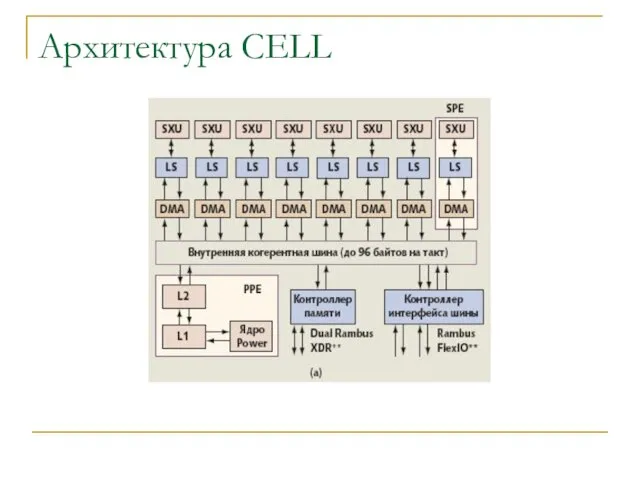

- 30. Архитектура CELL

- 32. Скачать презентацию

Ещё одна экскурсия в мой виртуальный музей

Ещё одна экскурсия в мой виртуальный музей Рисуем карандашом

Рисуем карандашом Барокко классицизм

Барокко классицизм Подростковый клуб Скаут. Проект

Подростковый клуб Скаут. Проект Разметка заготовок из древесины

Разметка заготовок из древесины Empire State Building

Empire State Building Презентация на тему Английские колонии в Северной Америке 7 класс

Презентация на тему Английские колонии в Северной Америке 7 класс 1 октября - День добра и уважения

1 октября - День добра и уважения мезенская роспись

мезенская роспись Права ребенка

Права ребенка Кто под маской? Викторина

Кто под маской? Викторина Департамент образования Вологодской области

Департамент образования Вологодской области НОВЫЙ УЧЕБНЫЙ КУРС

НОВЫЙ УЧЕБНЫЙ КУРС Лесная промышленность

Лесная промышленность Презентация на тему Внешнее строение птиц. Строение перьев

Презентация на тему Внешнее строение птиц. Строение перьев Образ ворона в русской и зарубежной литературе

Образ ворона в русской и зарубежной литературе Система здравоохранения в Израиле

Система здравоохранения в Израиле Стиль Шебби-шик

Стиль Шебби-шик Экскурсия в лексический сад

Экскурсия в лексический сад Тургенев-сказочник

Тургенев-сказочник Тема: «Составление и использование игровых компьютерных презентаций на уроке товароведения пищевых продуктов»

Тема: «Составление и использование игровых компьютерных презентаций на уроке товароведения пищевых продуктов» Презентация на тему Развитие государства и права США в ХХ веке

Презентация на тему Развитие государства и права США в ХХ веке  Таможенная процедура – «Экспорта» Подготовили: Миронова Шайдуллина

Таможенная процедура – «Экспорта» Подготовили: Миронова Шайдуллина ПОЧАТОК Украинской революции

ПОЧАТОК Украинской революции  Самые страшные тюрьмы России и мира

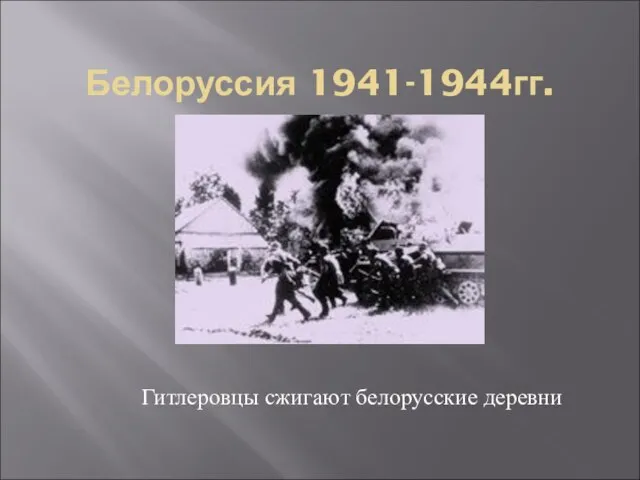

Самые страшные тюрьмы России и мира Белоруссия 1941-1944гг

Белоруссия 1941-1944гг Обмен веществ и энергии в клетке

Обмен веществ и энергии в клетке Программа В.Ф.Виноградовой Начальная школа XXI века

Программа В.Ф.Виноградовой Начальная школа XXI века