Содержание

- 2. Background Required to Understand this Chapter Advanced Computer Architecture. Smruti R. Sarangi http://www.cse.iitd.ac.in/~srsarangi/archbooksoft.html

- 3. Advanced Computer Architecture. Smruti R. Sarangi

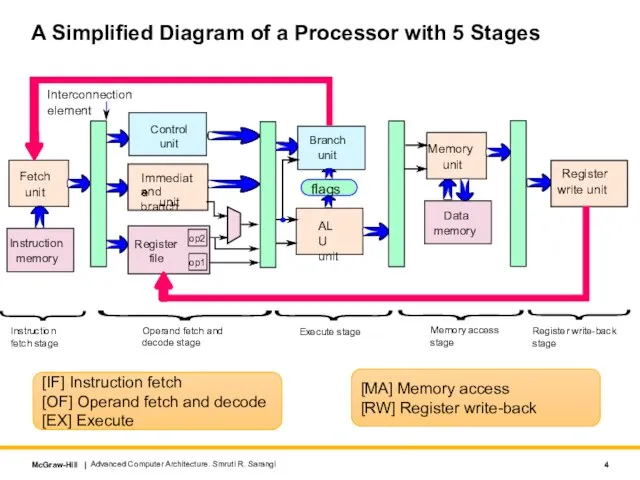

- 4. A Simplified Diagram of a Processor with 5 Stages Advanced Computer Architecture. Smruti R. Sarangi Fetch

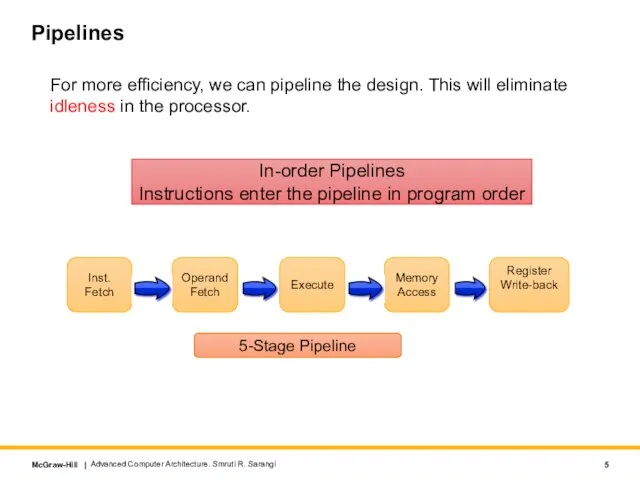

- 5. Pipelines For more efficiency, we can pipeline the design. This will eliminate idleness in the processor.

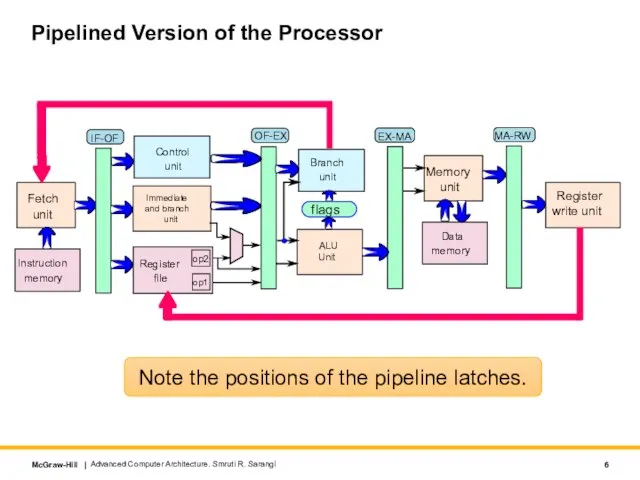

- 6. Pipelined Version of the Processor Advanced Computer Architecture. Smruti R. Sarangi Note the positions of the

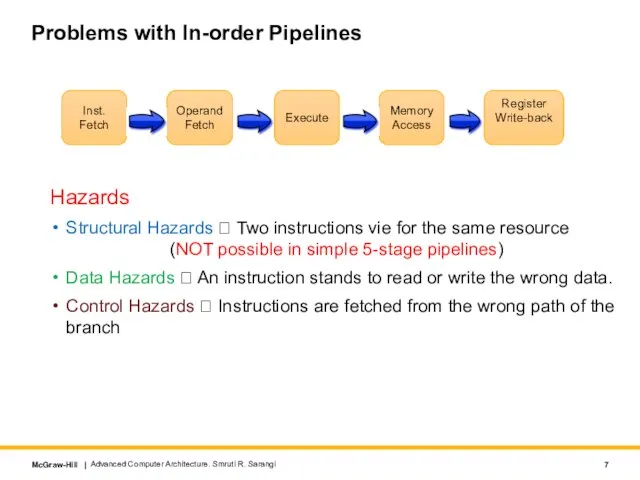

- 7. Problems with In-order Pipelines Hazards Structural Hazards ? Two instructions vie for the same resource (NOT

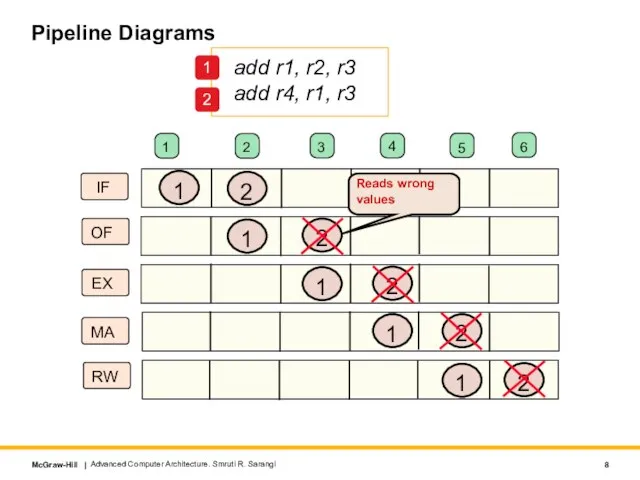

- 8. Pipeline Diagrams Advanced Computer Architecture. Smruti R. Sarangi add r1, r2, r3 add r4, r1, r3

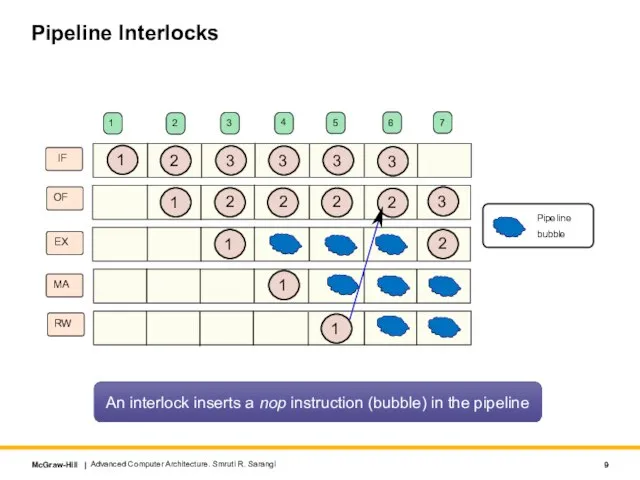

- 9. Pipeline Interlocks Advanced Computer Architecture. Smruti R. Sarangi IF OF EX MA RW 1 1 1

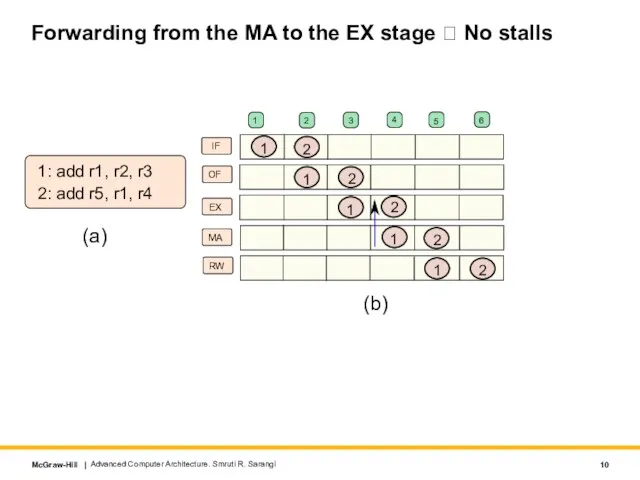

- 10. Forwarding from the MA to the EX stage ? No stalls Advanced Computer Architecture. Smruti R.

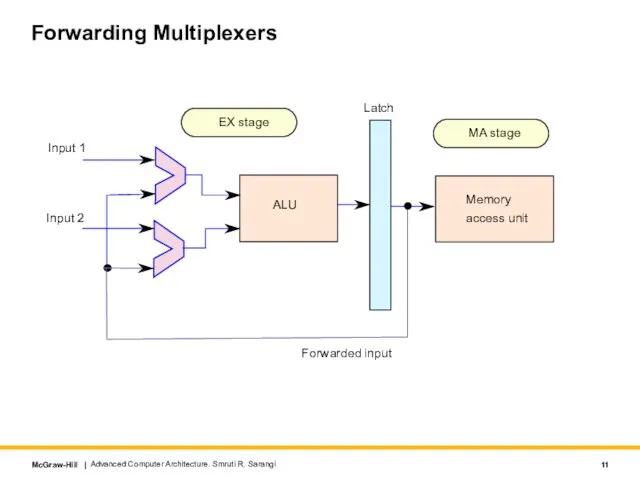

- 11. Forwarding Multiplexers Advanced Computer Architecture. Smruti R. Sarangi ALU Latch Memory access unit Forwarded input Input

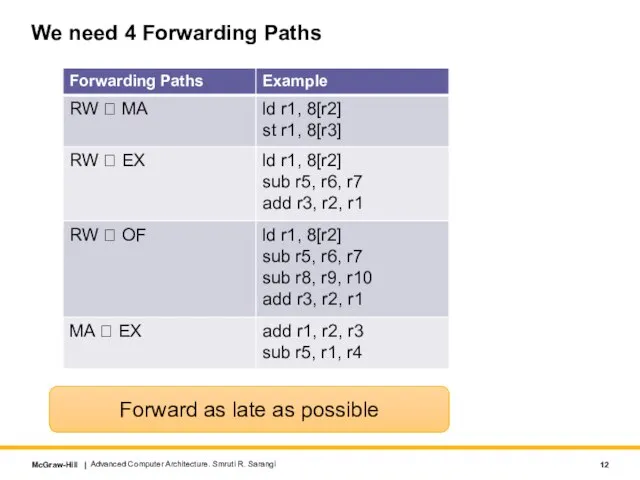

- 12. We need 4 Forwarding Paths Advanced Computer Architecture. Smruti R. Sarangi Forward as late as possible

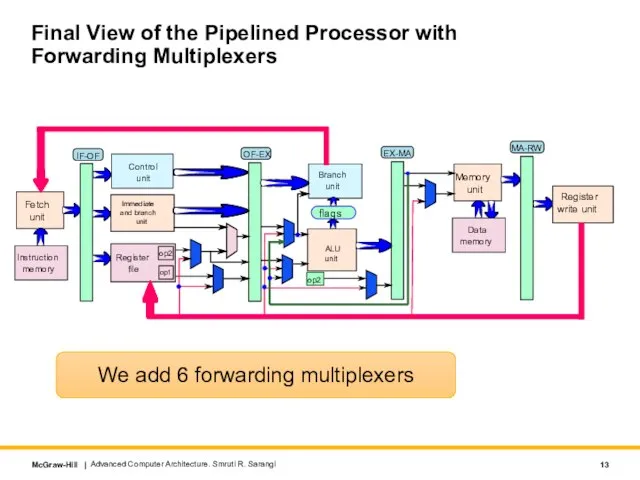

- 13. Final View of the Pipelined Processor with Forwarding Multiplexers Advanced Computer Architecture. Smruti R. Sarangi We

- 14. Data Hazards in In-order Pipelines with Forwarding ld r4, 4[r0] add r5, r4, 1 Need the

- 15. Solution: Stall the Pipeline ld r4, 4[r0] add r5, r4, 1 Cycle N Cycle N+1 ld

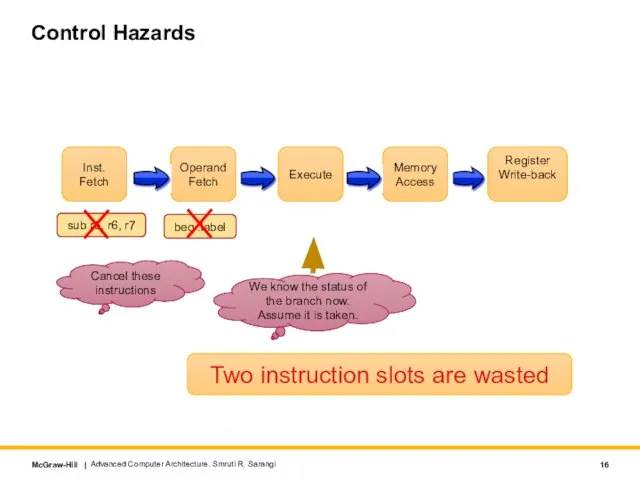

- 16. Control Hazards beq .label add r1, r2, r3 beq .label sub r5, r6, r7 We know

- 17. Advanced Computer Architecture. Smruti R. Sarangi

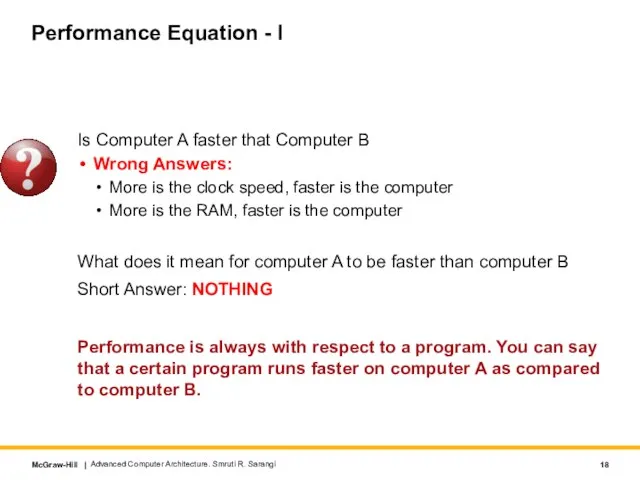

- 18. Performance Equation - I Is Computer A faster that Computer B Wrong Answers: More is the

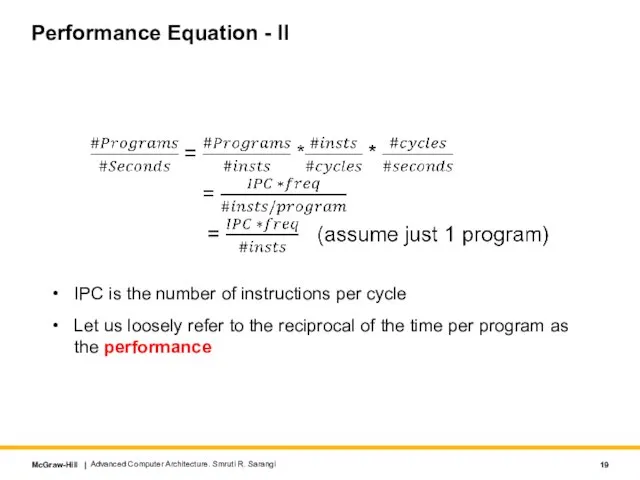

- 19. Performance Equation - II IPC is the number of instructions per cycle Let us loosely refer

- 20. So, what does performance depend on … #instructions in the program Depends on the compiler Frequency

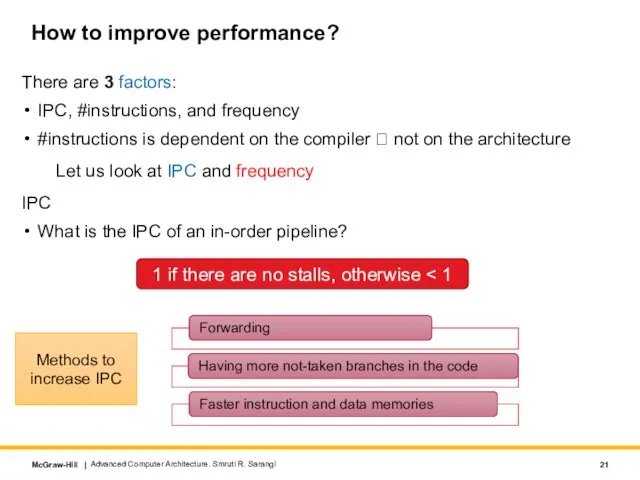

- 21. How to improve performance? There are 3 factors: IPC, #instructions, and frequency #instructions is dependent on

- 22. What about frequency? What is frequency dependent on … Frequency = 1 / clock period Clock

- 23. Limits to Increasing Frequency Assume that we have the fastest possible transistors Can we increase the

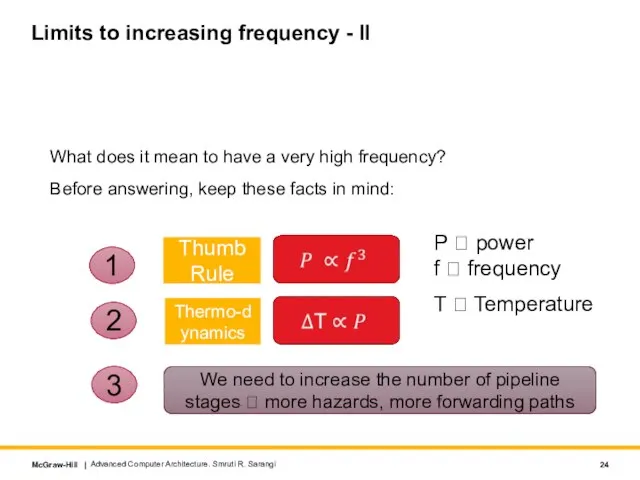

- 24. Limits to increasing frequency - II What does it mean to have a very high frequency?

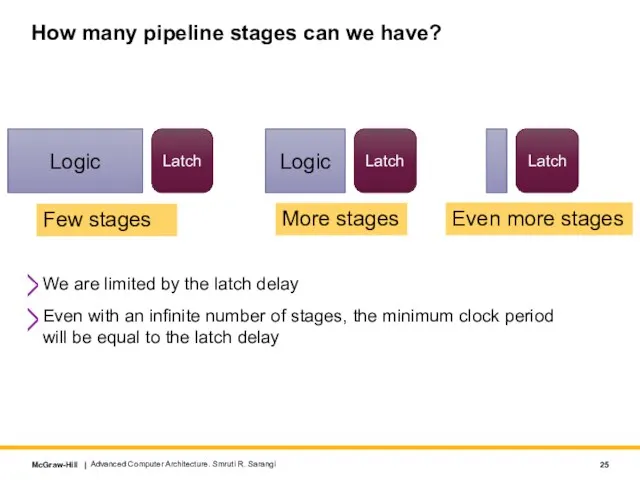

- 25. How many pipeline stages can we have? We are limited by the latch delay Even with

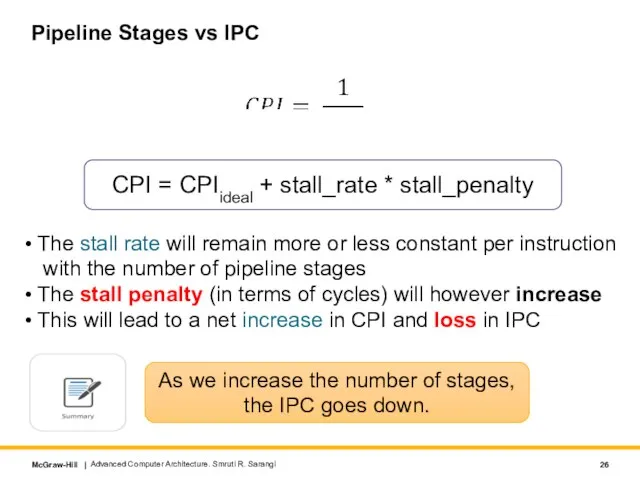

- 26. Pipeline Stages vs IPC CPI = CPIideal + stall_rate * stall_penalty The stall rate will remain

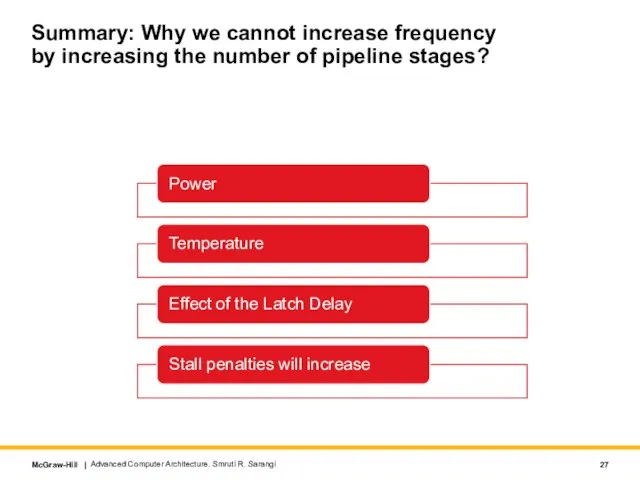

- 27. Summary: Why we cannot increase frequency by increasing the number of pipeline stages? Advanced Computer Architecture.

- 28. Since we cannot increase frequency … Increase IPC Advanced Computer Architecture. Smruti R. Sarangi

- 29. Increase IPC Issue more instructions per cycle 2, 4, or 8 instructions Make it a superscalar

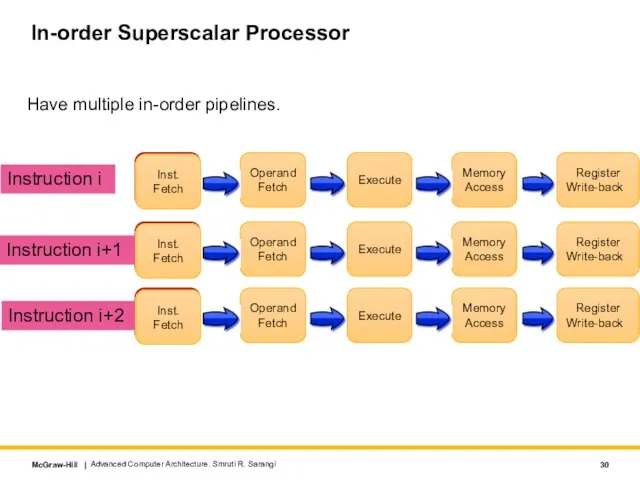

- 30. In-order Superscalar Processor Have multiple in-order pipelines. Inst. Fetch Operand Fetch Execute Memory Access Register Write-back

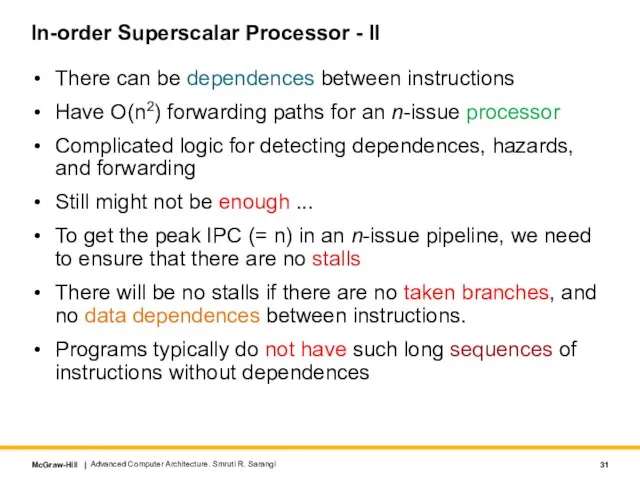

- 31. In-order Superscalar Processor - II There can be dependences between instructions Have O(n2) forwarding paths for

- 32. Contents Advanced Computer Architecture. Smruti R. Sarangi

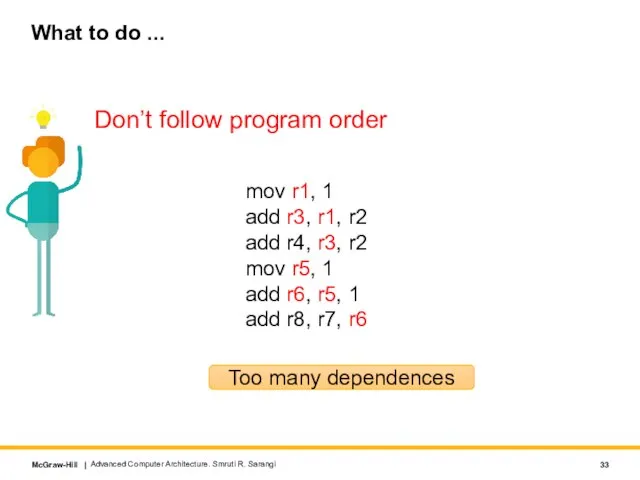

- 33. What to do ... Don’t follow program order Too many dependences mov r1, 1 add r3,

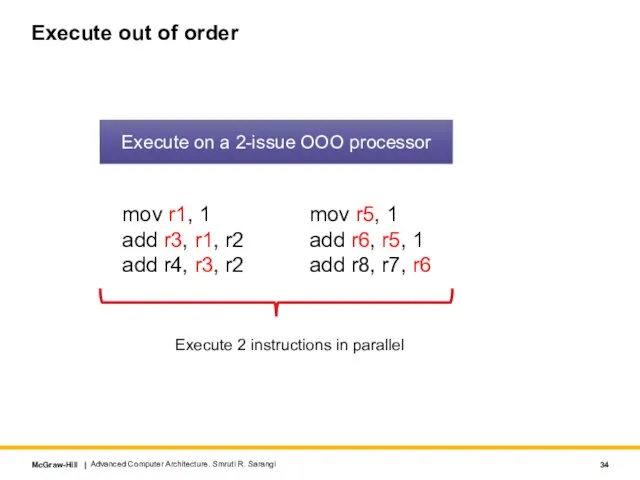

- 34. Execute out of order mov r1, 1 add r3, r1, r2 add r4, r3, r2 mov

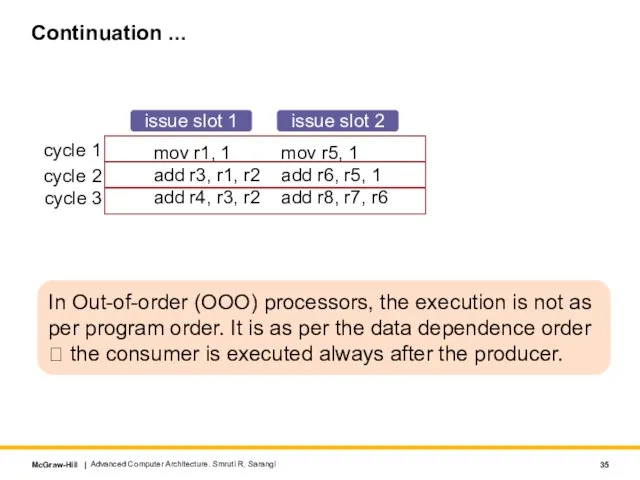

- 35. Continuation ... mov r1, 1 add r3, r1, r2 add r4, r3, r2 mov r5, 1

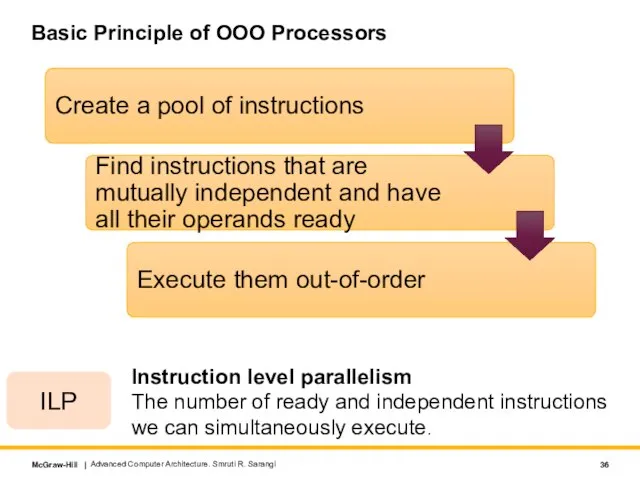

- 36. Basic Principle of OOO Processors Advanced Computer Architecture. Smruti R. Sarangi ILP Instruction level parallelism The

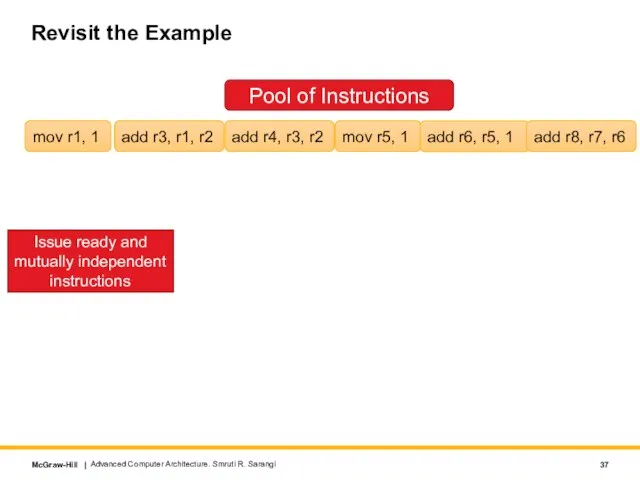

- 37. Revisit the Example mov r1, 1 add r3, r1, r2 add r4, r3, r2 mov r5,

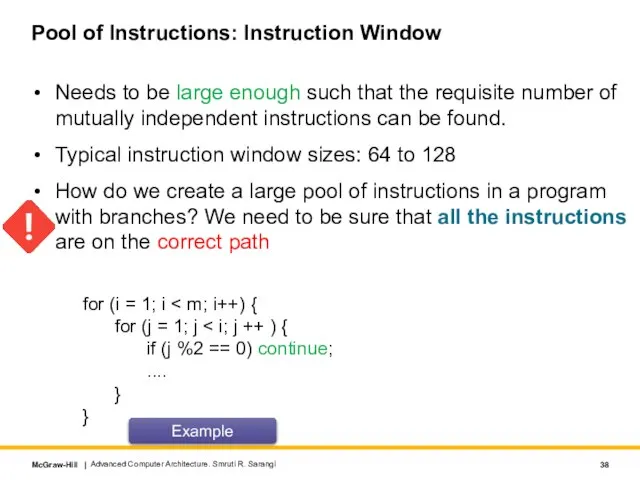

- 38. Pool of Instructions: Instruction Window Needs to be large enough such that the requisite number of

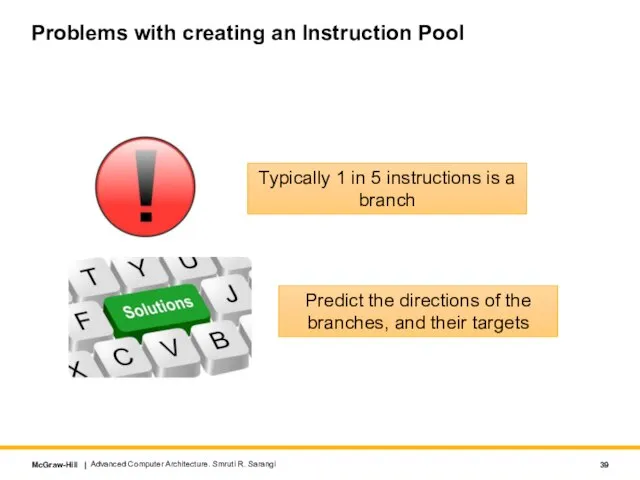

- 39. Problems with creating an Instruction Pool Typically 1 in 5 instructions is a branch Predict the

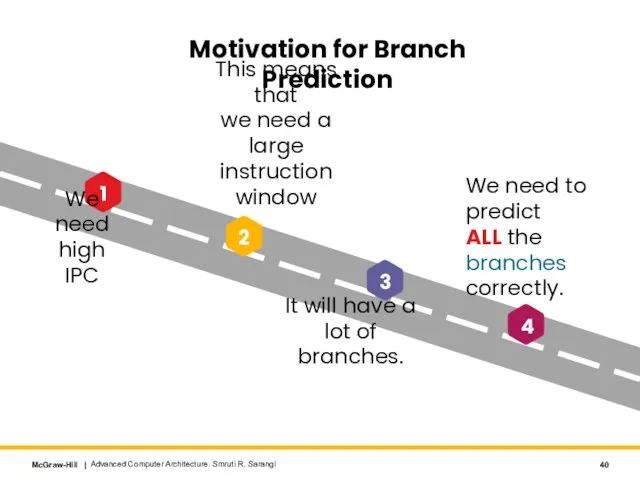

- 40. Advanced Computer Architecture. Smruti R. Sarangi Motivation for Branch Prediction 1 2 3 4 We need

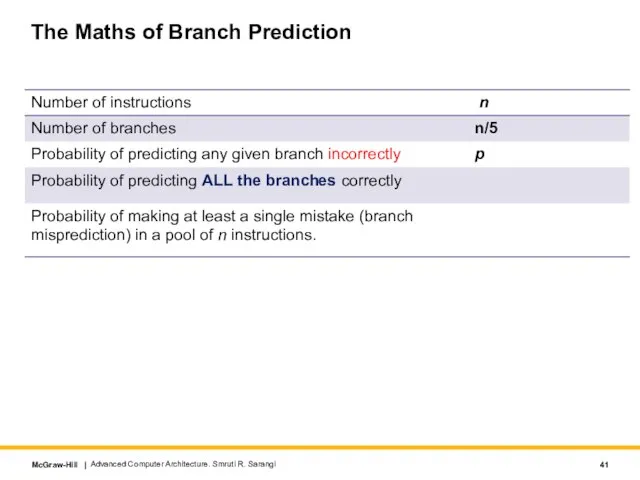

- 41. The Maths of Branch Prediction Advanced Computer Architecture. Smruti R. Sarangi

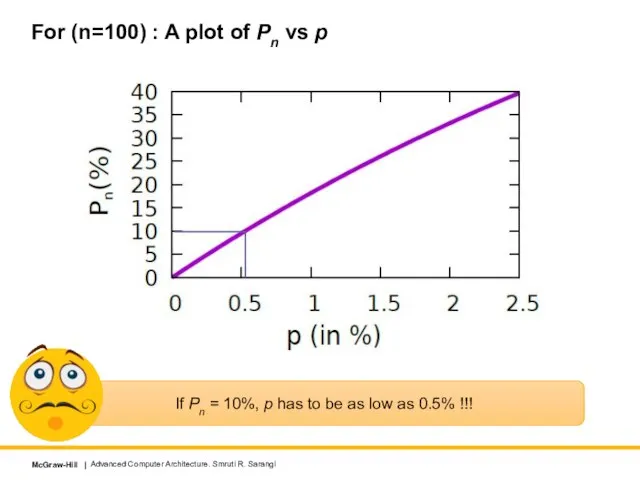

- 42. Advanced Computer Architecture. Smruti R. Sarangi For (n=100) : A plot of Pn vs p If

- 43. Advanced Computer Architecture. Smruti R. Sarangi If we need a large instruction window, we need a

- 44. Advanced Computer Architecture. Smruti R. Sarangi Nature of Dependences

- 45. Dependences between Instructions Program Order Dependence mov r1, 1 mov r2, 2 One instruction appears after

- 46. Data Dependences RAW ? Read after Write Dependence (True dependence) mov r1, 1 add r3, r1,

- 47. Data Dependences - II WAW ? Write after Write Dependence (Output dependence) mov r1, 1 add

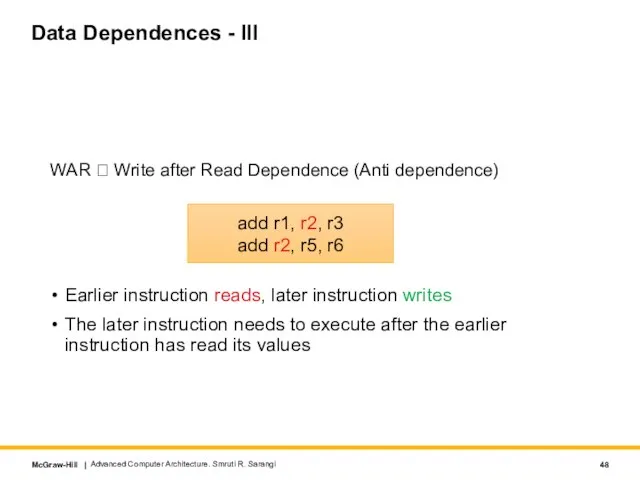

- 48. Data Dependences - III WAR ? Write after Read Dependence (Anti dependence) add r1, r2, r3

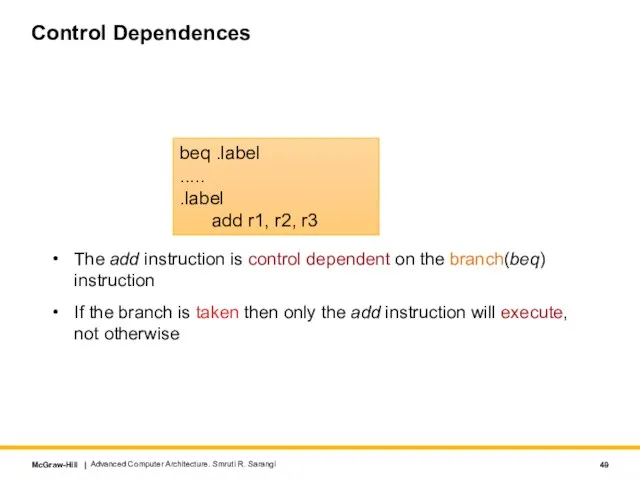

- 49. Control Dependences The add instruction is control dependent on the branch(beq) instruction If the branch is

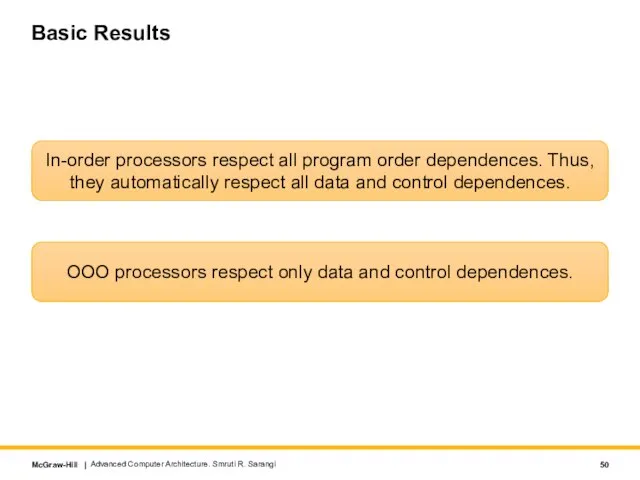

- 50. Basic Results In-order processors respect all program order dependences. Thus, they automatically respect all data and

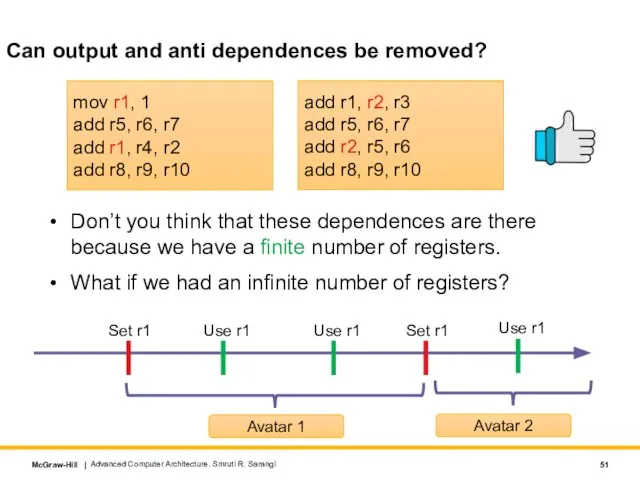

- 51. Can output and anti dependences be removed? Don’t you think that these dependences are there because

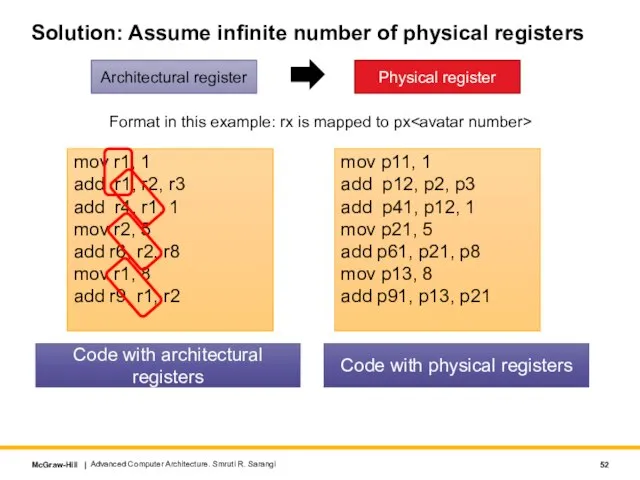

- 52. Solution: Assume infinite number of physical registers mov r1, 1 add r1, r2, r3 add r4,

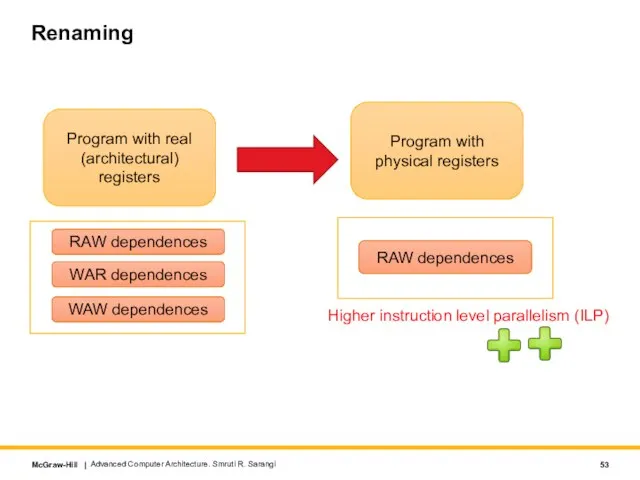

- 53. Renaming Program with real (architectural) registers Program with physical registers RAW dependences WAR dependences WAW dependences

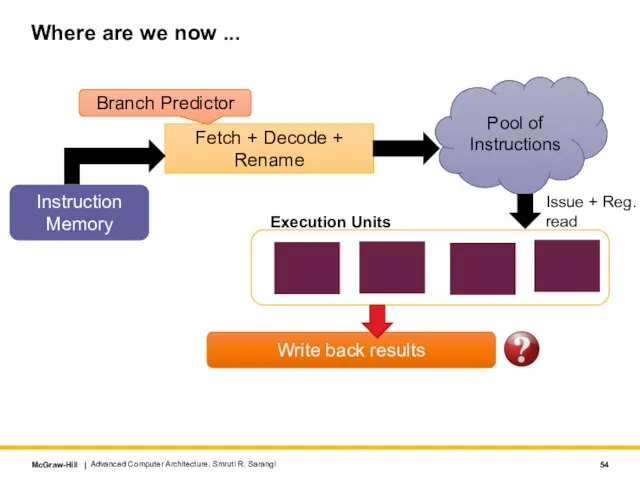

- 54. Where are we now ... Fetch + Decode + Rename Instruction Memory Pool of Instructions Execution

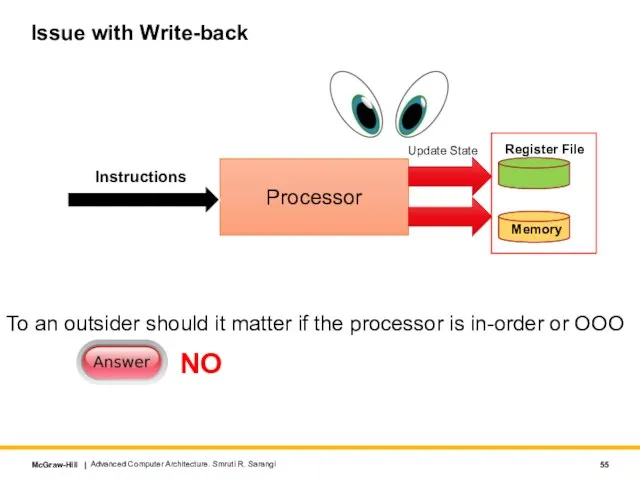

- 55. Issue with Write-back To an outsider should it matter if the processor is in-order or OOO

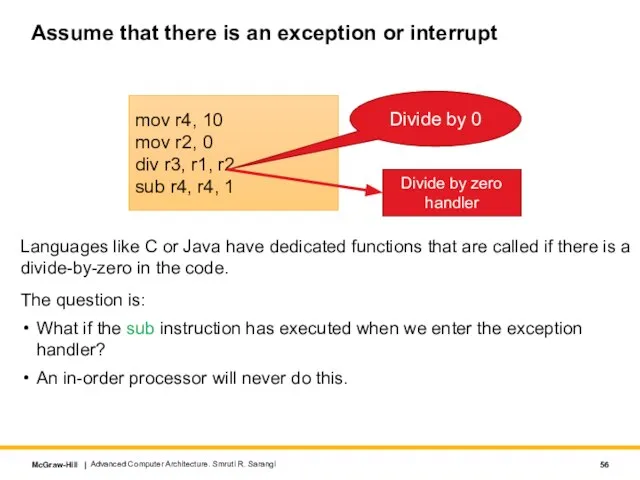

- 56. Assume that there is an exception or interrupt Languages like C or Java have dedicated functions

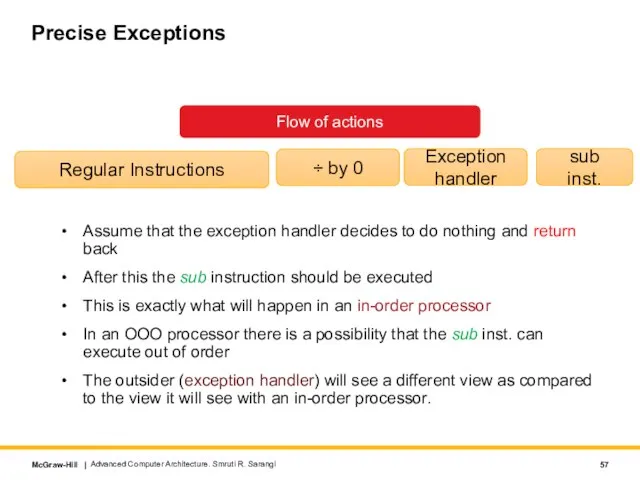

- 57. Precise Exceptions Assume that the exception handler decides to do nothing and return back After this

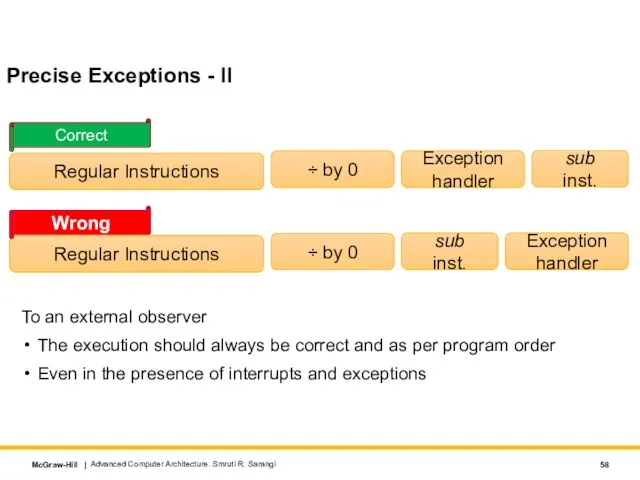

- 58. Precise Exceptions - II To an external observer The execution should always be correct and as

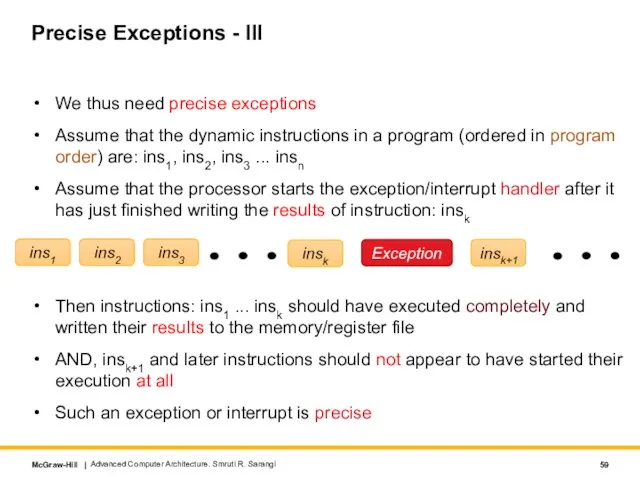

- 59. Precise Exceptions - III We thus need precise exceptions Assume that the dynamic instructions in a

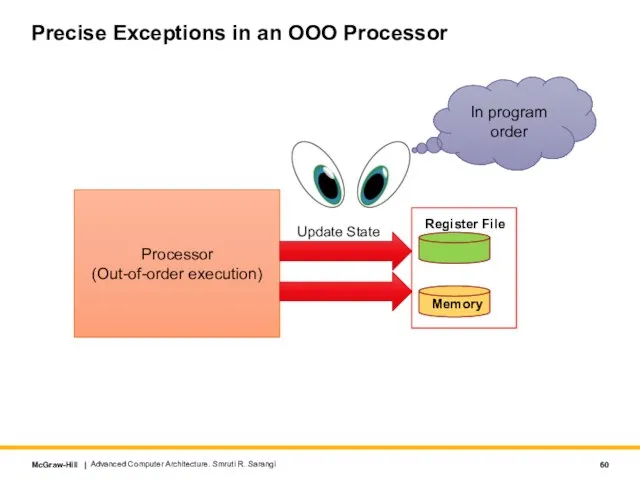

- 60. Precise Exceptions in an OOO Processor Processor (Out-of-order execution) Register File Memory Update State In program

- 61. Advanced Computer Architecture. Smruti R. Sarangi In-order pipelines have a limited IPC because of hazards and

- 63. Скачать презентацию

![Data Hazards in In-order Pipelines with Forwarding ld r4, 4[r0] add r5,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/901210/slide-13.jpg)

![Solution: Stall the Pipeline ld r4, 4[r0] add r5, r4, 1 Cycle](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/901210/slide-14.jpg)

Сахарный диабет, профилактика

Сахарный диабет, профилактика Национальная книжная палата БеларусиЕрмолич Елена Ивановна

Национальная книжная палата БеларусиЕрмолич Елена Ивановна Эмпирическая Игра

Эмпирическая Игра Презентация на тему Заказники Новосибирской области

Презентация на тему Заказники Новосибирской области Послание Президента Республики Казахстан Назарбаева Н.А. народу Казахстана

Послание Президента Республики Казахстан Назарбаева Н.А. народу Казахстана Модернизированная функция с постоянной эластичностью замещения.

Модернизированная функция с постоянной эластичностью замещения. Презентация на тему Я - гражданин и патриот России

Презентация на тему Я - гражданин и патриот России Планирование и ликвидации аварий

Планирование и ликвидации аварий Формирование творческих способностей обучающихся

Формирование творческих способностей обучающихся 20171011_madagaskar_-

20171011_madagaskar_- Презентация на тему Осенний лес

Презентация на тему Осенний лес  Экологический жизненный цикл вещи и возможности его оптимизации

Экологический жизненный цикл вещи и возможности его оптимизации Экологичный способ производства водорода

Экологичный способ производства водорода УК РФ Статья 131. Изнасилование

УК РФ Статья 131. Изнасилование Эскимосы

Эскимосы Арктика

Арктика История школьного самоуправления

История школьного самоуправления Одночлены

Одночлены Кроссворды. Сказки

Кроссворды. Сказки ОАО «НТЦ электроэнергетики» Методы инструментального выявления недостоверного учета электрической энергии

ОАО «НТЦ электроэнергетики» Методы инструментального выявления недостоверного учета электрической энергии Задания для текущего контроля

Задания для текущего контроля «А в попугаях я всё-таки длиннее» С чего начались измерения… Авторы: Уч-ся 8 класса Камышинский район Волгоградской области МБОУ Воднобуерачная СОШ

«А в попугаях я всё-таки длиннее» С чего начались измерения… Авторы: Уч-ся 8 класса Камышинский район Волгоградской области МБОУ Воднобуерачная СОШ  Права и обязанности ученика

Права и обязанности ученика Презентация на тему Мезозойская эра

Презентация на тему Мезозойская эра  Основные направления деятельности муниципальной методической службы (ГМЦ)

Основные направления деятельности муниципальной методической службы (ГМЦ) Карагандинский Технический Университет. Вниманию студентов IV курса!

Карагандинский Технический Университет. Вниманию студентов IV курса! Символьные и Строковые величины

Символьные и Строковые величины Гид на книжной полке. Чарующий мир кинематографа

Гид на книжной полке. Чарующий мир кинематографа