Содержание

- 2. Что делает вычислительная машина Компьютер преобразует коды, и эти преобразования должны соответствовать принятым правилам выполнения арифметико-логических

- 3. Основные понятия Цифра (символ) – обозначает предмет или явление и является необходимым в любой информационной системе.

- 4. Предпосылки создания и развития вычислительной техники С самого начала вычислительная техника была нацелена на устранение угроз

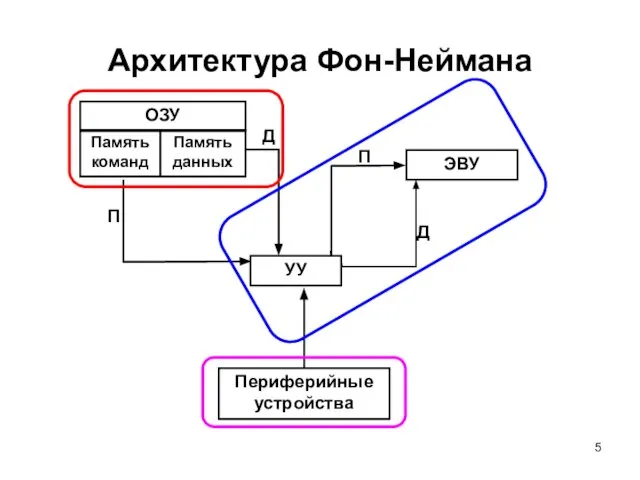

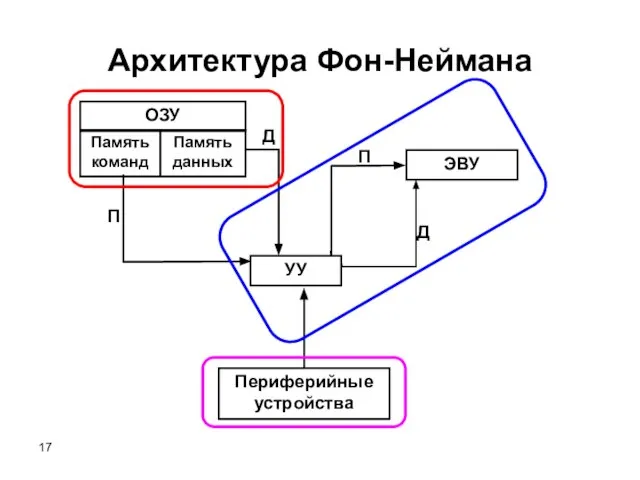

- 5. Архитектура Фон-Неймана УУ ЭВУ Периферийные устройства П П Д Д

- 6. Эл. база Эл. лампы Взаимосвязь компонентов Память Средства коммутации Булева алгебра Эл. реле

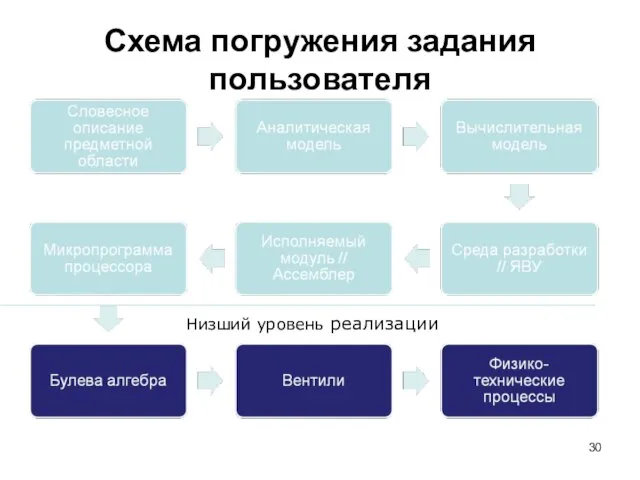

- 7. Схема погружения задания пользователя на уровень аппаратной реализации Предметная область Вычислительная модель Ассемблер Аналитическая модель Микрокоманды

- 8. Вычислительный процесс Вычислительный процесс с точки зрения автоматизации его кодов представляет собой взаимодействие на операционном устройстве

- 9. Учебный курс Принципы построения и функционирования ЭВМ Лекция 2 Алгоритмы и машина Тьюринга профессор ГУ-ВШЭ, доктор

- 10. Основное положение Вычислительный процесс можно реализовать только за N шагов Проблемы: Почему решить задачу пользователя за

- 11. Языки высокого уровня Вычислительная модель Вентиля (булева алгебра) Микрокоманды Предметная область Ассемблер Аналитическая модель Физико-технический процесс

- 12. Центральная проблема Центральная проблема, связанная с организацией вычислений, сосредоточена в предметной области: невозможно сформулировать аналитическую формулу

- 13. Алгоритм центральное понятие в теории вычислений представляет собой конечный набор правил выполнения некоторой процедуры, которая должна

- 14. Теория алгоритмов Восходит к Давиду Гильберту На рубеже 20 века сформулировал мировую проблему: Можно ли построить

- 15. Соглашение об алгоритме Вычислительным алгоритмом принято считать все то, что представимо в виде машины Тьюринга

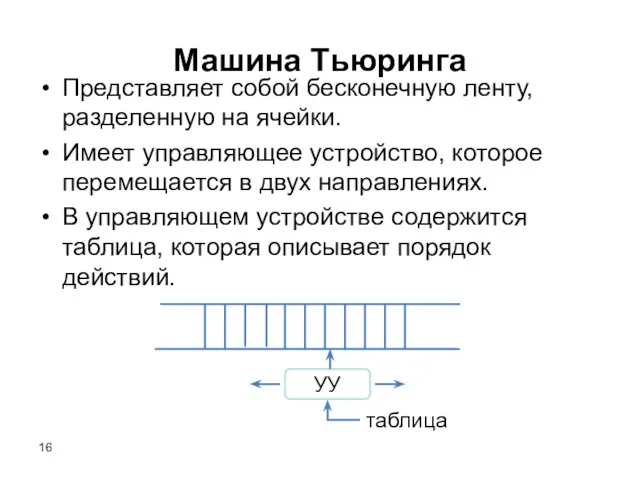

- 16. УУ таблица Машина Тьюринга Представляет собой бесконечную ленту, разделенную на ячейки. Имеет управляющее устройство, которое перемещается

- 17. Архитектура Фон-Неймана УУ ЭВУ Периферийные устройства П П Д Д

- 18. Языки высокого уровня Вычислительная модель Вентиля (булева алгебра) Микрокоманды Предметная область Ассемблер Аналитическая модель Физико-технический процесс

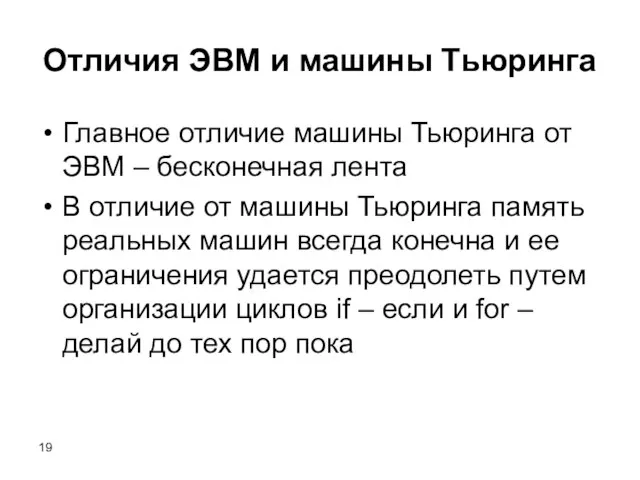

- 19. Отличия ЭВМ и машины Тьюринга Главное отличие машины Тьюринга от ЭВМ – бесконечная лента В отличие

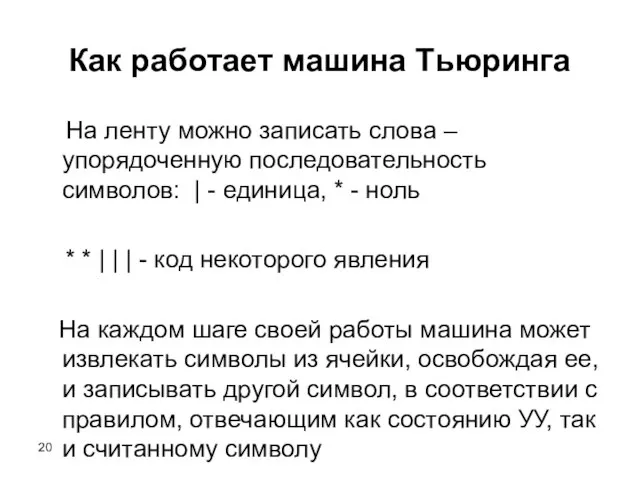

- 20. Как работает машина Тьюринга На ленту можно записать слова – упорядоченную последовательность символов: | - единица,

- 21. Управляющая таблица В современных процессорах “управляющая таблица” хранится в ПЗУ, в которое информация заносится изготовителями процессора,

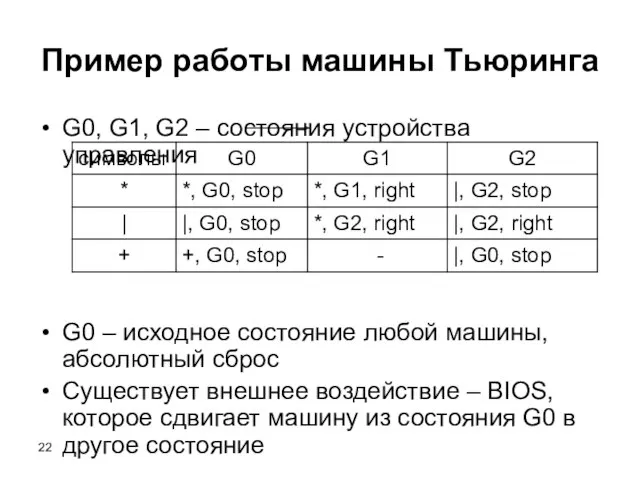

- 22. G0, G1, G2 – состояния устройства управления G0 – исходное состояние любой машины, абсолютный сброс Существует

- 23. Пример вида ленты G1 G1 G1 G1 G2 G2 G0 stop

- 24. Результат работы Машина заменяет одни символы на другие в соответствии с некоторой таблицей, но не вычисляет

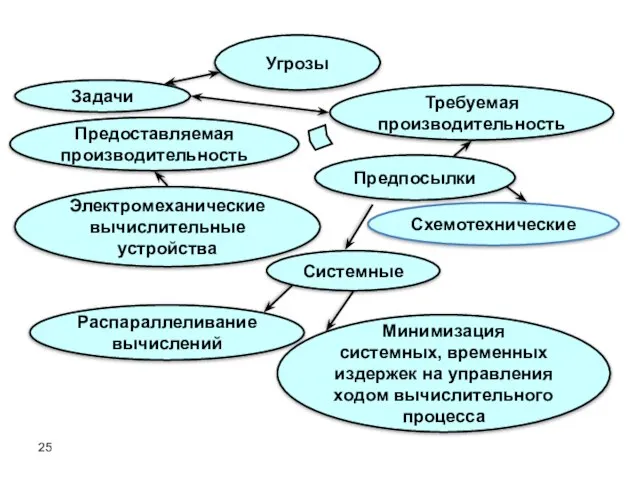

- 25. Угрозы Задачи Требуемая производительность Предоставляемая производительность Электромеханические вычислительные устройства Предпосылки Схемотехнические Системные Распараллеливание вычислений Минимизация системных,

- 26. Общие выводы Схемотехнические факторы повышения производительности предполагают развитие технологий производства элементной базы Глобальные национальные задачи, связанные

- 27. Учебный курс Принципы построения и функционирования ЭВМ Лекция 3 Механизмы реализации алгоритмов на низшем уровне профессор

- 28. Список литературы «Организация ЭВМ и систем», Цилькер Б.Я., Орлов С.А., 2004 – сегодня. «Электронно-вычислительные машины и

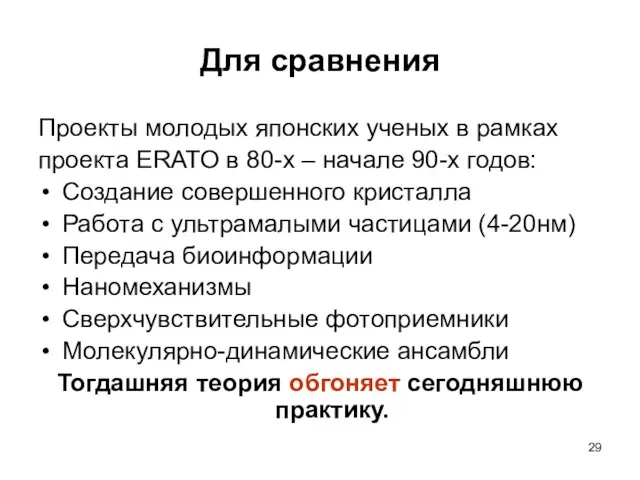

- 29. Для сравнения Проекты молодых японских ученых в рамках проекта ERATO в 80-х – начале 90-х годов:

- 30. Схема погружения задания пользователя Низший уровень реализации

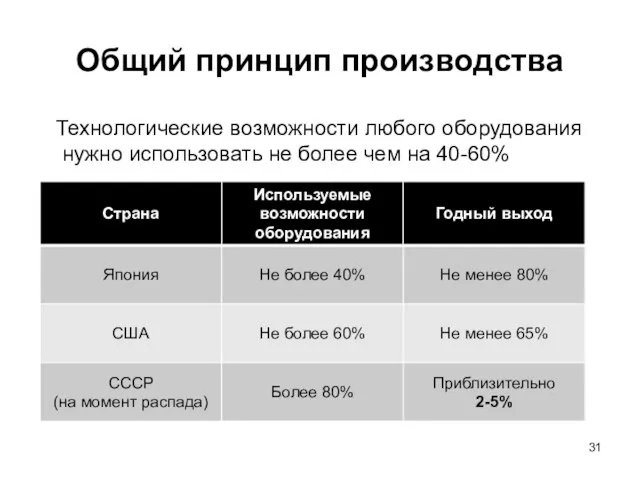

- 31. Общий принцип производства Технологические возможности любого оборудования нужно использовать не более чем на 40-60%

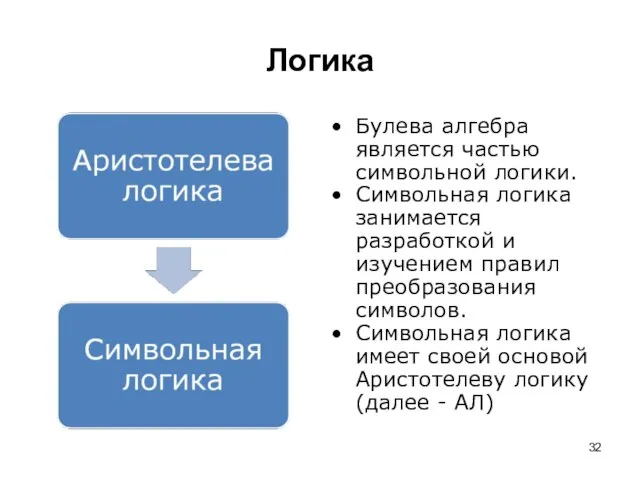

- 32. Логика Булева алгебра является частью символьной логики. Символьная логика занимается разработкой и изучением правил преобразования символов.

- 33. Правила (аксиомы) АЛ

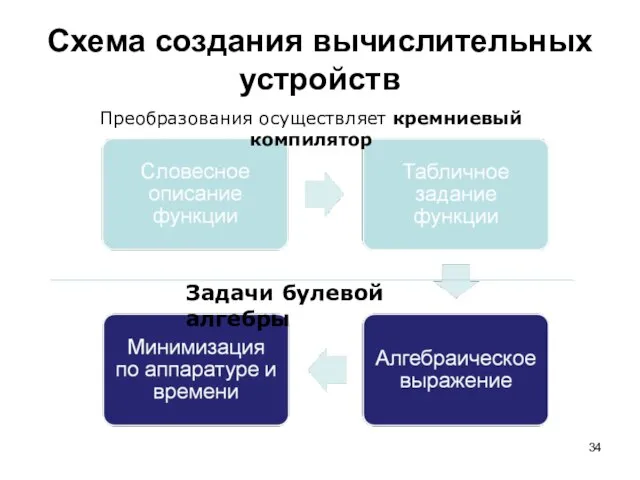

- 34. Схема создания вычислительных устройств Задачи булевой алгебры Преобразования осуществляет кремниевый компилятор

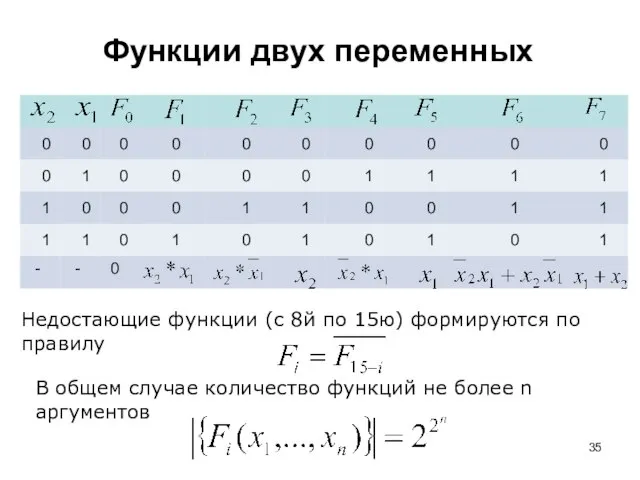

- 35. Функции двух переменных Недостающие функции (с 8й по 15ю) формируются по правилу В общем случае количество

- 36. Требования к устройству Необходима реализация всех возможных функций Технические ограничения Используется базисный набор Используемые базисы «И-НЕ»

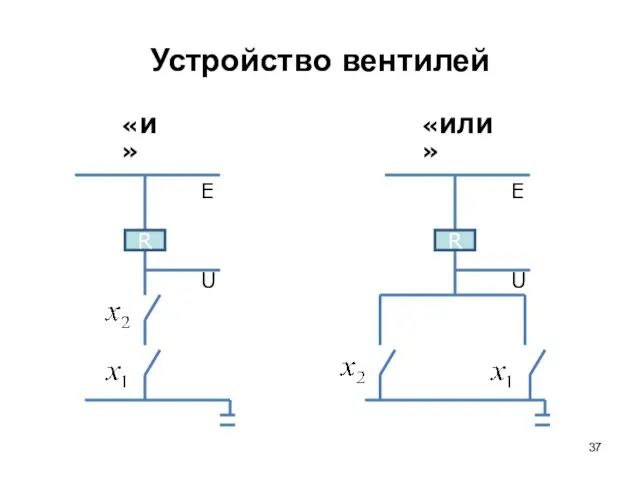

- 37. Устройство вентилей E U R E U R «И» «ИЛИ»

- 38. Полупроводниковый вентиль P N затвор Область P-N перехода И С Т О К С Т О

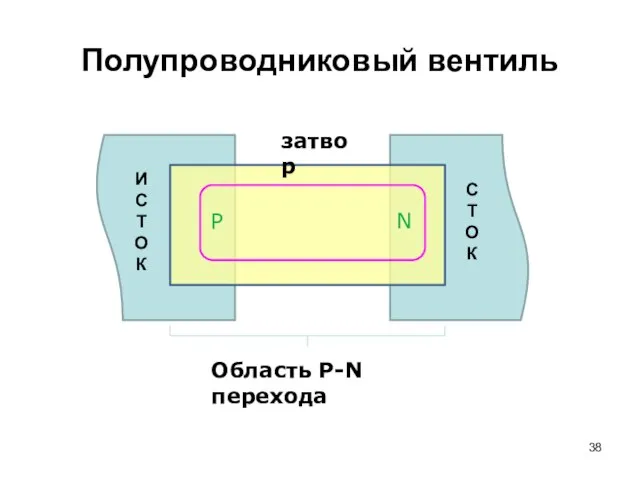

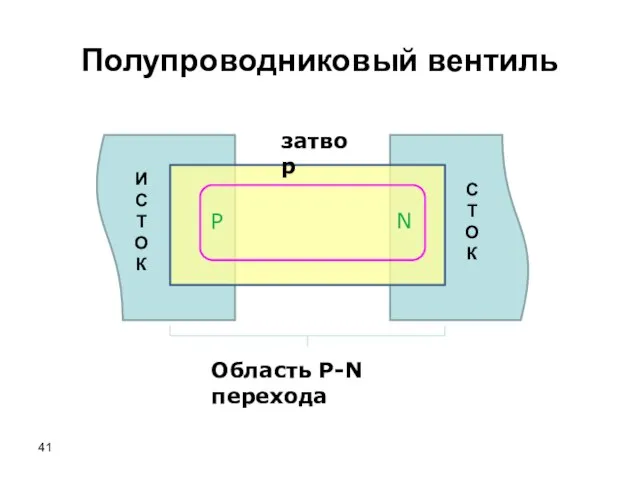

- 39. Размер имеет значение Ширина контактов = уровень технологии = = топологическая норма Уменьшение линейных размеров Квадратичный

- 40. Учебный курс Принципы построения и функционирования ЭВМ Лекция 4 Схемы вентилей профессор ГУ-ВШЭ, доктор технических наук

- 41. Полупроводниковый вентиль P N затвор Область P-N перехода И С Т О К С Т О

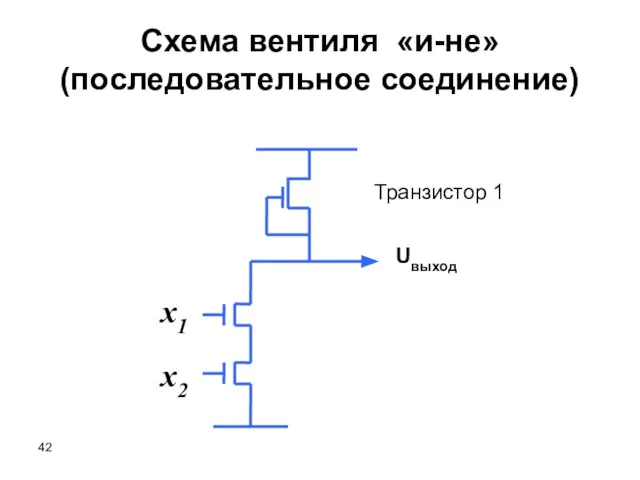

- 42. Транзистор 1 Uвыход x1 x2 Схема вентиля «и-не» (последовательное соединение)

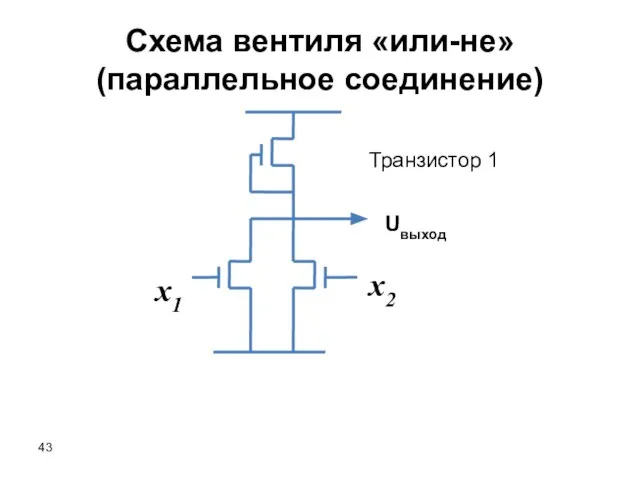

- 43. x2 x1 Схема вентиля «или-не» (параллельное соединение) Транзистор 1 Uвыход

- 44. & 0 0 0 1 0 0 0 0 И ИЛИ НЕ Логические схемы вентилей

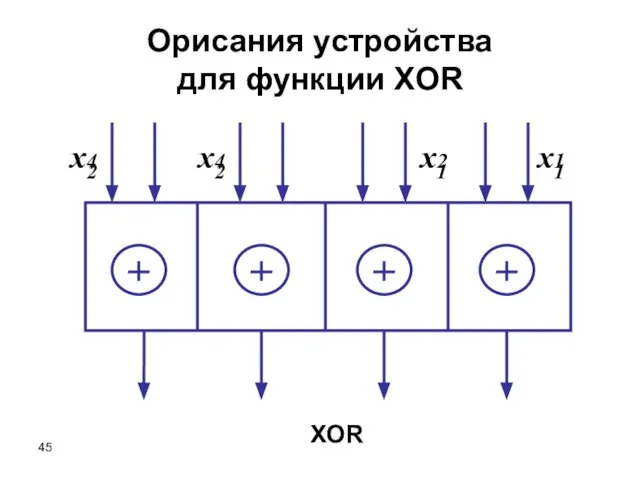

- 45. XOR Орисания устройства для функции XOR x2 4 x1 2 x1 1

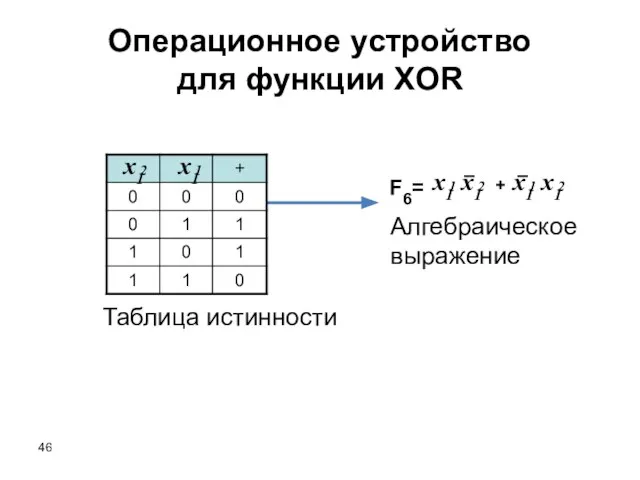

- 46. Таблица истинности Алгебраическое выражение Операционное устройство для функции XOR F6= +

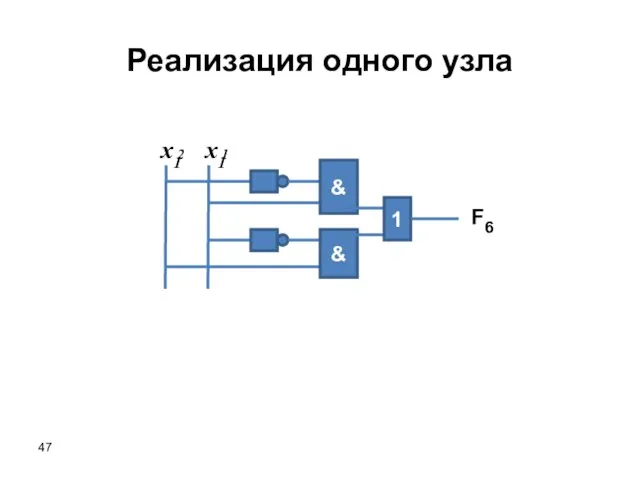

- 47. & & 1 Реализация одного узла F6

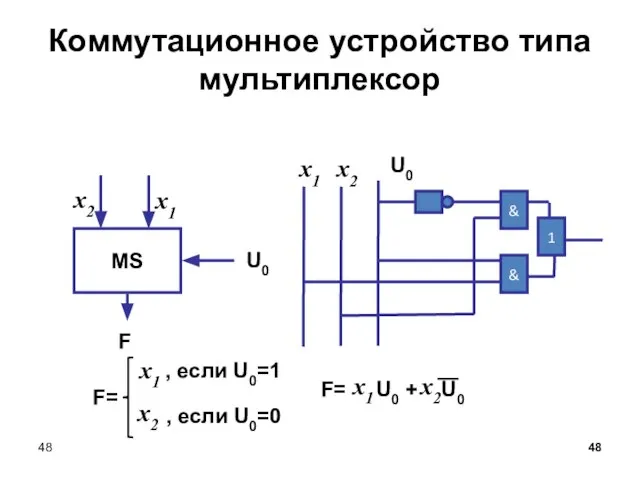

- 48. MS x1 x2 U0 x1 x2 U0 & & 1 Коммутационное устройство типа мультиплексор F F=

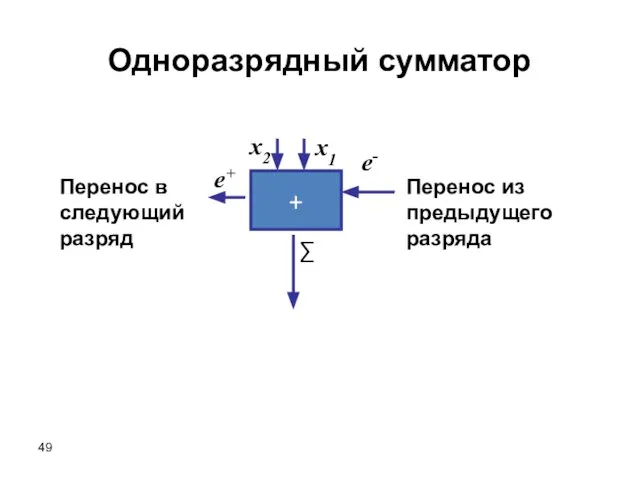

- 49. + ∑ Перенос из предыдущего разряда Перенос в следующий разряд Одноразрядный сумматор x2 x1 e- e+

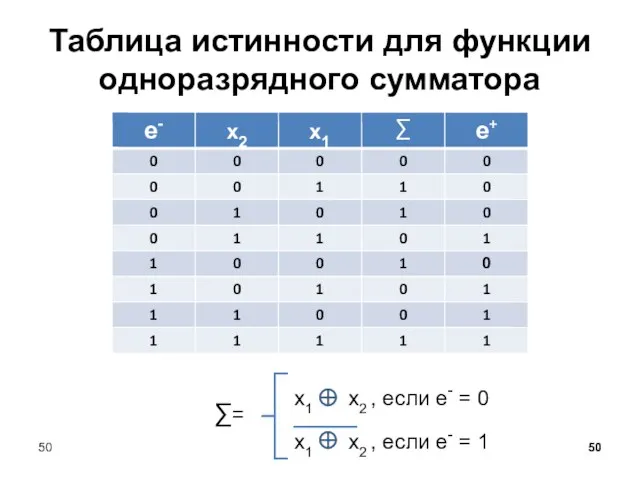

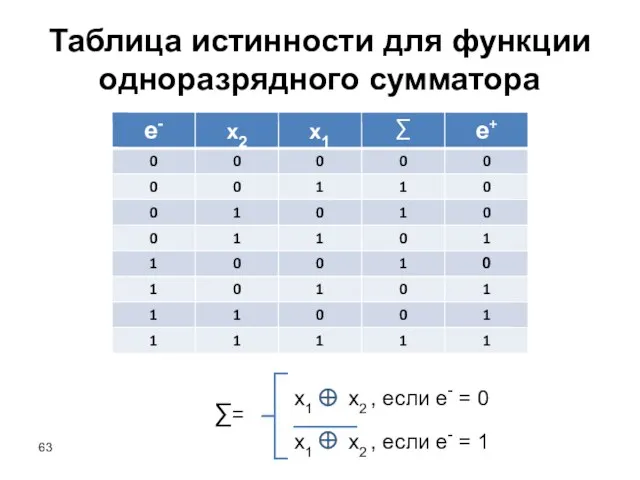

- 50. ∑= x1 x2 , если е- = 0 x1 x2 , если е- = 1 Таблица

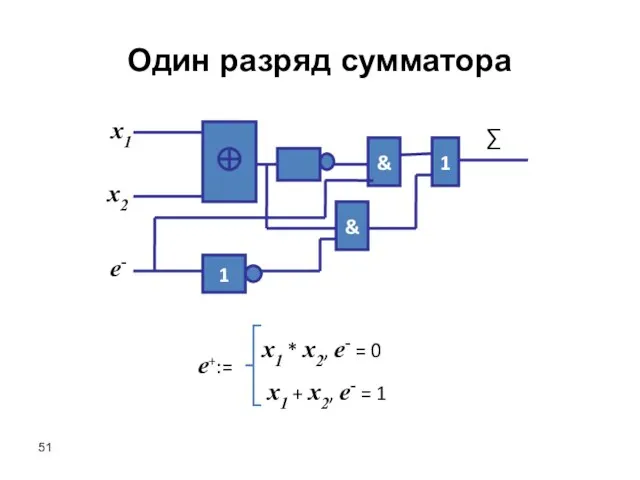

- 51. x1 x2 e- & 1 ∑ & 1 e+:= x1 * x2, e- = 0 x1

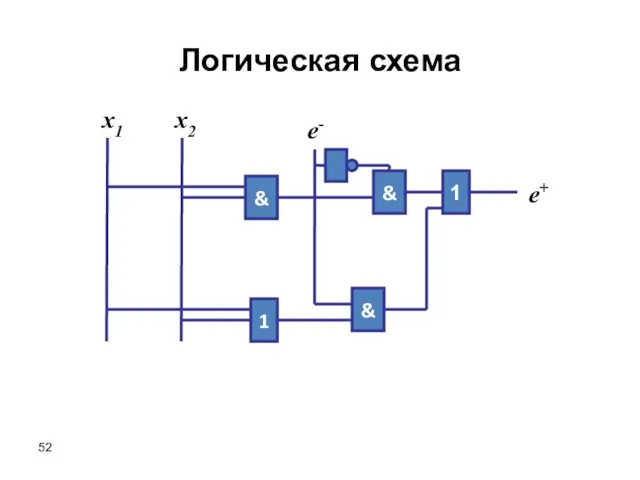

- 52. & 1 & & 1 Логическая схема x1 x2 e- e+

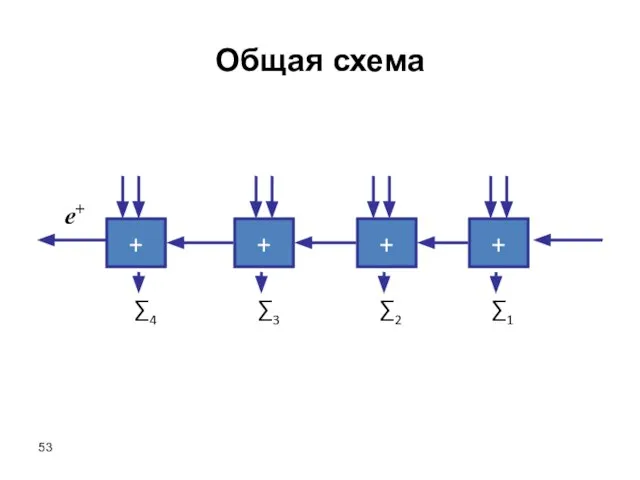

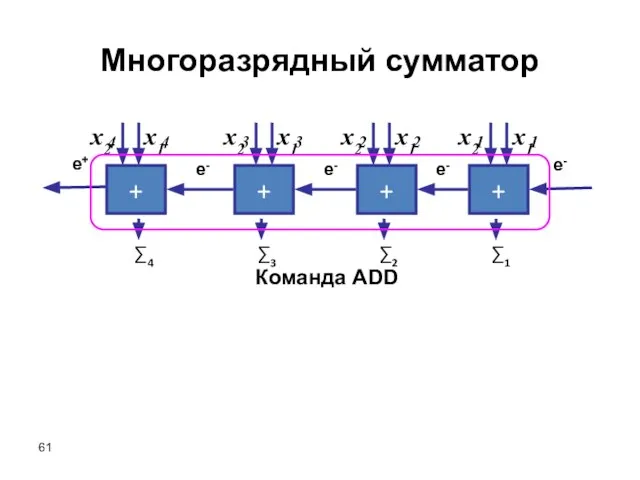

- 53. + + + + ∑1 ∑2 ∑3 ∑4 Общая схема e+

- 54. Учебный курс Принципы построения и функционирования ЭВМ Лекция 5 Синтез цифровых устройств профессор ГУ-ВШЭ, доктор технических

- 55. Роль и место булевой алгебры Последовательность действий синтеза вычислительных устройств: Словесное описание функции Таблица истинности Алгебраическое

- 56. Последовательность действий в аппаратной среде Физико-технический процесс Транзистор Вентиль Узел Блок Устройство

- 57. Минимизация алгебраического выражения Минимизация алгебраического выражения проводится по двум критериям: Минимум аппаратных затрат (вентилей) Минимум времени

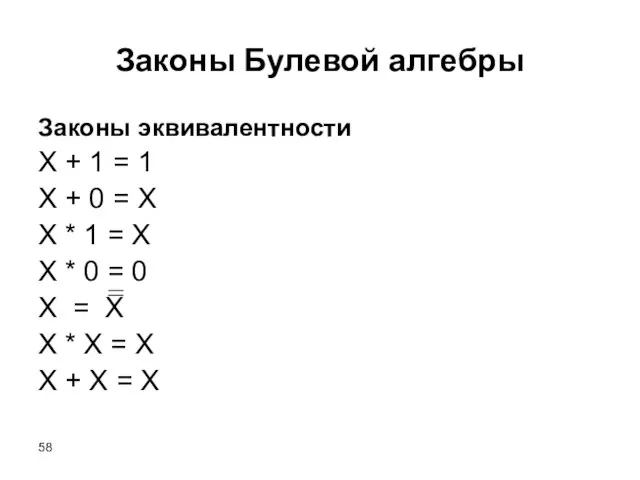

- 58. Законы Булевой алгебры Законы эквивалентности X + 1 = 1 X + 0 = X X

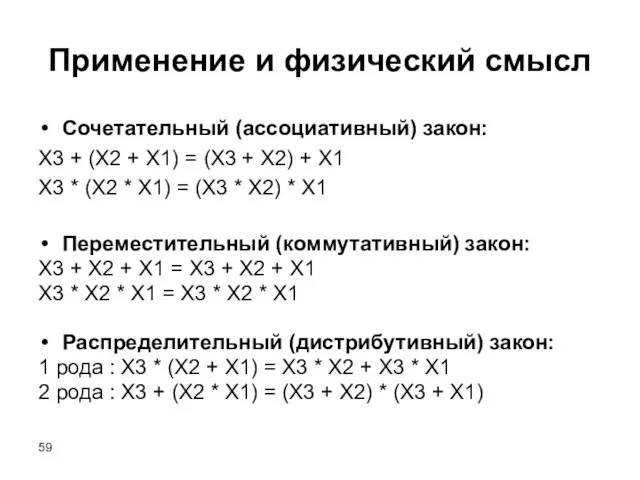

- 59. Применение и физический смысл Сочетательный (ассоциативный) закон: X3 + (X2 + X1) = (X3 + X2)

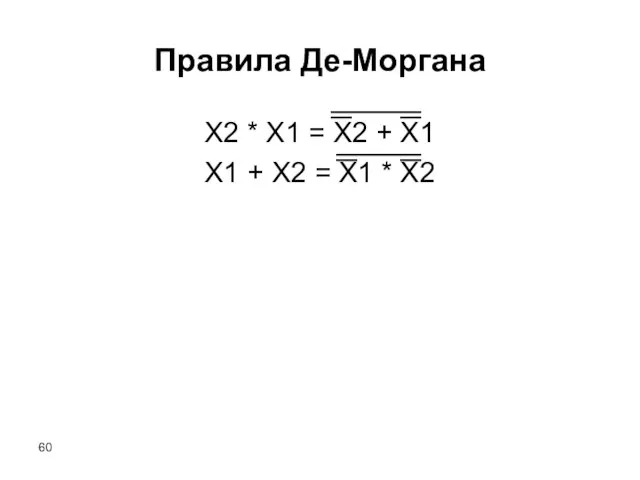

- 60. Правила Де-Моргана X2 * X1 = X2 + X1 X1 + X2 = X1 * X2

- 61. Многоразрядный сумматор + + + + ∑1 ∑2 ∑3 ∑4 e- e- e- e- e+ Команда

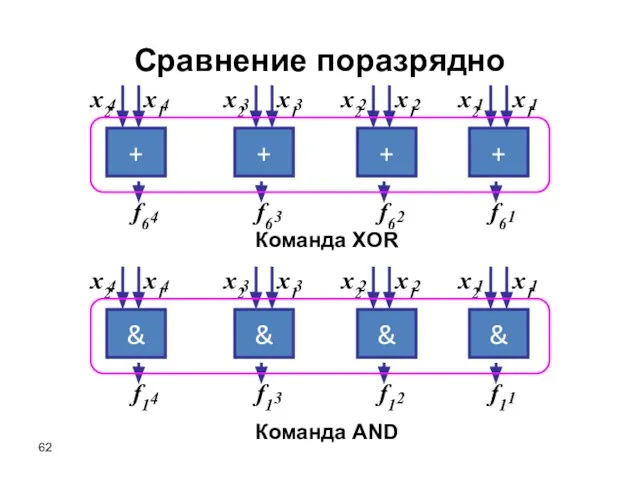

- 62. Сравнение поразрядно + + + + Команда XOR & & & & Команда AND

- 63. ∑= x1 x2 , если е- = 0 x1 x2 , если е- = 1 Таблица

- 64. Функциональная схема полного одноразрядного сумматора

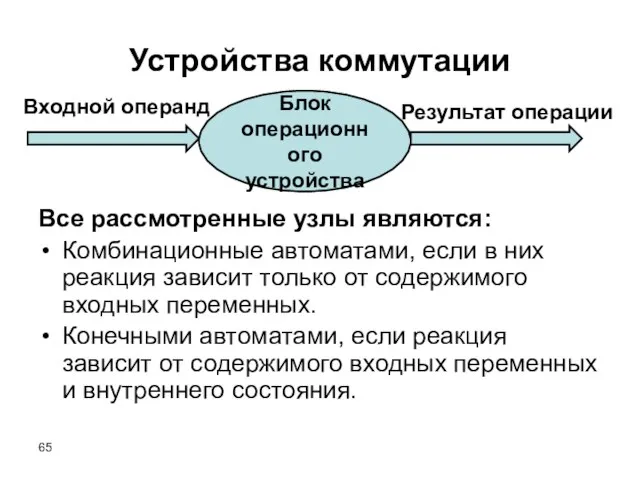

- 65. Устройства коммутации Все рассмотренные узлы являются: Комбинационные автоматами, если в них реакция зависит только от содержимого

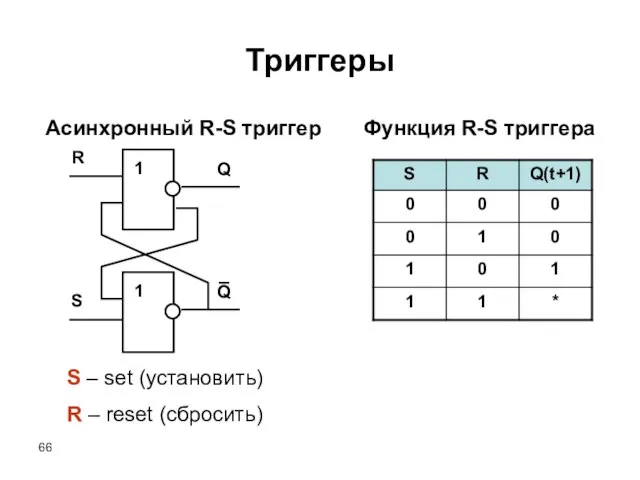

- 66. Триггеры Асинхронный R-S триггер S – set (установить) R – reset (сбросить) Функция R-S триггера

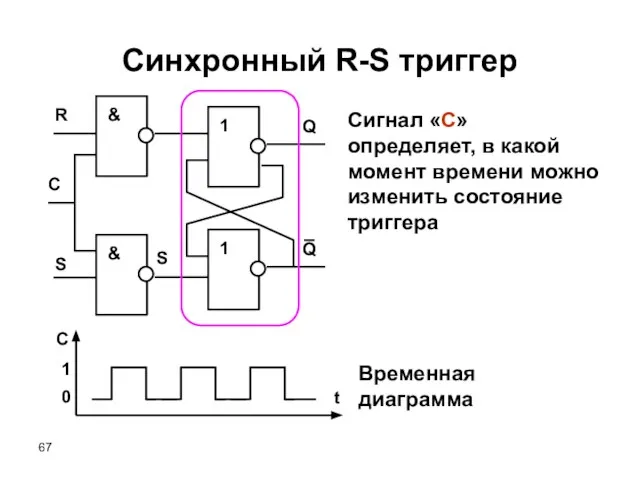

- 67. Синхронный R-S триггер Сигнал «С» определяет, в какой момент времени можно изменить состояние триггера Временная диаграмма

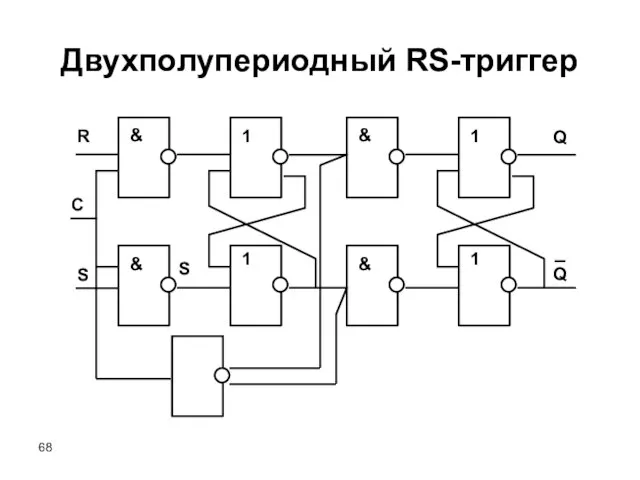

- 68. Двухполупериодный RS-триггер 1 1 R S & & S C 1 Q 1 Q & &

- 69. Учебный курс Принципы построения и функционирования ЭВМ Лекция 6 Триггеры и регистры профессор ГУ-ВШЭ, доктор технических

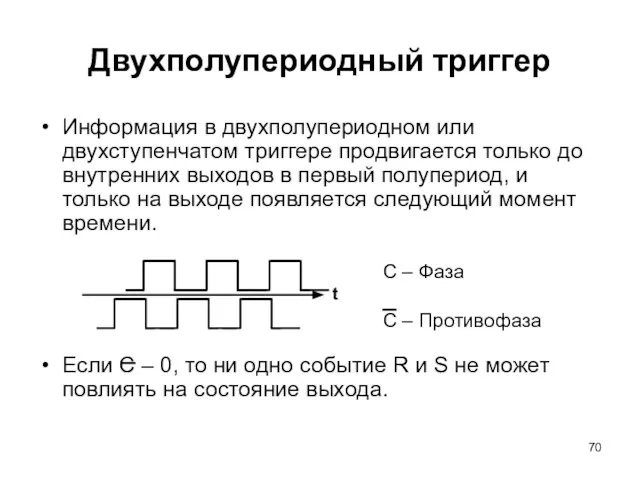

- 70. Информация в двухполупериодном или двухступенчатом триггере продвигается только до внутренних выходов в первый полупериод, и только

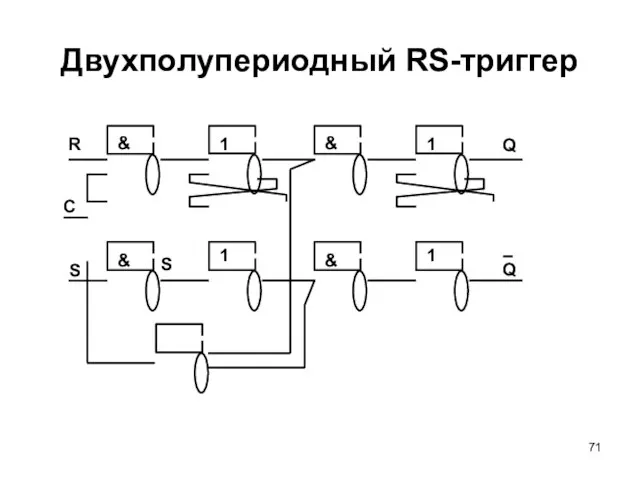

- 71. Двухполупериодный RS-триггер 1 1 R S & & S C 1 Q 1 Q & &

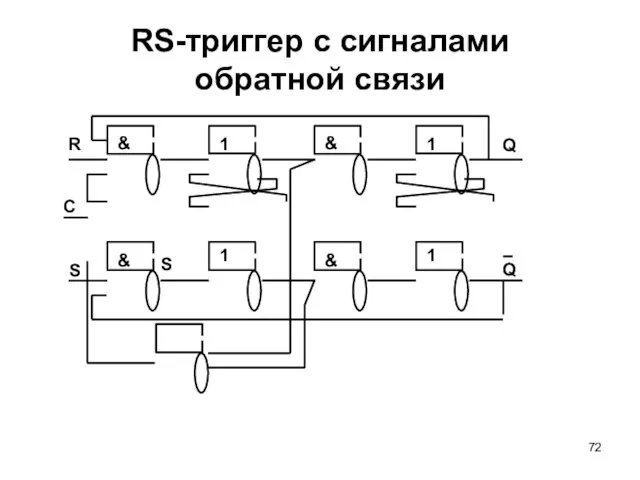

- 72. RS-триггер с сигналами обратной связи 1 1 R S & & S C 1 Q 1

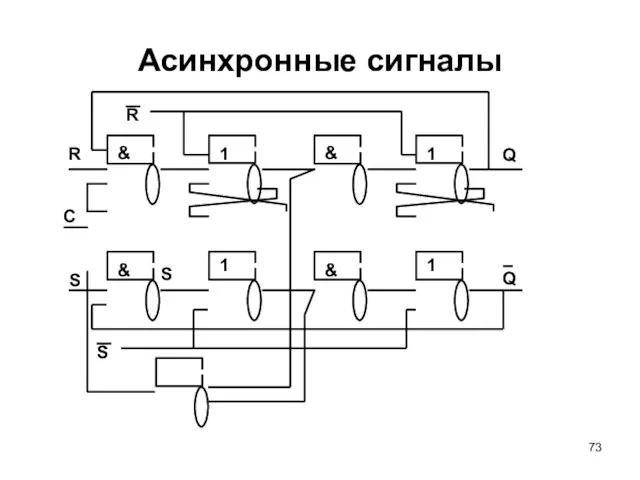

- 73. Асинхронные сигналы 1 1 R S & & S C 1 Q 1 Q & &

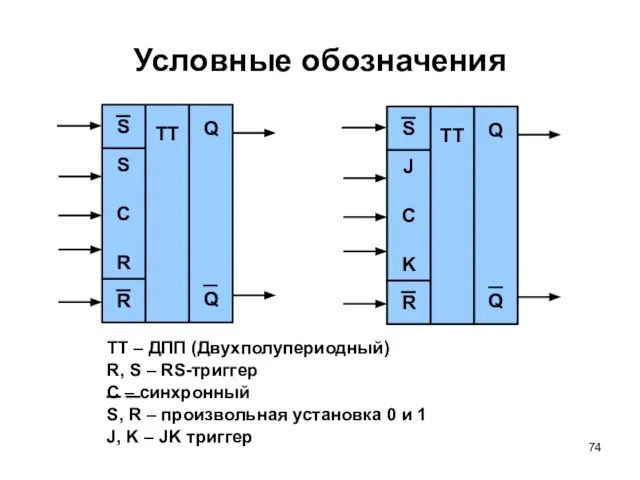

- 74. TT – ДПП (Двухполупериодный) R, S – RS-триггер C – синхронный S, R – произвольная установка

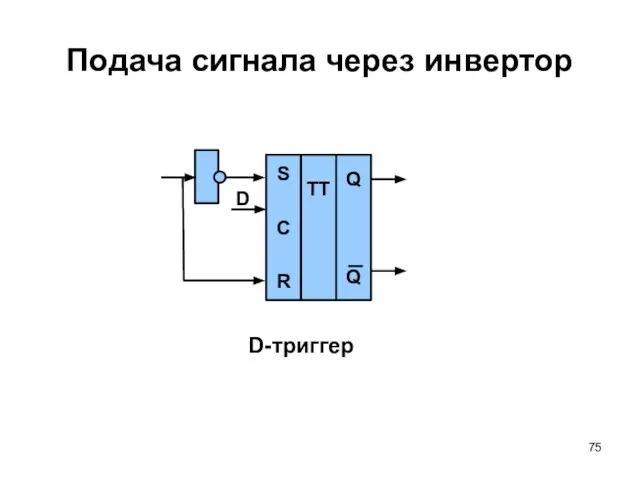

- 75. S C R TT Q Q D Подача сигнала через инвертор D-триггер

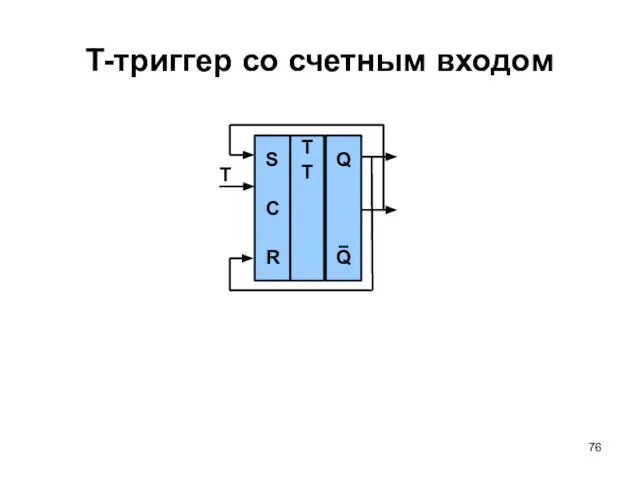

- 76. T-триггер со счетным входом S C R TT Q Q T

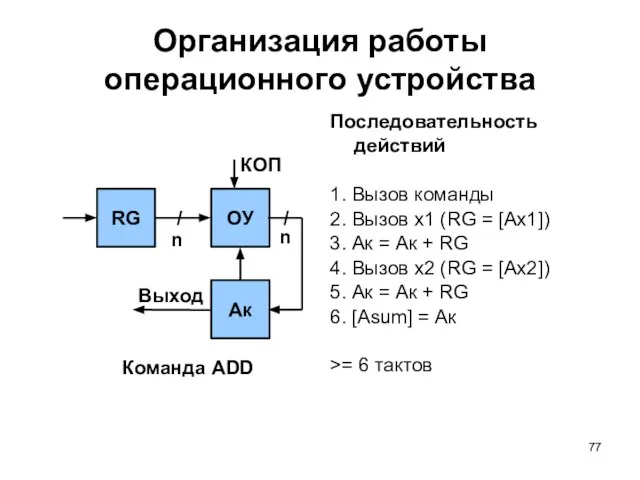

- 77. ОУ RG Ак Выход КОП / Организация работы операционного устройства Последовательность действий 1. Вызов команды 2.

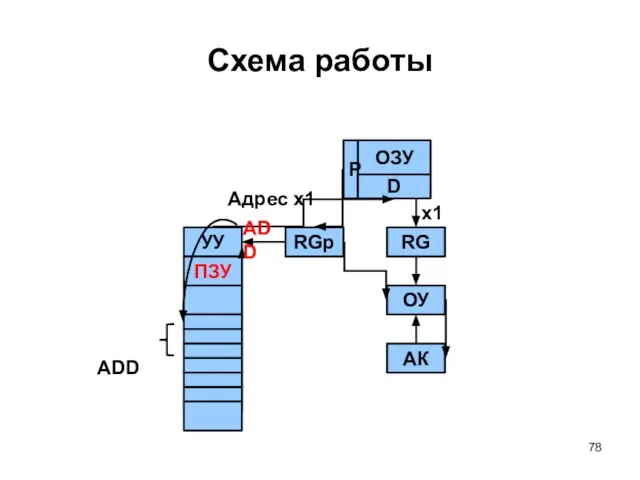

- 78. ОЗУ P D RGp УУ Адрес x1 RG x1 ОУ АК ПЗУ ADD ADD Схема работы

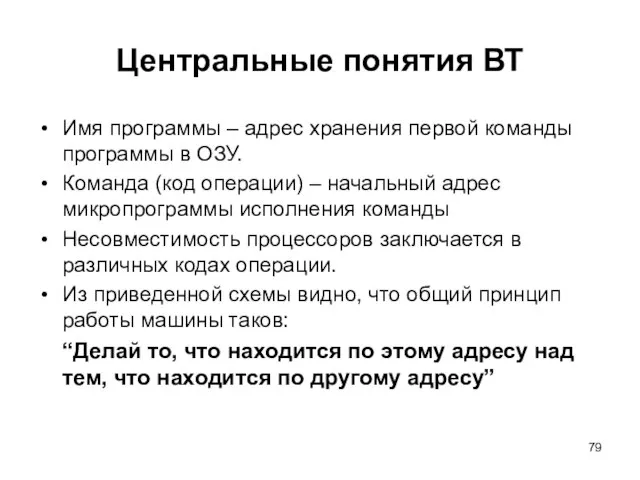

- 79. Центральные понятия ВТ Имя программы – адрес хранения первой команды программы в ОЗУ. Команда (код операции)

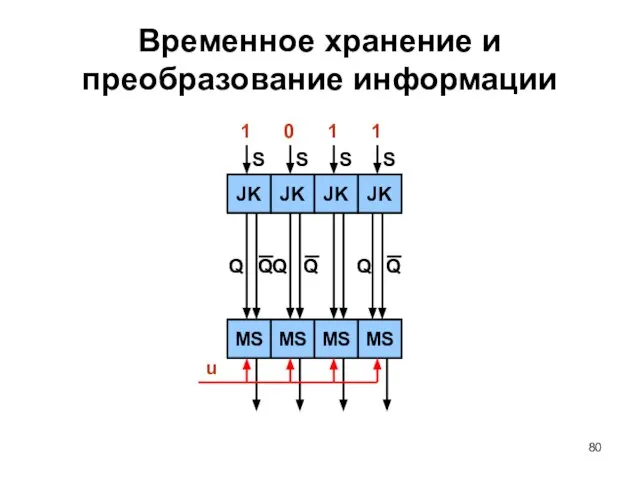

- 80. S Временное хранение и преобразование информации JK JK JK JK S S S MS MS MS

- 81. Коммутация Коммутация на примере 32-разрядного процессора Для сумматора требуются Aк, КОП, A1, A2, A3, D1, D2,

- 82. Учебный курс Принципы построения и функционирования ЭВМ Лекция 7 Элементы и узлы вычислительной техники профессор ГУ-ВШЭ,

- 83. Общая схема работы машины Основное правило: делай то, что находится по этому адресу над тем, что

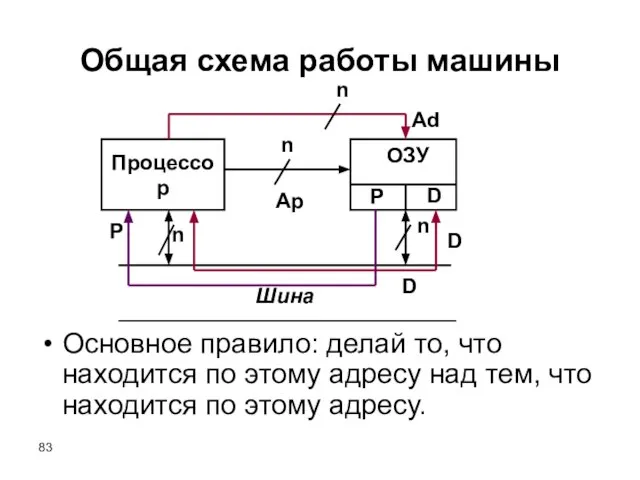

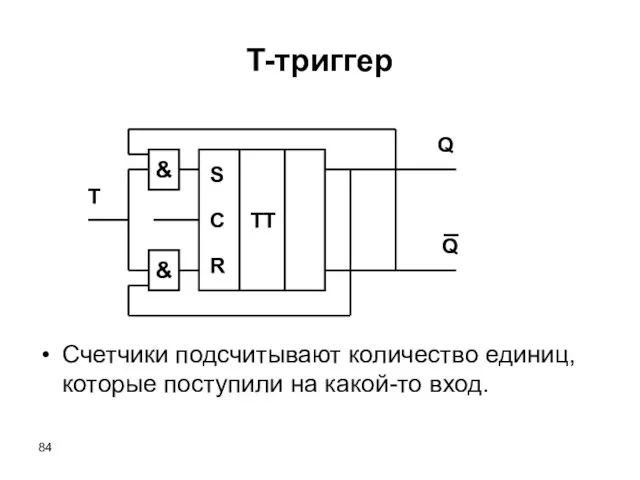

- 84. T-триггер Счетчики подсчитывают количество единиц, которые поступили на какой-то вход. & & Q Q S R

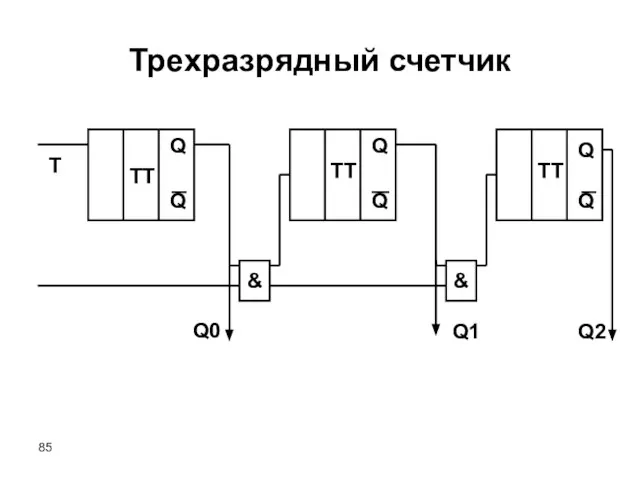

- 85. Трехразрядный счетчик & & TT TT TT Q Q Q Q Q Q T Q0 Q2

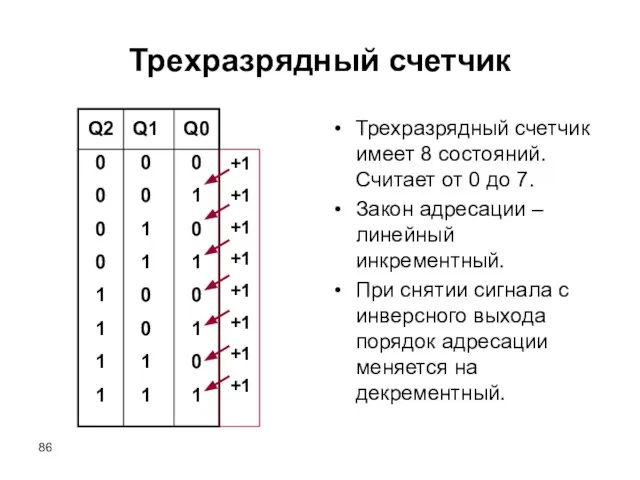

- 86. Трехразрядный счетчик Трехразрядный счетчик имеет 8 состояний. Считает от 0 до 7. Закон адресации – линейный

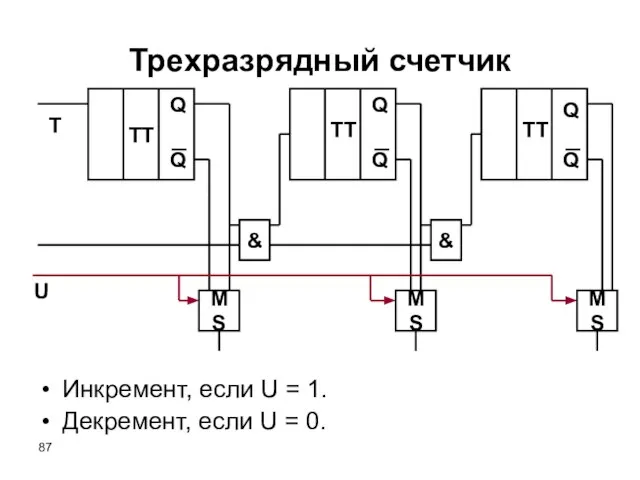

- 87. Трехразрядный счетчик Инкремент, если U = 1. Декремент, если U = 0. & & TT TT

- 88. Логическая адресация Рассмотренный линейный закон адресации предусматривает перемещение по памяти с шагом 1. Для увеличения шага

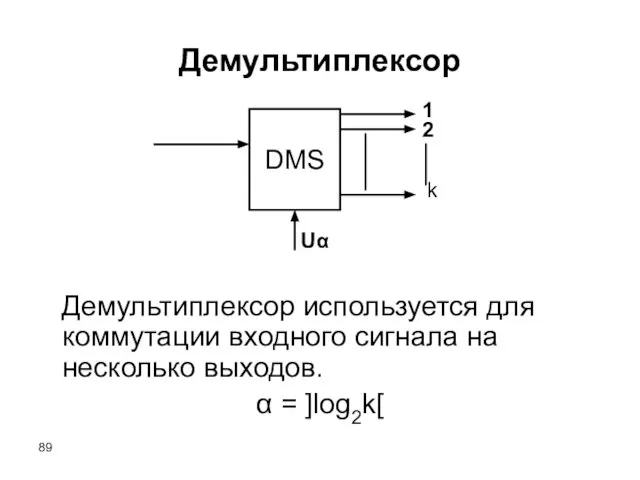

- 89. Демультиплексор Демультиплексор используется для коммутации входного сигнала на несколько выходов. α = ]log2k[ DMS 1 2

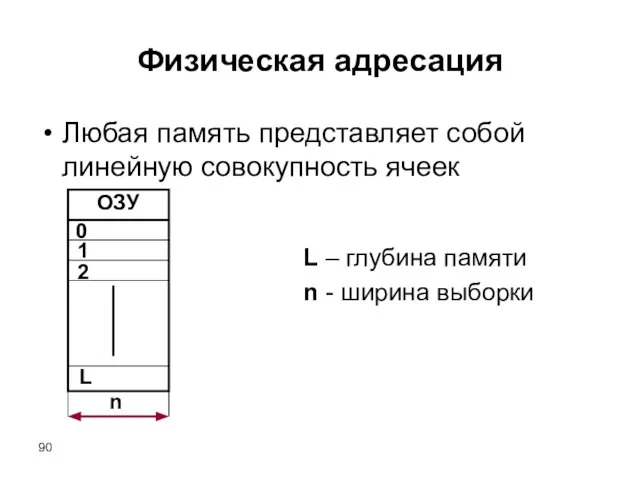

- 90. Физическая адресация Любая память представляет собой линейную совокупность ячеек L – глубина памяти n - ширина

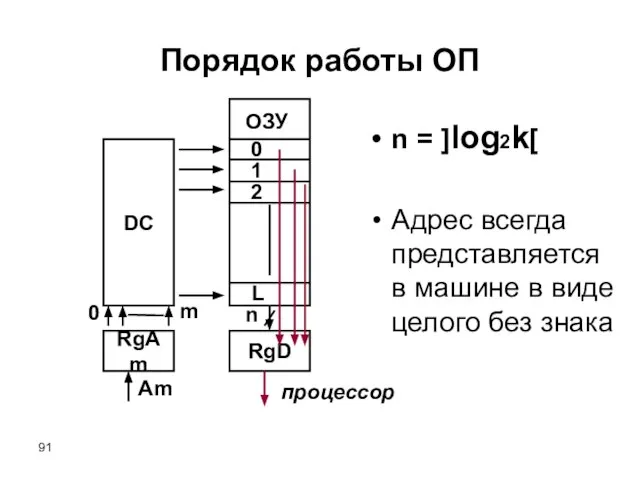

- 91. Порядок работы ОП DC RgD RgAm ОЗУ Am 0 1 2 L n n = ]log2k[

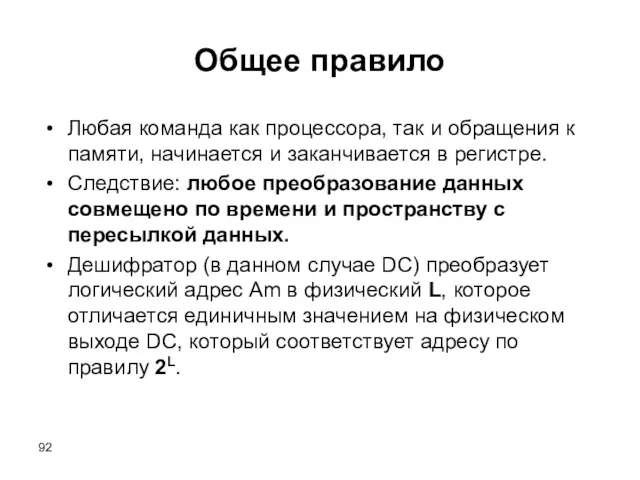

- 92. Общее правило Любая команда как процессора, так и обращения к памяти, начинается и заканчивается в регистре.

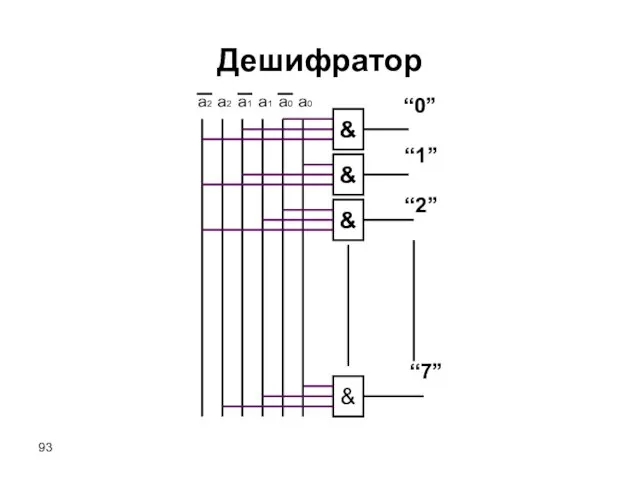

- 93. Дешифратор а0 а2 а2 а0 а1 а1 & “0” & “1” & “2” & “7”

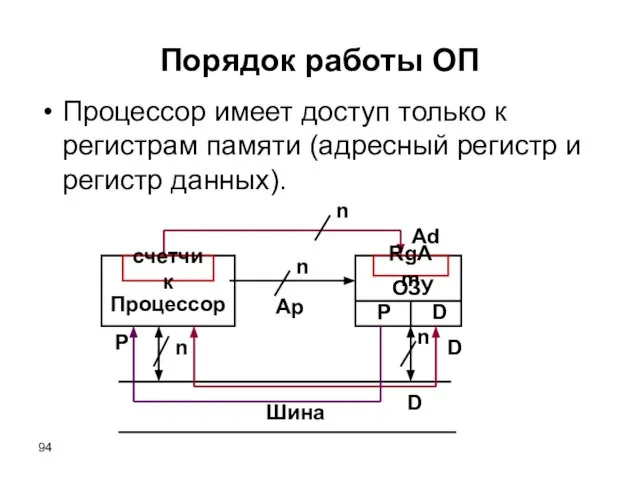

- 94. Порядок работы ОП Процессор имеет доступ только к регистрам памяти (адресный регистр и регистр данных). Процессор

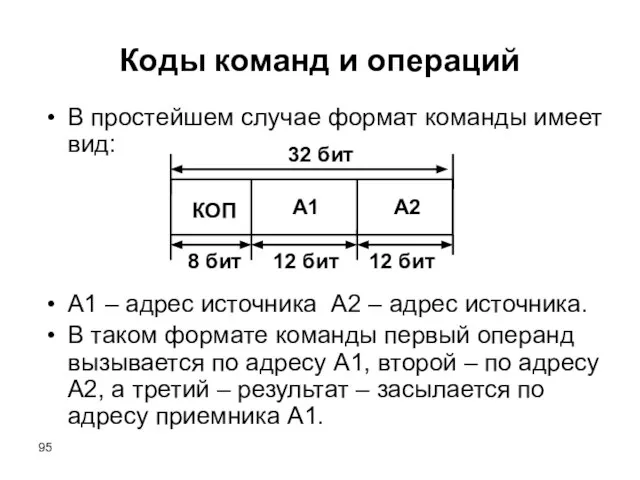

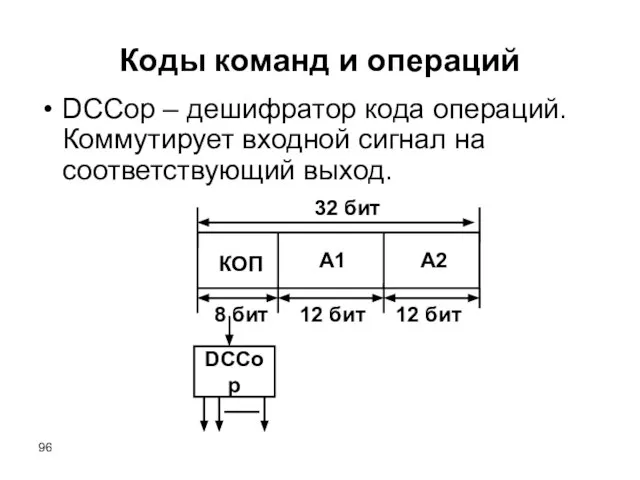

- 95. Коды команд и операций В простейшем случае формат команды имеет вид: A1 – адрес источника А2

- 96. Коды команд и операций DCСop – дешифратор кода операций. Коммутирует входной сигнал на соответствующий выход. DCCop

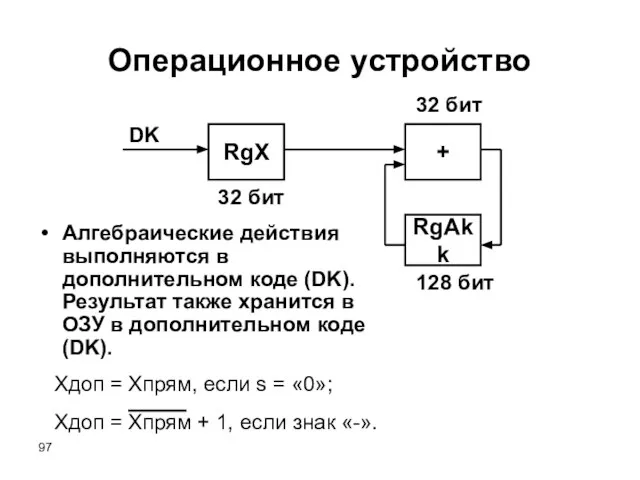

- 97. Операционное устройство Алгебраические действия выполняются в дополнительном коде (DK). Результат также хранится в ОЗУ в дополнительном

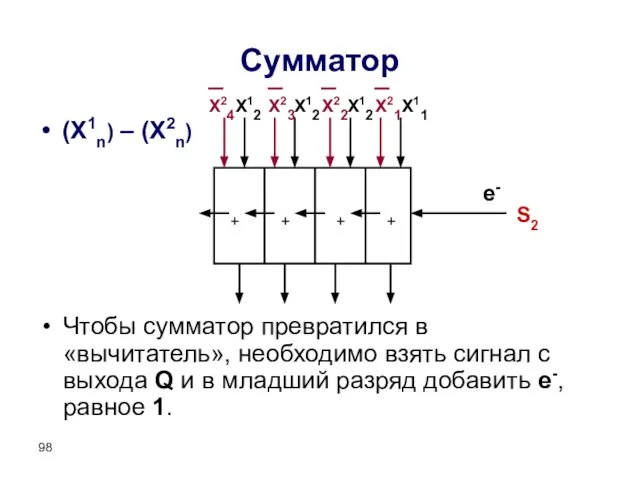

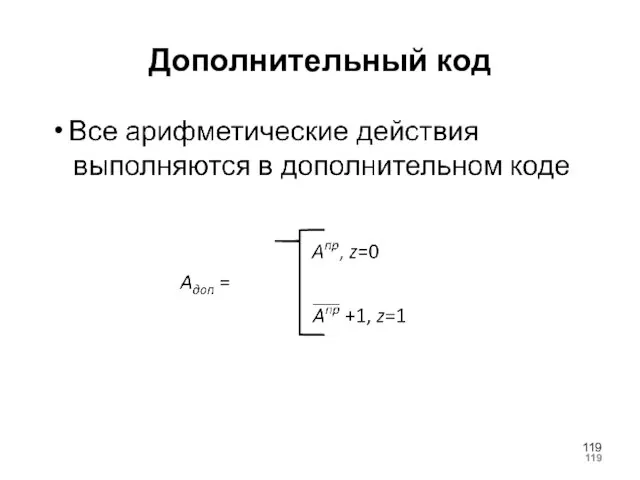

- 98. Сумматор (X1n) – (X2n) Чтобы сумматор превратился в «вычитатель», необходимо взять сигнал с выхода Q и

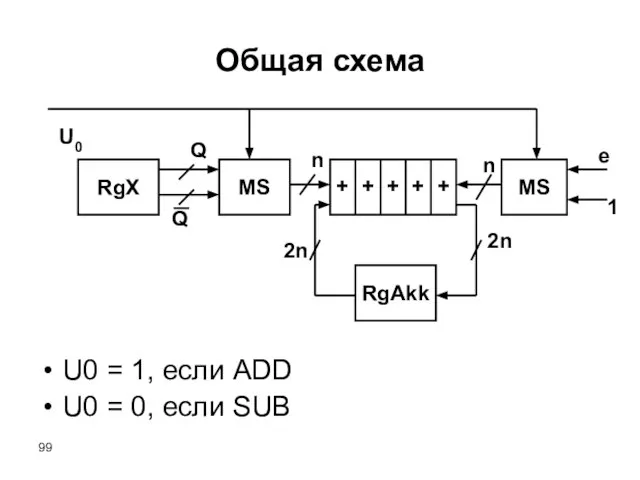

- 99. Общая схема U0 = 1, если ADD U0 = 0, если SUB RgX MS MS +

- 100. Итог С помощью переключательной функции и вентилей можно покрыть все функции, которые выполняет машина.

- 101. Учебный курс Принципы построения и функционирования ЭВМ Лекция 8 Организация памяти в ЭВМ профессор ГУ-ВШЭ, доктор

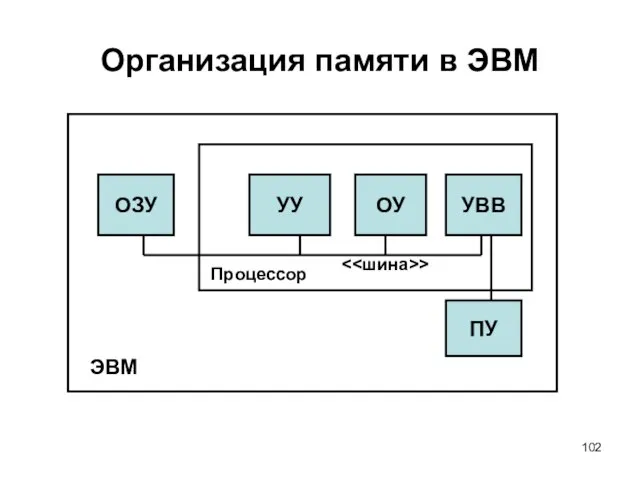

- 102. Организация памяти в ЭВМ УУ ОУ УВВ ПУ ОЗУ ЭВМ Процессор >

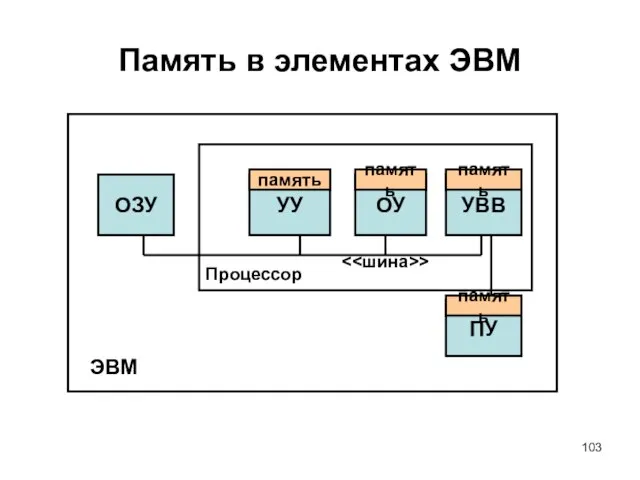

- 103. Память в элементах ЭВМ УУ ОУ УВВ ПУ ОЗУ ЭВМ Процессор > память память память память

- 104. Классификация памяти по признакам внешняя (оптическая память, магнитная память) и внутренняя оперативная и буферная (кэш) регистровая

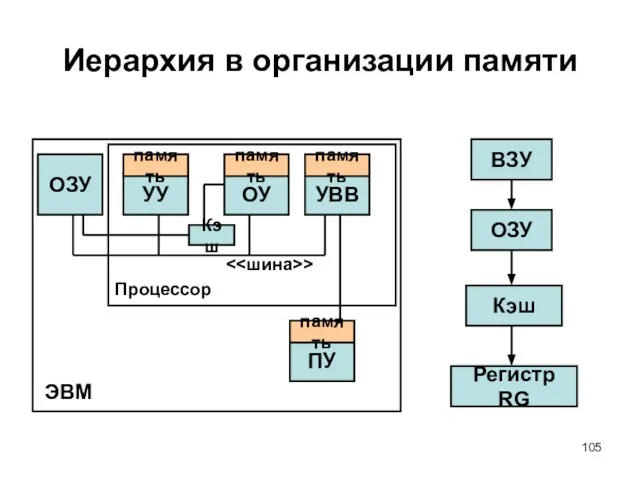

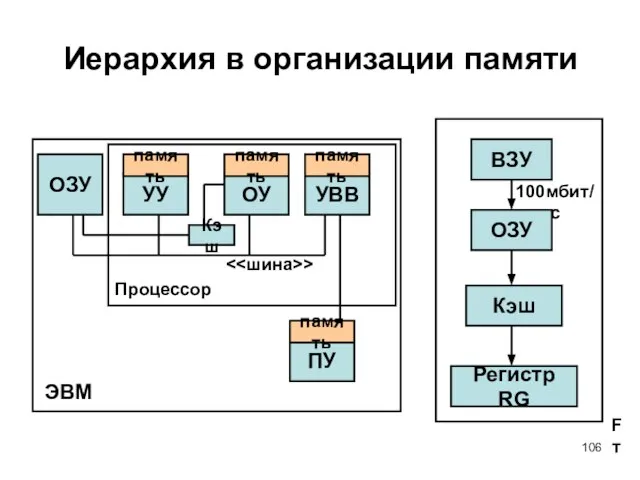

- 105. Иерархия в организации памяти ПУ ЭВМ Процессор > память ВЗУ ОЗУ Кэш Регистр RG Кэш ОУ

- 106. Иерархия в организации памяти Fт ПУ ЭВМ Процессор > память ВЗУ ОЗУ Кэш Регистр RG Кэш

- 107. Физико-технические процессы электронные переключательные процессы магнитные, электромагнитные (фиритные ячейки памяти) оптические

- 108. Организация доступа к элементам памяти параллельный (прямой) доступ время доступа = 2*T последовательный доступ время доступа

- 109. Классификация памяти по типу записи постоянные запоминающие устройства (ПЗУ, ROM) память чтения-записи (RAM)

- 110. Классификация памяти по продолжительности хранения статическая память динамическая память (DRAM) (хранение осуществляется на паразитных плоскостях pn-переходов)

- 111. Чем характеризуется любая память? глубиной и шириной «выборки» продолжительностью цикла обращения (быстродействием) надежностью

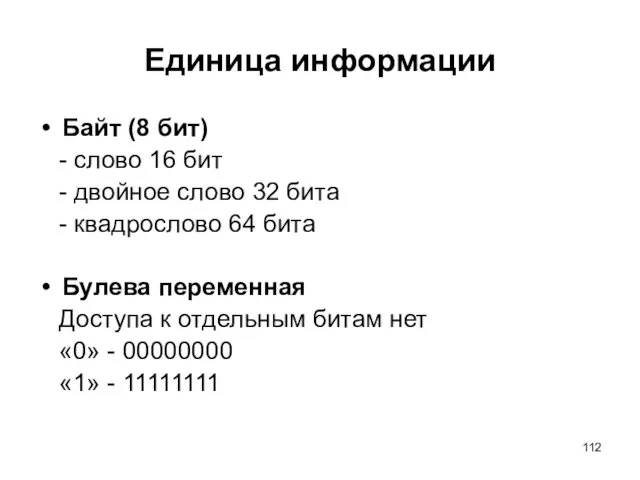

- 112. Единица информации Байт (8 бит) - слово 16 бит - двойное слово 32 бита - квадрослово

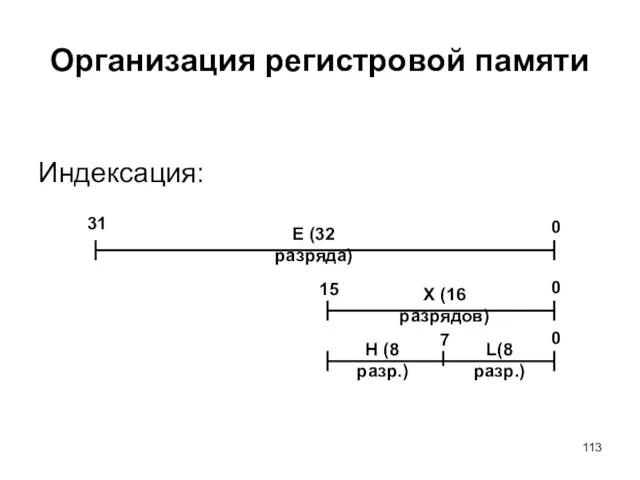

- 113. Организация регистровой памяти Индексация: 31 0 15 0 7 0 E (32 разряда) X (16 разрядов)

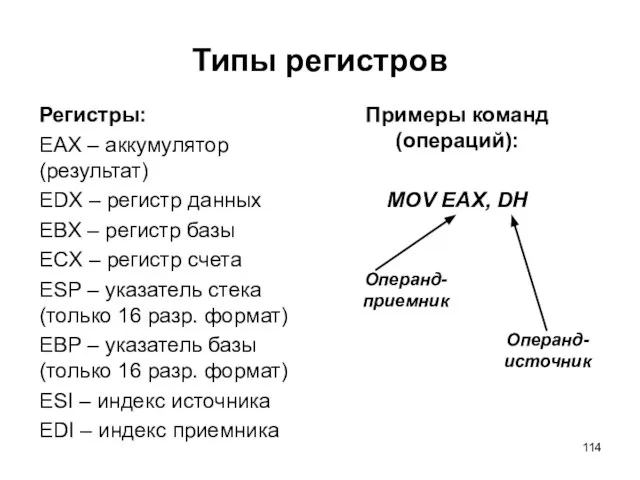

- 114. Типы регистров Операнд-источник Операнд-приемник

- 115. Учебный курс Принципы построения и функционирования ЭВМ Лекция 9 Методы адресации. Способы представления информации в ЭВМ.

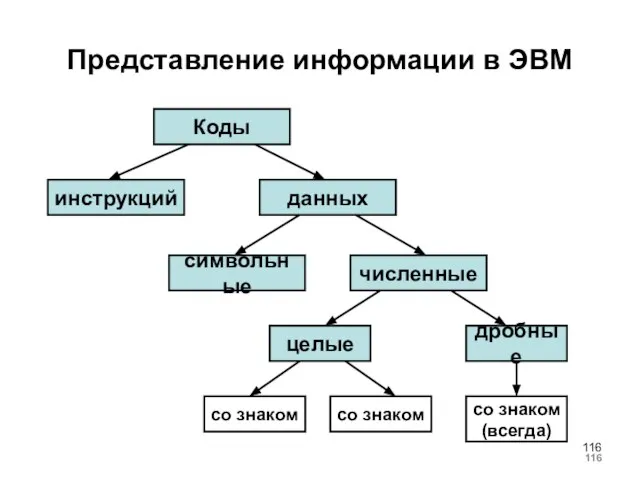

- 116. Представление информации в ЭВМ Коды инструкций данных символьные численные дробные целые со знаком со знаком со

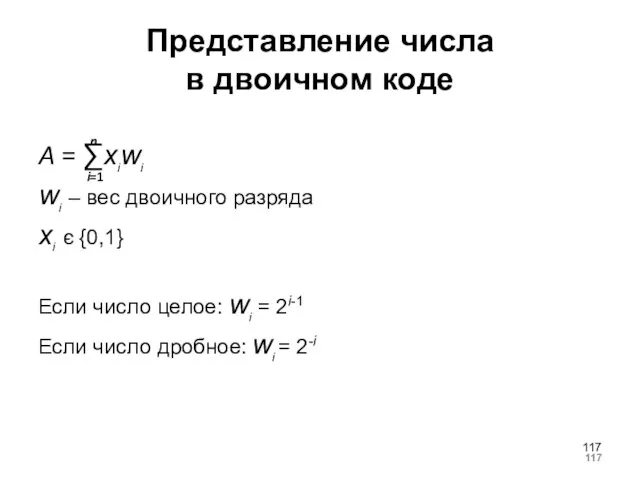

- 117. Представление числа в двоичном коде A = ∑xiwi wi – вес двоичного разряда xi є {0,1}

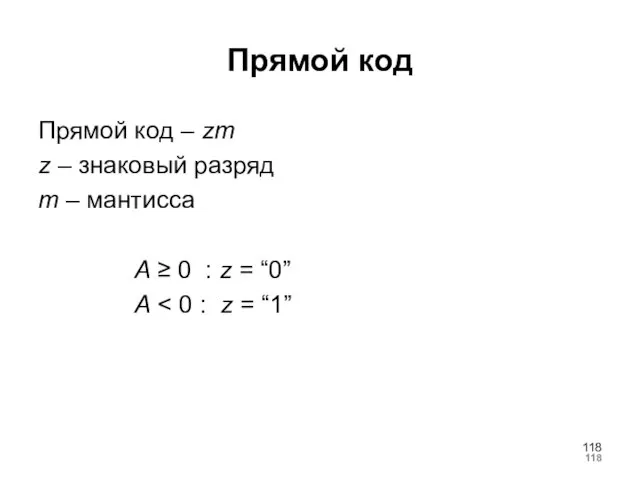

- 118. Прямой код Прямой код – zm z – знаковый разряд m – мантисса A ≥ 0

- 119. Дополнительный код

- 120. Цена перехода от десятичного кода к двоичному При переводе целого числа мы делим до получения результата

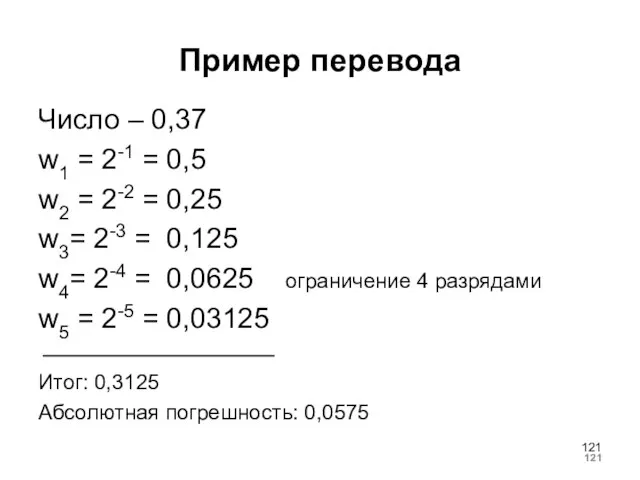

- 121. Пример перевода Число – 0,37 w1 = 2-1 = 0,5 w2 = 2-2 = 0,25 w3=

- 122. Представление данных в памяти 1000 1011 - хранится 8B - представляется

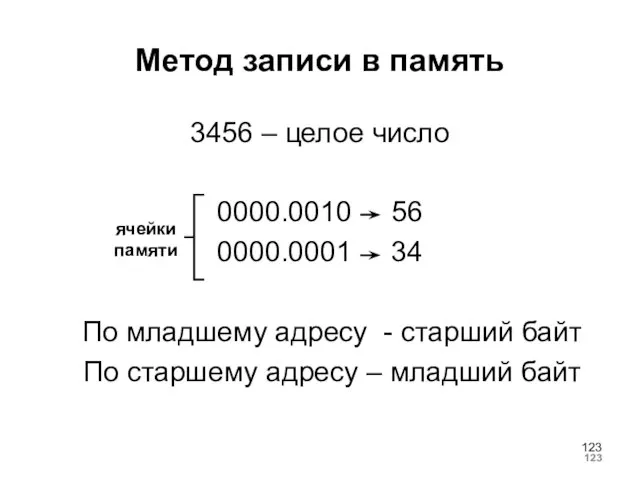

- 123. Метод записи в память 3456 – целое число 0000.0010 56 0000.0001 34 По младшему адресу -

- 124. Адресация данных в ЭВМ Основные способы адресации: линейная сегментная страничная смешанная

- 125. Сегментация Сегментация позволяет: минимизировать паразитные пересылки из ОЗУ во внешнюю память улучшить защиту памяти в многозадачном

- 126. Основные сегменты Выделяют пять основных сегментов: сегмент программ стек три сегмента пользователя данных

- 127. Техника адресации Существует девять типов адресаций: непосредственная регистровая прямая адресация к памяти косвенная регистровая относительная прямая

- 128. Учебный курс Принципы построения и функционирования ЭВМ Лекция 10 Типы адресации. Стеки. Процессоры. ОЗУ. профессор ГУ-ВШЭ,

- 129. 1.Организация работы с памятью пропускная способность ЭВМ определяется скоростью обмена с памятью скорость обмена с внешними

- 130. 1.1 Логическая и физическая организация памяти на логическом уровне организация памяти структурируется сегментами на физическом –

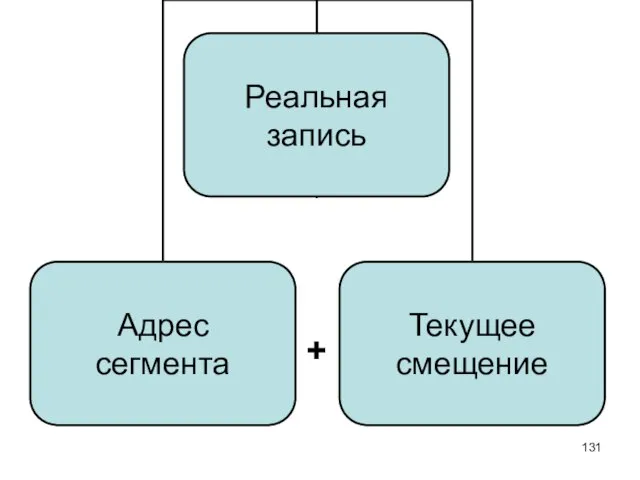

- 131. +

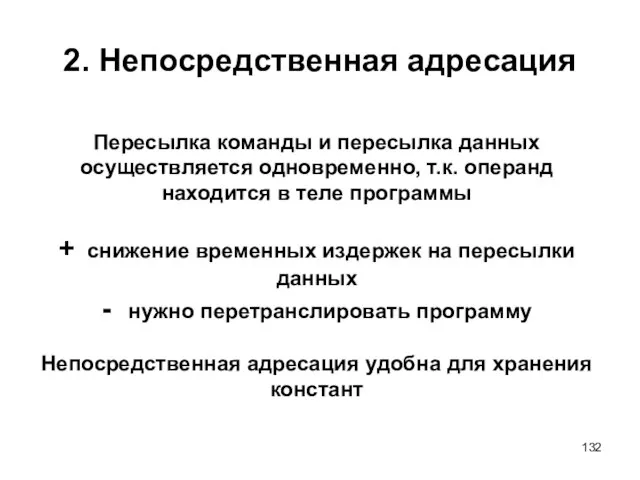

- 132. 2. Непосредственная адресация Пересылка команды и пересылка данных осуществляется одновременно, т.к. операнд находится в теле программы

- 133. 3. Регистровая адресация При регистровой адресации значение операнда-источника предварительно запоминается в одном из внутренних регистров процессора

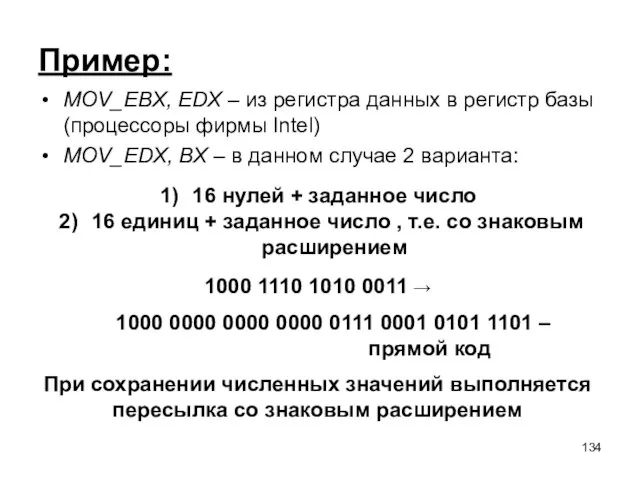

- 134. Пример: MOV_EBX, EDX – из регистра данных в регистр базы (процессоры фирмы Intel) MOV_EDX, BX –

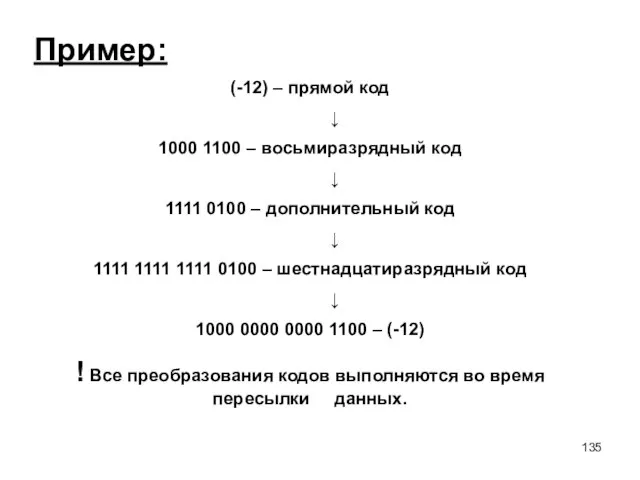

- 135. (-12) – прямой код ↓ 1000 1100 – восьмиразрядный код ↓ 1111 0100 – дополнительный код

- 136. 4. Прямая адресация Операндом является переменное имя или метка. Пример: MOV_AX, mydata – по имени mydata

- 137. 5. Косвенная регистровая адресация В этом случае вместо метки используется значение операнда по адресу смещения, который

- 138. Данный способ адресации наиболее удобно использовать, когда данные хранятся в форме таблицы Доступ к отдельным значениям

- 139. 6. Относительная адресация Действующий адрес получается суммированием смещения с содержимым регистра базы Пример: MOV_EDX, [EBX+4] Данный

- 140. 7. Прямая индексная адресация смещение операнда определяется суммой смещения и значения одного из индексных регистров E(SI),

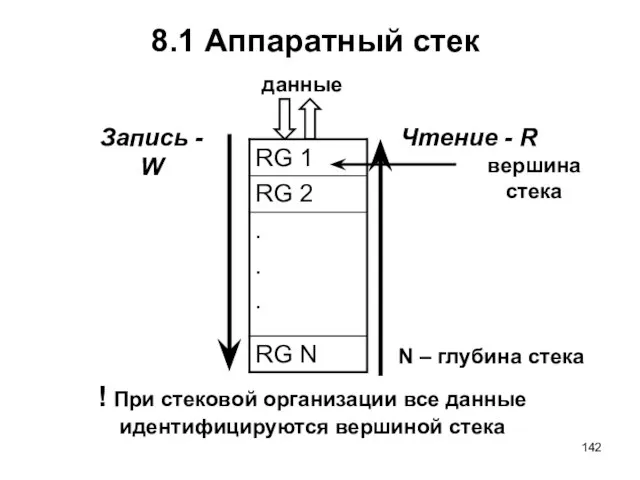

- 141. 8. Стеки Механизм стеков снижает издержки на адресацию Стек программный аппаратный совокупность регистров сдвига

- 142. 8.1 Аппаратный стек Запись - W данные вершина стека N – глубина стека Чтение - R

- 143. Учебный курс Принципы построения и функционирования ЭВМ Лекция 11 Микрокоманды и микрооперации профессор ГУ-ВШЭ, доктор технических

- 144. Процессоры Процессор: дешифрует выполняет команды программы организует обращение к АЗУ инициирует работу периферийных устройств воспринимает и

- 145. Выполнение команд ЭВМ строго регламентировано во времени: на каждом этапе выполняется одна или несколько микроопераций Конкретный

- 146. Машинный такт процессора регламентирует интервал времени, в течение которого выполняется одна или несколько микроопераций Границы тактов

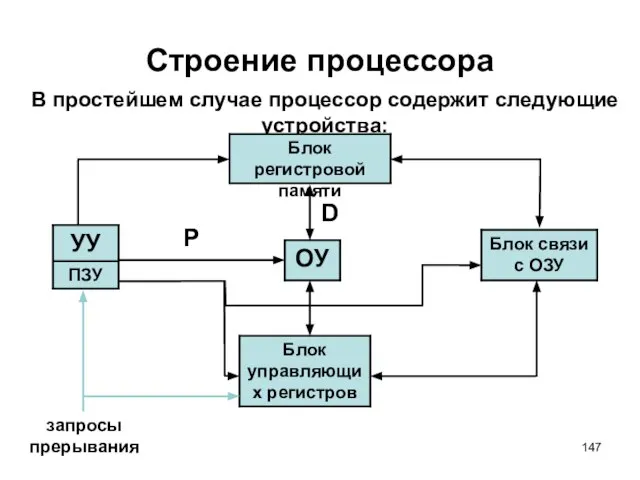

- 147. Строение процессора В простейшем случае процессор содержит следующие устройства: Блок регистровой памяти Блок связи с ОЗУ

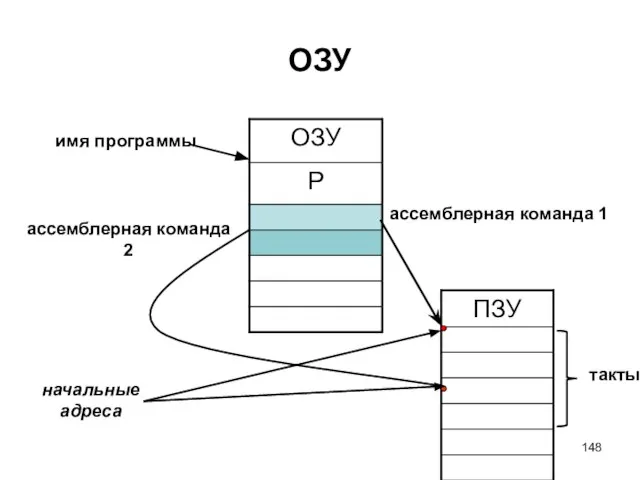

- 148. ОЗУ имя программы ассемблерная команда 1 ассемблерная команда 2 начальные адреса такты

- 149. Функции операционного устройства непосредственное преобразование информации над данными постоянной или переменной длины (в формате фиксированной и

- 150. Устройство управления формирует необходимые управляющие сигналы для выборки очередной команды из ОЗУ, дешифрации кода операции, формирование

- 151. Блок управляющих регистров предназначен для временного хранения управляющей информации содержит как регистры, так и счетчики

- 152. Интерфейс процессора Обеспечивает: обмен информацией защиту сегментов ОЗУ от недозволенных обращений связь процессора с периферийными устройствами

- 153. Блок контроля и диагностики Служит для: обнаружения сбоев и отказов в аппаратуре восстановления работы после сбоя

- 154. Сбои и отказы Сбой - это кратковременный отказ Для предотвращения ошибок вводятся специальные контрольные регистры, определяющие

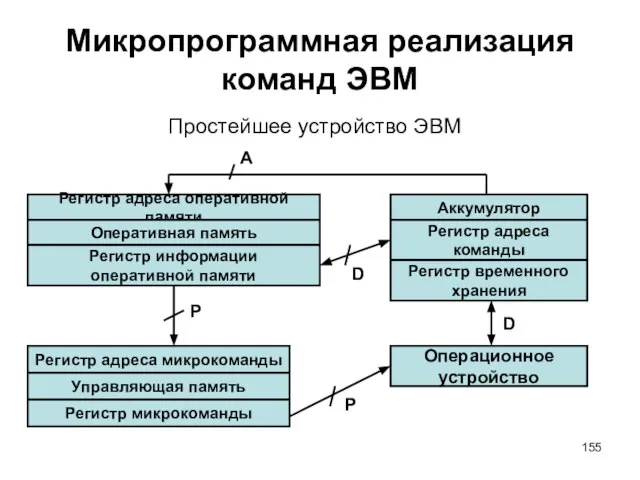

- 155. Микропрограммная реализация команд ЭВМ Простейшее устройство ЭВМ Операционное устройство D

- 156. Группа команд межрегистровой пересылки данных В группу входят команды типа ADD (Акк := Акк + (А)

- 157. Микрооперации управления выборкой регистра любому регистру можно присвоить значение аккумулятора, регистра адреса команды и регистра временного

- 158. Считывание и запись информации оперативной памяти В эту группу входит возможность обмена данными между регистром информации

- 159. Адресная арифметика В эту группу входит возможность обмена данными между аккумулятором и любым другим регистром, арифметическое

- 160. Регистр адреса микрокоманды В эту группу входит реализация счетчика и получение регистром адреса микрокоманды значения регистра

- 161. Учебный курс Принципы построения и функционирования ЭВМ Лекция 12 Архитектура ЭВМ. Прерывания. профессор ГУ-ВШЭ, доктор технических

- 162. Распараллеливание вычислений производится для повышения производительности вычислительной системы необходим аппаратный параллельный коммутационный ресурс

- 163. 1. Способы распараллеливания вычислений Векторизация. Преобразования осуществляются параллельно над несколькими потоками. Конвейеризация. Один и тот же

- 164. 2. Конвейер команд Ресурсы: Выборка – процессор, ОЗУ Дешифрация – устройство управления процессора (УУ) Исполнение –

- 165. 2.1. Организация циклов Циклы применяются для решения проблемы конечности памяти Использование цикла в конвейере существенно уменьшает

- 166. 3. Векторизация Несколько процессов должны выполняться одновременно и параллельно Команды становятся протяжённей, но выполняются за меньшее

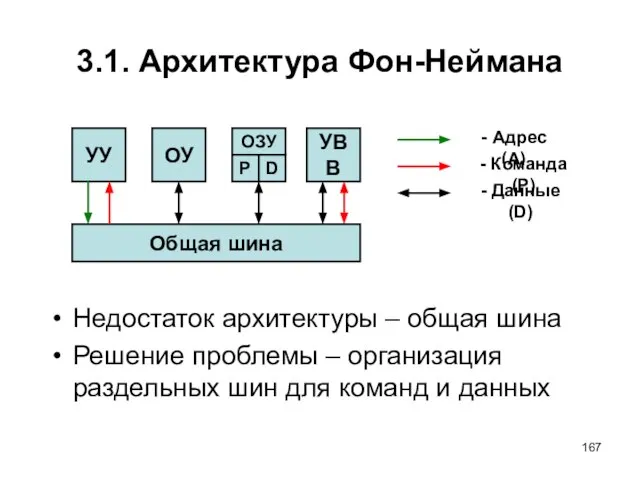

- 167. 3.1. Архитектура Фон-Неймана Недостаток архитектуры – общая шина Решение проблемы – организация раздельных шин для команд

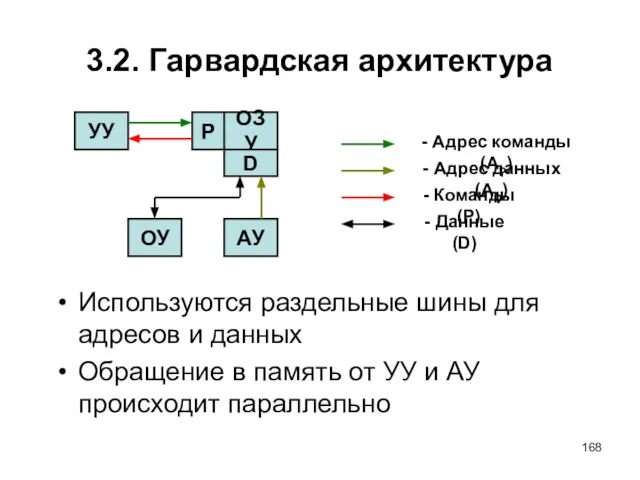

- 168. 3.2. Гарвардская архитектура Используются раздельные шины для адресов и данных Обращение в память от УУ и

- 169. 3.3. RISC-архитектура Архитектура с редуцированной системой команд Все команды выполняются за равное количество тактов, что позволяет

- 170. 4. Система прерывания Изначально СП появилась для повышения надежности вычислительного процесса Инженерное решение состояло в том,

- 171. Совокупность информации, необходимой для восстановления вычислительного процесса называется вектором состояния или словом состояния (PSW) Вектор состояния

- 172. 4.1. PSW фирмы Intel Основные флаги: CF – флаг переноса. Используется для команд сдвига или циклического

- 173. AF – вспомогательный флаг переноса. Используется для двоично-десятичной арифметики. ZF – признак нуля. SF – флаг

- 174. TF – «1» - пошаговый режим. Запрет перехода к следующей команде. IF – флаг разрешения прерывания.

- 175. 4.2. Управление системой Все периферийные устройства также характеризуются своим состоянием Управление вычислительным процессом осуществляется с помощью

- 176. Учебный курс Принципы построения и функционирования ЭВМ Лекция 13 Система прерывания. Команды ввода/вывода. профессор ГУ-ВШЭ, доктор

- 177. Система прерывания Характеристики системы прерывания Показатели качества работы системы

- 178. Основные функции системы прерывания обнаружение и идентификация типа прерывания запоминание состояния прерываемой программы и управление переходом

- 179. Характеристики системы прерывания общее количество запросов прерывания время реакции системы глубина прерывания насыщение системы прерывания допустимые

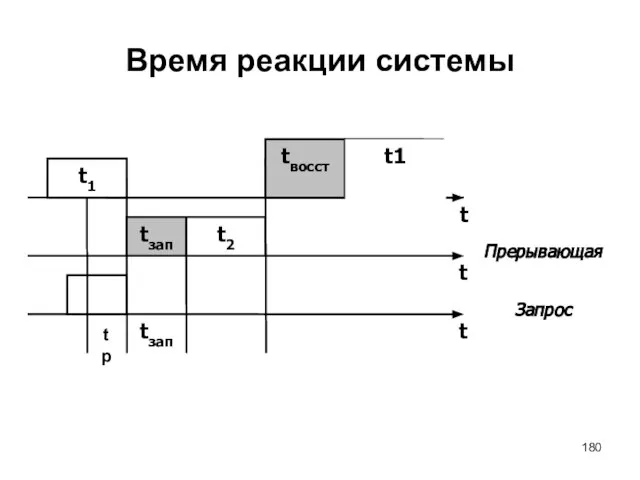

- 180. Время реакции системы t1 tр

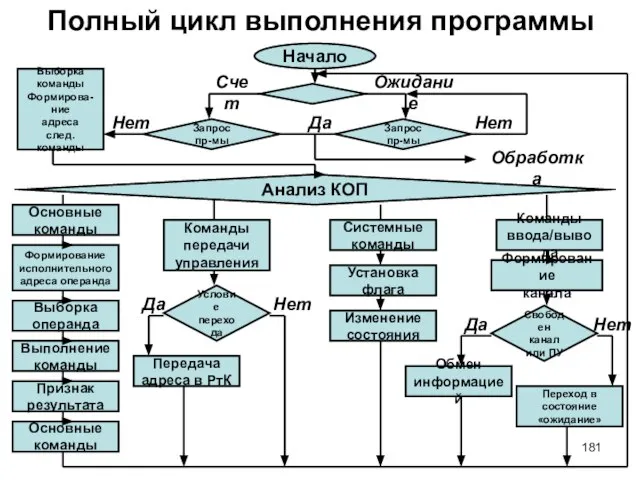

- 181. Полный цикл выполнения программы Начало Запрос пр-мы Выборка команды Формирова- ние адреса след. команды Запрос пр-мы

- 182. Специфика выполнения команд ввода/вывода Основная специфика порождается относительно медленной работой устройств

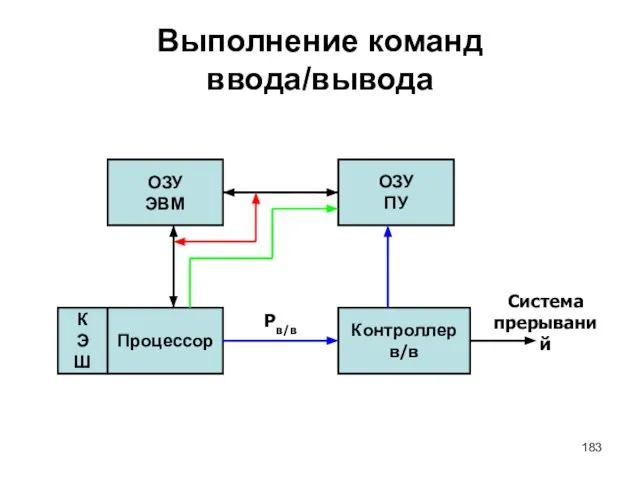

- 183. Выполнение команд ввода/вывода

- 184. Учебный курс Принципы построения и функционирования ЭВМ Лекция 14 Организация вычислительных сетей профессор ГУ-ВШЭ, доктор технических

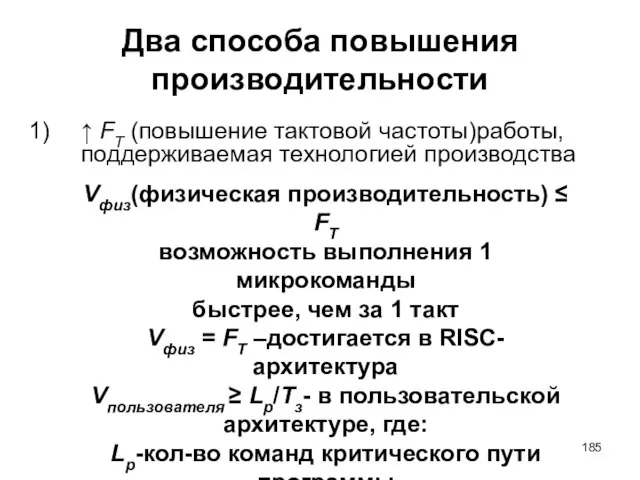

- 185. Два способа повышения производительности ↑ FT (повышение тактовой частоты)работы, поддерживаемая технологией производства Vфиз(физическая производительность) ≤ FT

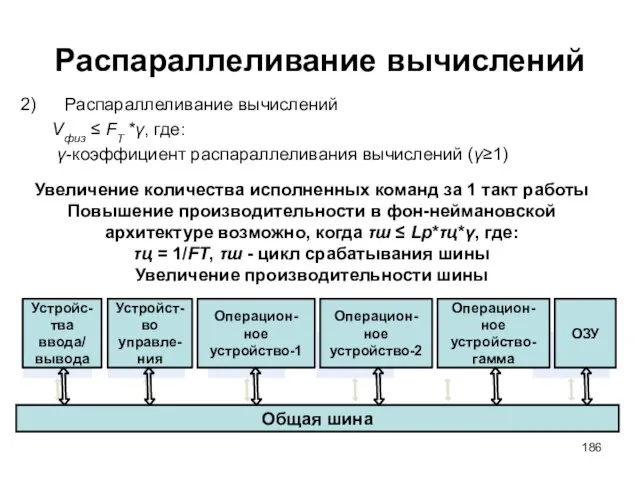

- 186. Распараллеливание вычислений Распараллеливание вычислений Vфиз ≤ FT *γ, где: γ-коэффициент распараллеливания вычислений (γ≥1) Увеличение количества исполненных

- 187. Идеал системы коммутации Отсутствие конфликтов (блокировок) запроса на передачу команд и данных между всеми без исключения

- 188. Коммутационный аспект В данном аспекте любая вычислительная система представляет собой сеть, узлы которой связаны трактами передачи

- 189. Организация внутренней коммутации и топология Организация внутренней коммутации вычислительной системы называется ее топологией, определяемая множеством узлов

- 190. Примеры топологии Кольцевая топология сети Достоинства: Передать сообщение можно в любую точку сети, но только двум

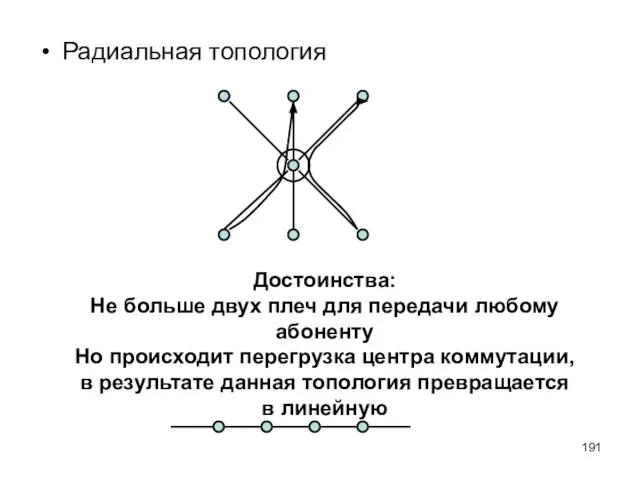

- 191. Радиальная топология Достоинства: Не больше двух плеч для передачи любому абоненту Но происходит перегрузка центра коммутации,

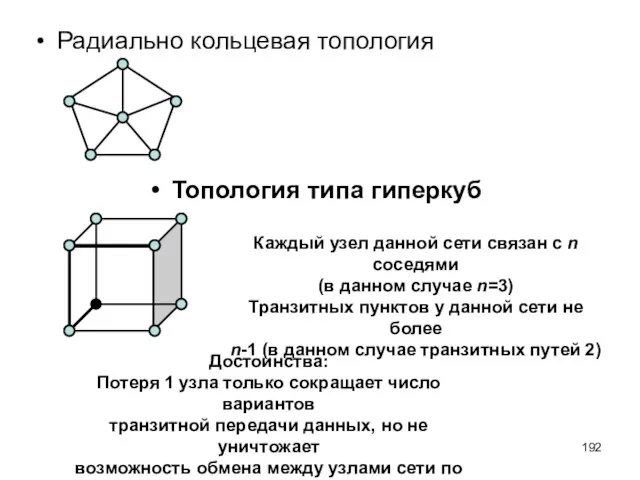

- 192. Радиально кольцевая топология Топология типа гиперкуб Каждый узел данной сети связан с n соседями (в данном

- 193. Смежные узлы и каналы Канал характеризуется: шириной (количеством сигнальных линий) частотой (скоростью передачи одной выборки данных)

- 194. Начальная задержка от источника к приемнику физическая d/Vк =tºк, где: d - длина канала tºк -

- 195. “Грамматика” передаваемого сообщения Параметры электромагнитных сигналов и правила кодирования логических переменных на физическом уровне Структура передаваемого

- 196. Топология сети и три главных атрибута сети статическая динамическая (программируемая) Главная задача - связать алгоритм с

- 197. Стратегия синхронизации и коммутации Сети синхронные (все фиксировано) асинхронные (обмен информацией происходит между двумя активными узлами

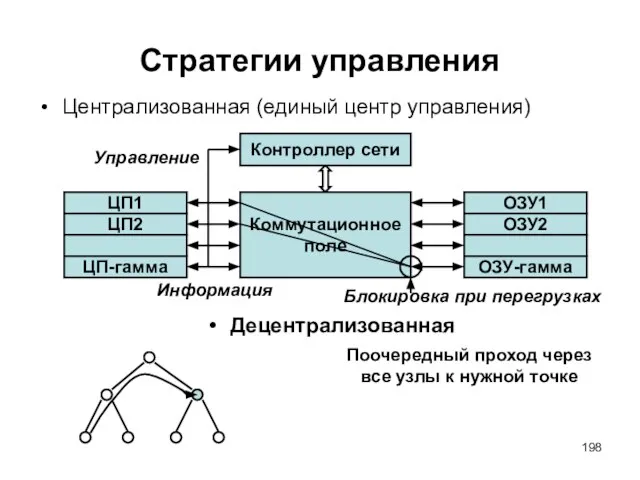

- 198. Стратегии управления Централизованная (единый центр управления) Поочередный проход через все узлы к нужной точке Децентрализованная

- 200. Скачать презентацию

Эффективные методики автоматизированного тестирования в условиях непрерывной интеграции Сергей Андреев, JetBrains. - презентация

Эффективные методики автоматизированного тестирования в условиях непрерывной интеграции Сергей Андреев, JetBrains. - презентация Загадки снеговика

Загадки снеговика Участие в допросе законного представителя, педагога, психолога и переводчика в процессе допроса несовершеннолетнего

Участие в допросе законного представителя, педагога, психолога и переводчика в процессе допроса несовершеннолетнего Имя Ломоносова на карте Архангельской области

Имя Ломоносова на карте Архангельской области Социологический портрет

Социологический портрет Безнапорные системы. Система Raineo

Безнапорные системы. Система Raineo РЕН ТВ ПРЕДСТАВЛЯЕТ

РЕН ТВ ПРЕДСТАВЛЯЕТ Аттестация педагогических работников

Аттестация педагогических работников Проект “Кабинет искусств”

Проект “Кабинет искусств” Финансовые пирамиды

Финансовые пирамиды Исследование баллистического движения

Исследование баллистического движения Функция и структура мембраны

Функция и структура мембраны Передача сигналов через линейные системы

Передача сигналов через линейные системы Презентация на тему Плоскостопие у детей и взрослых

Презентация на тему Плоскостопие у детей и взрослых  Презентация Родительское собрание 9 классов 22.09.2022

Презентация Родительское собрание 9 классов 22.09.2022 Переход к предоставлению услуги «Назначение и выплата пособия на оплату проезда на общественном транспорте» в электронном виде

Переход к предоставлению услуги «Назначение и выплата пособия на оплату проезда на общественном транспорте» в электронном виде Презентация на тему древние образы в народном искусстве 5 класс

Презентация на тему древние образы в народном искусстве 5 класс  Жилища животных 7 класс

Жилища животных 7 класс Работа со слабыми учащимися

Работа со слабыми учащимися Реки России

Реки России Технология изготовления изделий с использованием сложных соединений. Шиповые соединения

Технология изготовления изделий с использованием сложных соединений. Шиповые соединения Продажа участка 26 Га в Малой Даниловке. Харьковская область

Продажа участка 26 Га в Малой Даниловке. Харьковская область Закон Паскаля

Закон Паскаля Схема дузазы-биле тоолду тургузары

Схема дузазы-биле тоолду тургузары История создания музеяЛьва Кассиля

История создания музеяЛьва Кассиля Ожирение

Ожирение Роман был дописан. «И я вышел в жизнь, держа его в руках, и тогда моя жизнь кончилась». Что означает эта фраза? Что же произойд

Роман был дописан. «И я вышел в жизнь, держа его в руках, и тогда моя жизнь кончилась». Что означает эта фраза? Что же произойд Патологическая анатомия, ее содержание и задачи

Патологическая анатомия, ее содержание и задачи