Содержание

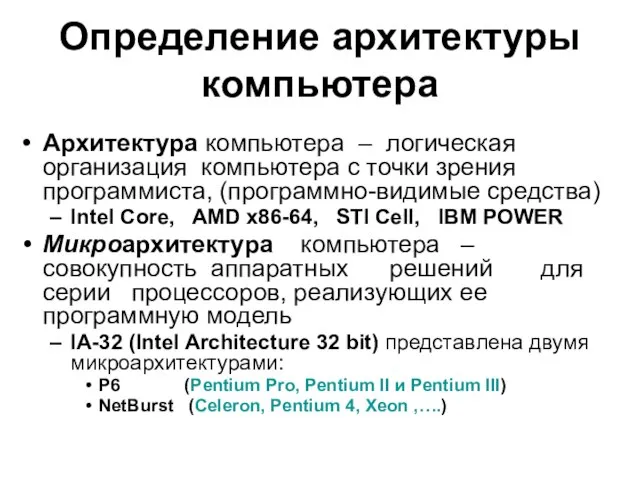

- 2. Определение архитектуры компьютера Архитектура компьютера – логическая организация компьютера с точки зрения программиста, (программно-видимые средства) Intel

- 3. ENIAC (Electronic Numerical Integrator and Computer) 1943 г., Джон Мочли, Джон Эккерт Не хранится программа Нет

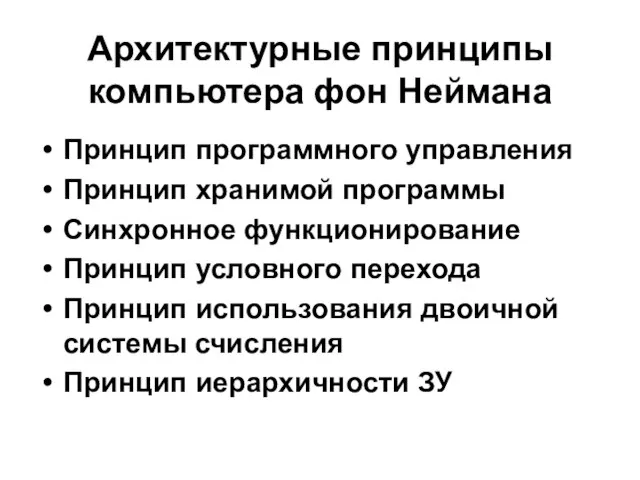

- 4. Архитектурные принципы компьютера фон Неймана Принцип программного управления Принцип хранимой программы Синхронное функционирование Принцип условного перехода

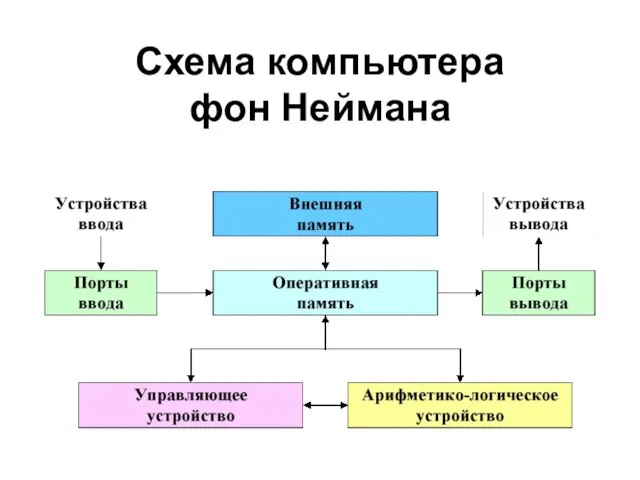

- 5. Схема компьютера фон Неймана

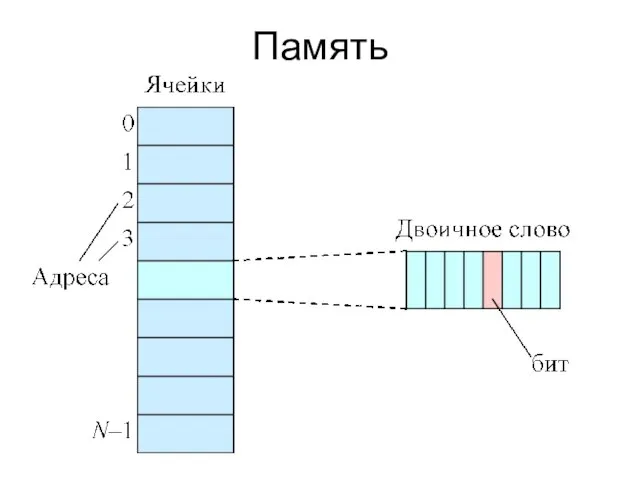

- 6. Память

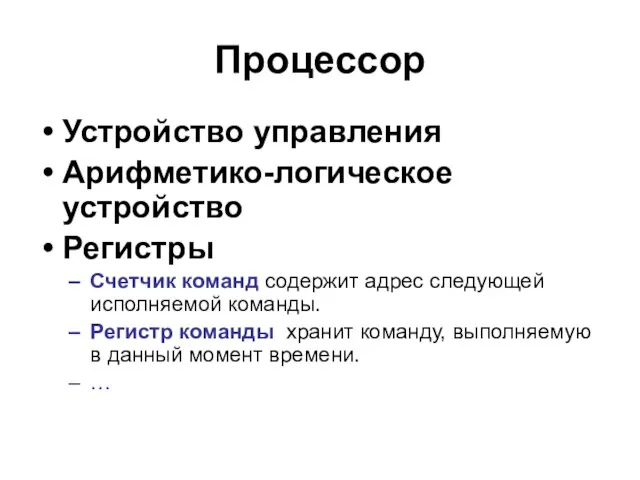

- 7. Процессор Устройство управления Арифметико-логическое устройство Регистры Счетчик команд содержит адрес следующей исполняемой команды. Регистр команды хранит

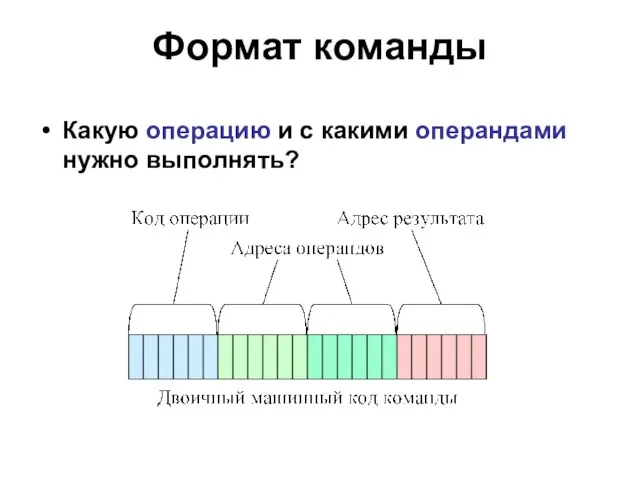

- 8. Формат команды Какую операцию и с какими операндами нужно выполнять?

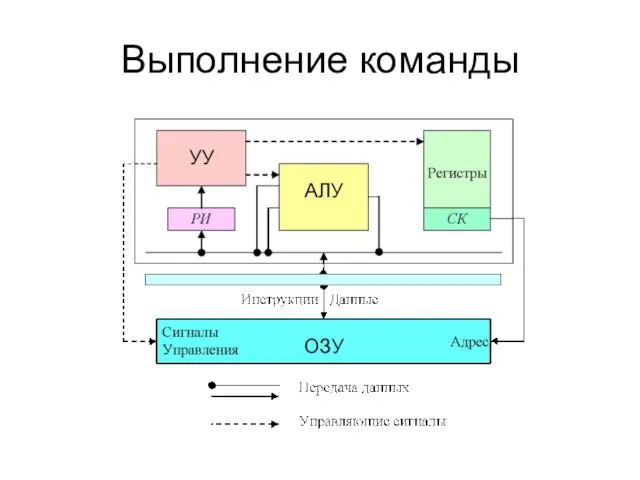

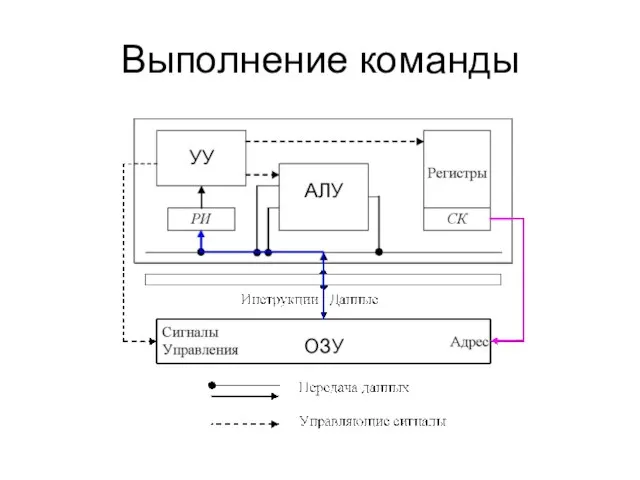

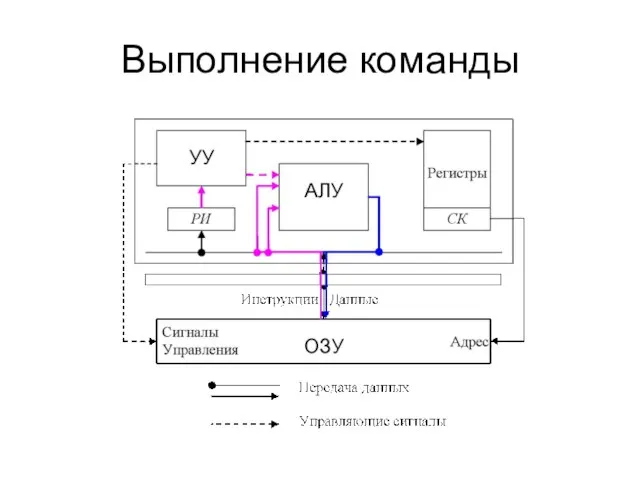

- 9. Выполнение команды

- 10. Выполнение команды

- 11. Выполнение команды

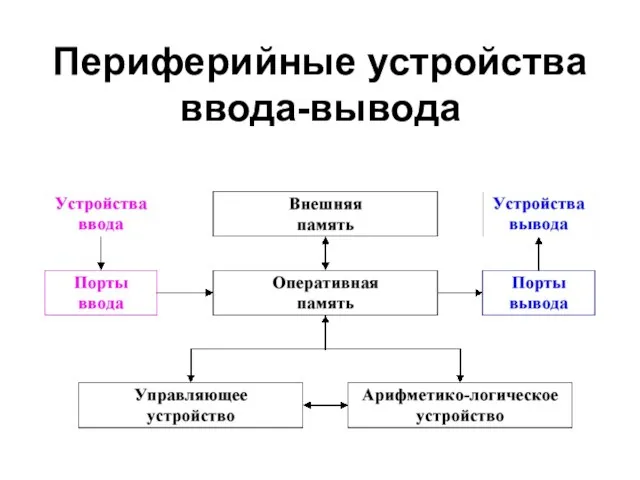

- 12. Периферийные устройства ввода-вывода

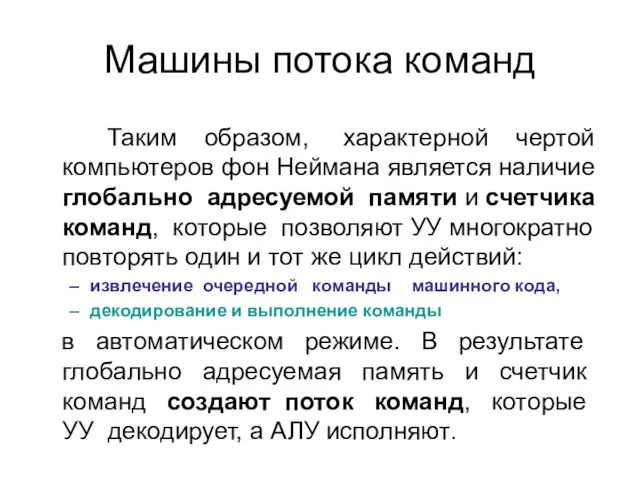

- 13. Машины потока команд Таким образом, характерной чертой компьютеров фон Неймана является наличие глобально адресуемой памяти и

- 14. Управляющие стратегии вычислений Команда выполняется, если предыдущая команда, определенная в машинном коде, выполнена (control flow). Команда

- 15. Узкие места архитектуры фон Неймана Последовательное выполнение команд Хранение данных и программы в одном ОЗУ Один

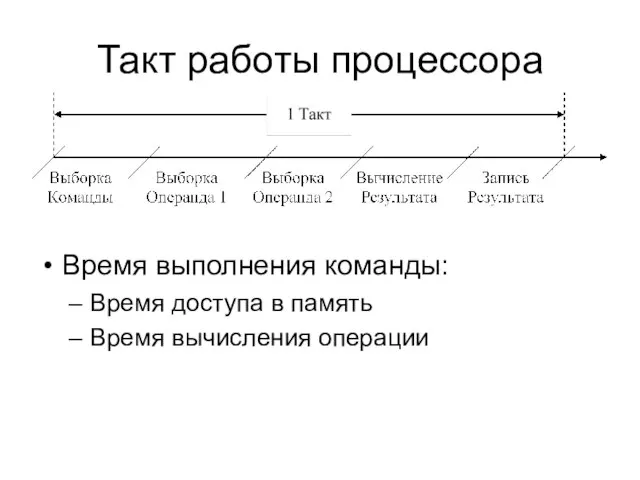

- 16. Такт работы процессора Время выполнения команды: Время доступа в память Время вычисления операции

- 17. 1951-53 гг. С. Лебедев, МЭСМ и БЭСМ 8-10 тыс. оп/сек

- 18. Усовершенствования архитектуры фон Неймана Усовершенствования в области CБИС-технологий. Программного обеспечения. Архитектурные усовершенствования.

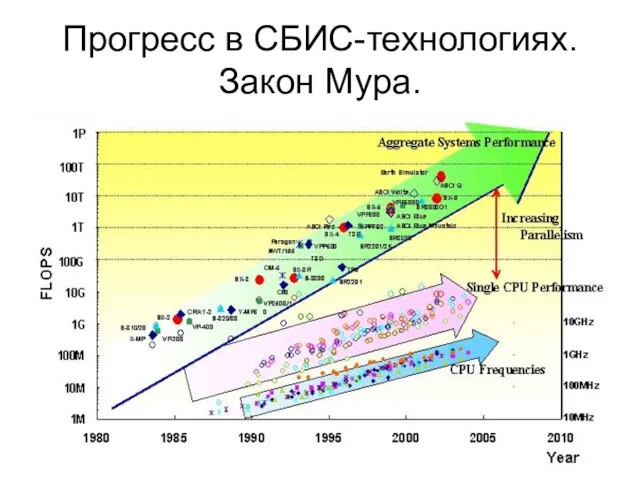

- 19. Прогресс в СБИС-технологиях. Закон Мура.

- 20. Усовершенствование ПО Языки программирования высокого уровня Компиляторы Библиотеки подпрограмм Параллельные языки программирования Коммуникационные библиотеки

- 21. Характеристики суперкомпьютера Roadrunner (№1 http://www.top500.org) Процессоры PowerXCell 8i 3.2 ГГц (12 240 шт.) Opteron DC 1.8

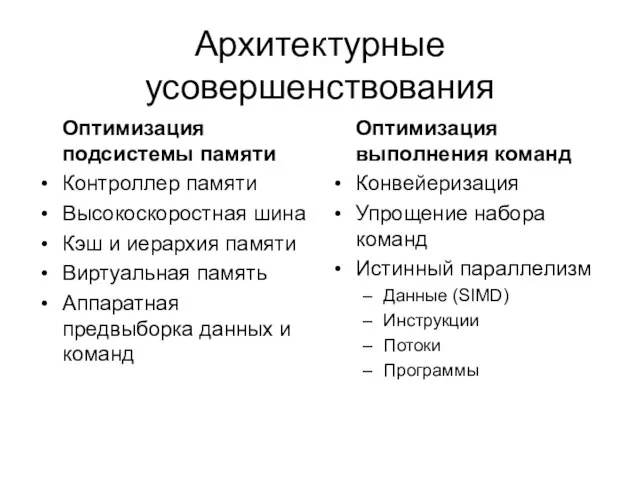

- 22. Архитектурные усовершенствования Оптимизация подсистемы памяти Контроллер памяти Высокоскоростная шина Кэш и иерархия памяти Виртуальная память Аппаратная

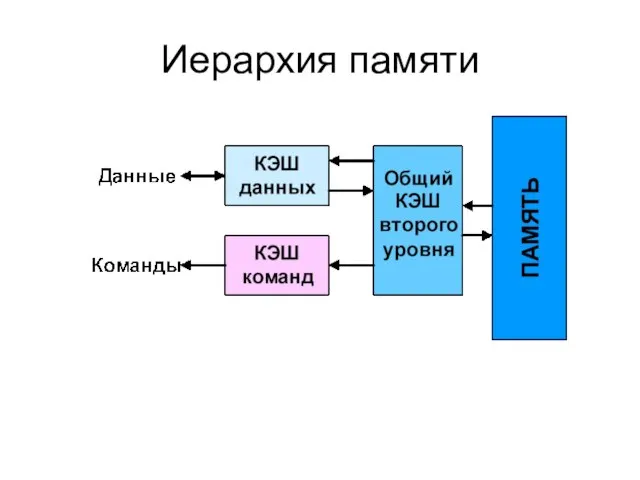

- 23. Иерархия памяти

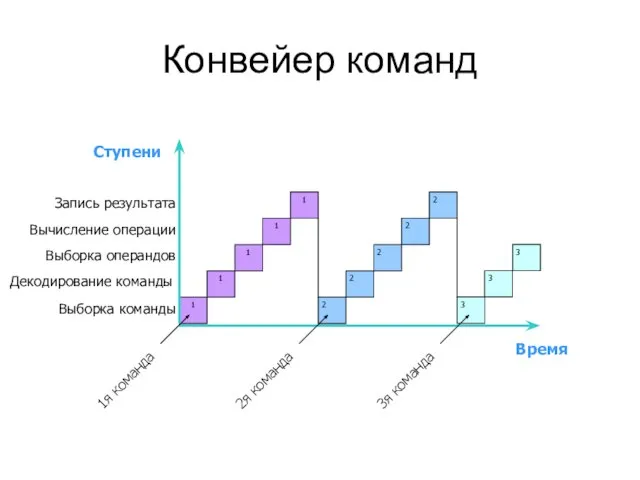

- 24. Конвейер команд 1 2 1 2 1 2 1 2 1 2 Ступени Выборка команды Декодирование

- 25. Конвейер команд 1 2 3 4 5 6 1 2 3 4 5 6 1 2

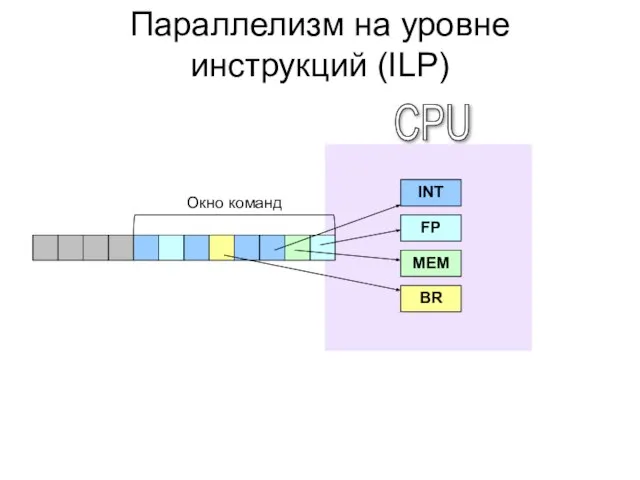

- 26. Параллелизм на уровне инструкций (ILP) INT FP MEM BR Окно команд CPU

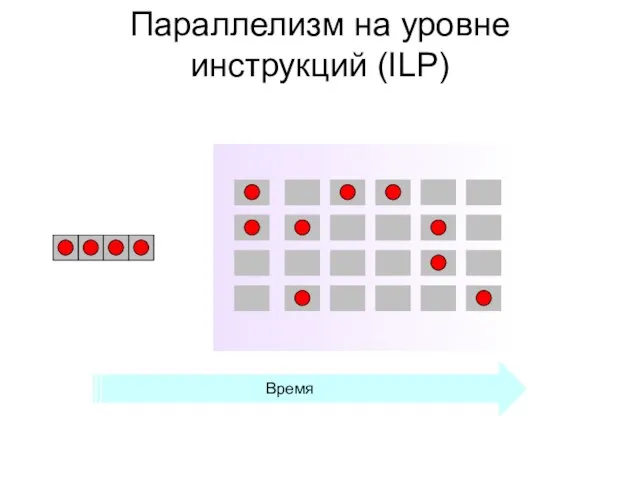

- 27. Параллелизм на уровне инструкций (ILP) Время

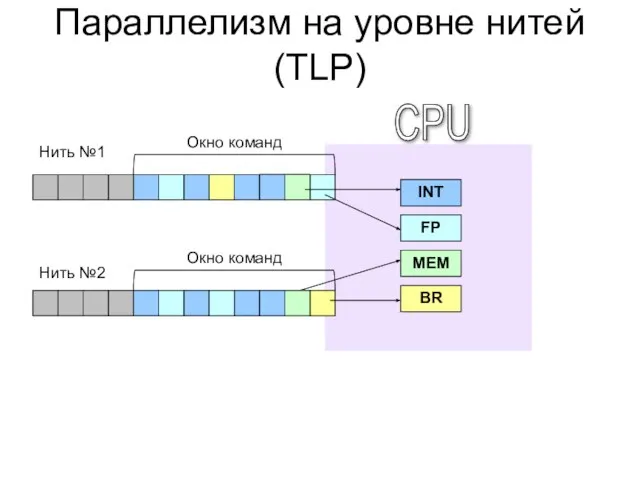

- 28. Параллелизм на уровне нитей (TLP) INT FP MEM BR Окно команд CPU Окно команд Нить №1

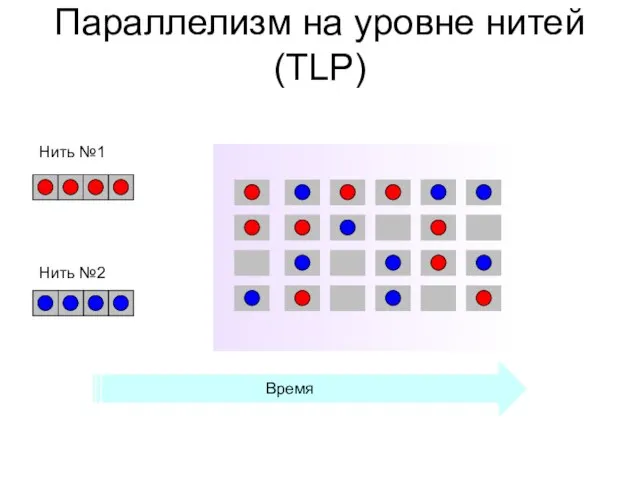

- 29. Параллелизм на уровне нитей (TLP) Время Нить №1 Нить №2

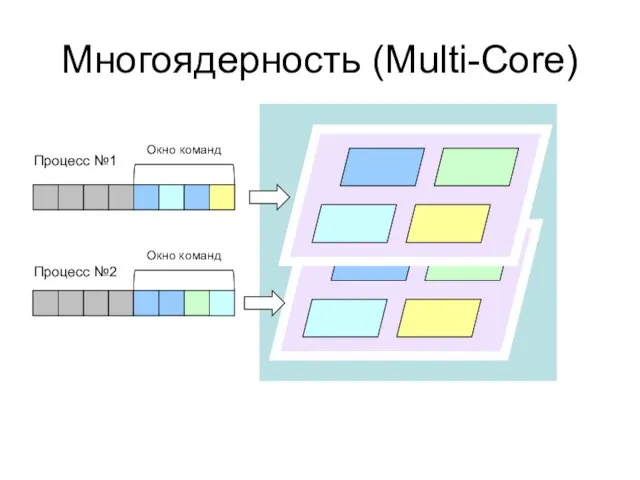

- 30. Многоядерность (Multi-Core) Окно команд Окно команд Процесс №1 Процесс №2

- 32. Скачать презентацию

Использование наглядности на уроках русского языка

Использование наглядности на уроках русского языка Взаимное расположение графиков линейных функций.

Взаимное расположение графиков линейных функций. Оленеводство

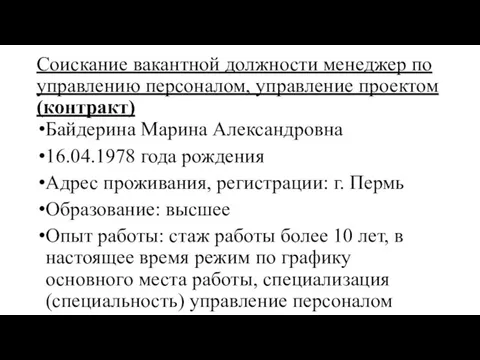

Оленеводство Соискание вакантной должности менеджер по управлению персоналом, управление проектом (контракт)

Соискание вакантной должности менеджер по управлению персоналом, управление проектом (контракт) Маркетинг территории. Город Керчь

Маркетинг территории. Город Керчь Презентация учебника литературы

Презентация учебника литературы Электронные усилители и генераторы

Электронные усилители и генераторы Модульный курс для аспирантов «Перспективы развития налогообложения в Российской Федерации» Романова Марина Владимировна Д.э

Модульный курс для аспирантов «Перспективы развития налогообложения в Российской Федерации» Романова Марина Владимировна Д.э Сервировка чайного стола

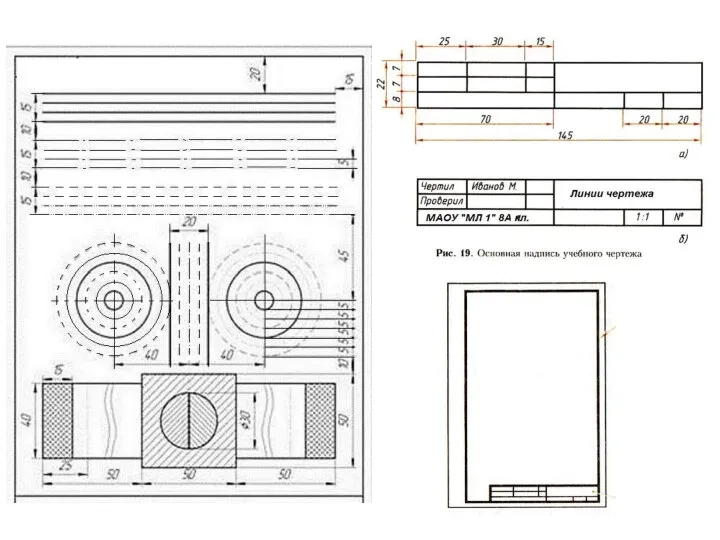

Сервировка чайного стола Линии чертежа

Линии чертежа Современное декоративно-прикладное искусство

Современное декоративно-прикладное искусство ЖИЗНЬ И ТВОРЧЕСТВО М.С.БЕРЕЗОВСКОГО

ЖИЗНЬ И ТВОРЧЕСТВО М.С.БЕРЕЗОВСКОГО ОНТП 01-91. Общесоюзные нормы технологического проектирования предприятий автомобильного транспорта

ОНТП 01-91. Общесоюзные нормы технологического проектирования предприятий автомобильного транспорта Типы знаков

Типы знаков Знаки и символы в искусстве. Язык наскальной живописи

Знаки и символы в искусстве. Язык наскальной живописи Музыкальные картинки

Музыкальные картинки Технология беспроблемного общения Т. Гордона

Технология беспроблемного общения Т. Гордона "Мама, папа, я - спортивная семья!"

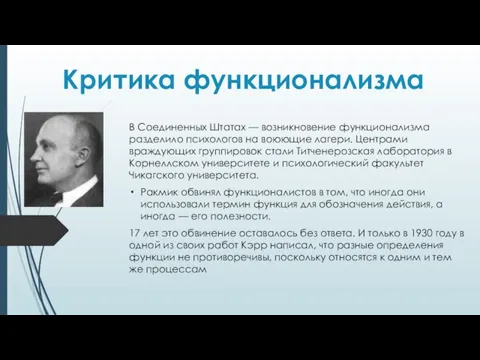

"Мама, папа, я - спортивная семья!" Критика функционализма

Критика функционализма Предложение с однородными членами

Предложение с однородными членами Отрасль Машиностроения

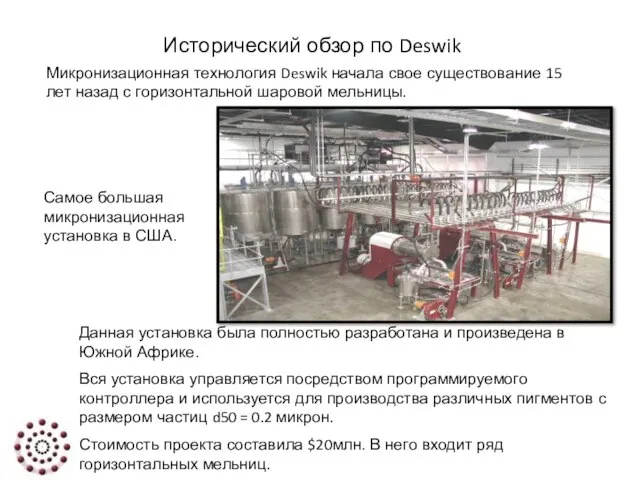

Отрасль Машиностроения Микронизационная технология Deswik

Микронизационная технология Deswik Покровы тела Сравнительная характеристика

Покровы тела Сравнительная характеристика Подбор руководителя

Подбор руководителя Шаблоны. 8 марта

Шаблоны. 8 марта Новые подходы Банка России к целеполаганию на валютном рынке

Новые подходы Банка России к целеполаганию на валютном рынке Символика России

Символика России Современные подходы к оцениванию учебных достижений обучающихся

Современные подходы к оцениванию учебных достижений обучающихся