Содержание

- 2. Память Основной единицей хранения данных в памяти является двоичный разряд - бит. Набор бит объединяется в

- 3. Память Память выполняет три операции: а) хранение информации; б) запись информации; в) чтение информации.

- 4. Характеристики памяти Емкость памяти - определяет максимальное количество хранимой в памяти информации (в битах, байтах, килобайтах,

- 5. Характеристики памяти Пропускная способность шины памяти (Bandwidth) Количество данных, переданных памятью по шине памяти за единицу

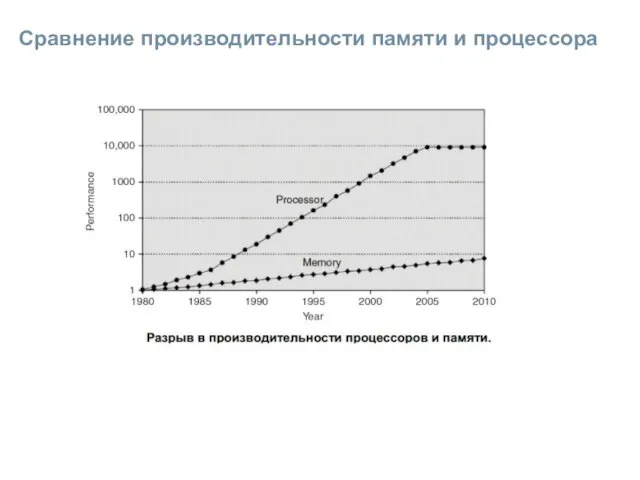

- 6. Сравнение производительности памяти и процессора

- 7. Организация микросхем памяти

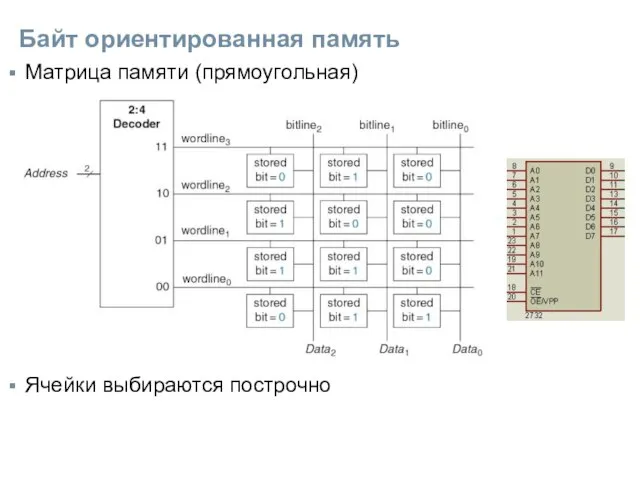

- 8. Байт ориентированная память Матрица памяти (прямоугольная) Ячейки выбираются построчно

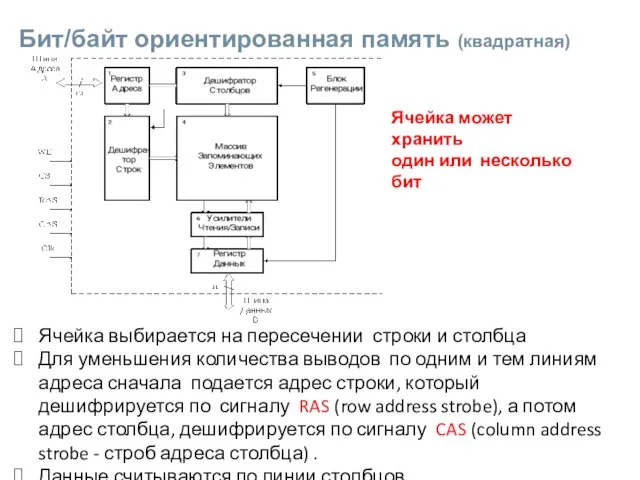

- 9. Бит/байт ориентированная память (квадратная) Ячейка выбирается на пересечении строки и столбца Для уменьшения количества выводов по

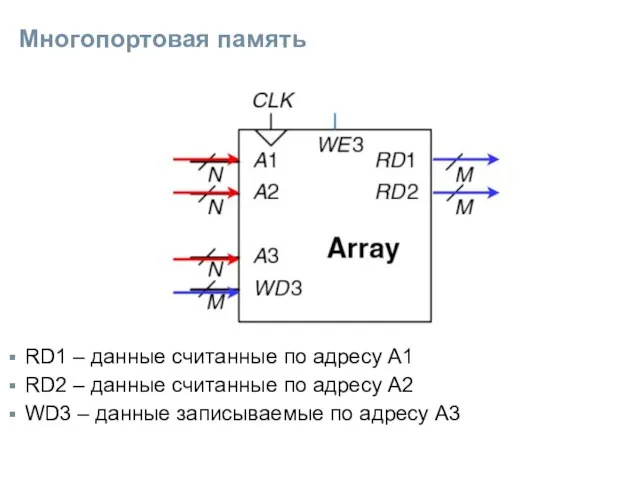

- 10. Многопортовая память RD1 – данные считанные по адресу А1 RD2 – данные считанные по адресу А2

- 11. Типы памяти Статическая память (СОЗУ); Динамическая память (ДОЗУ); Энергонезависимая память : Однократно программируемая; Многократно программируемая память;

- 12. Иерархия памяти Задержка в регистрах процессора зависит от тактовой частоты

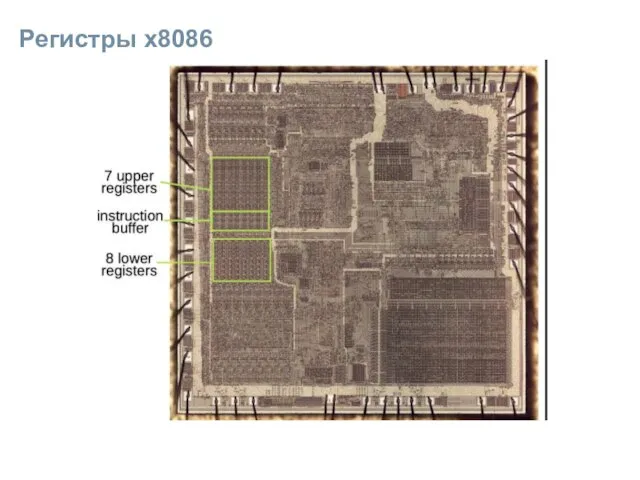

- 13. Регистры х8086

- 14. Регистры процессора Работают на частоте процессора В качестве запоминающего элемента используются триггеры с количеством транзисторов от

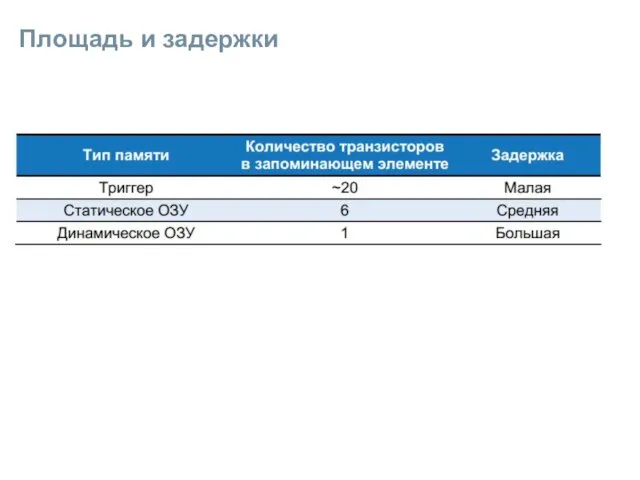

- 15. Площадь и задержки

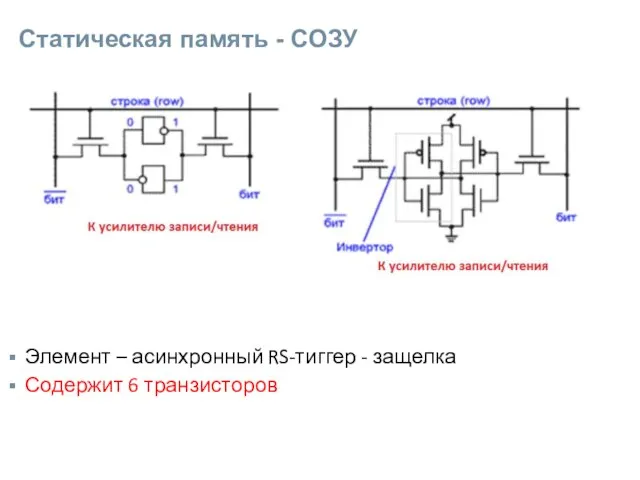

- 16. Статическая память - СОЗУ Элемент – асинхронный RS-тиггер - защелка Содержит 6 транзисторов

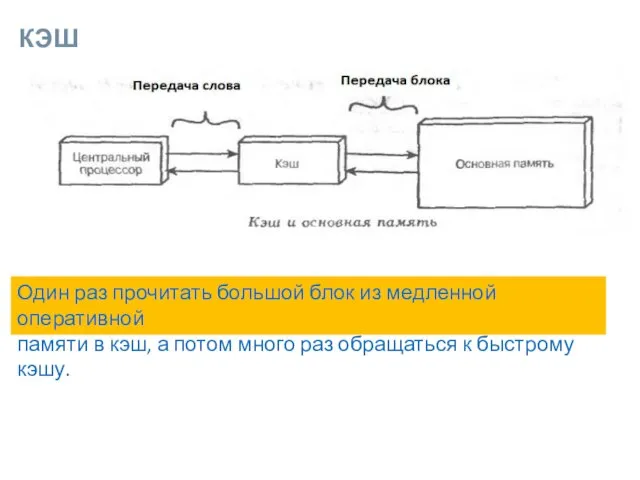

- 17. КЭШ Один раз прочитать большой блок из медленной оперативной памяти в кэш, а потом много раз

- 18. КЭШ Кэш должен предсказать, какие данные понадобятся процессору, и выбирать их из оперативной памяти Для предсказания

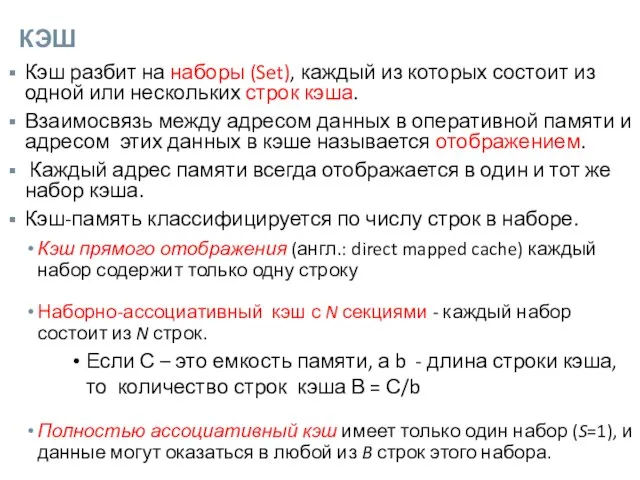

- 19. КЭШ Кэш разбит на наборы (Set), каждый из которых состоит из одной или нескольких строк кэша.

- 20. Кэш прямого отображения

- 21. КЭШ прямого отображения В кэш-памяти прямого отображения каждый набор содержит только одну строку кэша Оперативная память

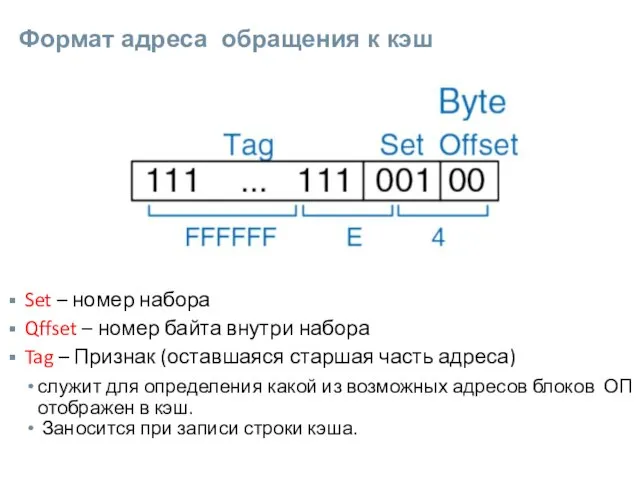

- 22. Формат адреса обращения к кэш Set – номер набора Qffset – номер байта внутри набора Tag

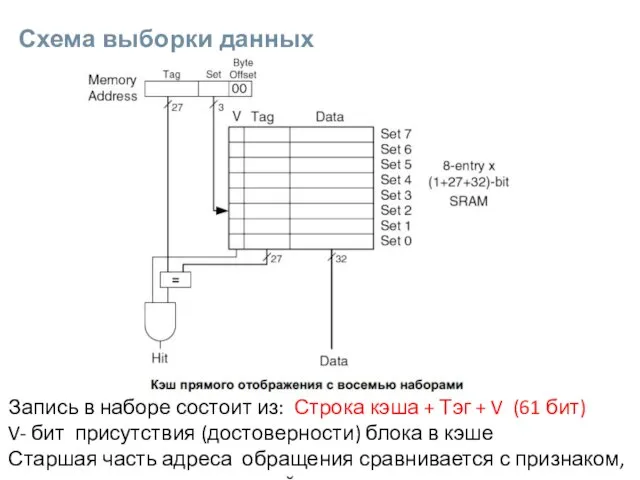

- 23. Схема выборки данных Запись в наборе состоит из: Строка кэша + Тэг + V (61 бит)

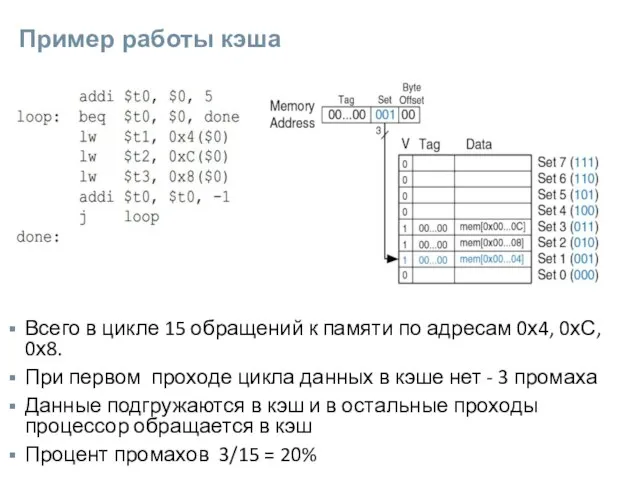

- 24. Пример работы кэша Всего в цикле 15 обращений к памяти по адресам 0х4, 0хС, 0х8. При

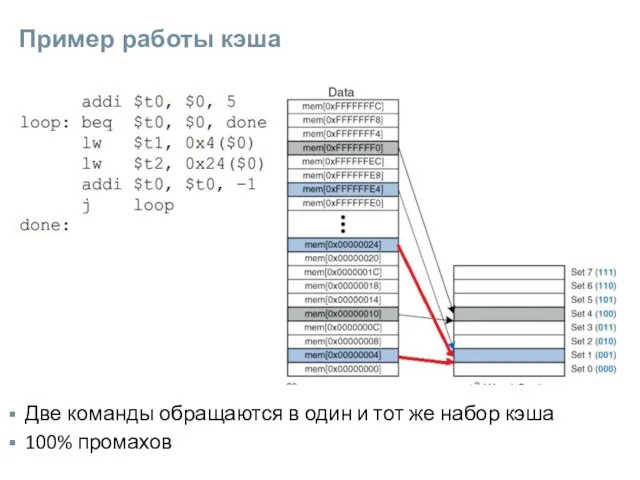

- 25. Пример работы кэша Две команды обращаются в один и тот же набор кэша 100% промахов

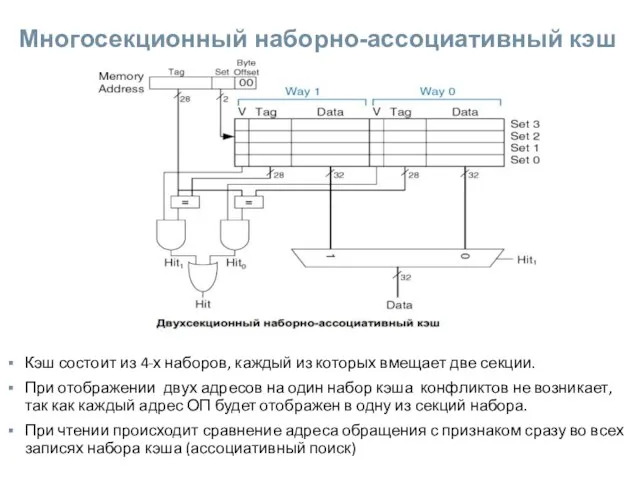

- 26. Многосекционный наборно-ассоциативный кэш Кэш состоит из 4-х наборов, каждый из которых вмещает две секции. При отображении

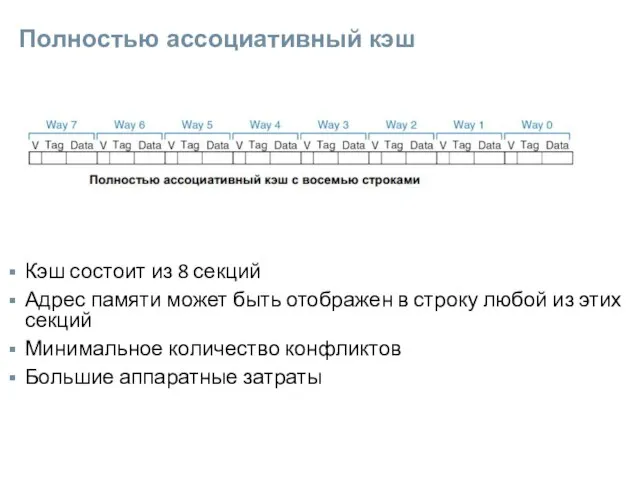

- 27. Полностью ассоциативный кэш Кэш состоит из 8 секций Адрес памяти может быть отображен в строку любой

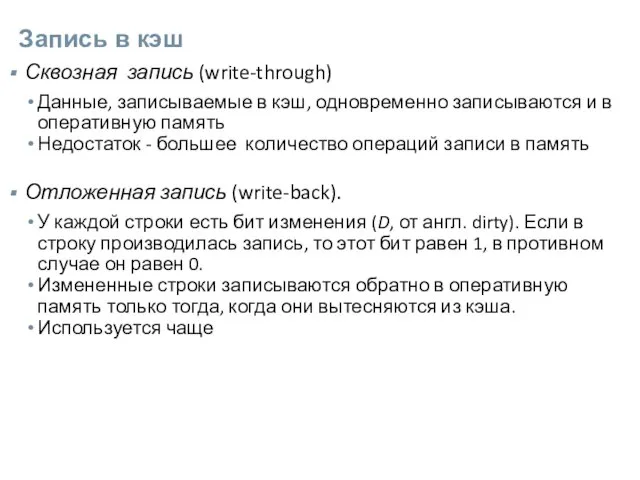

- 28. Запись в кэш Сквозная запись (write-through) Данные, записываемые в кэш, одновременно записываются и в оперативную память

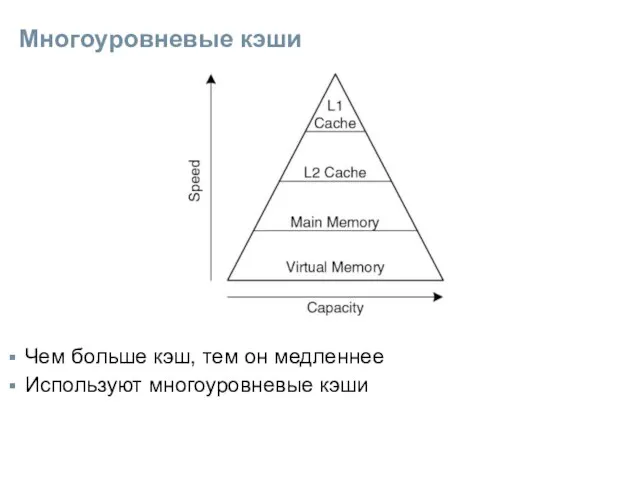

- 29. Многоуровневые кэши Чем больше кэш, тем он медленнее Используют многоуровневые кэши

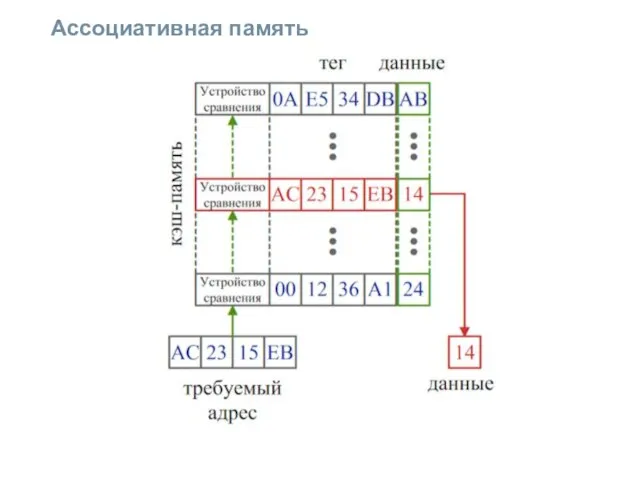

- 30. Ассоциативная память

- 31. Динамическая память

- 32. Динамическая память Матрица запоминающих элементов (конденсаторов) Низкая стоимость. (один транзистор) Низкое быстродействие (конденсатор надо периодически подзаряжать

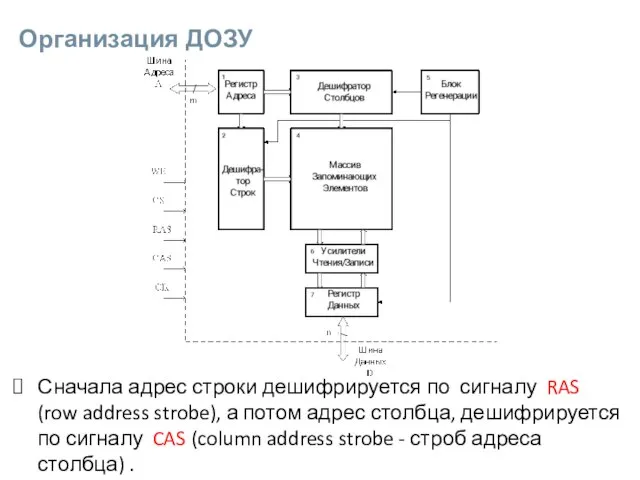

- 33. Организация ДОЗУ Сначала адрес строки дешифрируется по сигналу RAS (row address strobe), а потом адрес столбца,

- 34. Структура динамической памяти

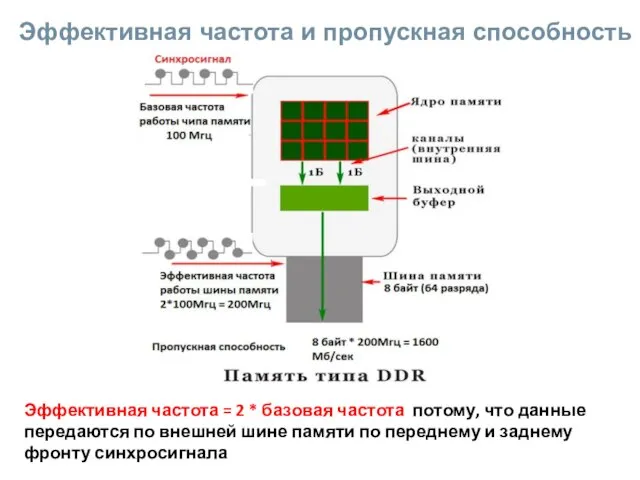

- 35. Эффективная частота и пропускная способность Эффективная частота = 2 * базовая частота потому, что данные передаются

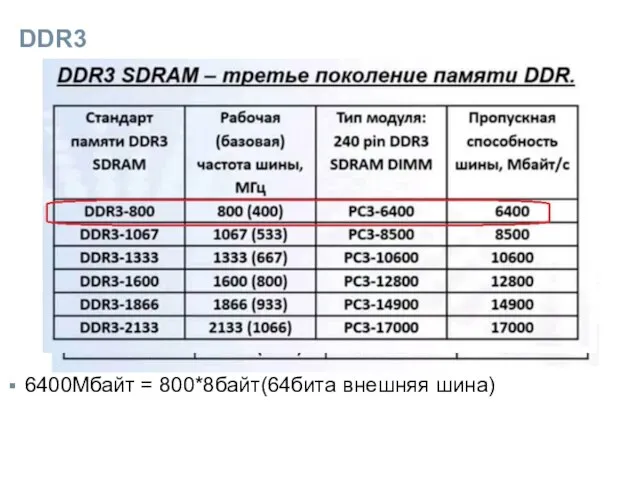

- 36. DDR3 6400Мбайт = 800*8байт(64бита внешняя шина)

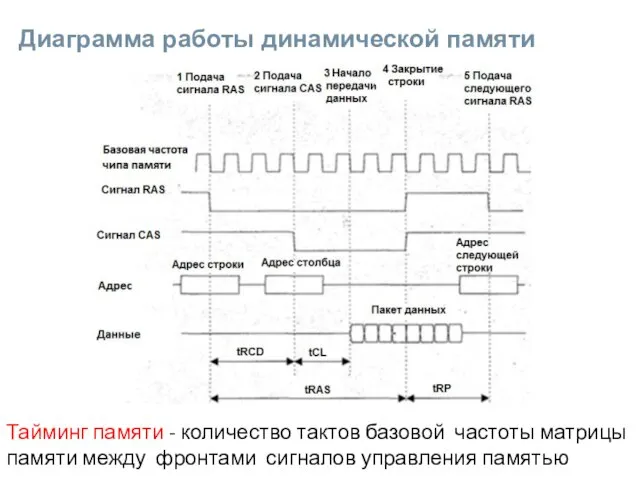

- 37. Диаграмма работы динамической памяти Тайминг памяти - количество тактов базовой частоты матрицы памяти между фронтами сигналов

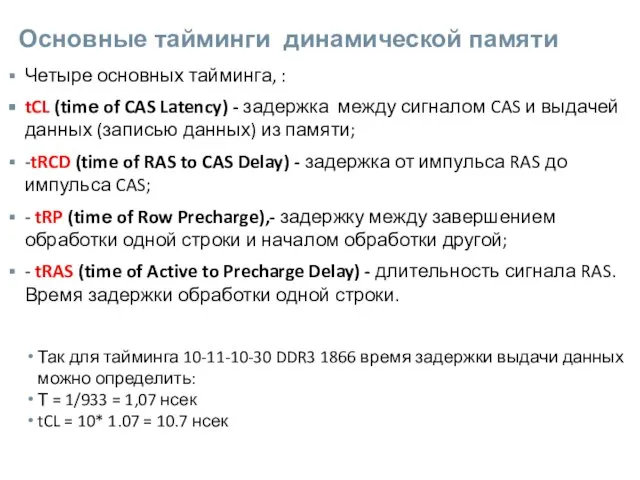

- 38. Основные тайминги динамической памяти Четыре основных тайминга, : tCL (timе of CAS Latency) - задержка между

- 39. Тайминги динамической памяти Идеально – все единицы. Для памяти с большей частотой внешней шины(DDR3 и DDR4)

- 40. Тайминги памяти

- 41. Эволюция динамической памяти SDRAM-(Synchronous Dynamic Random Access Memory) динамическое ОЗУ, работало в синхронном режиме с контроллером

- 42. Эволюция динамической памяти Double Data Rate 2 SDRAM Double Data Rate 3 SDRAM Double Data Rate

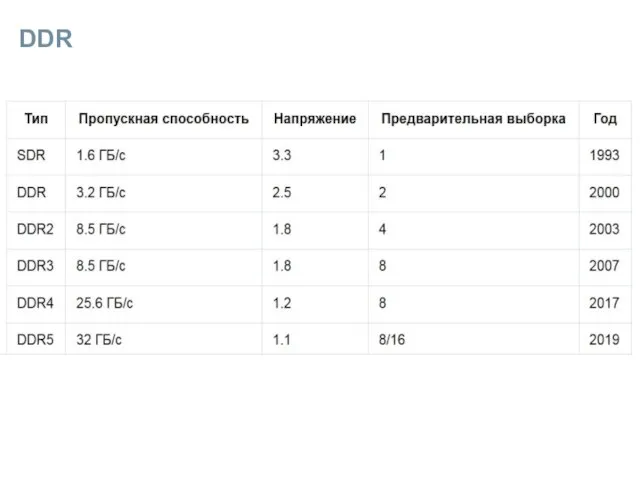

- 43. DDR

- 44. Режимы работы ДОЗУ Память может работать в: одноканальном (Single Channel), двухканальном (Dual Channel), трехканальном (Triple Channel)

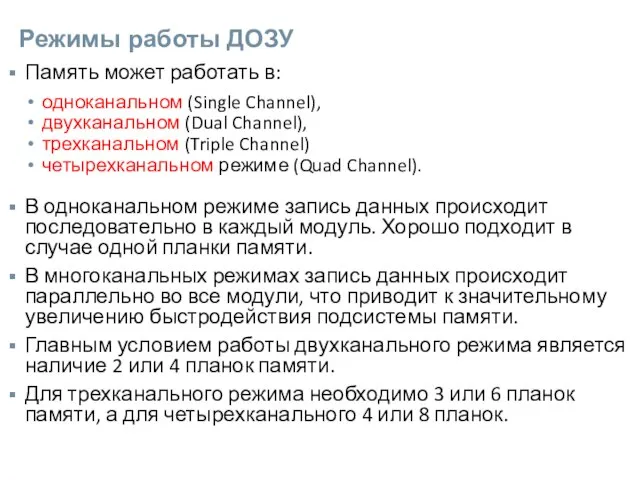

- 45. Лучшие производители Kingston Crucial Samsung Transcend Hynix Доля их брака составляет всего 0,6%

- 46. Постоянная память

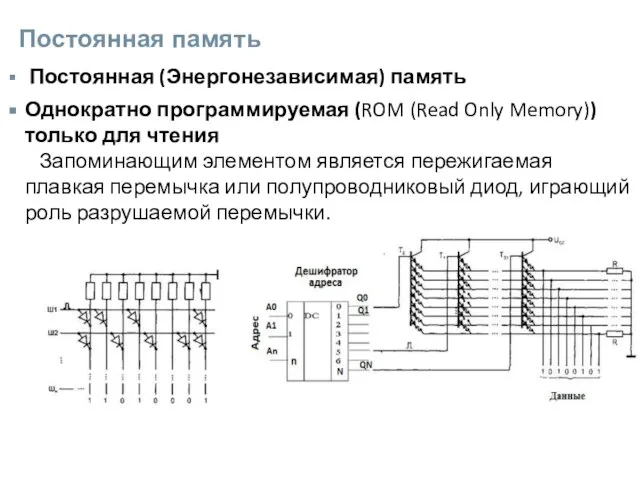

- 47. Постоянная память Постоянная (Энергонезависимая) память Однократно программируемая (ROM (Read Only Memory)) только для чтения Запоминающим элементом

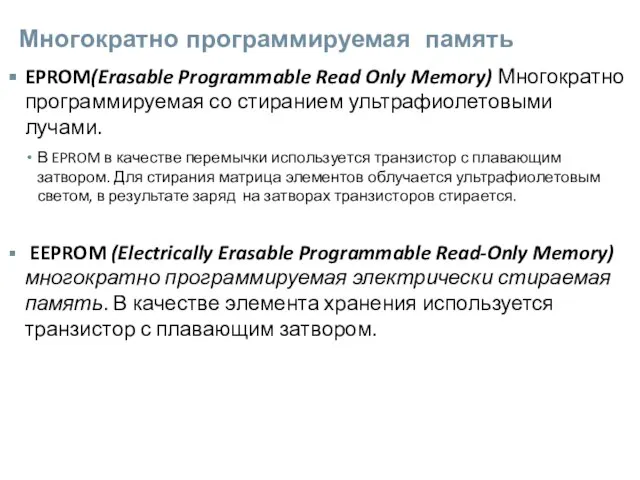

- 48. Многократно программируемая память EPROM(Erasable Programmable Read Only Memory) Многократно программируемая со стиранием ультрафиолетовыми лучами. В EPROM

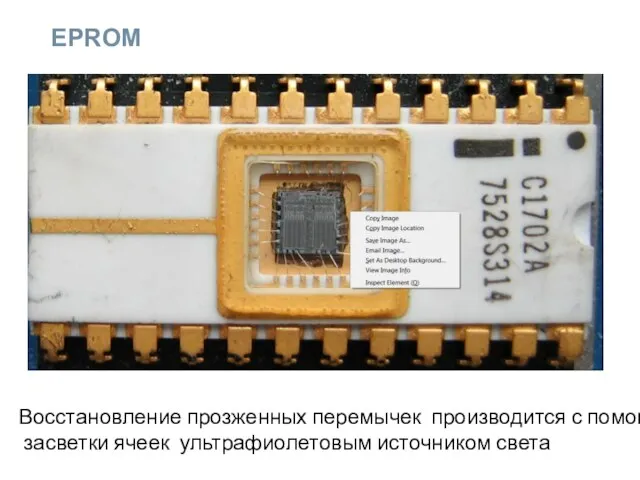

- 49. EPROM Восстановление прозженных перемычек производится с помощью засветки ячеек ультрафиолетовым источником света

- 50. Flash память

- 51. Полевой транзистор

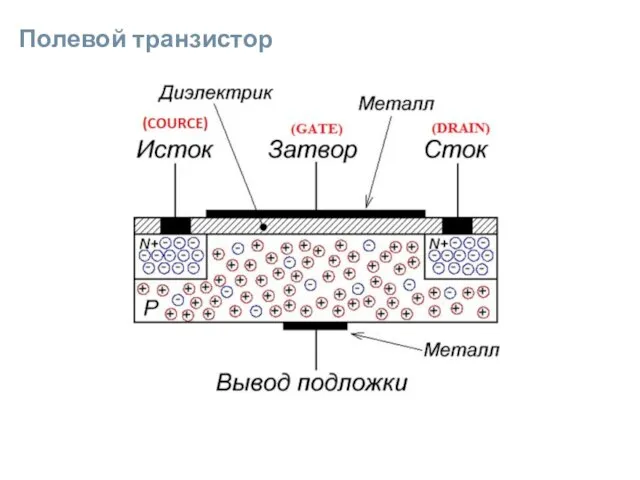

- 52. Транзистор с плавающим затвором Плавающий затвор изолирован двумя слоями диэлектрика

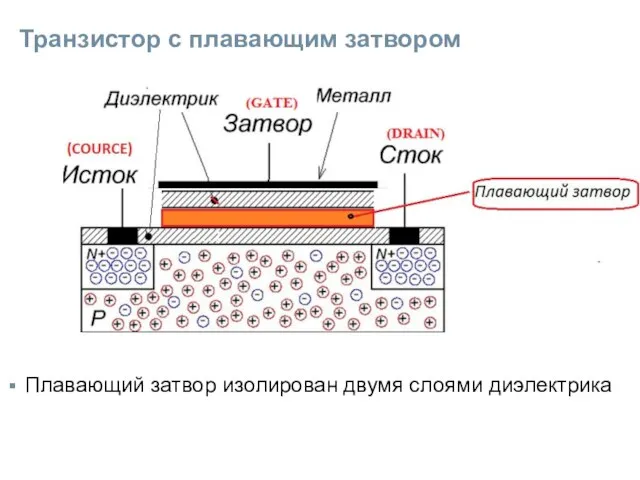

- 53. Запись При подаче на затвор более положительного напряжения чем на сток происходит перенос части электронов через

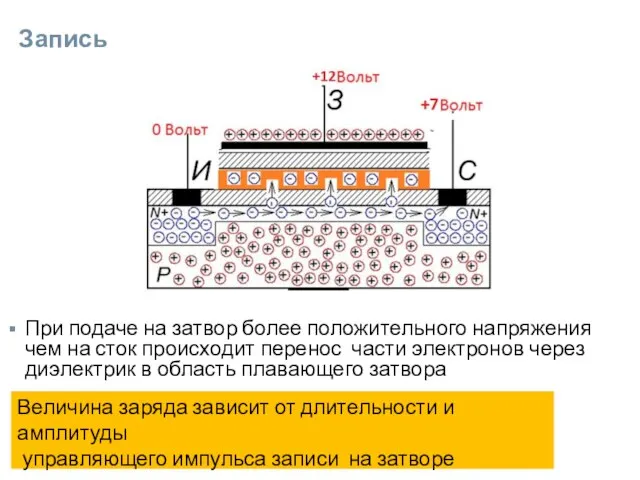

- 54. Стирание При подаче на затвор более отрицательного напряжения относительно истока происходит стекание электронов в область истока

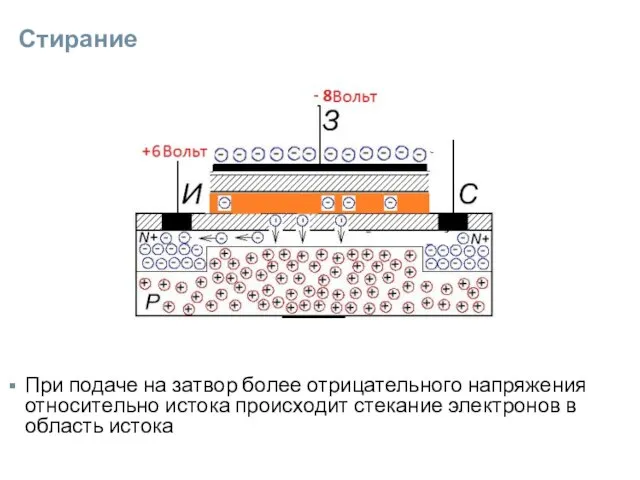

- 55. Ячейка флэш-памяти Операции записи и чтения приводят к разрушению(износу) и диэлектричсекого слоя и его постепенной деградации.

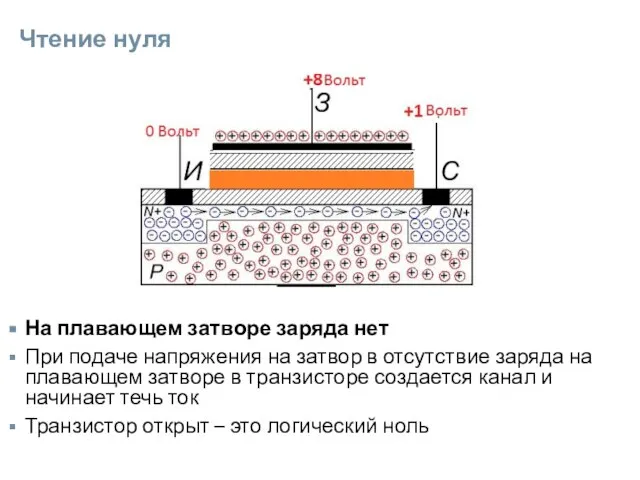

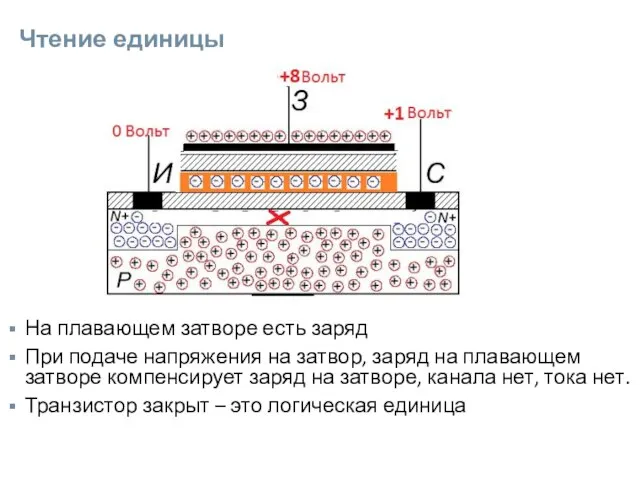

- 56. Чтение нуля На плавающем затворе заряда нет При подаче напряжения на затвор в отсутствие заряда на

- 57. Чтение единицы На плавающем затворе есть заряд При подаче напряжения на затвор, заряд на плавающем затворе

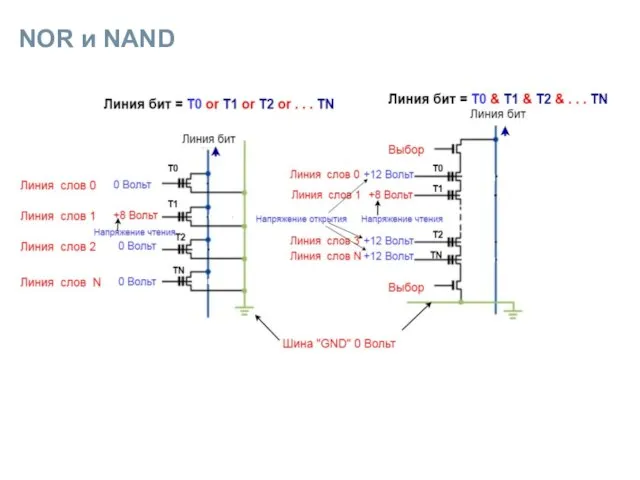

- 58. NOR и NAND

- 59. NOR - ячейка NOR При подаче напряжения чтения на линию слов транзисторы, содержащие заряд на плавающем

- 60. NAND-ячейка NAND На необходимую линию слова подается напряжение чтения, а на все остальные линии слова подается

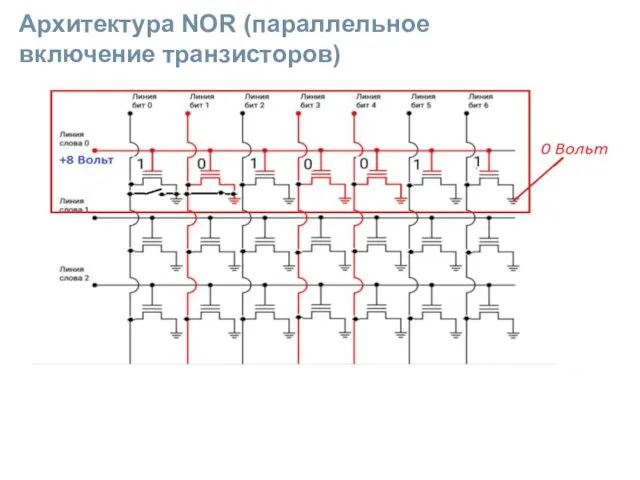

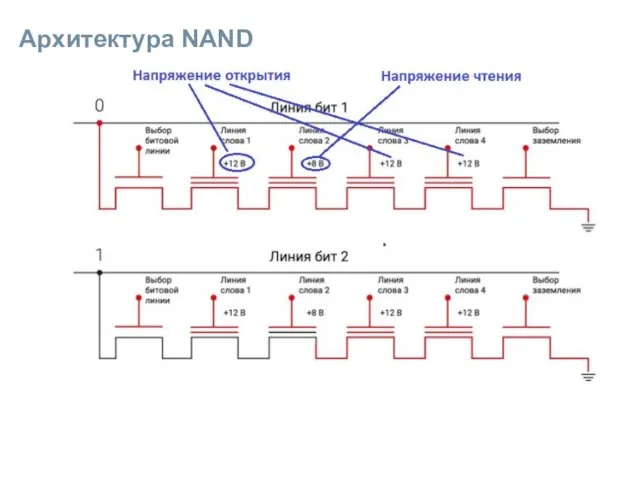

- 61. Архитектура NOR (параллельное включение транзисторов)

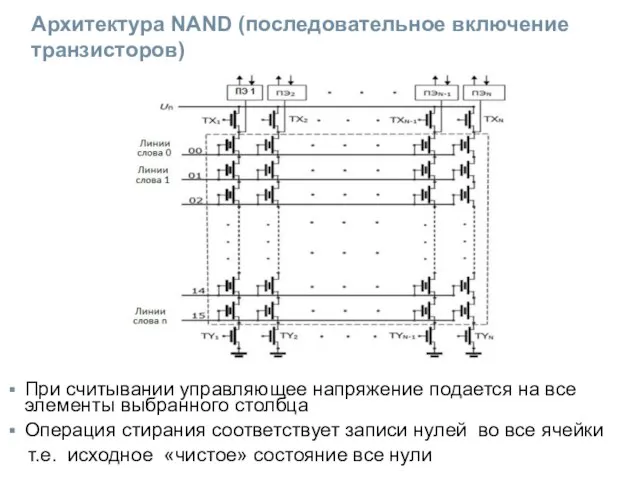

- 62. Архитектура NAND

- 63. Архитектура NOR (параллельное включение транзисторов) Операция стирания соответствует записи единиц во все ячейки т.е исходное «чистое»

- 64. Архитектура NAND (последовательное включение транзисторов) При считывании управляющее напряжение подается на все элементы выбранного столбца Операция

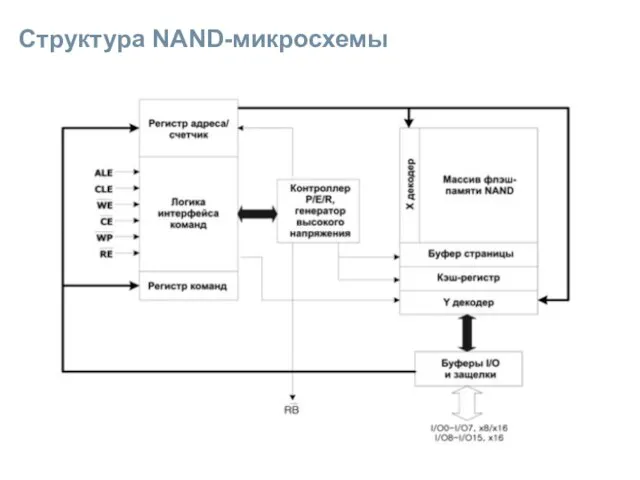

- 65. Структура NAND-микросхемы

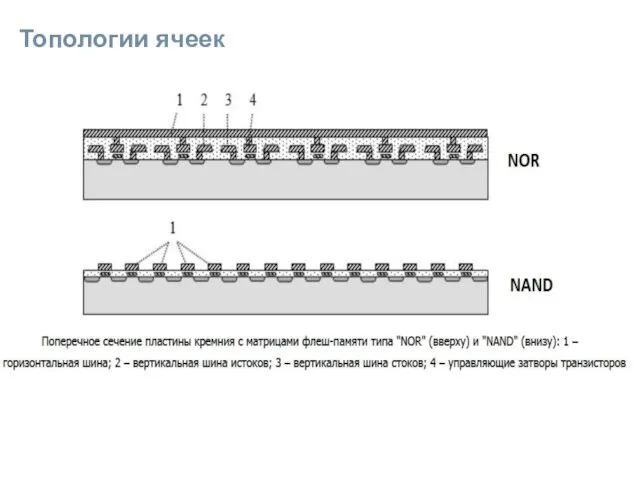

- 66. Топологии ячеек

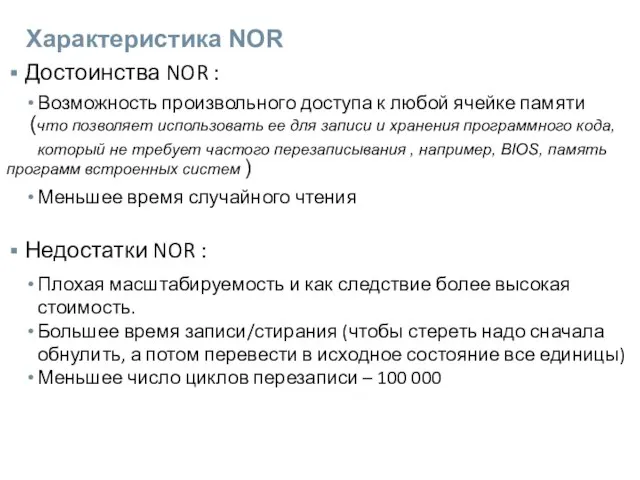

- 67. Характеристика NOR Достоинства NOR : Возможность произвольного доступа к любой ячейке памяти (что позволяет использовать ее

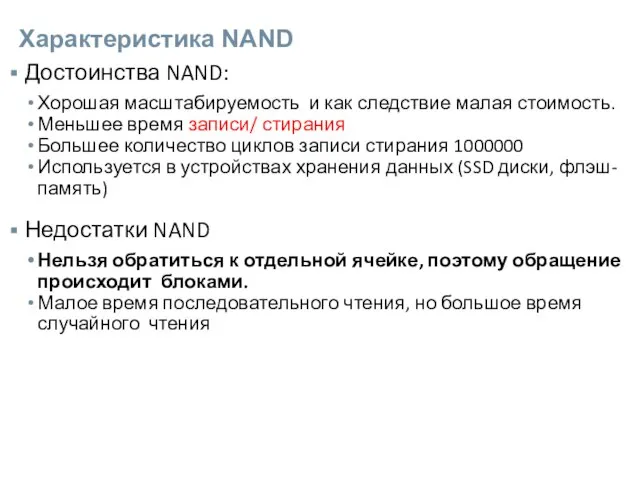

- 68. Характеристика NAND Достоинства NAND: Хорошая масштабируемость и как следствие малая стоимость. Меньшее время записи/ стирания Большее

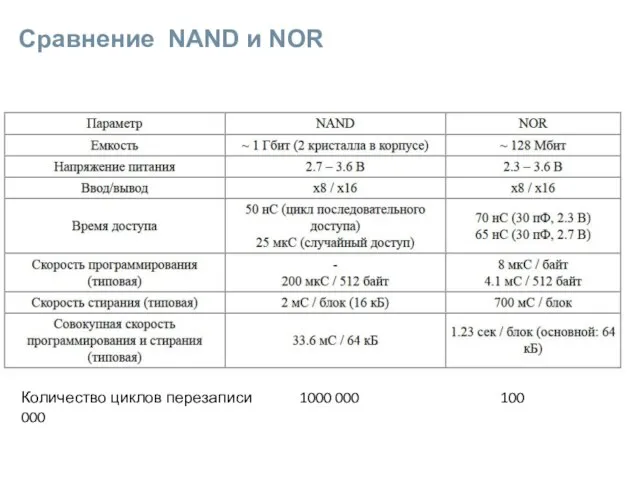

- 69. Сравнение NAND и NOR Количество циклов перезаписи 1000 000 100 000

- 70. Одноуровневые (Single Level Cell) и многоуровневые ячейки (Multi Level Cell, Three Level Cell)

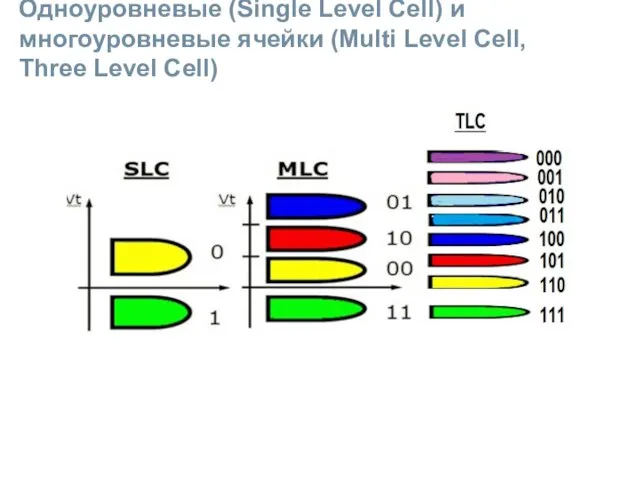

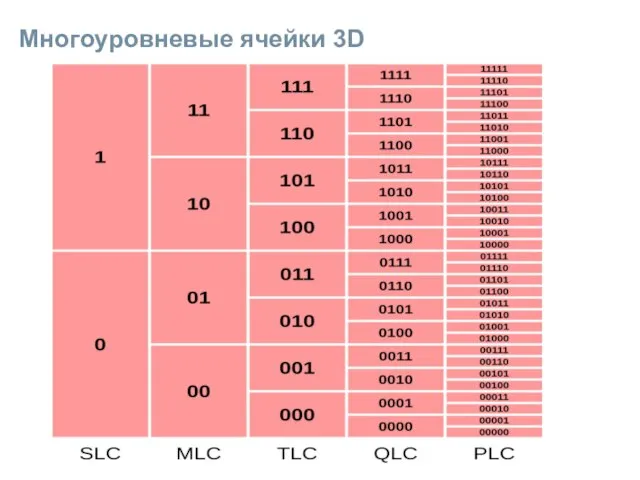

- 71. Многоуровневые ячейки 3D

- 72. Сравнение SLC и MLC SLC записывают только один бит в ячейку и это обеспечивает до 10

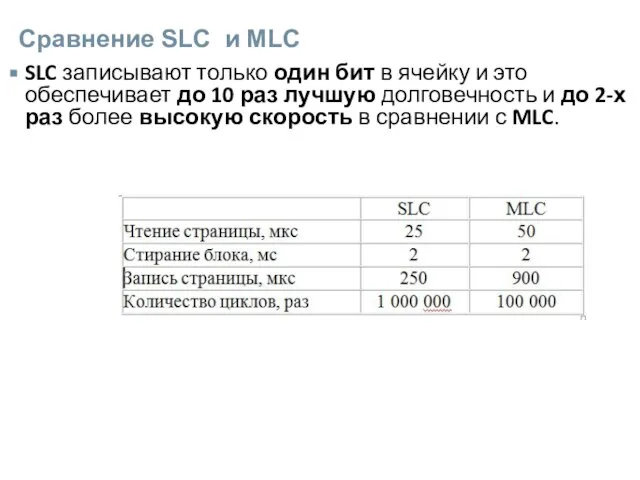

- 73. 3D флэш память (флэш-трубки) Технология 3D NAND позволяет увеличить плотность ячеек флэш памяти

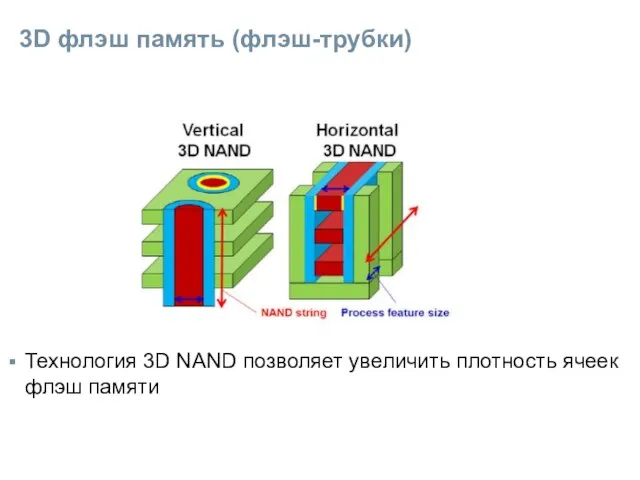

- 74. Операции при обращении к флэш -памяти Возможны операции: Стирание (ограниченное количество раз); Запись ограниченное количество раз;

- 75. Структурная организация SSD – диска (Solid State Drive) SCL и MCL ячейки объединяются в страницы по

- 76. Запись на свободный диск Данные записываются последовательно в физические блоки порциями по 4 Кбайт. При этом

- 77. Перезапись данных Если производится перезапись данных, они последовательно записываются в следующие по порядку свободные страницы памяти,

- 78. Запись на заполненный диск При заполнении диска блоки памяти могут содержать как страницы, помеченные на удаление

- 79. Запись на заполненный диск Страницы с актуальными данными из выбранного блока переносятся в пустой или резервный

- 80. Резервные блоки Разница между двоичным и десятичным значением емкости дает резервные блоки Так для диска емкостью

- 81. Механизм Wear Leveling Wear Leveling обеспечивает равномерное использование всех ячеек памяти и как следствие повышает долговечность

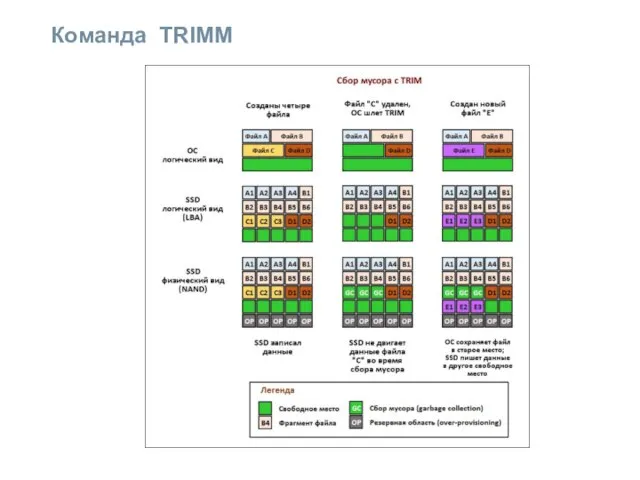

- 82. Команда TRIMM При удалении файлов операционная система лишь логически удаляет ненужные файлы. При этом физически они

- 83. Команда TRIMM

- 84. Команда TRIMM Для работы команды TRIM необходима поддержка со стороны как ОС, так и SSD-диска. Команда

- 85. SSD -диск В SSD-диска входит поле Flach – памяти, SSD-контроллер, блок динамической DRAM- памяти

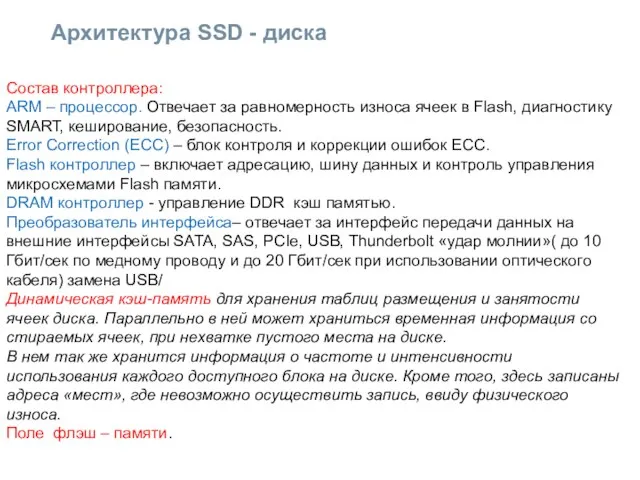

- 86. Архитектура SSD - диска Состав контроллера: ARM – процессор. Отвечает за равномерность износа ячеек в Flash,

- 87. Кэш - память В SSD накопителях применяется кэш память в виде энергозависимой DRAM микросхемы, наподобие как

- 88. Характеристики SSD накпителей Тип – внутренний, внешний, внутренний/ внешний (универсальный); Емкость; Форм - фактор: - 1.8,

- 89. Характеристики SSD накпителей Скорость случайной записи блоками определенного размера : измеряется в IOPS( Input/Output Operations Per

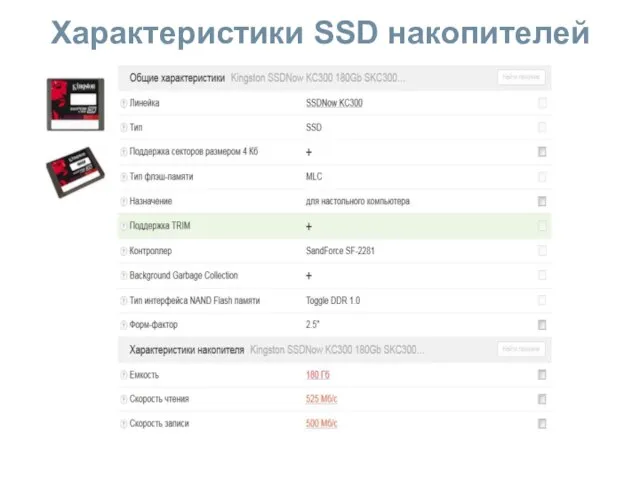

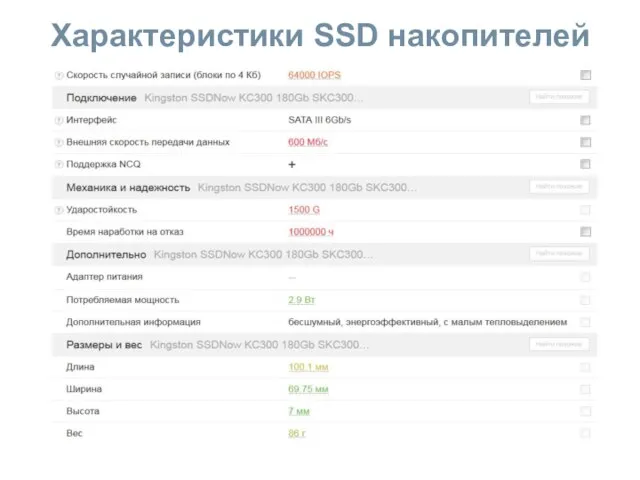

- 90. Характеристики SSD накопителей

- 91. Характеристики SSD накопителей

- 92. Оптимизация работы SSD При использовании в компьютере на SSD диск лучше установить только ОС, а файлы

- 93. Оптимизация работы SSD 2) В реестре отключить системный кэш Prefetch и Superfetch. (Они не нужны при

- 94. Оптимизация работы SSD 5)Отключить индексирование файлов SSD(в свойствах системного диска снимаем галочку с параметра «Разрешить индексировать

- 95. NVRAM (Non Volatile Random Access Memory); Тип энергонезависимой памяти (называется также полупостоянной памятью), в которой обеспечивается

- 96. ВИРТУАЛЬНАЯ ПАМЯТЬ

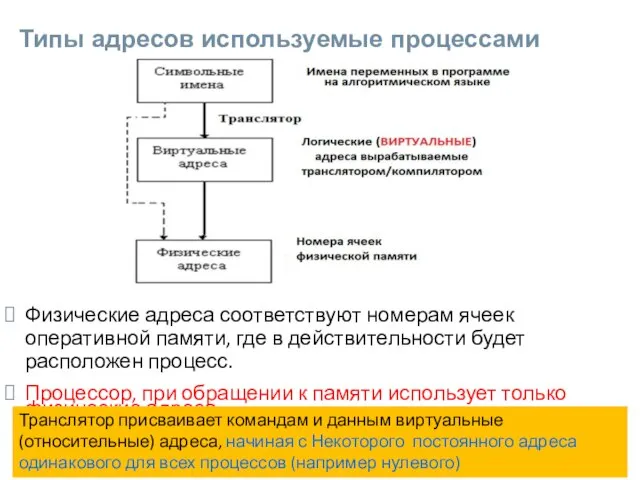

- 97. Типы адресов используемые процессами Физические адреса соответствуют номерам ячеек оперативной памяти, где в действительности будет расположен

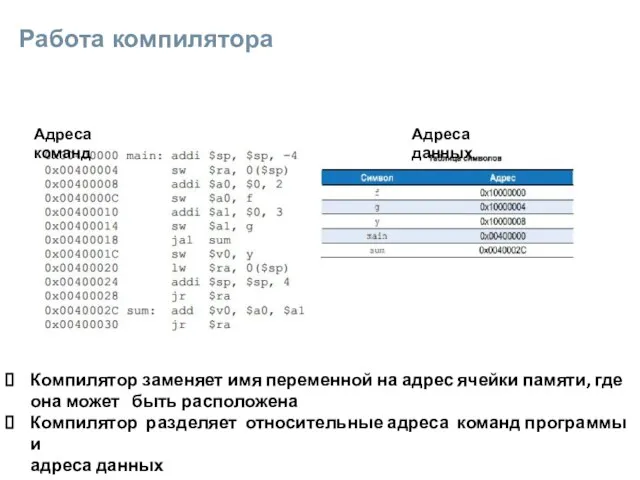

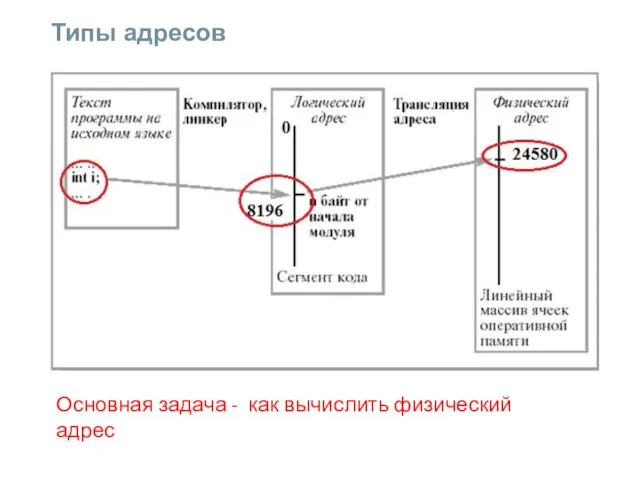

- 98. Работа компилятора Адреса команд Адреса данных Компилятор заменяет имя переменной на адрес ячейки памяти, где она

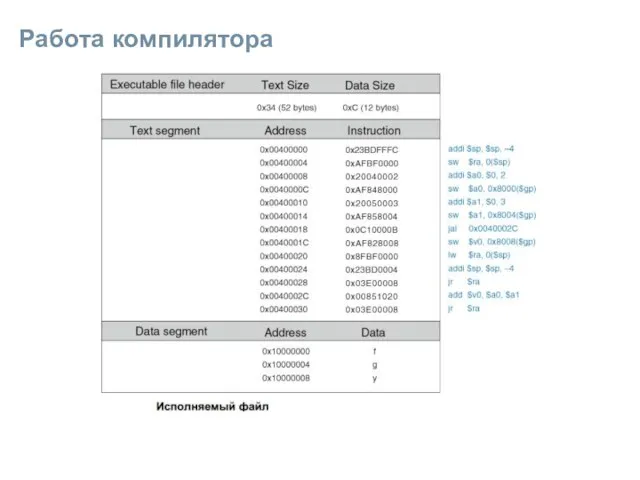

- 99. Работа компилятора

- 100. Типы адресов Основная задача - как вычислить физический адрес

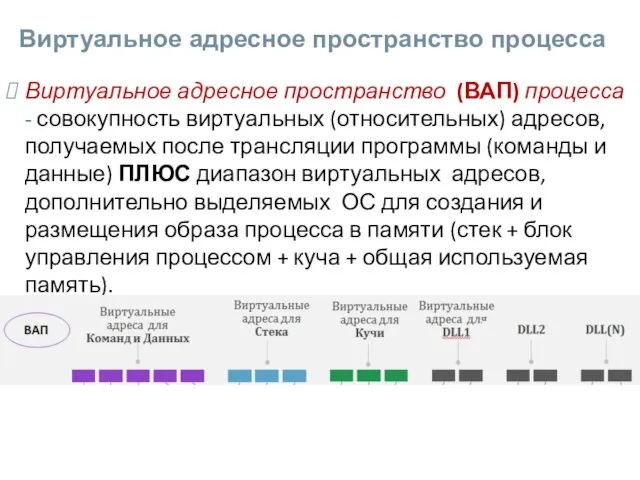

- 101. Виртуальное адресное пространство процесса Виртуальное адресное пространство (ВАП) процесса - совокупность виртуальных (относительных) адресов, получаемых после

- 102. Виртуальное адресное пространство процесса Компоновщик ,при компоновке может пересчитать адреса с учетом подключаемых модулей. У разных

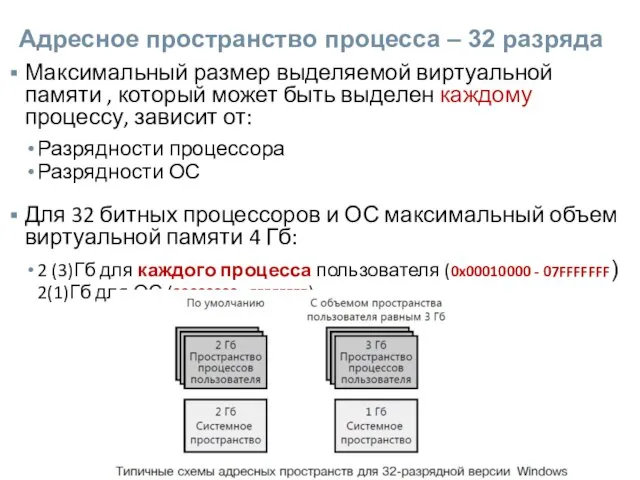

- 103. Адресное пространство процесса – 32 разряда Максимальный размер выделяемой виртуальной памяти , который может быть выделен

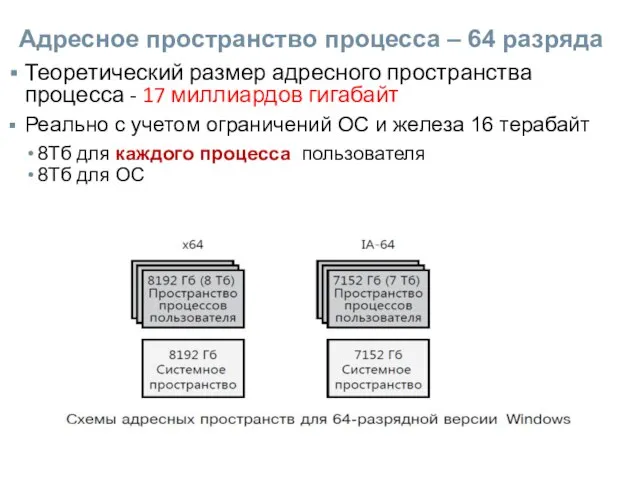

- 104. Адресное пространство процесса – 64 разряда Теоретический размер адресного пространства процесса - 17 миллиардов гигабайт Реально

- 105. Резервирование адресного пространства процесса Происходит в три этапа ОС выделяет (резервирует) для процесса диапазон виртуальных адресов

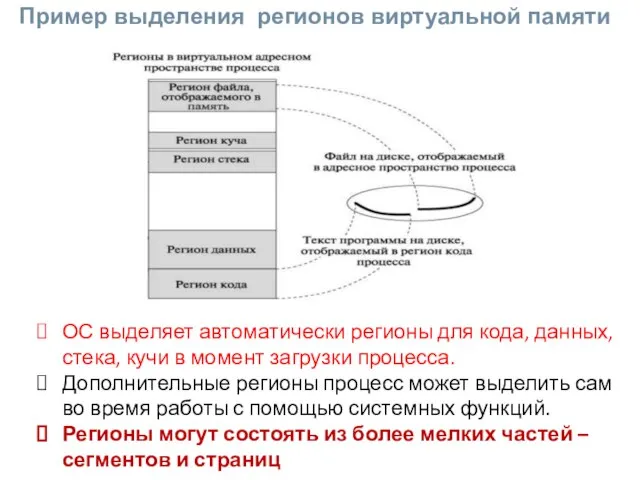

- 106. Пример выделения регионов виртуальной памяти ОС выделяет автоматически регионы для кода, данных, стека, кучи в момент

- 107. Выделение физической памяти процессу Виртуальное адресное пространство (регионы) условно поделено на блоки фиксированного размера, называемые виртуальными

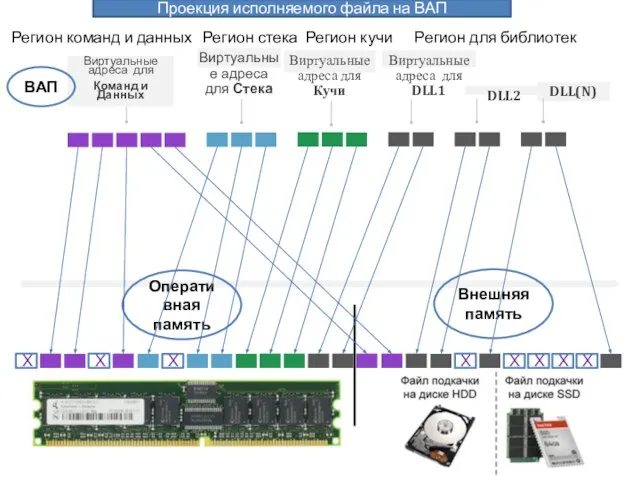

- 108. Виртуальные адреса для Команд и Данных Виртуальные адреса для Стека Виртуальные адреса для Кучи Виртуальные адреса

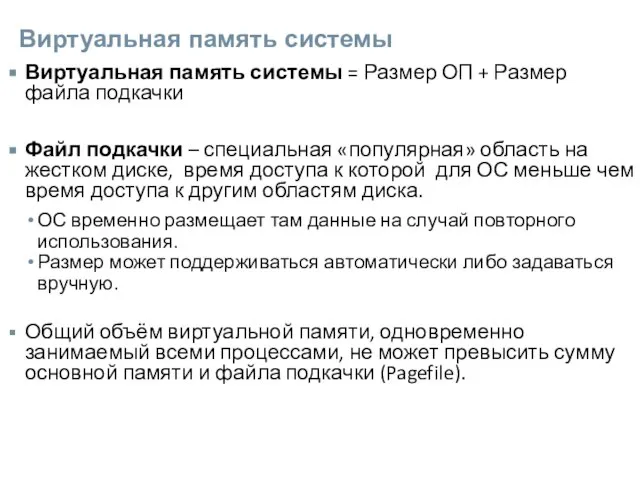

- 109. Виртуальная память системы Виртуальная память системы = Размер ОП + Размер файла подкачки Файл подкачки –

- 110. Преобразование виртуального адреса в физический

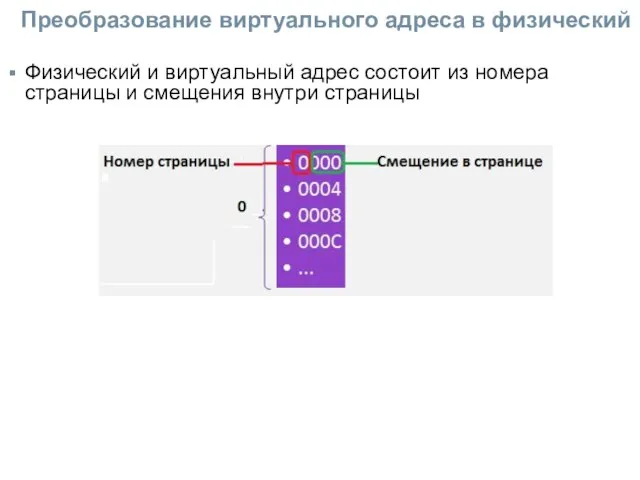

- 111. Преобразование виртуального адреса в физический Физический и виртуальный адрес состоит из номера страницы и смещения внутри

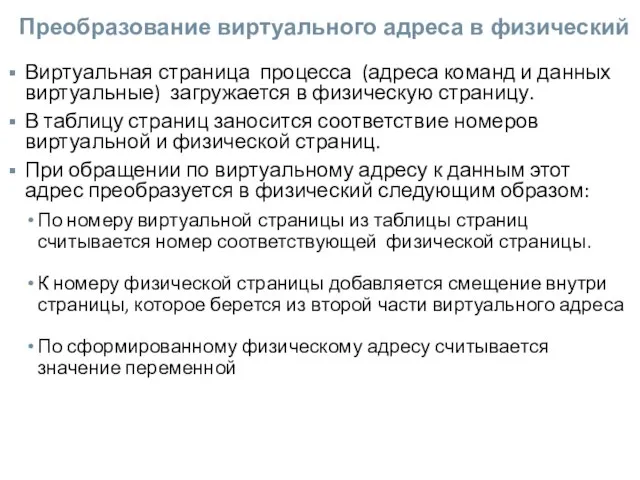

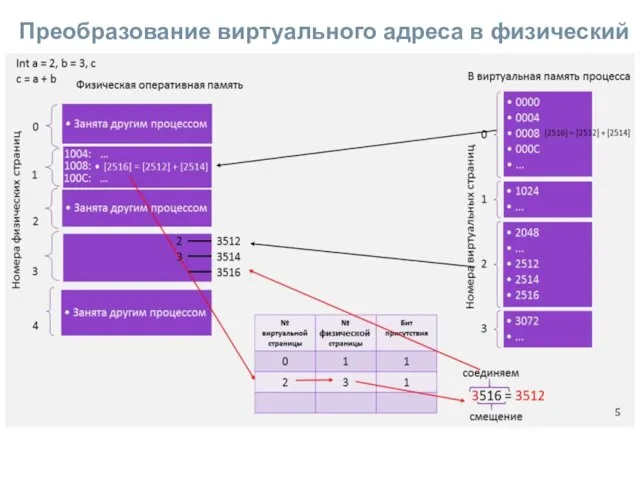

- 112. Преобразование виртуального адреса в физический Виртуальная страница процесса (адреса команд и данных виртуальные) загружается в физическую

- 113. Преобразование виртуального адреса в физический

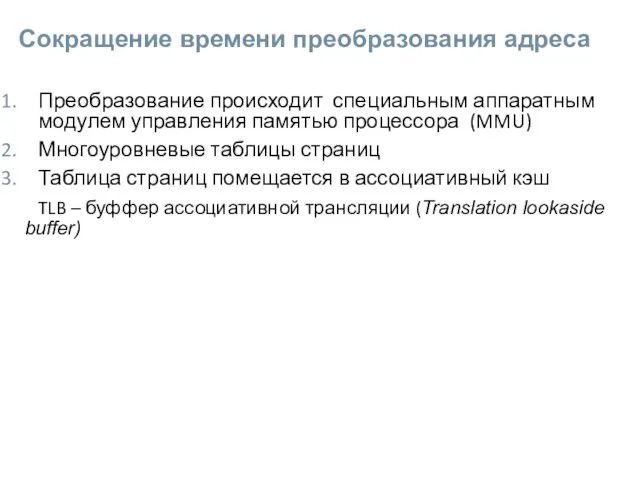

- 114. Сокращение времени преобразования адреса Преобразование происходит специальным аппаратным модулем управления памятью процессора (MMU) Многоуровневые таблицы страниц

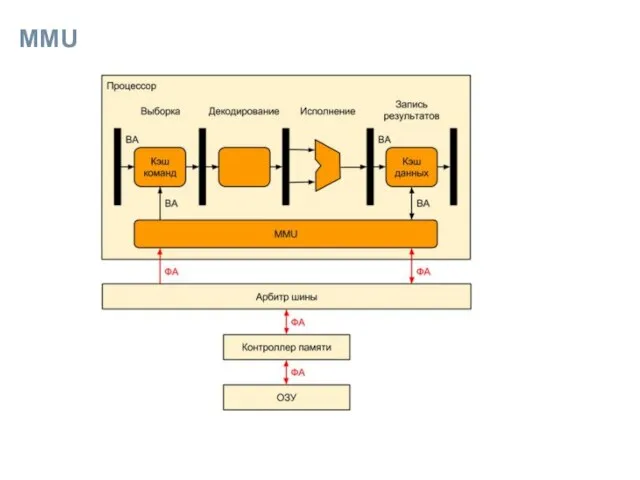

- 115. Во время выполнения программы при каждом обращении к памяти виртуальные адреса не выставляются напрямую на шину

- 116. MMU

- 117. Многоуровневые таблицы страниц

- 119. Скачать презентацию

криволинейной трапеции

криволинейной трапеции 2.2 Основные способы повышения безопасности ЛИА: использование блокирующего сепаратора

2.2 Основные способы повышения безопасности ЛИА: использование блокирующего сепаратора Мастер-класс Рисование пластилином картин

Мастер-класс Рисование пластилином картин МОУ «СОШ № 2 г. Калининска Саратовской области»Аляева Л.Н.19.11.09

МОУ «СОШ № 2 г. Калининска Саратовской области»Аляева Л.Н.19.11.09 Величайшие мастера и мыслители эпохи Высокого Возрождения

Величайшие мастера и мыслители эпохи Высокого Возрождения Математика в жизни семьи

Математика в жизни семьи Южно - Африканская республика. Экономико - географическая характеристика

Южно - Африканская республика. Экономико - географическая характеристика Citius, Altius, Fortius

Citius, Altius, Fortius Кто такие зимующие птицы и перелетные?

Кто такие зимующие птицы и перелетные? Домашние кошки

Домашние кошки ИТ- услугиСквозь призму товарно-денежных отношений

ИТ- услугиСквозь призму товарно-денежных отношений Презентация на тему Скелет человека

Презентация на тему Скелет человека Использование проектов в процессе организации познавательной деятельности детей 4-5 лет

Использование проектов в процессе организации познавательной деятельности детей 4-5 лет Тарифная политика. Условия предоставления тарифов

Тарифная политика. Условия предоставления тарифов Твой новый взгляд на свободу

Твой новый взгляд на свободу Экологический кризис – глобальная проблема современности. На примере техногенных катастроф

Экологический кризис – глобальная проблема современности. На примере техногенных катастроф Организационно-методическое сопровождение уроков физической культуры в условиях низкой пропускной способности спортивного зала

Организационно-методическое сопровождение уроков физической культуры в условиях низкой пропускной способности спортивного зала Предложение о сотрудничестве

Предложение о сотрудничестве Презентация без названия(1)

Презентация без названия(1) Интегрированные коммуникации в сфере агротуризма Составители: Иссерс О.С., Никитина Е.А., Терских М.В., Плотникова О.А., Завальни

Интегрированные коммуникации в сфере агротуризма Составители: Иссерс О.С., Никитина Е.А., Терских М.В., Плотникова О.А., Завальни 50 Любовь Господню описать

50 Любовь Господню описать Правовое государство и гражданское общество. Гражданин

Правовое государство и гражданское общество. Гражданин Экслибрис. Задание по прикладной композиции

Экслибрис. Задание по прикладной композиции Пропорции

Пропорции Презентация на тему Упражнение в написании слов с двойными согласными

Презентация на тему Упражнение в написании слов с двойными согласными  Правоотношения: понятие, состав Выполнили: студенты 2 курса, Т-1202 Шабанов Тагир, Токманова Сандира

Правоотношения: понятие, состав Выполнили: студенты 2 курса, Т-1202 Шабанов Тагир, Токманова Сандира Не курить на АЗК

Не курить на АЗК Михаил Юрьевич Лермонтов 1814-1841

Михаил Юрьевич Лермонтов 1814-1841