Содержание

- 2. Часть III. Управление памятью Лекция 8. Простейшие схемы управления памятью

- 3. Иерархия памяти Вторичная память Оперативная память Кэш Регистры Стоимость одного бита Время доступа Объем Управляется ОС

- 4. Принцип локальности Большинство реальных программ в течение некоторого отрезка времени работает с небольшим набором адресов памяти

- 5. Проблема разрешения адресов Человеку свойственно символическое мышление. Адреса (имена) переменных описываются идентификаторами, формируя символьное адресное пространство

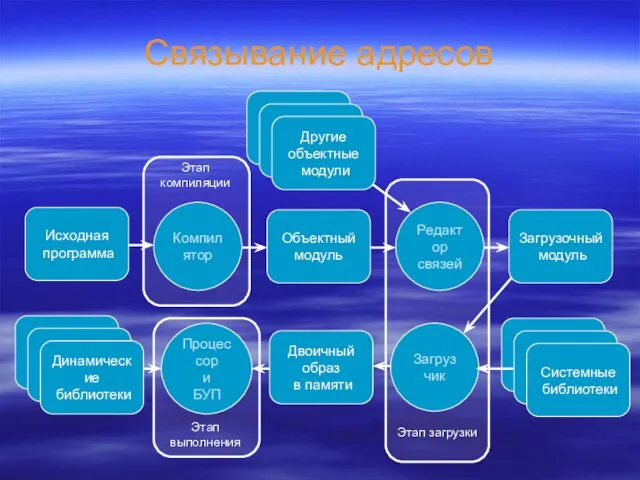

- 6. Связывание адресов Другие объектные модули Загрузчик Двоичный образ в памяти Системные библиотеки Динамические библиотеки Процессор и

- 7. Логическое адресное пространство Символьное адресное пространство – совокупность всех допустимых идентификаторов переменных Логическое адресное пространство –

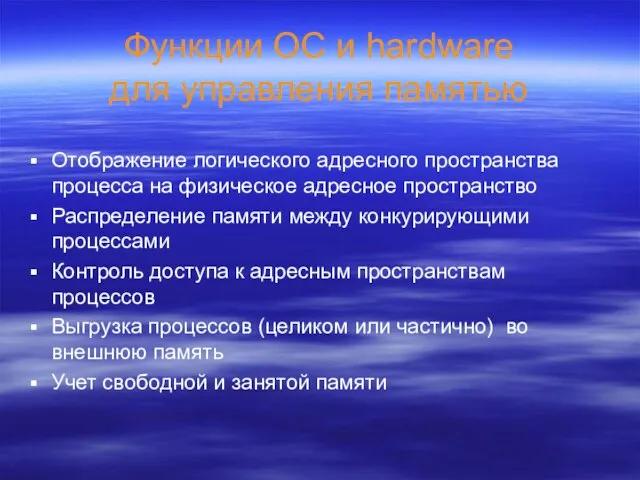

- 8. Функции ОС и hardware для управления памятью Отображение логического адресного пространства процесса на физическое адресное пространство

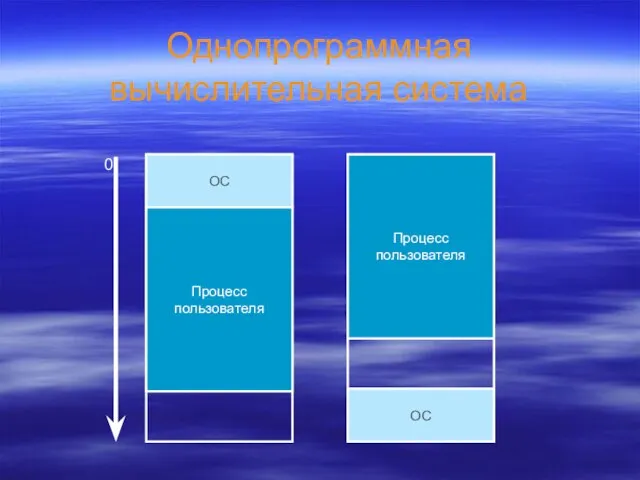

- 9. Однопрограммная вычислительная система ОС ОС 0 Процесс пользователя Процесс пользователя

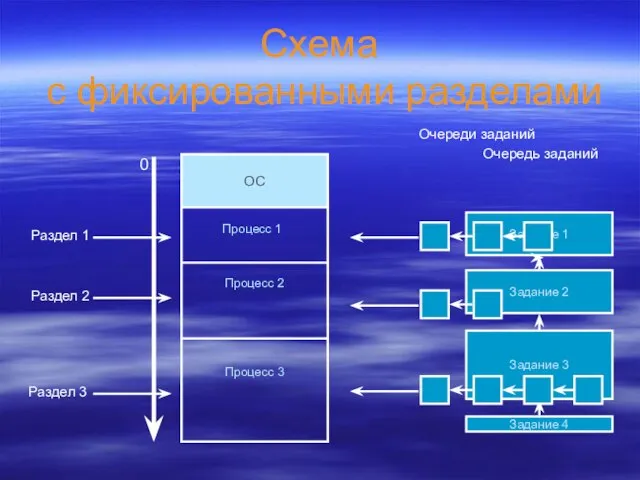

- 10. Схема с фиксированными разделами ОС 0 Раздел 1 Раздел 2 Раздел 3 Задание 1 Задание 2

- 11. Внутренняя фрагментация ОС 0 Раздел 1 Раздел 2 Раздел 3 Процесс 1 Процесс 2 Процесс 3

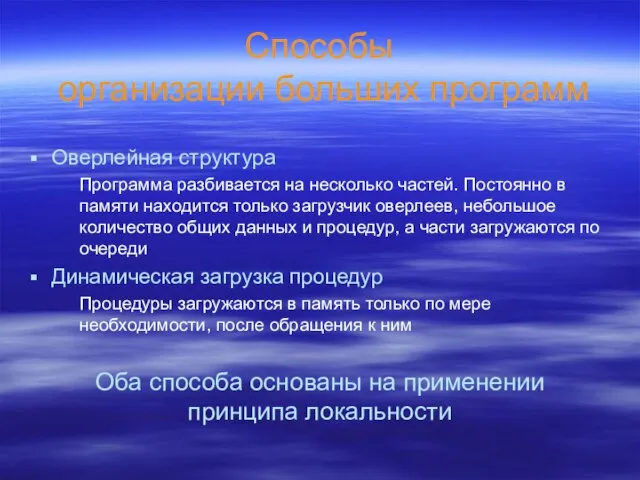

- 12. Способы организации больших программ Оверлейная структура Программа разбивается на несколько частей. Постоянно в памяти находится только

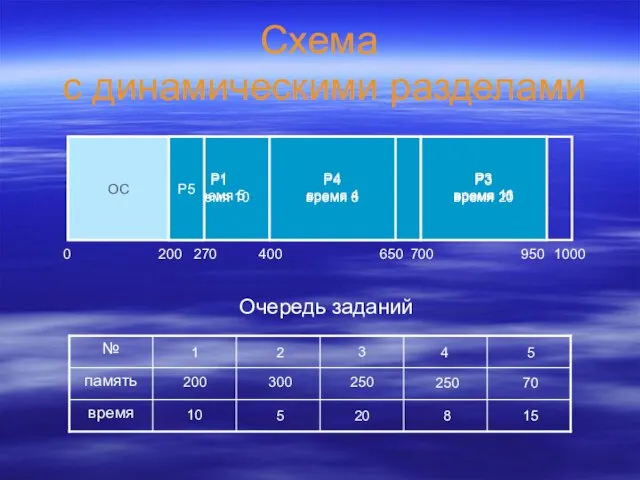

- 13. Схема с динамическими разделами ОС 0 200 1000 Очередь заданий 1 2 3 4 5 200

- 14. Схема с динамическими разделами Стратегии размещения нового процесса в памяти Первый подходящий (first-fit). Процесс размещается в

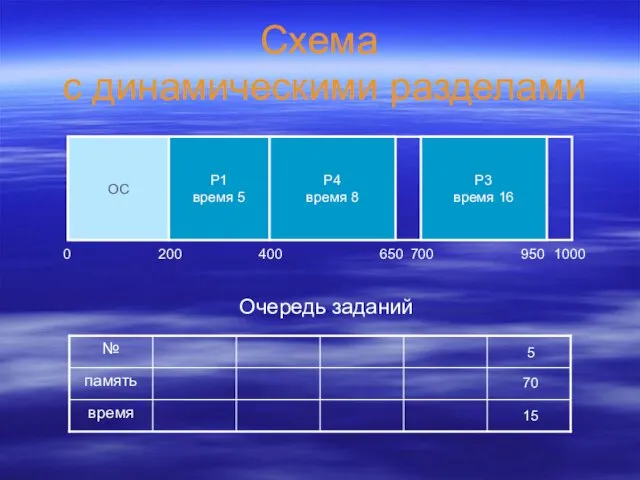

- 15. Схема с динамическими разделами ОС 0 200 1000 Очередь заданий 5 70 15 P1 время 5

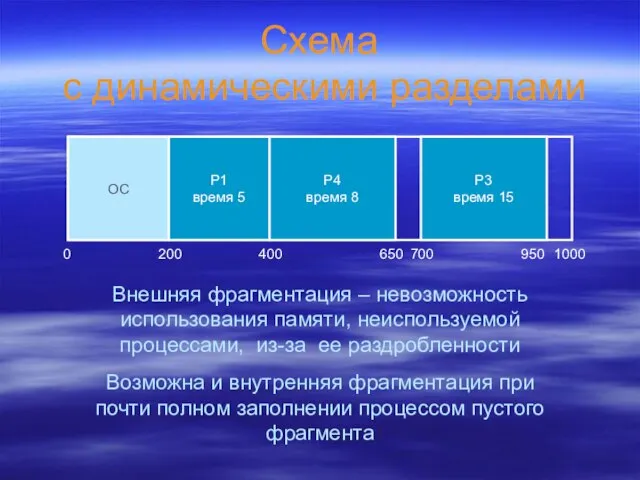

- 16. Схема с динамическими разделами ОС 0 200 1000 P1 время 5 400 700 P3 время 15

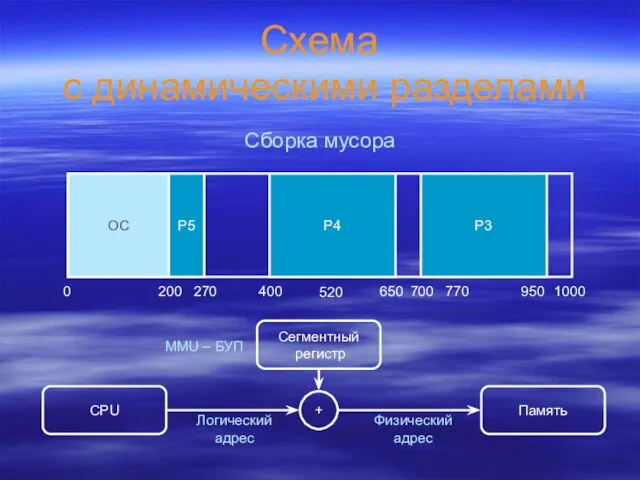

- 17. Схема с динамическими разделами ОС 0 200 1000 400 700 950 P4 650 P5 270 520

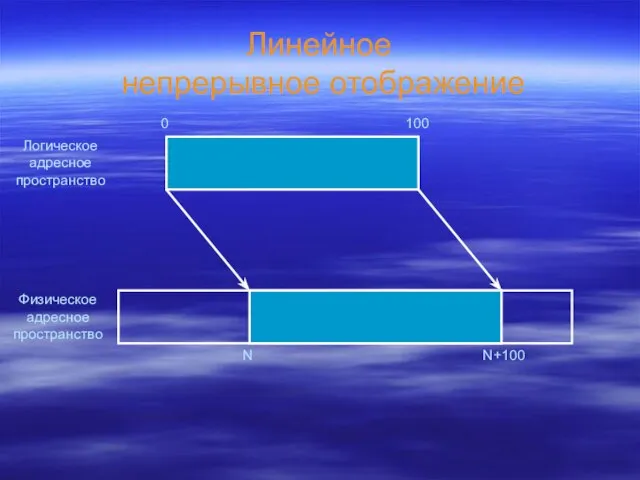

- 18. Линейное непрерывное отображение Логическое адресное пространство Физическое адресное пространство 0 100 N N+100

- 19. Линейное кусочно-непрерывное отображение Логическое адресное пространство Физическое адресное пространство Page 0 Page 1 Page 2 Page

- 20. Линейное кусочно-непрерывное отображение Страничная организация памяти CPU Логический адрес offset page Таблица страниц кадр Память Физический

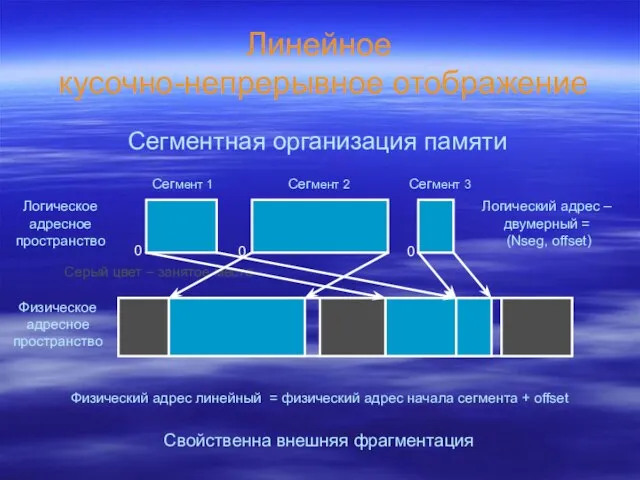

- 21. Линейное кусочно-непрерывное отображение Логическое адресное пространство Физическое адресное пространство Логический адрес – двумерный = (Nseg, offset)

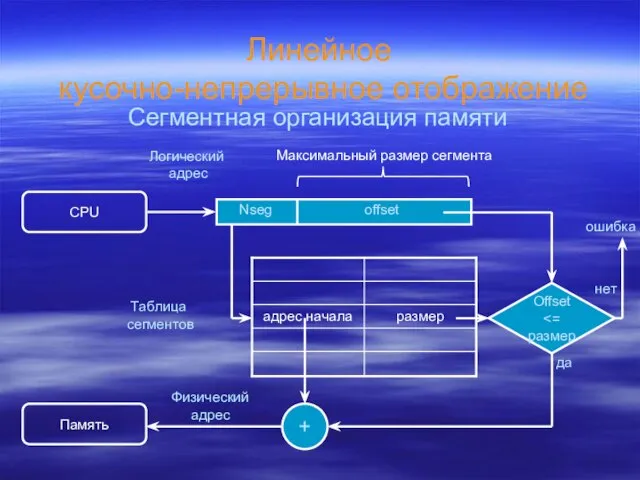

- 22. Линейное кусочно-непрерывное отображение Сегментная организация памяти CPU Логический адрес offset Nseg Таблица сегментов Память Физический адрес

- 23. Линейное кусочно-непрерывное отображение Сегментная организация памяти CPU Логический адрес offset Nseg Таблица сегментов Память Физический адрес

- 25. Скачать презентацию

Разработка информационной системы “Авиаучасток” для службы обеспечения авиаперевозок ОАО “Томскнефть” ВНК

Разработка информационной системы “Авиаучасток” для службы обеспечения авиаперевозок ОАО “Томскнефть” ВНК Анализ заявок и программ развития школ

Анализ заявок и программ развития школ Разработка способа и устройства для испепеления неугодных в крупных масштабах

Разработка способа и устройства для испепеления неугодных в крупных масштабах открытый урок 15 ноября

открытый урок 15 ноября Религиозные верования и традиции древних египтян

Религиозные верования и традиции древних египтян Датчики

Датчики Стратегия дистрибуции компании Rolsen: управляемость, стабильность, эффективность.

Стратегия дистрибуции компании Rolsen: управляемость, стабильность, эффективность. ЦЕНТР ОБРАЗОВАНИЯ №2045

ЦЕНТР ОБРАЗОВАНИЯ №2045 Искусство Фландрии

Искусство Фландрии Семья и школа как партнеры

Семья и школа как партнеры ВНИМАНИЕ !!!!

ВНИМАНИЕ !!!! История создания ИНКОТЕРМС и применение ИНКОТЕРМС в контракте купли-продажи Сударкина Анастасия, ДС.01

История создания ИНКОТЕРМС и применение ИНКОТЕРМС в контракте купли-продажи Сударкина Анастасия, ДС.01 Назначение ПТЭ. Общие обязанности работников железнодорожного транспорта

Назначение ПТЭ. Общие обязанности работников железнодорожного транспорта 14 Марта день рек

14 Марта день рек Storony_v_grazhdanskom_protsesse

Storony_v_grazhdanskom_protsesse 28 января – Международный день защиты персональных данных

28 января – Международный день защиты персональных данных Система диспетчеризации Plant Visor

Система диспетчеризации Plant Visor Insurance of International Trade Risks

Insurance of International Trade Risks  Открытая лига мини-футбола г. Вологды

Открытая лига мини-футбола г. Вологды История создания фартука

История создания фартука Антигитлеровская коалиция и итоги Второй мировой войны

Антигитлеровская коалиция и итоги Второй мировой войны "Учиться надо весело, чтоб хорошо учиться…"

"Учиться надо весело, чтоб хорошо учиться…" Кодекс ГТС. Принципи взаємодії з прямим споживачем

Кодекс ГТС. Принципи взаємодії з прямим споживачем С юбилеем! 55 лет

С юбилеем! 55 лет Saint Valentine’s day

Saint Valentine’s day Невидимый мир. Тема 3

Невидимый мир. Тема 3 Аварийные конструкции зданий

Аварийные конструкции зданий Имя существительное: кто? что?

Имя существительное: кто? что?