Содержание

- 2. Ивченко В.Г. Применение языка VHDL при проектировании специализированных СБИС: Учебное пособие. Таганрог: Изд-во ТРТУ, 1999. –80

- 3. Интегральная схема (микросхема) – законченное микроэлектронное изделие, выполняющее определенные функции обработки информации (сигналов), все интегральные элементы

- 4. Способы реализации специализированных сверхбольших интегральных схем (СБИС): - полностью заказные, предполагающие полный цикл проектирования на уровне

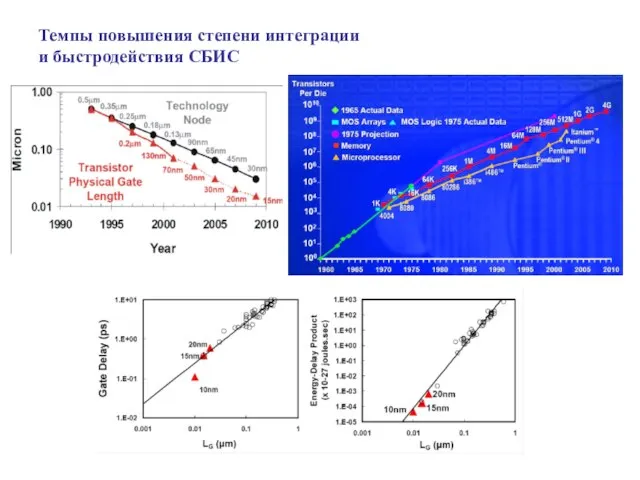

- 5. Темпы повышения степени интеграции и быстродействия СБИС

- 6. В «Концепции развития в Российской Федерации работ в области нанотехнологий на период до 2010 года», одобренной

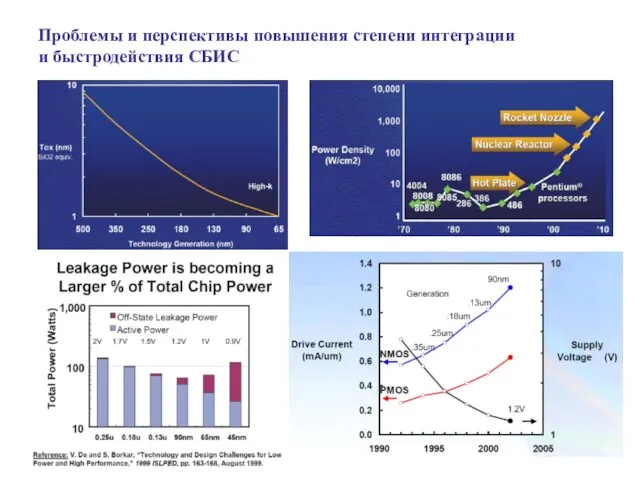

- 7. Проблемы и перспективы повышения степени интеграции и быстродействия СБИС

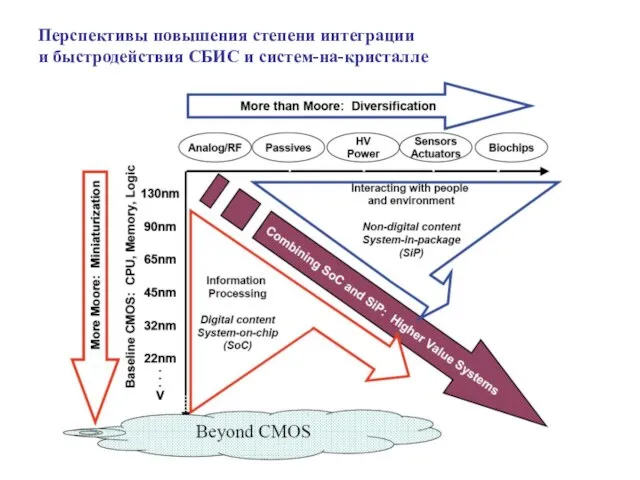

- 8. Перспективы повышения степени интеграции и быстродействия СБИС и систем-на-кристалле

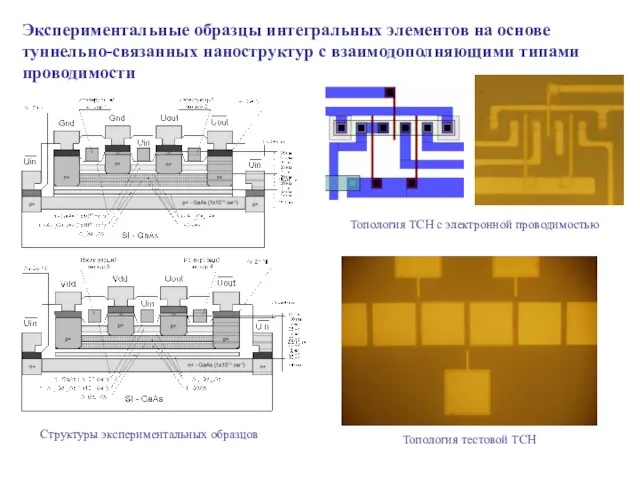

- 9. Экспериментальные образцы интегральных элементов на основе туннельно-связанных наноструктур с взаимодополняющими типами проводимости Структуры экспериментальных образцов Топология

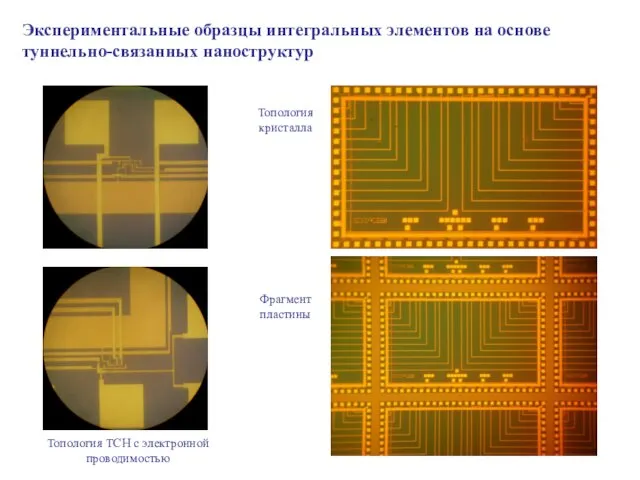

- 10. Экспериментальные образцы интегральных элементов на основе туннельно-связанных наноструктур Топология кристалла Фрагмент пластины Топология ТСН с электронной

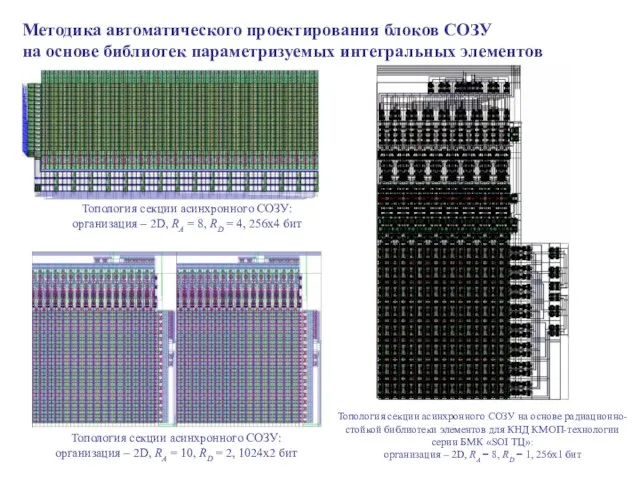

- 11. Методика автоматического проектирования блоков СОЗУ на основе библиотек параметризуемых интегральных элементов Топология секции асинхронного СОЗУ: организация

- 12. Виды обеспечений систем автоматизи-рованного проектирования (САПР): - информационное – совокупность информационных ресурсов, необходимых для автоматизированного проектирования;

- 13. Язык описания проекта СБИС – формальная запись, предназначенная для описания функции, логической организации и (или) структурной

- 14. Модули VHDL-описаний: - объявление объекта проекта (entity) – описание интерфейса объекта проекта (входных/выходных сигналов и параметров

- 15. Библиотеки VHDL (library): - рабочая библиотека (библиотека проекта) – совокупность файлов VHDL-описаний, находящихся в каталоге проекта;

- 16. Стили описаний архитектурного тела: - поведенческий – описание функции объекта проекта; - потоковый – описание логической

- 17. Описание параллельных потоков обработки данных в VHDL Процесс (process) – содержит набор операторов, выполняемых последовательно во

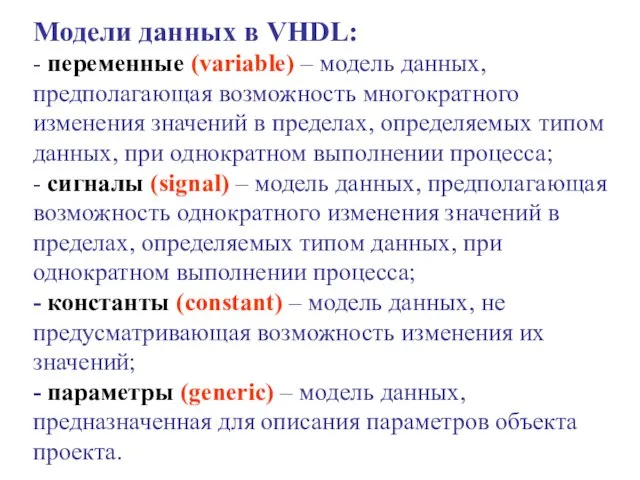

- 18. Модели данных в VHDL: - переменные (variable) – модель данных, предполагающая возможность многократного изменения значений в

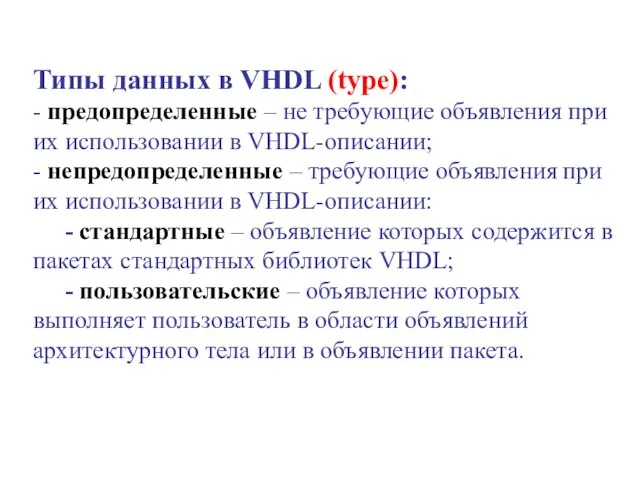

- 19. Типы данных в VHDL (type): - предопределенные – не требующие объявления при их использовании в VHDL-описании;

- 20. Примеры типов данных в VHDL: - предопределенные: целочисленные десятичные – integer, positive (25; -78); двоичные –

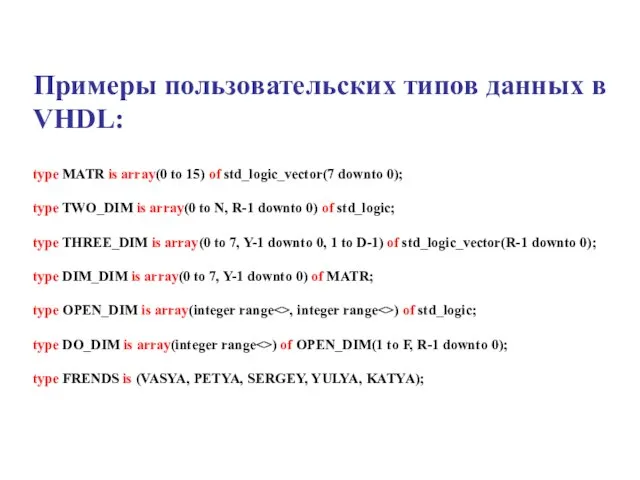

- 21. Примеры пользовательских типов данных в VHDL: type MATR is array(0 to 15) of std_logic_vector(7 downto 0);

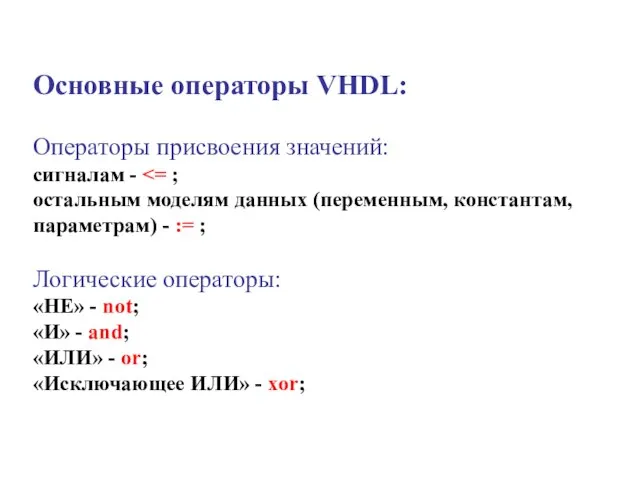

- 22. Основные операторы VHDL: Операторы присвоения значений: сигналам - остальным моделям данных (переменным, константам, параметрам) - :=

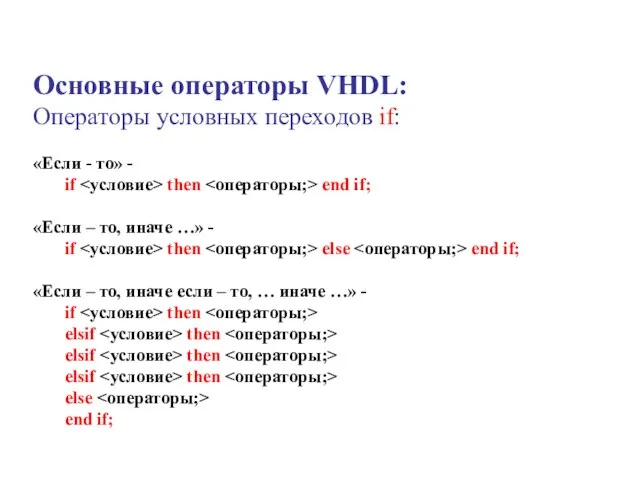

- 23. Основные операторы VHDL: Операторы условных переходов if: «Если - то» - if then end if; «Если

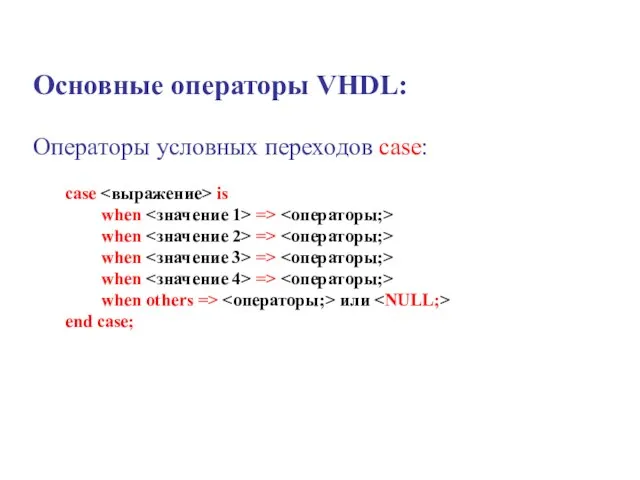

- 24. Основные операторы VHDL: Операторы условных переходов case: case is when => when => when => when

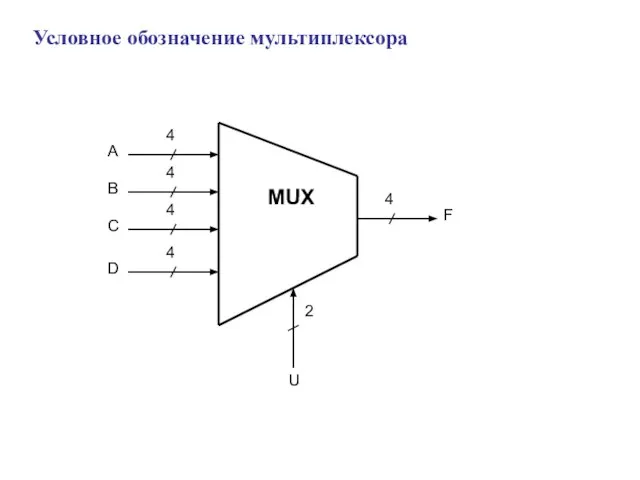

- 25. Условное обозначение мультиплексора MUX 4 2 A B C D U F 4 4 4 4

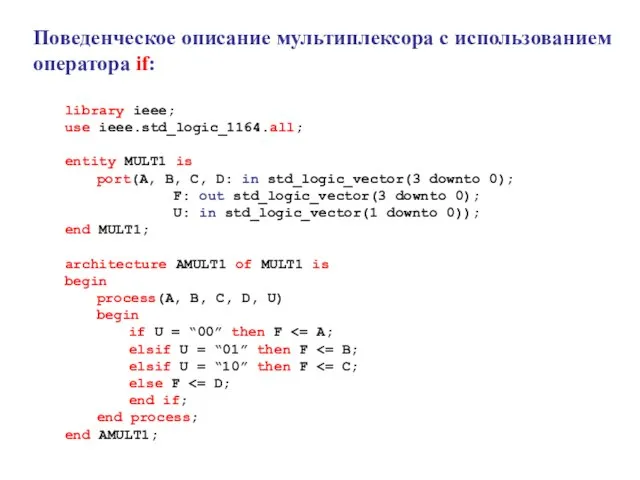

- 26. Поведенческое описание мультиплексора с использованием оператора if: library ieee; use ieee.std_logic_1164.all; entity MULT1 is port(A, B,

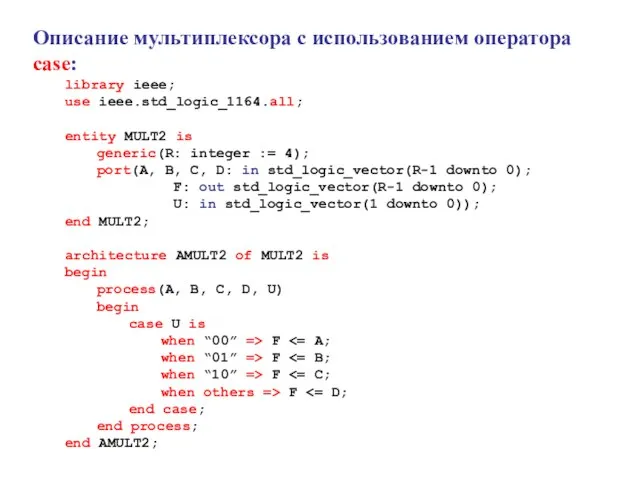

- 27. Описание мультиплексора с использованием оператора case: library ieee; use ieee.std_logic_1164.all; entity MULT2 is generic(R: integer :=

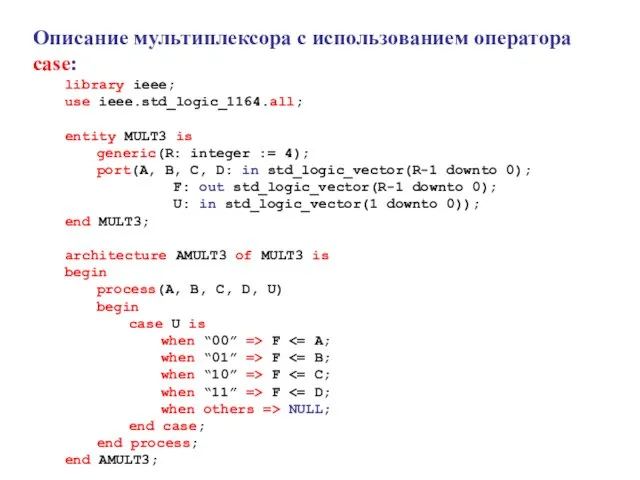

- 28. Описание мультиплексора с использованием оператора case: library ieee; use ieee.std_logic_1164.all; entity MULT3 is generic(R: integer :=

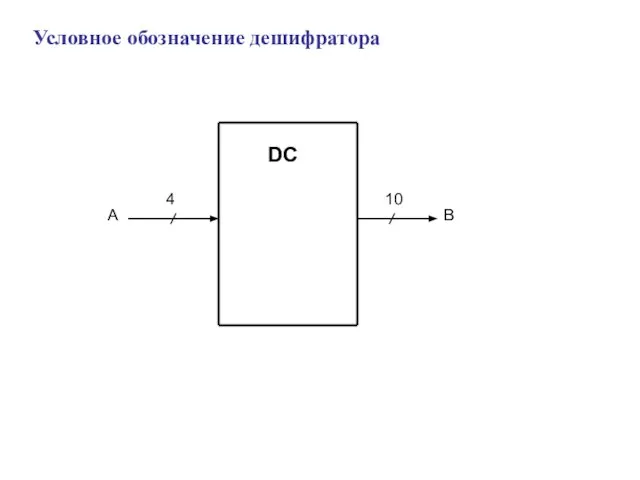

- 29. Условное обозначение дешифратора DC 4 A B 10

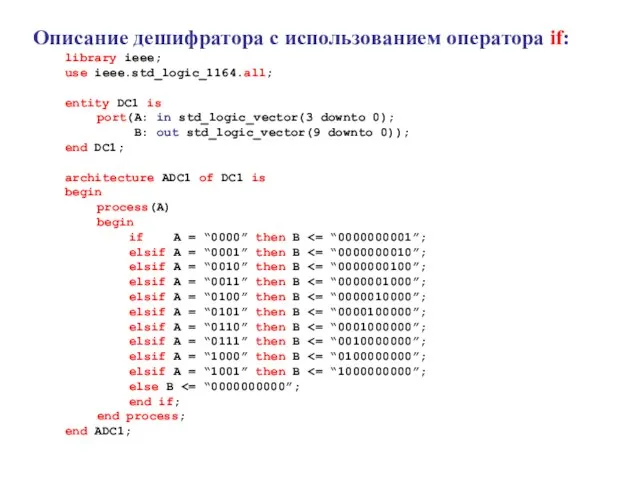

- 30. Описание дешифратора с использованием оператора if: library ieee; use ieee.std_logic_1164.all; entity DC1 is port(A: in std_logic_vector(3

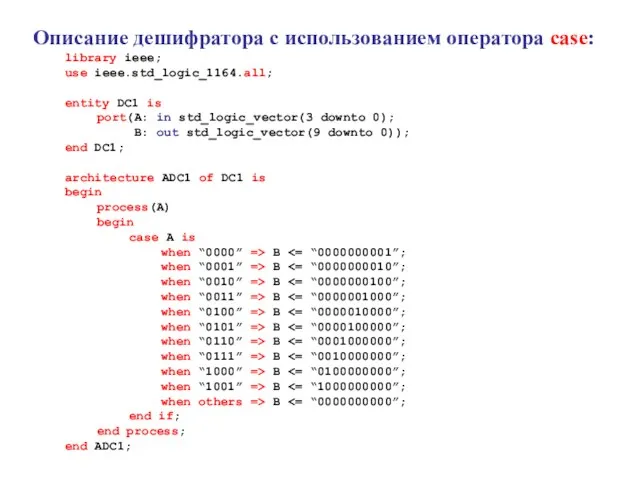

- 31. Описание дешифратора с использованием оператора case: library ieee; use ieee.std_logic_1164.all; entity DC1 is port(A: in std_logic_vector(3

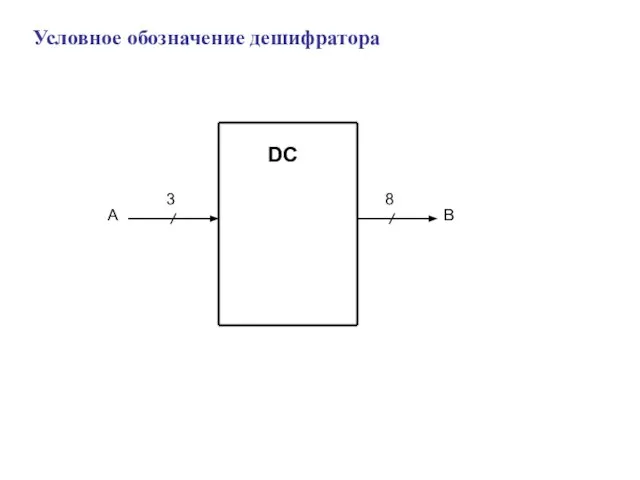

- 32. Условное обозначение дешифратора DC 3 A B 8

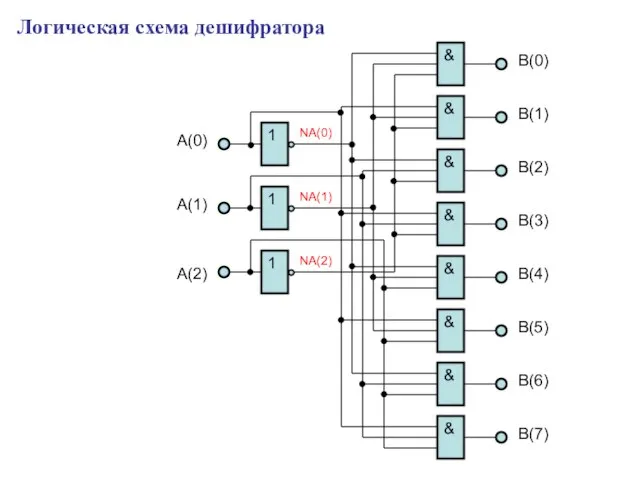

- 33. Логическая схема дешифратора & & & & & & & & 1 1 1 A(0) A(1)

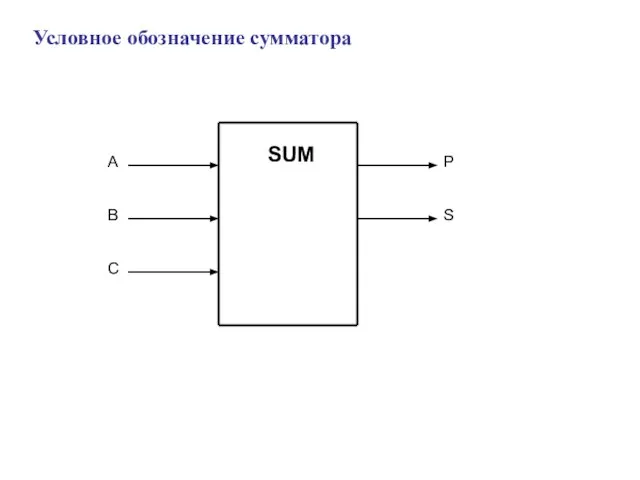

- 34. Условное обозначение сумматора SUM B S A C P

- 35. Таблица истинности сумматора

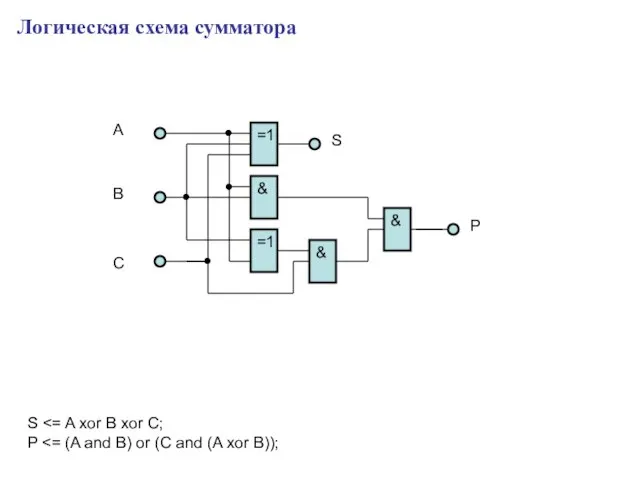

- 36. Логическая схема сумматора =1 & A B C S P S P =1 & &

- 37. Система автоматизированного проектирования специализированных СБИС FPGA Advantage Mentor Graphics

- 38. Одним из основных отличий языков описания аппаратуры и, в частности, VHDL от традиционных языков программирования (Паскаль,

- 39. Общая организация САПР FPGA ADVANTAGE САПР FPGA Advantage Mentor Graphics предназначена для автоматизированного проектирования СБИC с

- 40. Подсистема Renoir Renoir - подсистема синтеза, генерации и верификации VHDL/Verilog-описаний проекта, содержащая: текстовый редактор; синтаксический анализатор;

- 41. Подсистема ModelSim ModelSim - подсистема функционально-логического моделирования проекта, в том числе с учетом задержек в элементах

- 42. Подсистема Leonardo Spectrum Leonardo Spectrum - компилятор VHDL/Verilog-описаний проектов СБИС в стандартные форматы описания структуры (файлы

- 43. Пример проектирования конечного автомата в САПР FPGA Advantage Конечный автомат (КА, FSM) – это последовательностное устройство,

- 44. Пример проектирования конечного автомата в САПР FPGA Advantage

- 45. Синтез VHDL-описаний проектов СБИС в подсистеме Renoir Запуск системы. Оболочка Design Browser После запуска системы FPGA

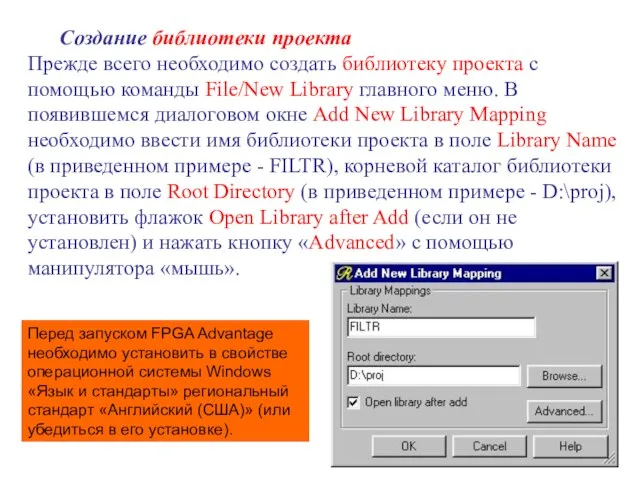

- 47. Создание библиотеки проекта Прежде всего необходимо создать библиотеку проекта с помощью команды File/New Library главного меню.

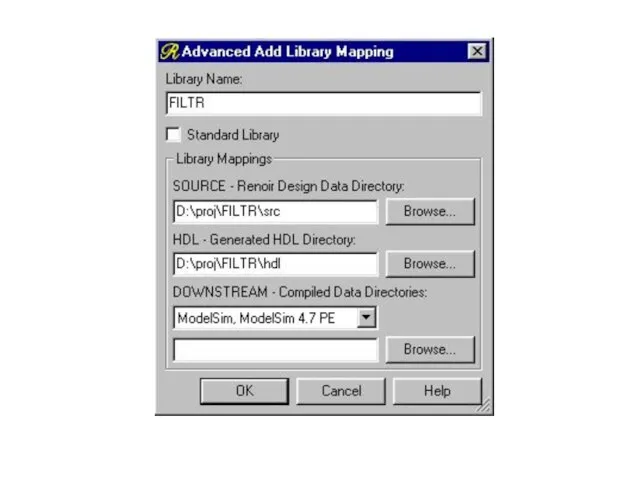

- 48. После активизации кнопки «Advanced» на экране появится окно Advanced Add Library Mapping, в котором будут автоматически

- 50. Открытие библиотеки проекта Для того, чтобы открыть вновь созданную (или ранее созданную) библиотеку проекта, необходимо воспользоваться

- 51. Создание файлов проекта в подсистеме Renoir После того, как библиотека проекта создана и открыта, можно приступать

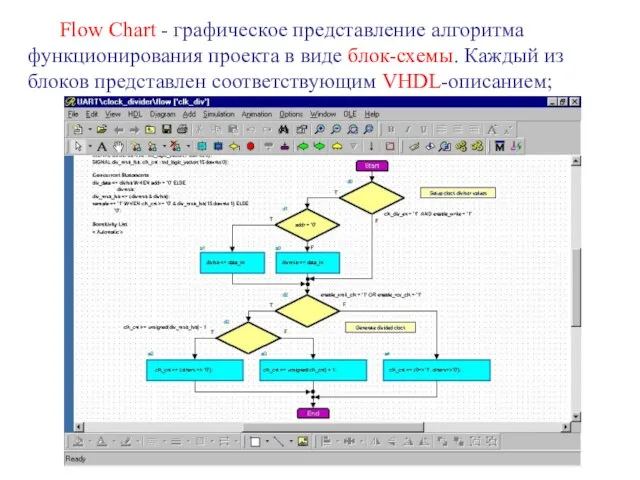

- 53. Flow Chart - графическое представление алгоритма функционирования проекта в виде блок-схемы. Каждый из блоков представлен соответствующим

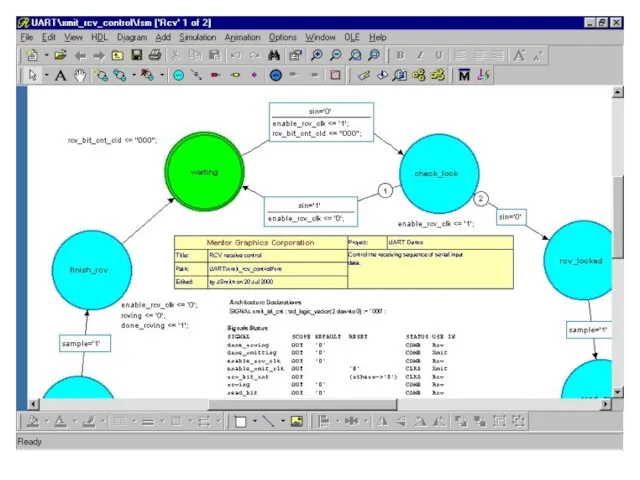

- 54. State Diagram - представление конечных автоматов - функциональное представление в виде направленного графа, вершины которого (круги)

- 56. Эти условия и функции представлены VHDL-описаниями, помещенными в прямоугольники, относящимися к соответствующим ребрам. Очередность проверки условий

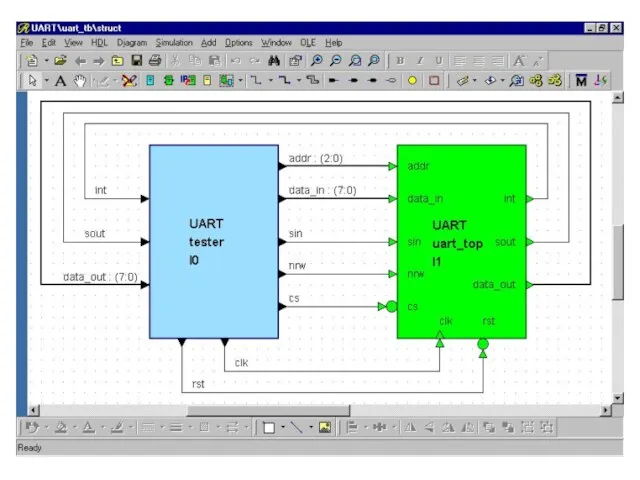

- 57. Symbol - создание условного графического обозначения компонента проекта. При активизации данной команды появляется окно редактора с

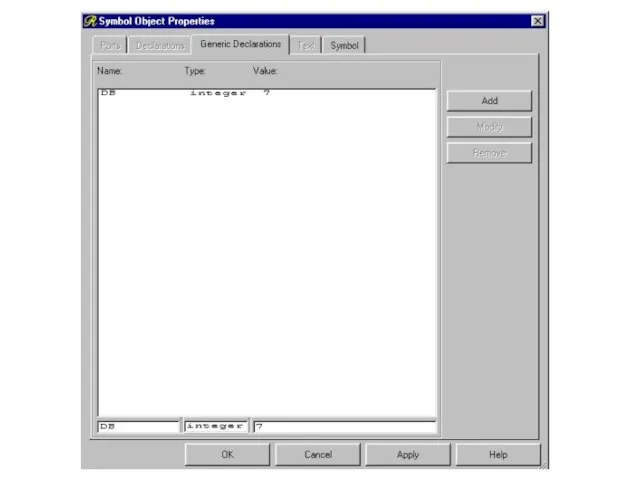

- 58. Если необходимо ввести параметры данного компонента (generic), необходимо навести курсор «мыши» на УГО, щелкнуть правой кнопкой

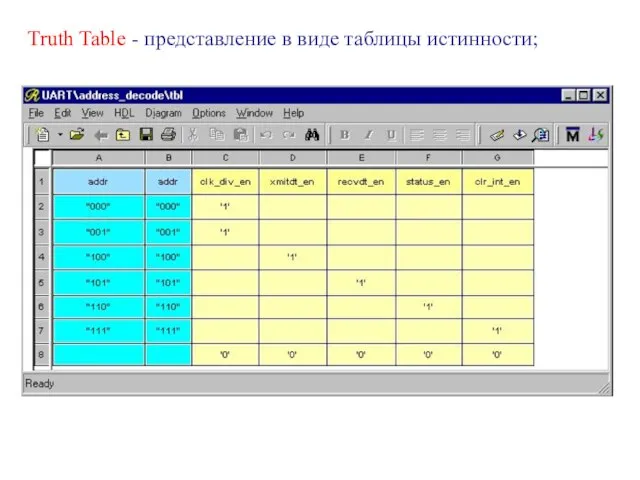

- 60. Truth Table - представление в виде таблицы истинности;

- 61. Verilog Include, Verilog Module - описания на языке Verilog; VHDL Architecture/Entity - VHDL-описание, включающее два обязательных

- 62. VHDL Package Body - VHDL-описание тела пакета; VHDL Package Header - объявление пакета. Файл верхнего уровня

- 63. Add/Block - добавление элемента структурной схемы, называемого «Блок», выполняющего определенную функцию обработки или хранения информации, которая

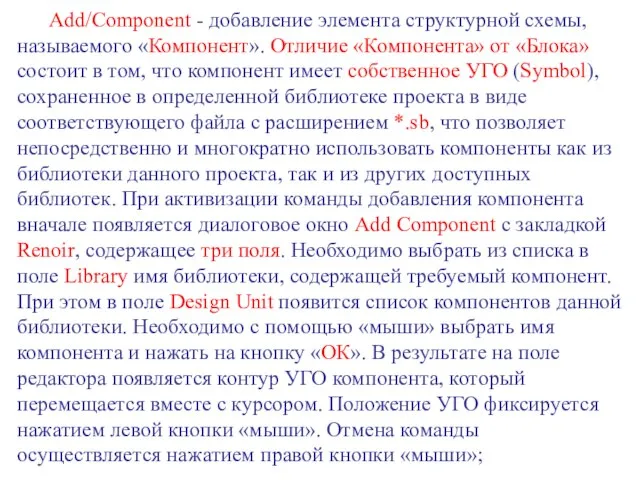

- 64. Add/Component - добавление элемента структурной схемы, называемого «Компонент». Отличие «Компонента» от «Блока» состоит в том, что

- 66. Add/Embedded Block - добавление так называемого встроенного блока, который не может быть самостоятельной единицей проекта, так

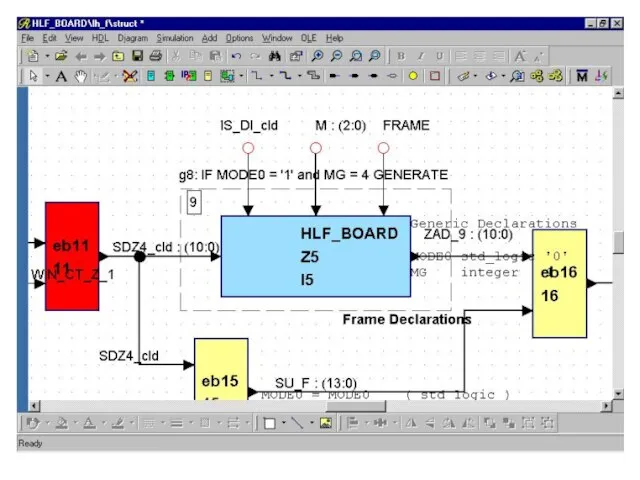

- 67. Add/Frame - добавление рамки условного синтеза. Если в проекте предусмотрены параметры (Generic), отдельные объекты структурной схемы

- 69. Add/Signal - добавление сигнала. После активизации данной команды следует навести курсор «мыши» в точку начала сигнальной

- 70. Add/Bus - добавление шины (нескольких сигналов, имеющих общее имя с соответствующей индексацией). Все необходимые действия аналогичны

- 71. Add/Global Connector - добавление глобального сигнала (объявленного и используемого во всех блоках проекта, например, тактового сигнала).

- 72. При описании проекта в виде конечного автомата (команда File/New/State Diagram) на экране монитора появляется окно редактора

- 73. Add/Hierarchical State - добавление иерархического состояния, содержимое которого определяется вложенной диаграммой состояний; Add/Entry Point - добавление

- 74. При описании проекта в виде таблицы истинности (команда File/New/Truth Table) на экране монитора появляется окно редактора

- 75. Описание содержимого каждого из введенных элементов структурной схемы проекта может, в свою очередь, быть выполнено любым

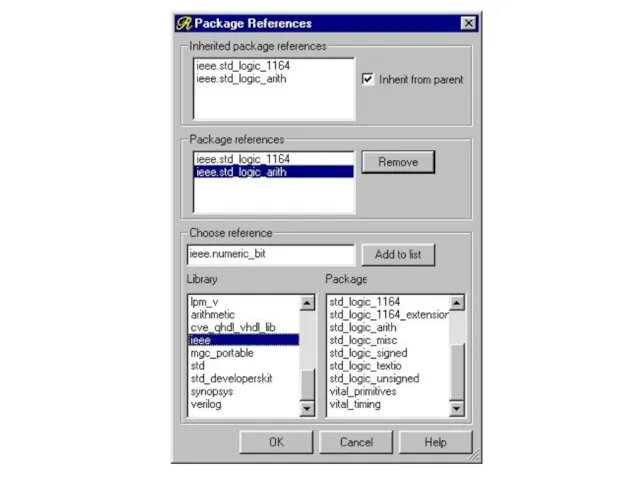

- 76. Подключение библиотек ресурсов в подсистеме Renoir Помимо рабочей библиотеки, в которой размещаются все файлы проекта, VHDL

- 78. В верхнем поле Inherent Package References отображается список пакетов, «унаследованных» от объектов верхних уровней иерархии. Наследование

- 79. Генерация файлов VHDL-описаний в подсистеме Renoir Следует отметить, что каким бы из вышеперечисленных способов не было

- 80. При успешном выполнении генерации, т.е. при отсутствии грамматических и синтаксических ошибок, правильном с точки зрения стандарта

- 81. КОМПИЛЯЦИЯ VHDL-ОПИСАНИЙ В ПОДСИСТЕМЕ RENOIR После успешного завершения генерации VHDL-файлов необходимо устранить все ошибки, связанные не

- 82. Компиляция VHDL-описаний осуществляется с помощью следующих команд: HDL/Compile/Single Level - компиляция VHDL-файла только текущего уровня описания

- 83. СИНТЕЗ ФАЙЛОВ ТОПОЛОГИИ Синтез топологии проектируемой СБИС осуществляется в отдельной САПР, выбираемой в зависимости от метода

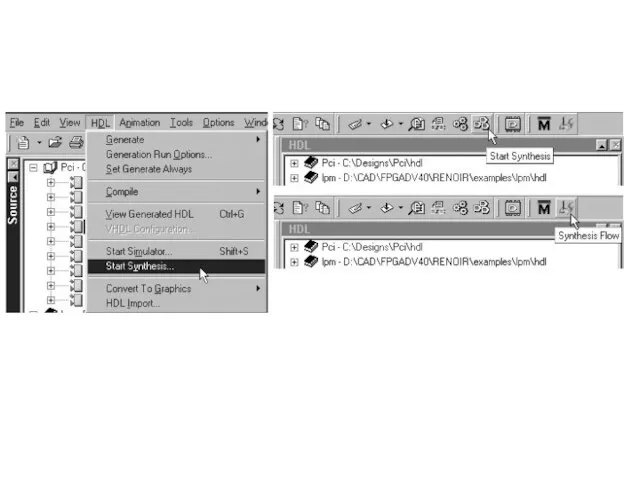

- 84. Запуск системы логического синтеза Leonardo Spectrum и передача в качестве исходного задания высокоуровневого VHDL-описания выполняется из

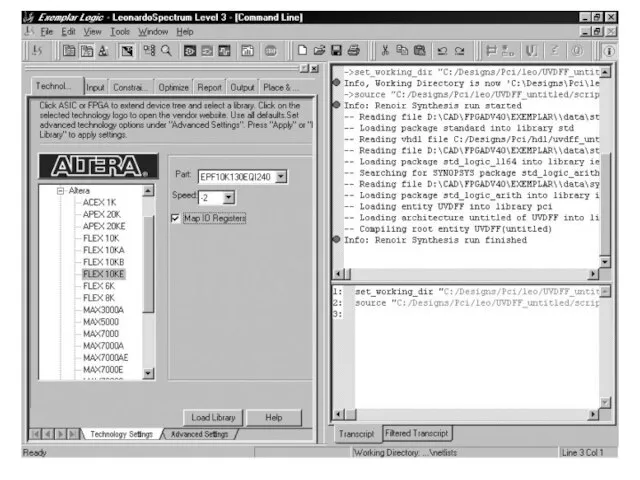

- 86. При этом происходит передача всех файлов, составляющих проект. Появляется окно, позволяющее настроить параметры запуска Leonardo. Как

- 89. Система Leonardo поставляется с набором готовых библиотек элементов, предназначенных для реализации в рамках конкретной целевой технологии.

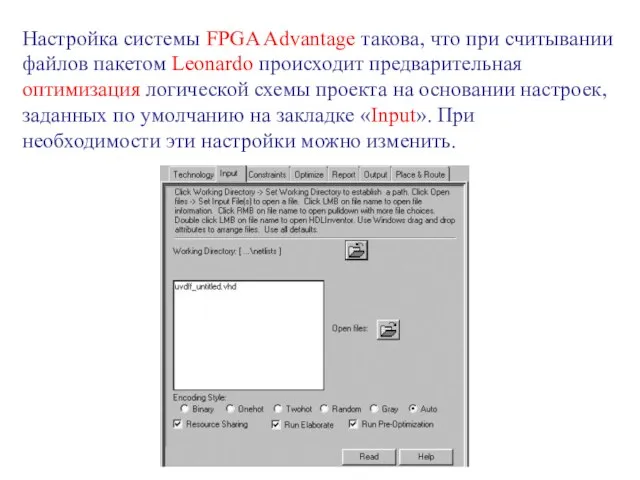

- 90. Настройка системы FPGA Advantage такова, что при считывании файлов пакетом Leonardo происходит предварительная оптимизация логической схемы

- 91. Выбор организации кодирования состояния конечных автоматов выбирается в поле Encoding Style. Стиль Binary обеспечивает обычный для

- 92. Стили Twohot и Random являются разновидностями рассмотренных. Стиль Gray аналогичен Binary, однако использует для кодирования код

- 93. Отметка свойства Resource Sharing обеспечивает сокращение расходуемых аппаратных ресурсов за счет их совместного использования в разных

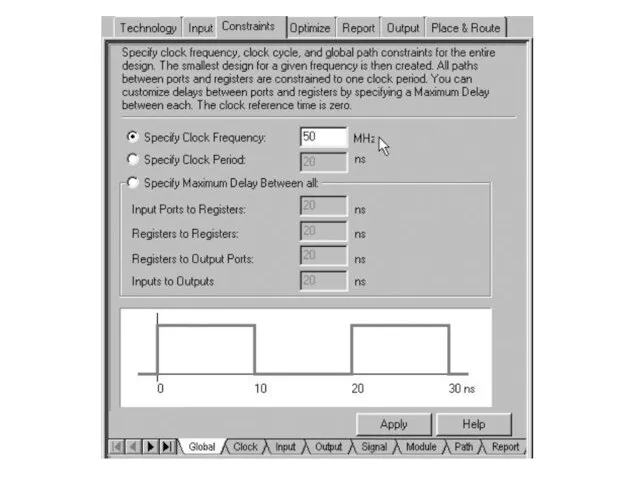

- 94. На следующей закладке «Constraints» имеется возможность задать основные требования к результатам синтеза схемы устройства в определенном

- 96. Если в схеме имеется несколько синхронизирующих сигналов, временные требования к каждому из них можно специфицировать на

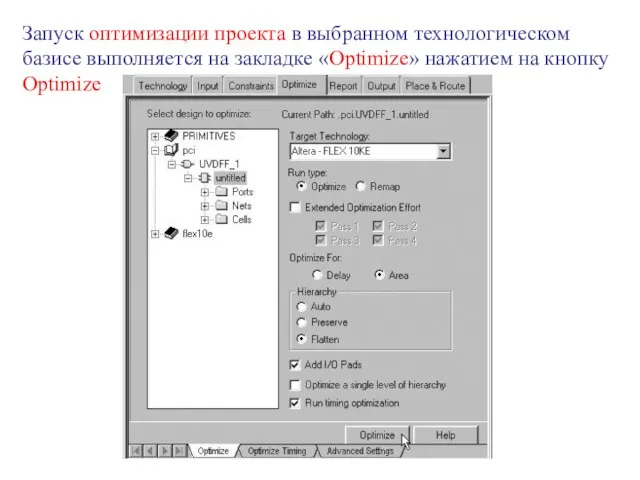

- 97. Запуск оптимизации проекта в выбранном технологическом базисе выполняется на закладке «Optimize» нажатием на кнопку Optimize

- 98. Если необходимо выполнить только переложение схемы в библиотечные элементы технологического базиса, в поле Run type выбирается

- 99. Поле Add I/O Pads позволяет включить в схему буферные библиотечные элементы, подключаемые к контактным площадкам. Это

- 101. Скачать презентацию

Денежные переводы физических лиц: состояние и тенденции развития (на примере ПАО Сбербанк)

Денежные переводы физических лиц: состояние и тенденции развития (на примере ПАО Сбербанк) Особенности истории информатики

Особенности истории информатики Мотивирование топ-менеджеров в банковской сфере: подходы и инструменты

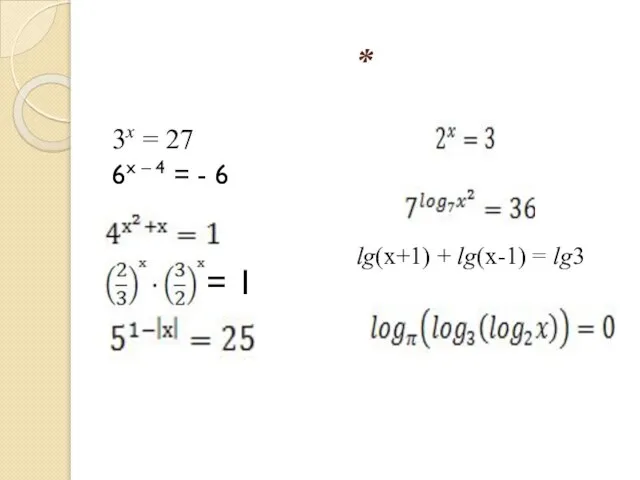

Мотивирование топ-менеджеров в банковской сфере: подходы и инструменты = 1

= 1 Изустная среда мордовского села

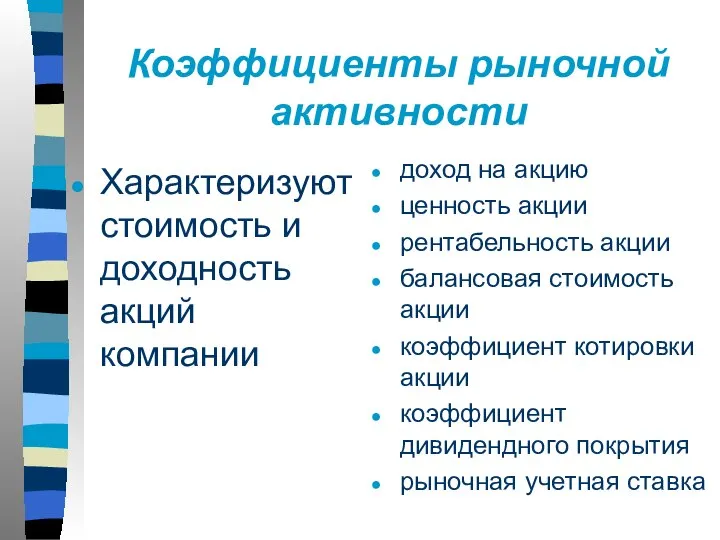

Изустная среда мордовского села Показатели рыночной активности

Показатели рыночной активности Выхухоль. Красная книга

Выхухоль. Красная книга Обработка текстовой и графической информации. Создаём комбинированный документ

Обработка текстовой и графической информации. Создаём комбинированный документ Телевидение: я выбираю или меня выбирают. Автор и руководитель проекта: Симонова Ольга Владимировна 2004 год

Телевидение: я выбираю или меня выбирают. Автор и руководитель проекта: Симонова Ольга Владимировна 2004 год Что я сделаю, чтобы доверенный мне магазин стал лучшим на рынке

Что я сделаю, чтобы доверенный мне магазин стал лучшим на рынке Туалетная вода для мужчин Faberlic Intense

Туалетная вода для мужчин Faberlic Intense Межпроцедурные анализы и оптимизации

Межпроцедурные анализы и оптимизации Внешняя политика СССР в 1930-е гг. и накануне Великой Отечественной войны

Внешняя политика СССР в 1930-е гг. и накануне Великой Отечественной войны Урок 3 Человек и Бог в православии-повторение

Урок 3 Человек и Бог в православии-повторение 17 век

17 век ПЕРЕГОВОРЫ

ПЕРЕГОВОРЫ Изготовление вечернего платья

Изготовление вечернего платья Теорiя iгор

Теорiя iгор  Презентация на тему Роль гормонов в обмене веществ, росте и развитии организма биология 8 класс

Презентация на тему Роль гормонов в обмене веществ, росте и развитии организма биология 8 класс аня хочет санчо панчо

аня хочет санчо панчо Создание таблиц в Microsoft Word

Создание таблиц в Microsoft Word Teenagers’ society problems

Teenagers’ society problems Воля познавать

Воля познавать Любимое блюдо моей семьи

Любимое блюдо моей семьи Ладья. Урок №8

Ладья. Урок №8 Описательные характеристики распределения тестовых результатов

Описательные характеристики распределения тестовых результатов Презентация на тему Одиночество

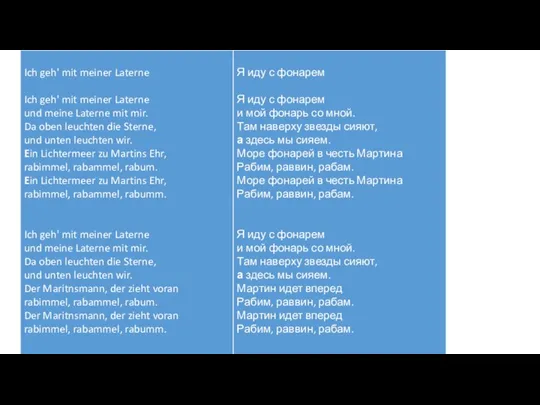

Презентация на тему Одиночество Ich gehe mit meine Laterne

Ich gehe mit meine Laterne