Содержание

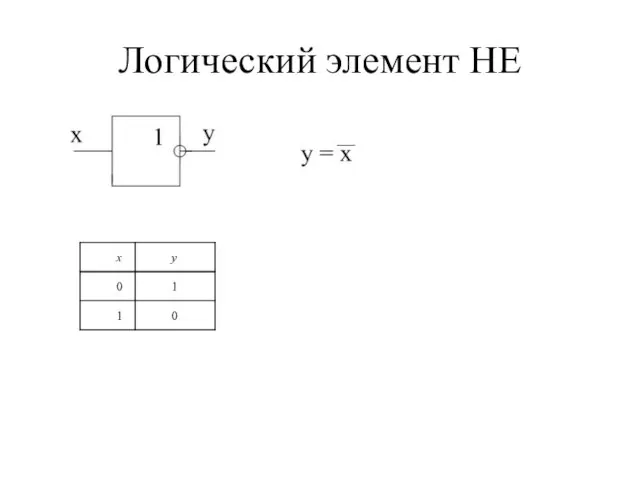

- 2. Логический элемент НЕ

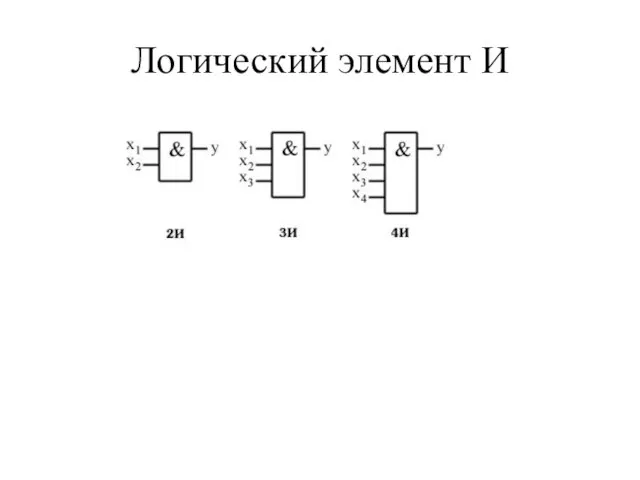

- 3. Логический элемент И

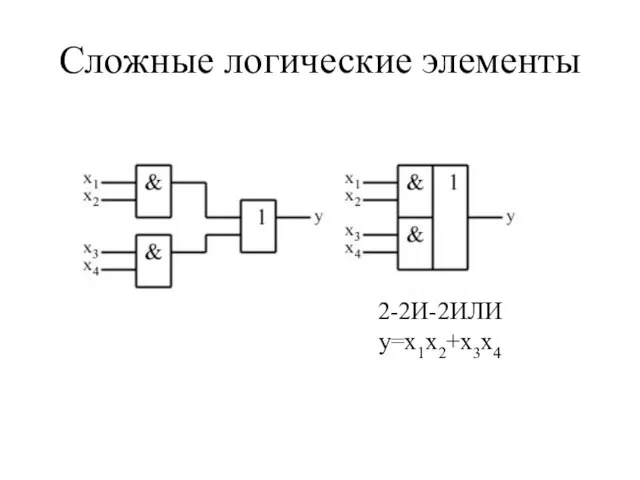

- 4. Сложные логические элементы 2-2И-2ИЛИ y=x1x2+x3x4

- 6. Комбинационные логические устройства Дешифратор и шифратор. Мультиплексор и демультиплексор. Полусумматор и сумматор. Арифметико-логическое устройство.

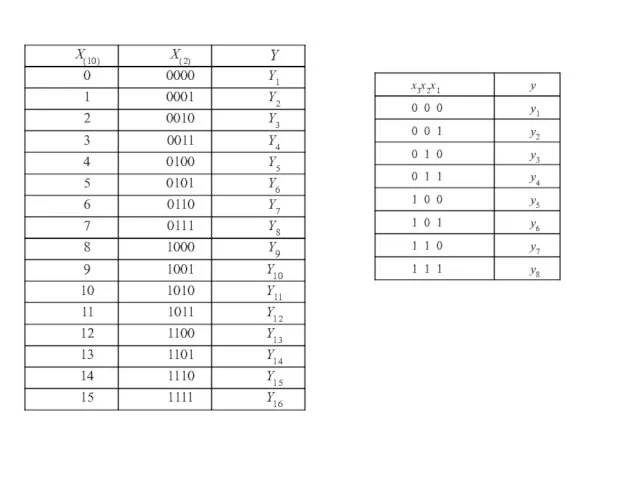

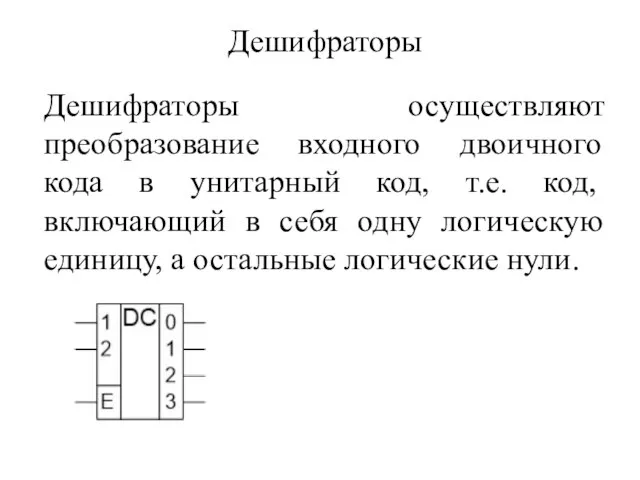

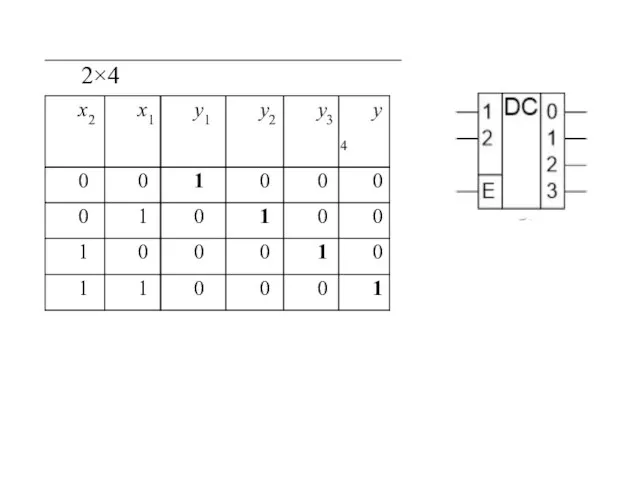

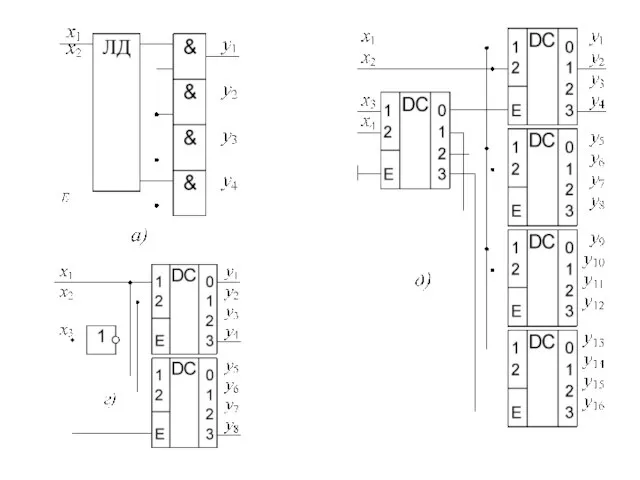

- 7. Дешифраторы Дешифраторы осуществляют преобразование входного двоичного кода в унитарный код, т.е. код, включающий в себя одну

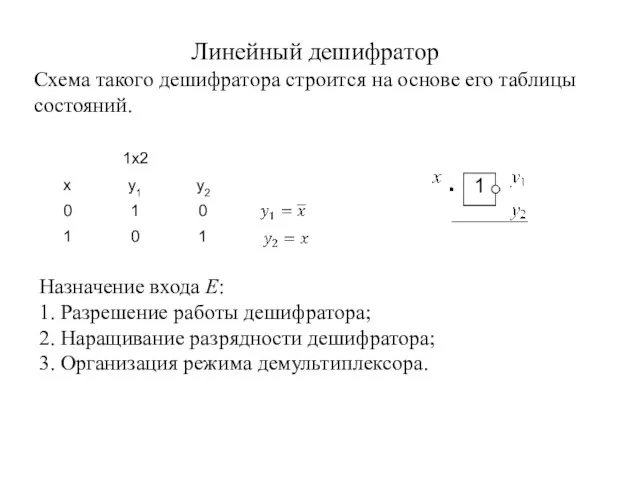

- 9. Линейный дешифратор Схема такого дешифратора строится на основе его таблицы состояний. Назначение входа E: 1. Разрешение

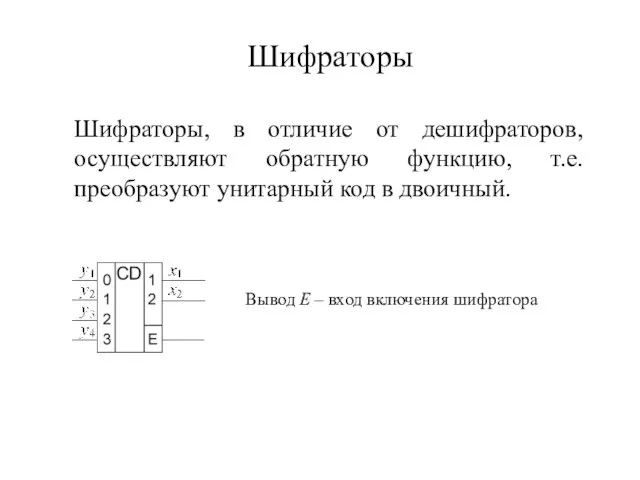

- 11. Шифраторы Шифраторы, в отличие от дешифраторов, осуществляют обратную функцию, т.е. преобразуют унитарный код в двоичный. Вывод

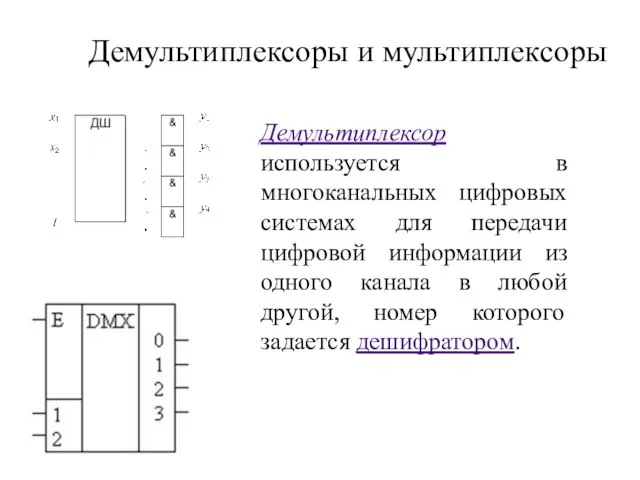

- 12. Демультиплексоры и мультиплексоры Демультиплексор используется в многоканальных цифровых системах для передачи цифровой информации из одного канала

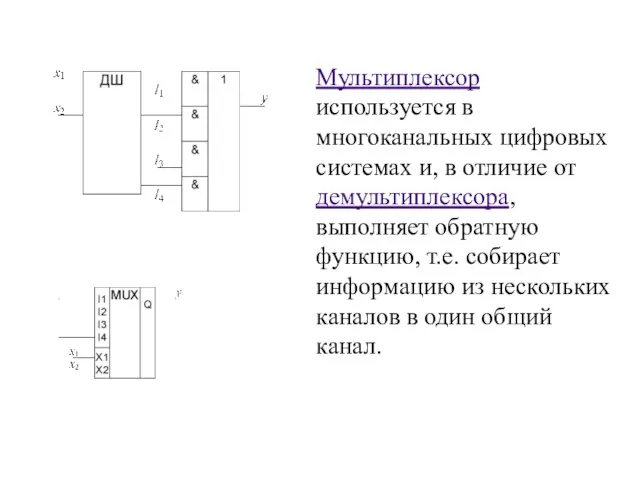

- 13. Мультиплексор используется в многоканальных цифровых системах и, в отличие от демультиплексора, выполняет обратную функцию, т.е. собирает

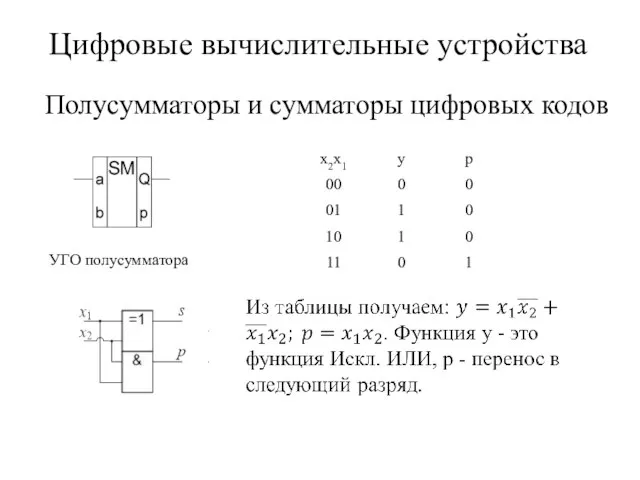

- 14. Цифровые вычислительные устройства Полусумматоры и сумматоры цифровых кодов УГО полусумматора

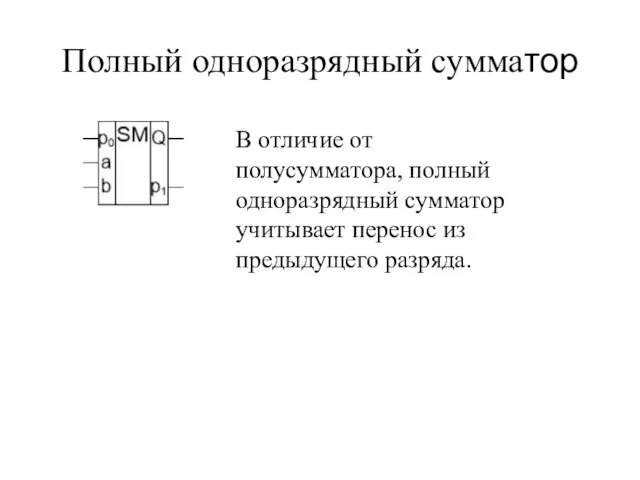

- 15. Полный одноразрядный сумматор В отличие от полусумматора, полный одноразрядный сумматор учитывает перенос из предыдущего разряда.

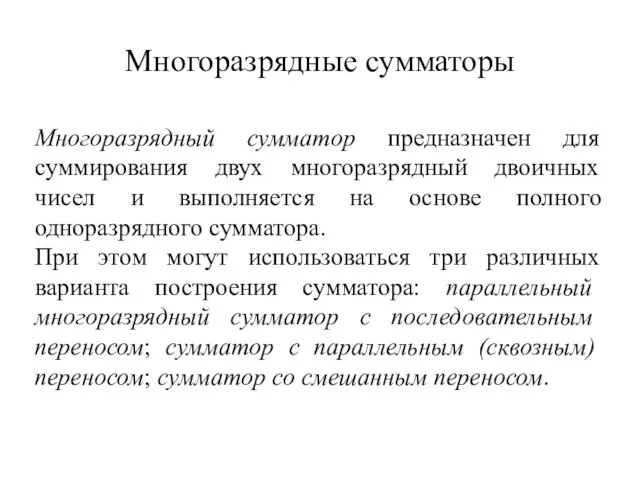

- 16. Многоразрядные сумматоры Многоразрядный сумматор предназначен для суммирования двух многоразрядный двоичных чисел и выполняется на основе полного

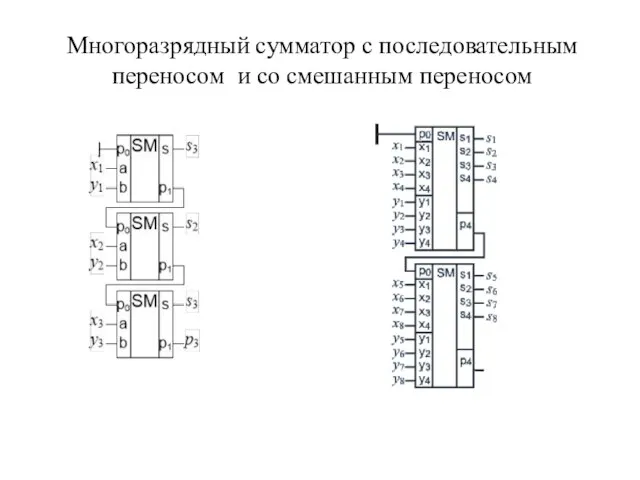

- 17. Многоразрядный сумматор с последовательным переносом и cо смешанным переносом

- 18. Арифметико-логическое устройство Таблица 3.6 - Операции АЛУ 531ИП3

- 19. Тактируемые цифровые устройства Цифровые запоминающие устройства Триггеры Триггер – это одноразрядное, цифровое запоминающее устройство, содержащее запоминающий

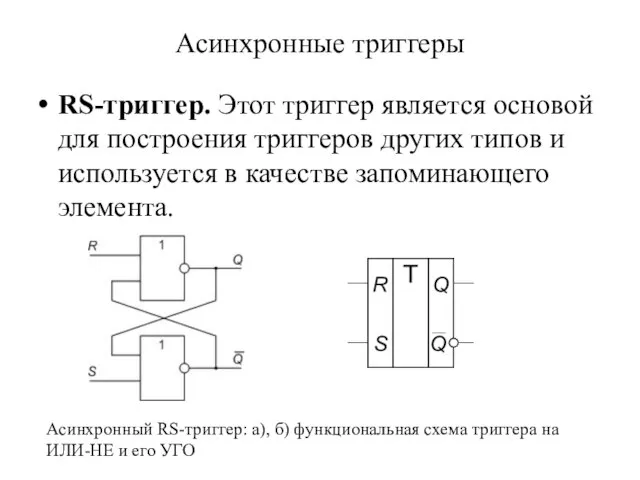

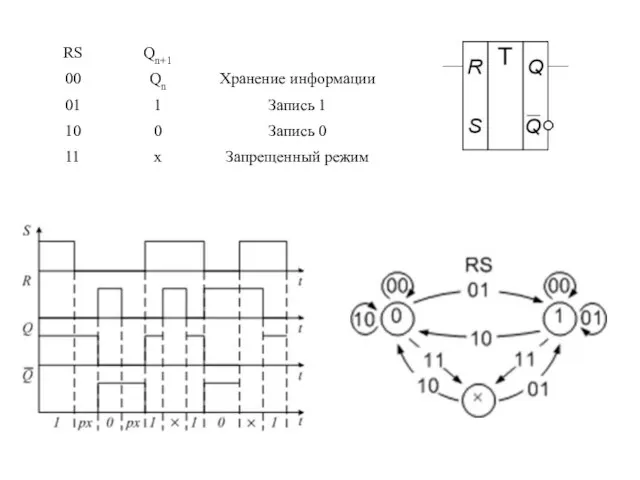

- 20. Асинхронные триггеры RS-триггер. Этот триггер является основой для построения триггеров других типов и используется в качестве

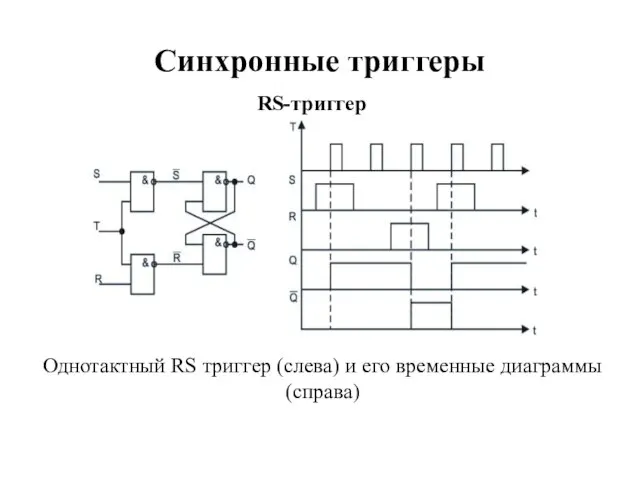

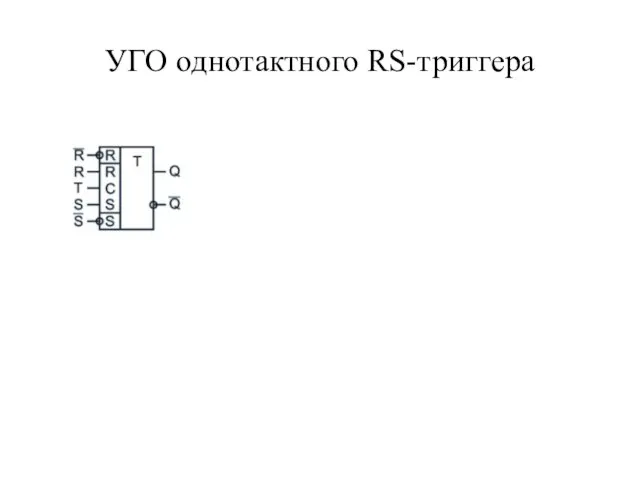

- 22. Синхронные триггеры RS-триггер Однотактный RS триггер (слева) и его временные диаграммы (справа)

- 23. УГО однотактного RS-триггера

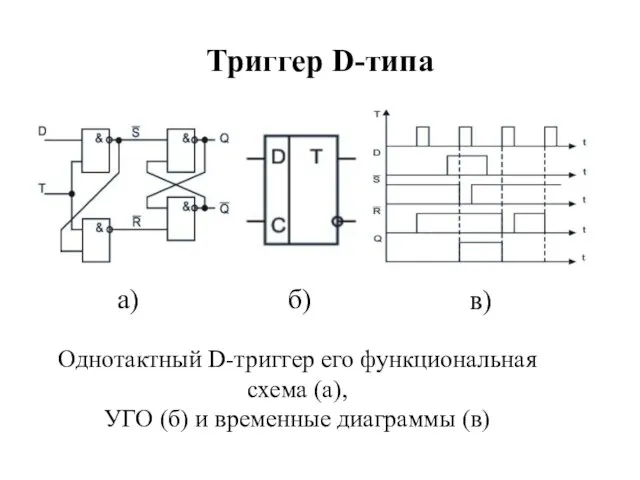

- 24. Триггер D-типа а) б) в) Однотактный D-триггер его функциональная схема (а), УГО (б) и временные диаграммы

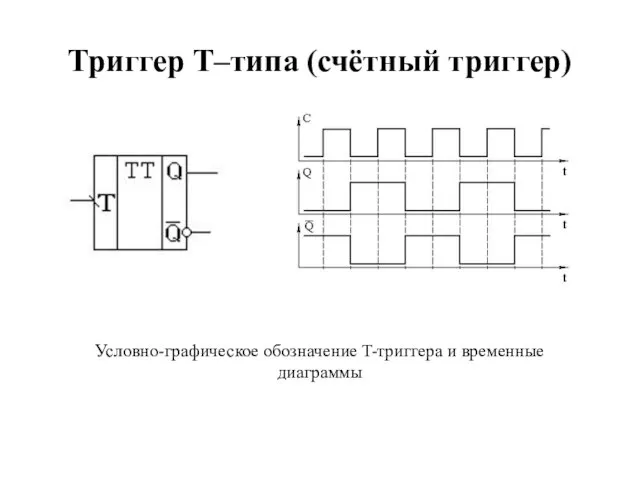

- 25. Триггер T–типа (счётный триггер) Условно-графическое обозначение T-триггера и временные диаграммы

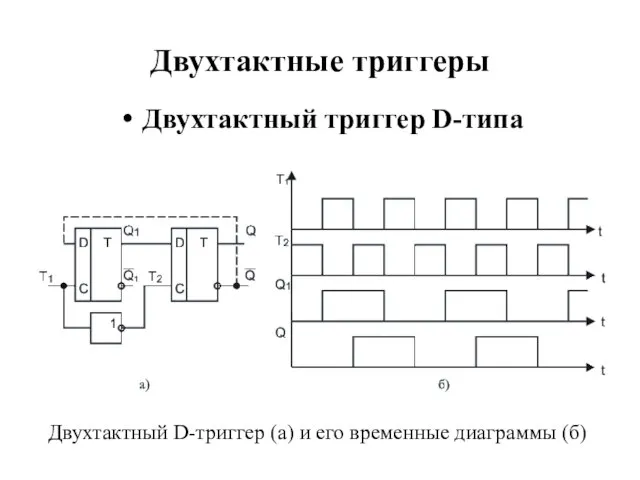

- 26. Двухтактные триггеры Двухтактный триггер D-типа Двухтактный D-триггер (а) и его временные диаграммы (б)

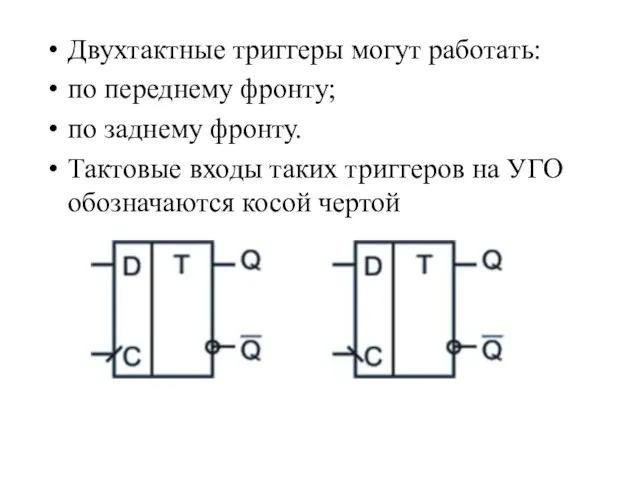

- 27. Двухтактные триггеры могут работать: по переднему фронту; по заднему фронту. Тактовые входы таких триггеров на УГО

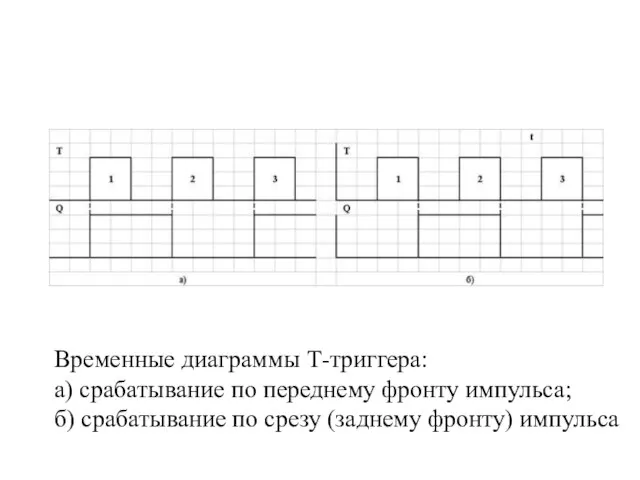

- 28. Временные диаграммы Т-триггера: а) срабатывание по переднему фронту импульса; б) срабатывание по срезу (заднему фронту) импульса

- 29. Регистры Регистрами называются многоразрядные цифровые запоминающие устройства, предназначенные для приёма, хранения, преобразования и передачи информации. Основу

- 30. Регистры делятся на: 1. параллельные; 2. последовательные; 3.параллельно-последовательные.

- 31. Параллельные регистры Параллельный n-разрядный регистр представляет собой n триггеров, на информационные входы которых подается n-разрядный двоичный

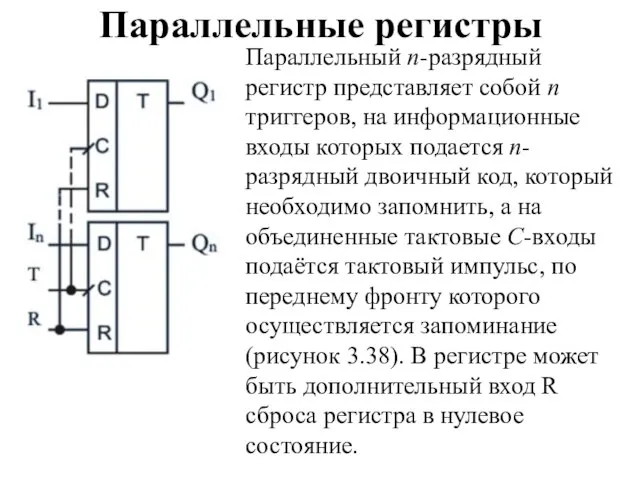

- 32. Параллельные регистры Параллельный n-разрядный регистр представляет собой n триггеров, на информационные входы которых подается n-разрядный двоичный

- 33. Последовательные регистры Последовательные регистры работают с последовательным кодом, разряды которого разделены во времени на интервалы, равные

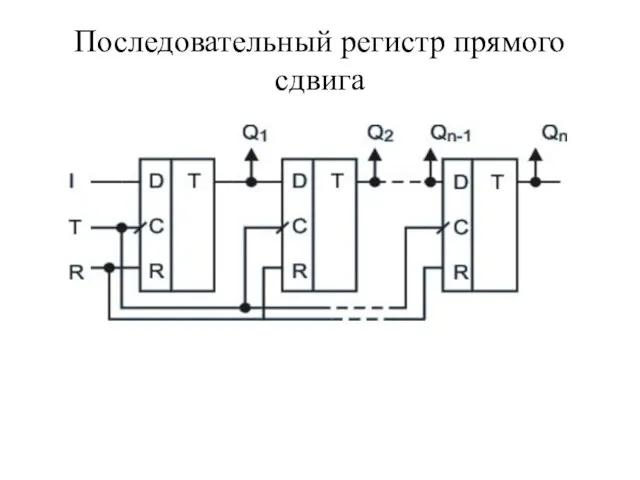

- 34. Последовательный регистр прямого сдвига

- 35. Регистры прямого сдвига осуществляют приём (передачу) информации, сдвигая её в регистре на 1 разряд вправо при

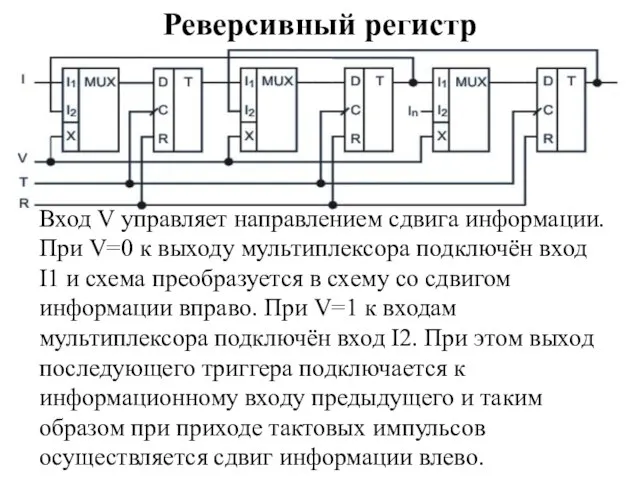

- 36. Реверсивный регистр Вход V управляет направлением сдвига информации. При V=0 к выходу мультиплексора подключён вход I1

- 37. Реверсивный сдвиговый регистр позволяет осуществить сдвиг информации внутри регистра, как вправо, так и влево. Это может

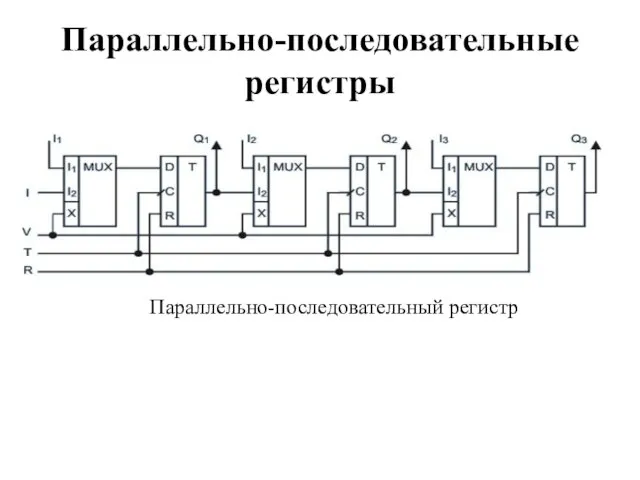

- 38. Параллельно-последовательные регистры Такие регистры служат для преобразования информации с последовательного кода в параллельный или наоборот, а

- 39. Параллельно-последовательные регистры Параллельно-последовательный регистр

- 40. Параллельно-последовательные регистры При V=0 организуется режим параллельного регистра. При этом в мультиплексорах к выходам подключены входы

- 41. Счётчики импульсов Счетчиком называется устройство, предназначенное для счета входных импульсов и фиксации их числа в двоичном

- 42. К основным характеристикам счетчиков относятся модуль счета (коэффициент пересчета Ксч) и быстродействие. Модуль счета Ксч характеризует

- 43. Асинхронные счётчики импульсов Асинхронный счетчик импульсов представляет собой последовательно соединенные триггеры Т-типа, при этом срабатывание каждого

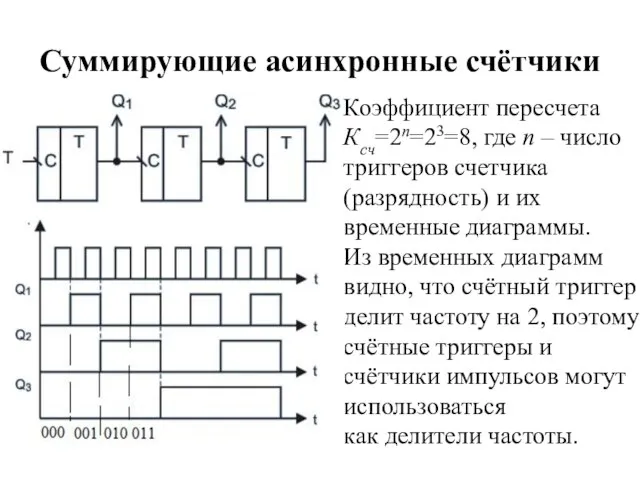

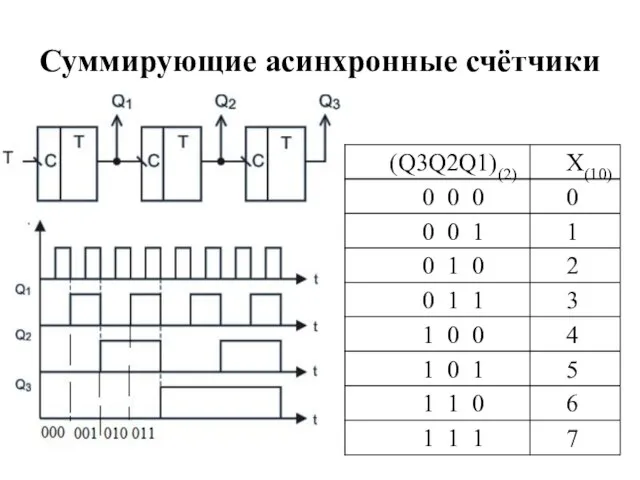

- 44. Суммирующие асинхронные счётчики Коэффициент пересчета Ксч=2n=23=8, где n – число триггеров счетчика (разрядность) и их временные

- 45. Суммирующие асинхронные счётчики

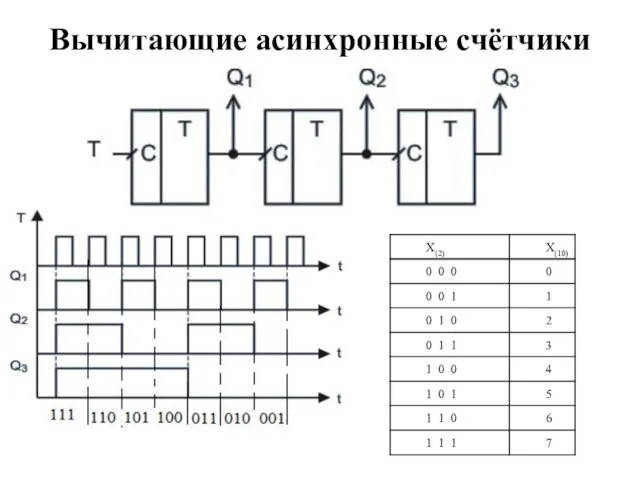

- 46. Вычитающие асинхронные счётчики

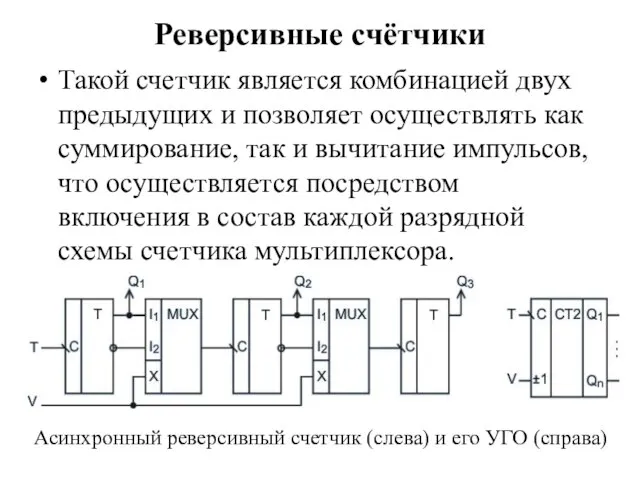

- 47. Реверсивные счётчики Такой счетчик является комбинацией двух предыдущих и позволяет осуществлять как суммирование, так и вычитание

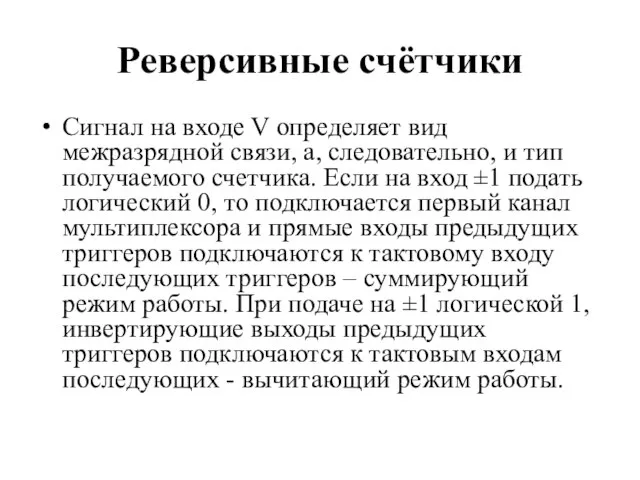

- 48. Реверсивные счётчики Сигнал на входе V определяет вид межразрядной связи, а, следовательно, и тип получаемого счетчика.

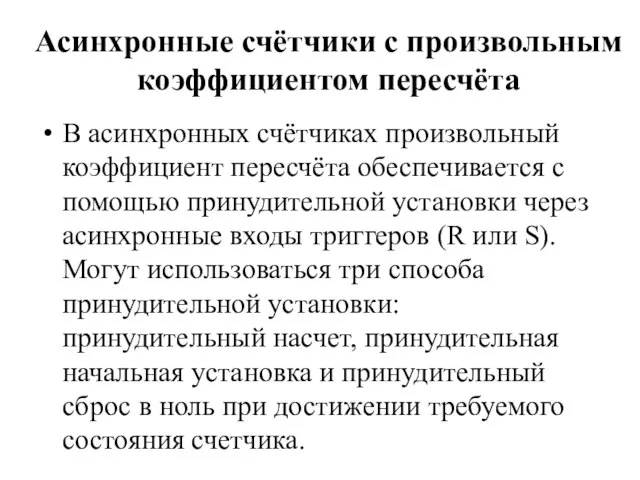

- 49. Асинхронные счётчики с произвольным коэффициентом пересчёта В асинхронных счётчиках произвольный коэффициент пересчёта обеспечивается с помощью принудительной

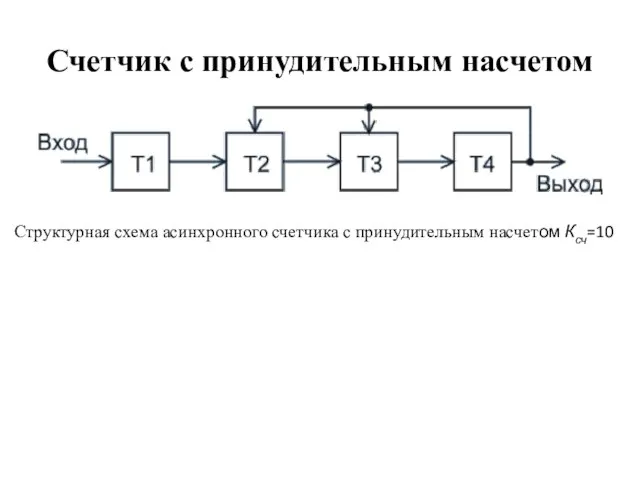

- 50. Счетчик с принудительным насчетом Структурная схема асинхронного счетчика с принудительным насчетом Ксч=10

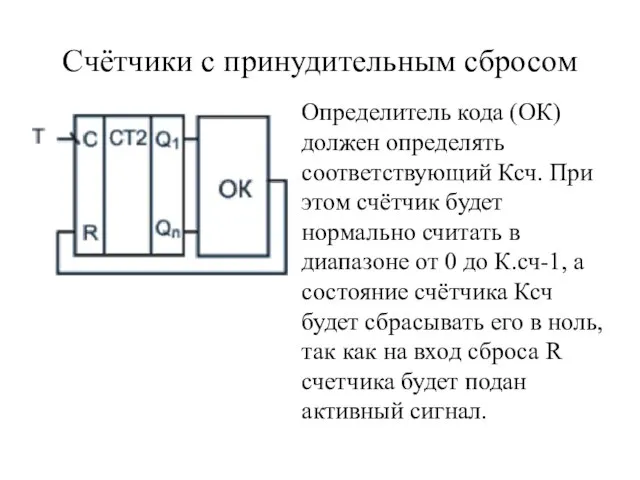

- 51. Счётчики с принудительным сбросом Определитель кода (ОК) должен определять соответствующий Ксч. При этом счётчик будет нормально

- 52. Счетчики с переносом Такие счётчики делятся на 2 типа: 1. С параллельным переносом; 2.С последовательным переносом.

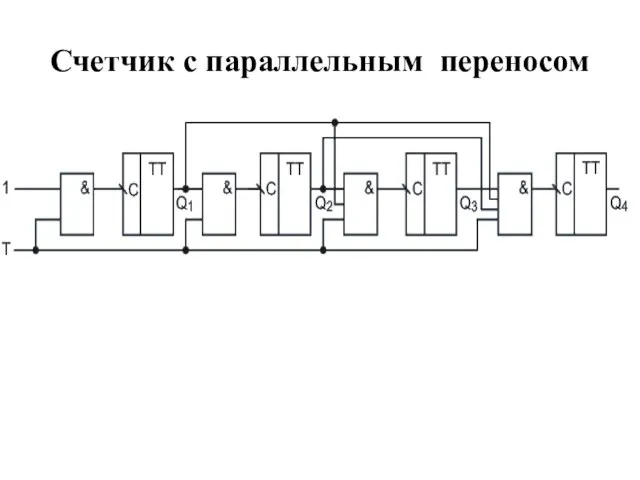

- 53. Счетчик с параллельным переносом

- 54. Счётчик с последовательным переносом

- 55. Счётчик с последовательным переносом Счетчик с параллельным переносом

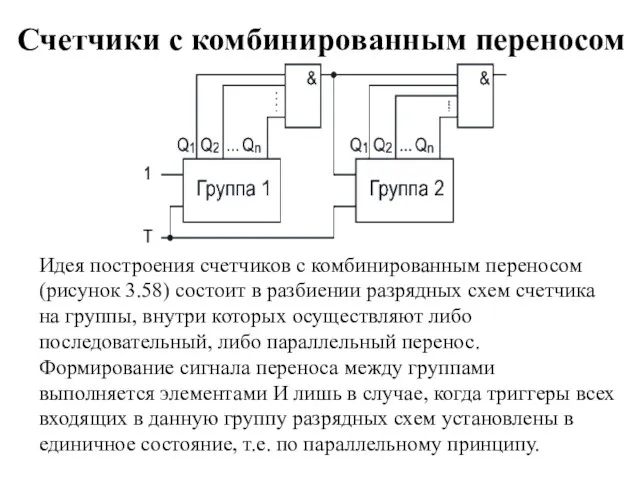

- 56. Счетчики с комбинированным переносом Идея построения счетчиков с комбинированным переносом (рисунок 3.58) состоит в разбиении разрядных

- 57. Счётчики с произвольным коэффициентом пересчёта Функциональная схема дешифратора (определителя) выходного кода счетчика

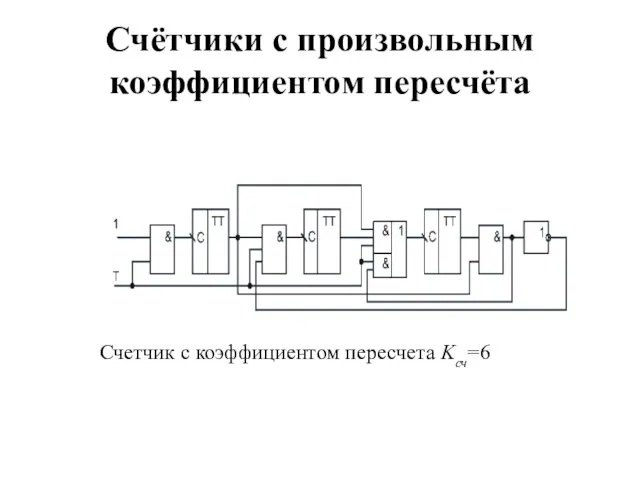

- 58. Счётчики с произвольным коэффициентом пересчёта Счетчик с коэффициентом пересчета Kсч=6

- 59. Счётчики с произвольным коэффициентом пересчёта В качестве основы для построения счётчиков с произвольным коэффициентом пересчёта служит

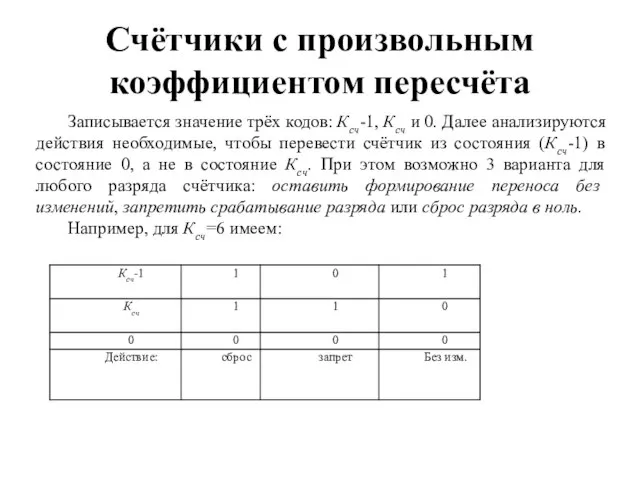

- 60. Счётчики с произвольным коэффициентом пересчёта Записывается значение трёх кодов: Ксч-1, Ксч и 0. Далее анализируются действия

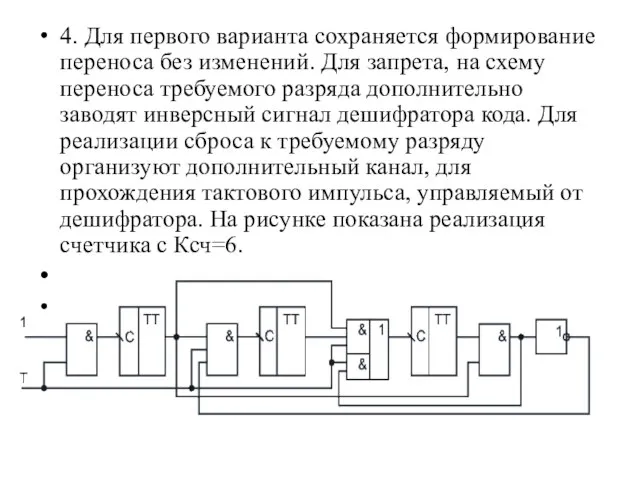

- 61. 4. Для первого варианта сохраняется формирование переноса без изменений. Для запрета, на схему переноса требуемого разряда

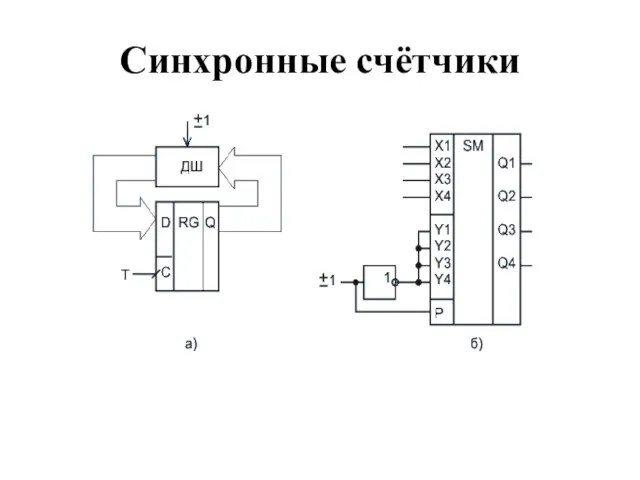

- 62. Синхронные счётчики

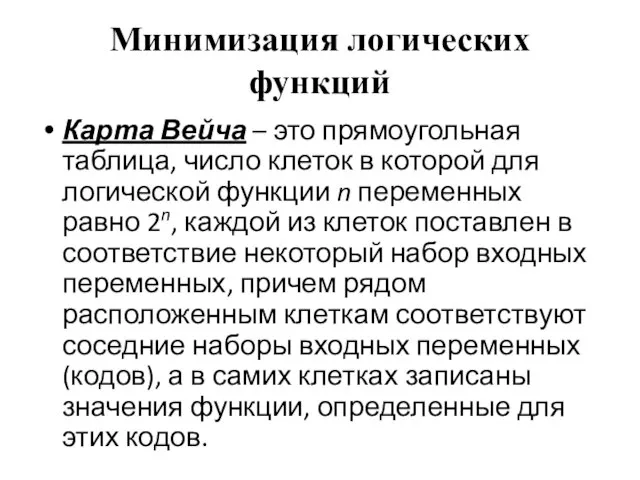

- 63. Минимизация логических функций Карта Вейча – это прямоугольная таблица, число клеток в которой для логической функции

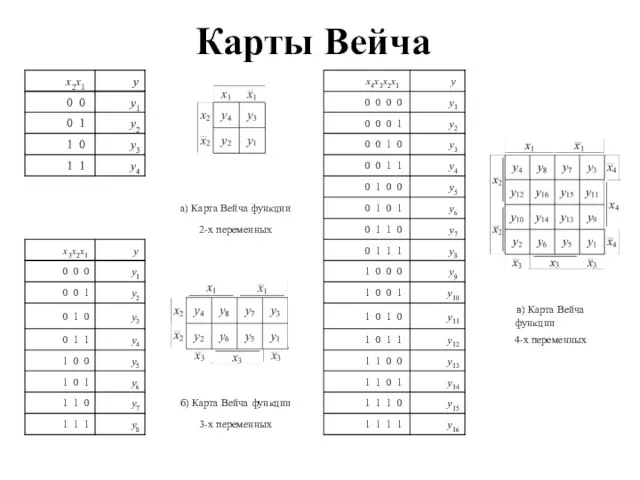

- 64. Карты Вейча

- 66. Скачать презентацию

Праздник Рождества в России

Праздник Рождества в России Маркунас Ирина Анатольевна, учитель русского языка и литературы высшей категории МОУ СОШ с углубленным изучением информатики №

Маркунас Ирина Анатольевна, учитель русского языка и литературы высшей категории МОУ СОШ с углубленным изучением информатики № Leonid Bugaev, Nordic Agency AB 24.10.2011 Екатеринбург, Web2Win.ru

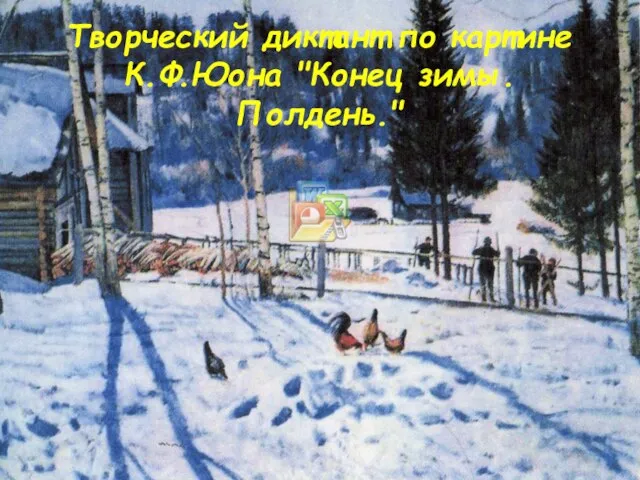

Leonid Bugaev, Nordic Agency AB 24.10.2011 Екатеринбург, Web2Win.ru Творческий диктант по картине К.Ф.Юона "Конец зимы. Полдень."

Творческий диктант по картине К.Ф.Юона "Конец зимы. Полдень." Типы и виды карьеры. Качества, присущие профессионалу нынешнего века

Типы и виды карьеры. Качества, присущие профессионалу нынешнего века Химические реакции. Составление уравнений химических реакций

Химические реакции. Составление уравнений химических реакций Classical Music

Classical Music  шелк

шелк Почему племена говорят на разных языках

Почему племена говорят на разных языках Вооружённые Силы Российской Федерации на защите государства от военных угроз

Вооружённые Силы Российской Федерации на защите государства от военных угроз Машиноведение Проверочная работа

Машиноведение Проверочная работа Презентация на тему Ботаника - наука о растениях

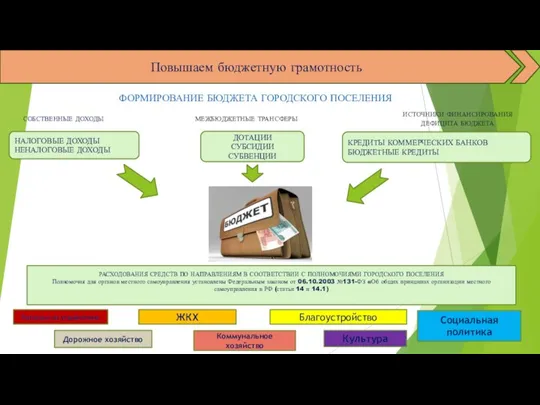

Презентация на тему Ботаника - наука о растениях Повышаем бюджетную грамотность

Повышаем бюджетную грамотность Составные части компьютера

Составные части компьютера Презентация на тему Построение графика функции методом ее исследования с помощью производной

Презентация на тему Построение графика функции методом ее исследования с помощью производной Мир живых организмов. Уровни организации и свойства живого

Мир живых организмов. Уровни организации и свойства живого СЕГМЕНТИРОВАНИЕ, ВЫБОР ЦЕЛЕВЫХ РЫНКОВ И ПОЗИЦИОНИРОВАНИЕГлава 8

СЕГМЕНТИРОВАНИЕ, ВЫБОР ЦЕЛЕВЫХ РЫНКОВ И ПОЗИЦИОНИРОВАНИЕГлава 8 Золотой ключик или приключения Буратино. Диафильм часть 2

Золотой ключик или приключения Буратино. Диафильм часть 2 Человек и природа в сказке-были М.М. Пришвина «Кладовая солнца»

Человек и природа в сказке-были М.М. Пришвина «Кладовая солнца» Презентация на тему Эдуард Шим "Храбрый опёнок" 2 класс

Презентация на тему Эдуард Шим "Храбрый опёнок" 2 класс  СТАТИСТИКА ОСНОВНЫХ И ОБОРОТНЫХ ФОНДОВ

СТАТИСТИКА ОСНОВНЫХ И ОБОРОТНЫХ ФОНДОВ Право интеллектуальной собственности

Право интеллектуальной собственности Декабристы и их идеология

Декабристы и их идеология Презентация на тему Как ухаживать за зубами

Презентация на тему Как ухаживать за зубами  Лётчик – истребитель Сергей Ачкасов

Лётчик – истребитель Сергей Ачкасов Гуманитарно-эстетическая кафедра

Гуманитарно-эстетическая кафедра Анемический и геморрагический синдром у новорожденных

Анемический и геморрагический синдром у новорожденных Психологическая зависимость

Психологическая зависимость