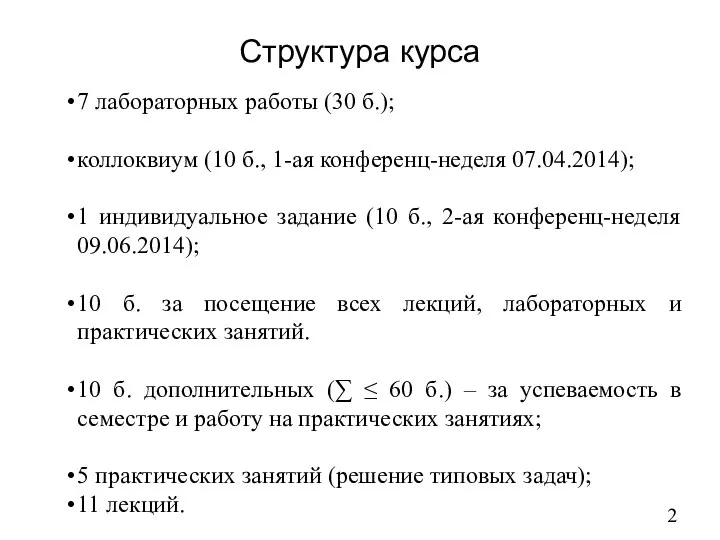

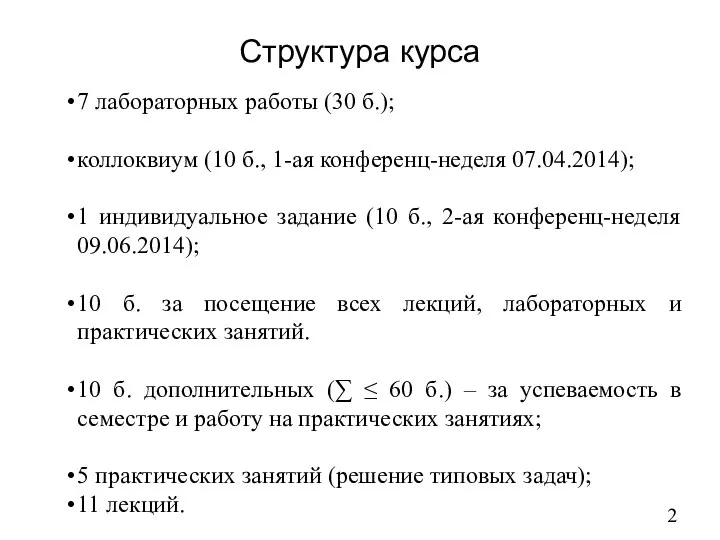

Слайд 2Структура курса

7 лабораторных работы (30 б.);

коллоквиум (10 б., 1-ая конференц-неделя 07.04.2014);

1 индивидуальное

задание (10 б., 2-ая конференц-неделя 09.06.2014);

10 б. за посещение всех лекций, лабораторных и практических занятий.

10 б. дополнительных (∑ ≤ 60 б.) – за успеваемость в семестре и работу на практических занятиях;

5 практических занятий (решение типовых задач);

11 лекций.

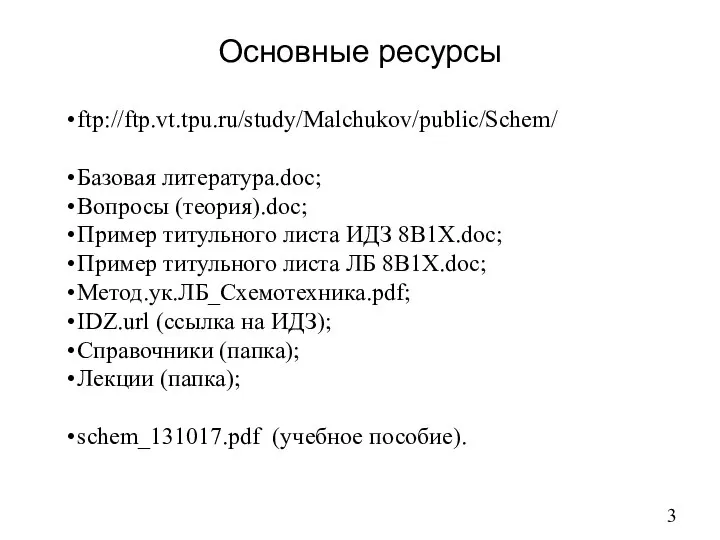

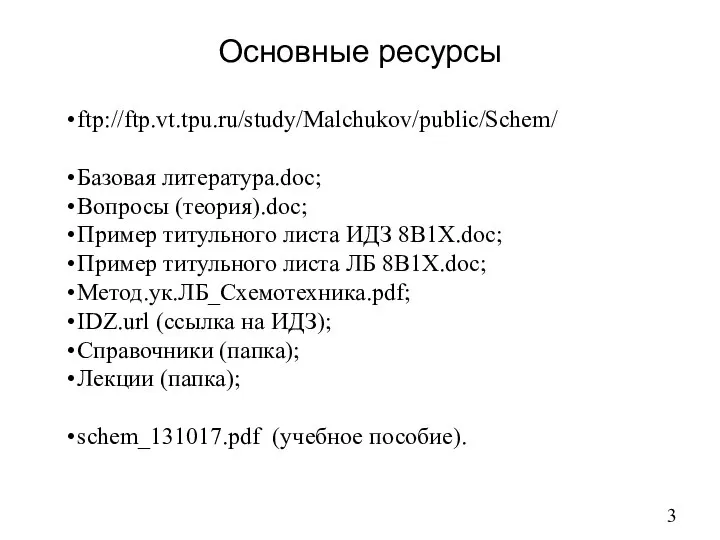

Слайд 3Основные ресурсы

ftp://ftp.vt.tpu.ru/study/Malchukov/public/Schem/

Базовая литература.doc;

Вопросы (теория).doc;

Пример титульного листа ИДЗ 8B1Х.doc;

Пример титульного листа ЛБ 8B1Х.doc;

Метод.ук.ЛБ_Схемотехника.pdf;

IDZ.url

(ссылка на ИДЗ);

Справочники (папка);

Лекции (папка);

schem_131017.pdf (учебное пособие).

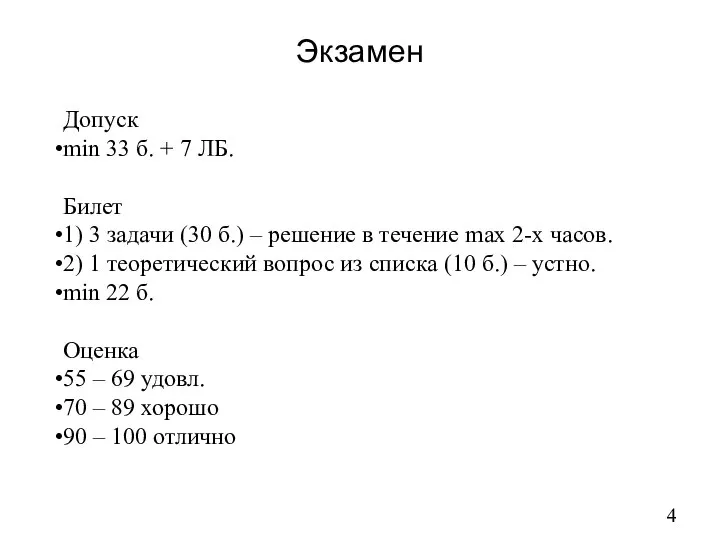

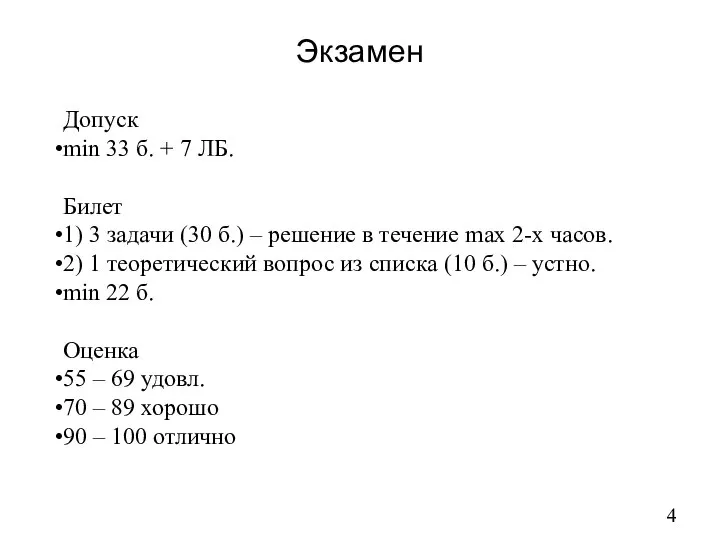

Слайд 4Экзамен

Допуск

min 33 б. + 7 ЛБ.

Билет

1) 3 задачи (30 б.) – решение

в течение max 2-х часов.

2) 1 теоретический вопрос из списка (10 б.) – устно.

min 22 б.

Оценка

55 – 69 удовл.

70 – 89 хорошо

90 – 100 отлично

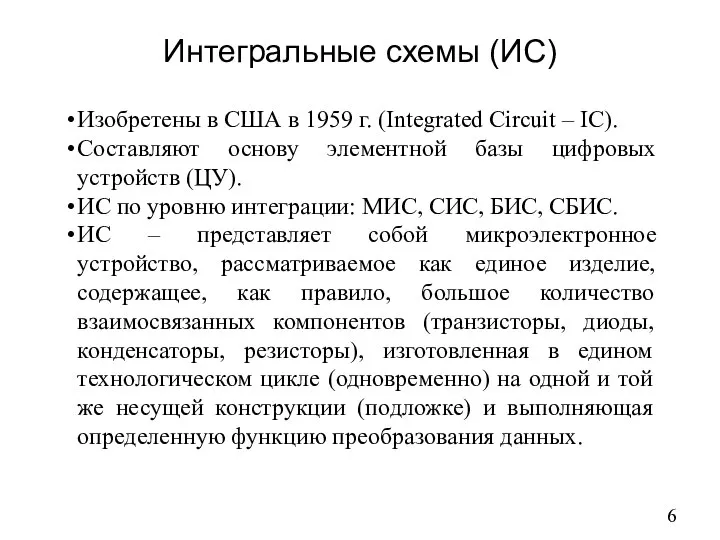

Слайд 6Интегральные схемы (ИС)

Изобретены в США в 1959 г. (Integrated Circuit – IC).

Составляют

основу элементной базы цифровых устройств (ЦУ).

ИС по уровню интеграции: МИС, СИС, БИС, СБИС.

ИС – представляет собой микроэлектронное устройство, рассматриваемое как единое изделие, содержащее, как правило, большое количество взаимосвязанных компонентов (транзисторы, диоды, конденсаторы, резисторы), изготовленная в едином технологическом цикле (одновременно) на одной и той же несущей конструкции (подложке) и выполняющая определенную функцию преобразования данных.

Слайд 7Понятие ИС и метод её изготовление

Элементы ИС (интегральные элементы) – компоненты, входящие

в состав ИС, которые не могут быть выделены из неё в качестве самостоятельных изделий.

Групповой метод – на одной пластине полупроводникового (ПП) материала одновременно изготавливается большое количество ИС, одновременно обрабатывается несколько пластин.

Отдельные кристаллы (chip) – получают после завершения определенных циклов изготовления, когда ПП разрезается в двух взаимно перпендикулярных направлениях.

Корпусирование – помещение ИС в корпус с присоединением лазерной сваркой контактных площадок к ножкам (pin) ИС.

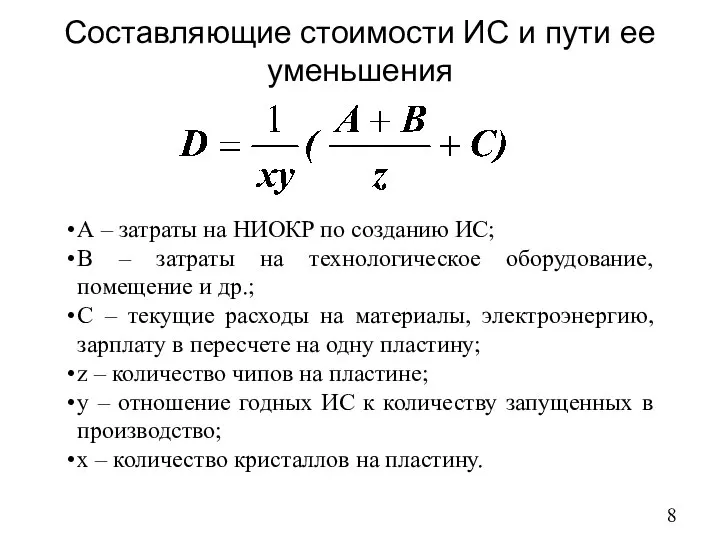

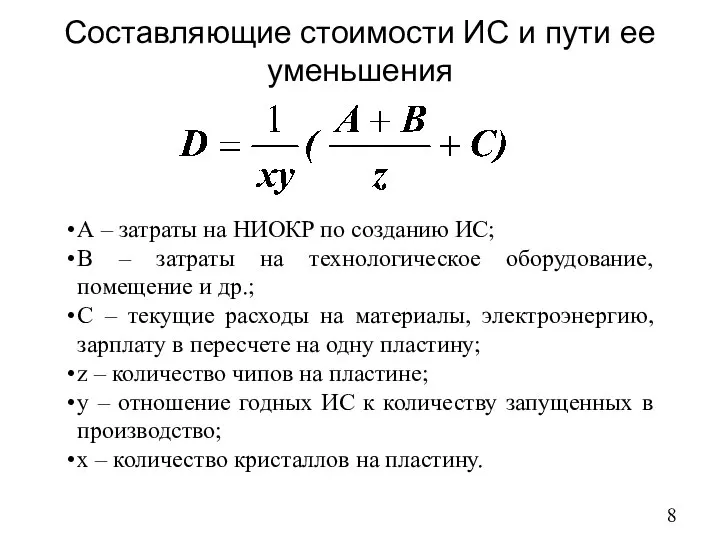

Слайд 8Составляющие стоимости ИС и пути ее уменьшения

А – затраты на НИОКР по

созданию ИС;

В – затраты на технологическое оборудование, помещение и др.;

С – текущие расходы на материалы, электроэнергию, зарплату в пересчете на одну пластину;

z – количество чипов на пластине;

у – отношение годных ИС к количеству запущенных в производство;

x – количество кристаллов на пластину.

Слайд 9Типы интегральных схем по технологическому признаку

Полупроводниковая ИС – ИС, все элементы и

межэлементные соединения которой выполнены в объеме и на поверхности ПП кристалла.

Гибридная ИС – ИС содержат элементы, компоненты и кристаллы, а также межэлементные соединения, размещенные на поверхности диэлектрической подложки.

Пленочные ИС – содержат элементы и межэлементные соединения, выполненные на поверхности диэлектрической подложки.

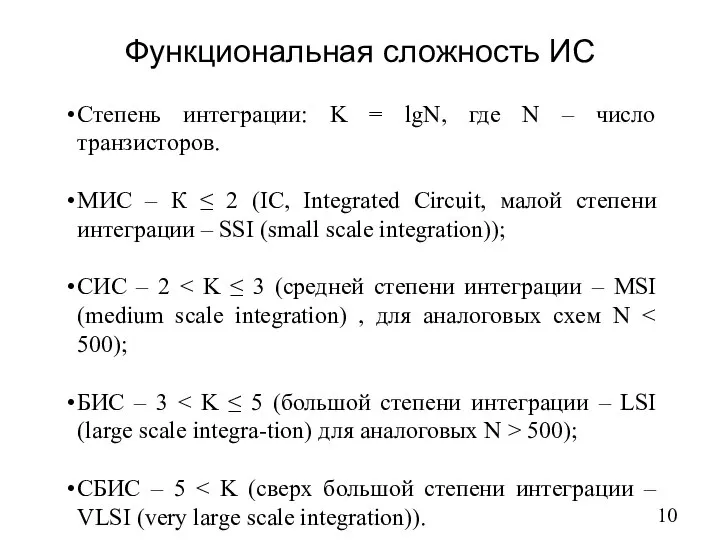

Слайд 10Функциональная сложность ИС

Степень интеграции: K = lgN, где N – число транзисторов.

МИС

– К ≤ 2 (IC, Integrated Circuit, малой степени интеграции – SSI (small scale integration));

СИС – 2 < K ≤ 3 (средней степени интеграции – MSI (medium scale integration) , для аналоговых схем N < 500);

БИС – 3 < K ≤ 5 (большой степени интеграции – LSI (large scale integra-tion) для аналоговых N > 500);

СБИС – 5 < K (сверх большой степени интеграции – VLSI (very large scale integration)).

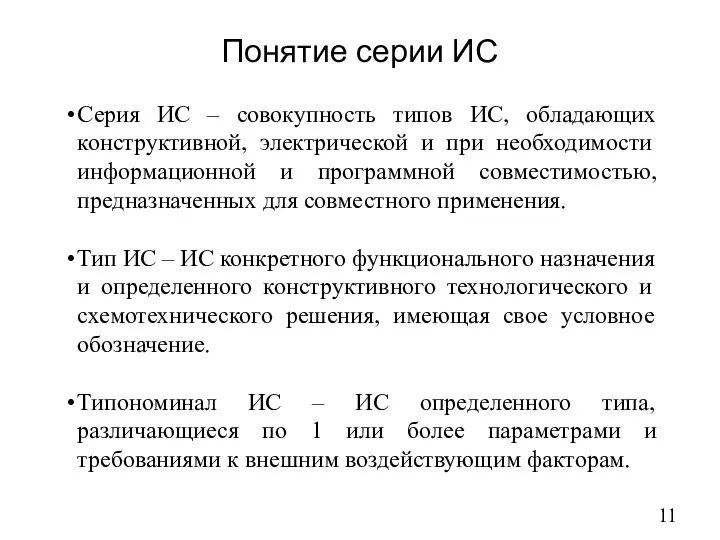

Слайд 11Понятие серии ИС

Серия ИС – совокупность типов ИС, обладающих конструктивной, электрической и

при необходимости информационной и программной совместимостью, предназначенных для совместного применения.

Тип ИС – ИС конкретного функционального назначения и определенного конструктивного технологического и схемотехнического решения, имеющая свое условное обозначение.

Типономинал ИС – ИС определенного типа, различающиеся по 1 или более параметрами и требованиями к внешним воздействующим факторам.

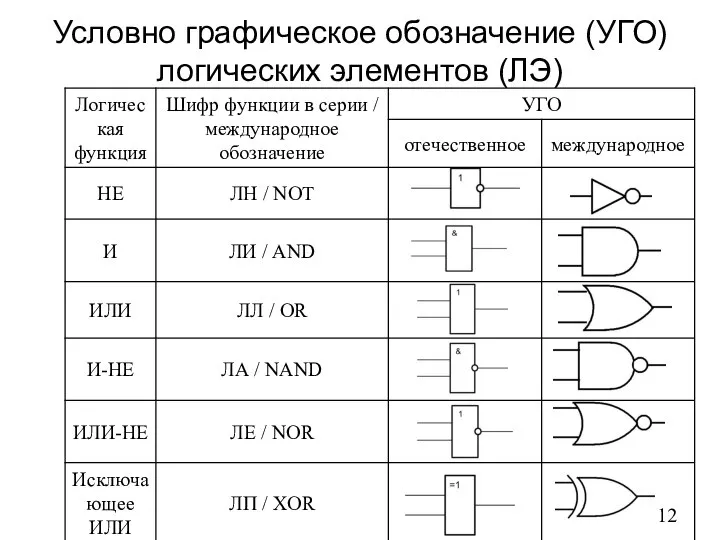

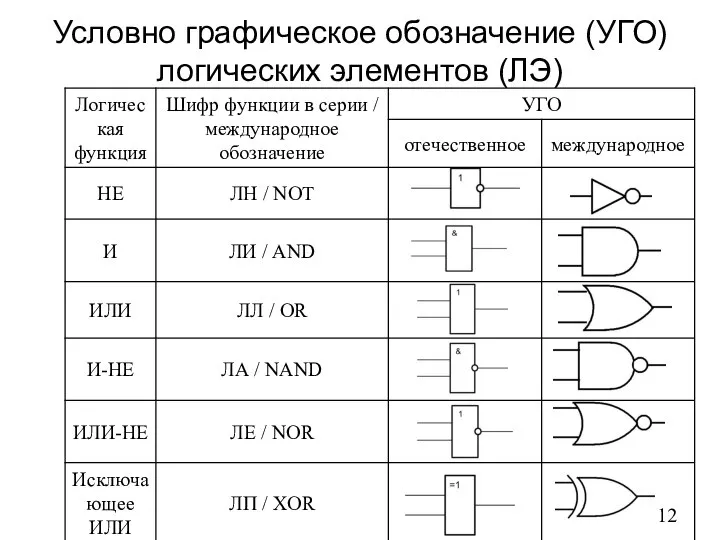

Слайд 12Условно графическое обозначение (УГО) логических элементов (ЛЭ)

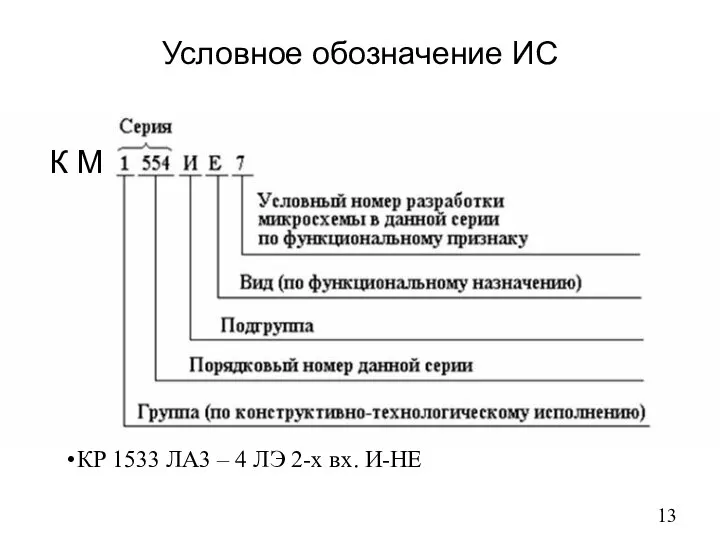

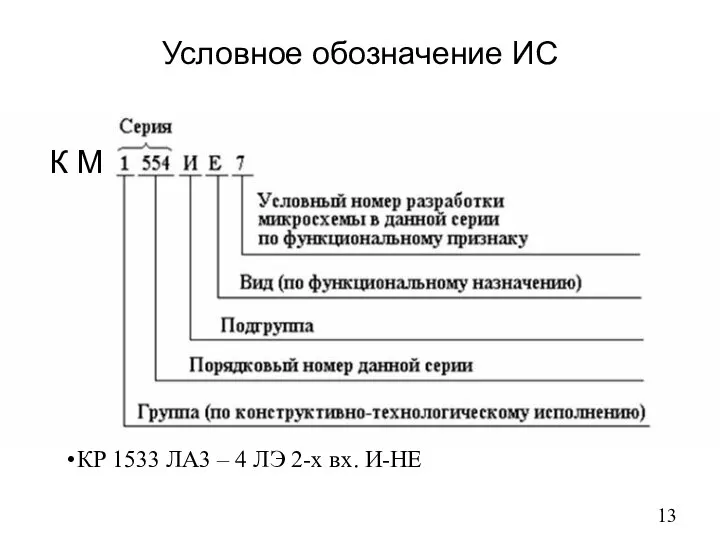

Слайд 13Условное обозначение ИС

К М

КP 1533 ЛА3 – 4 ЛЭ 2-х вх.

И-НЕ

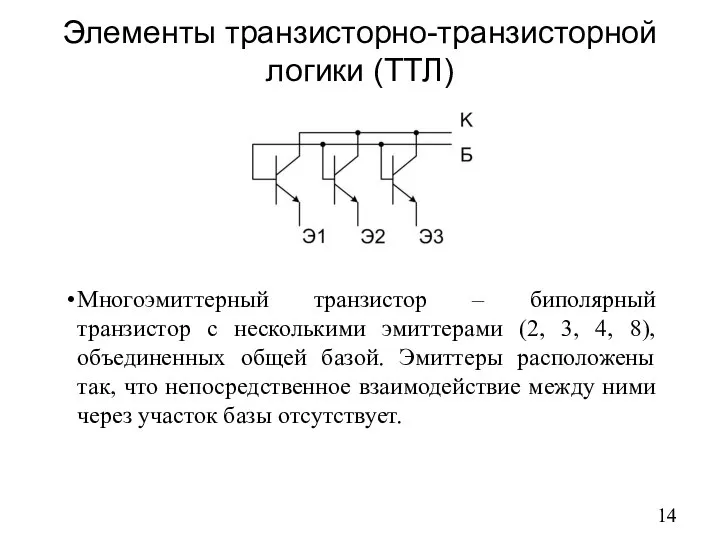

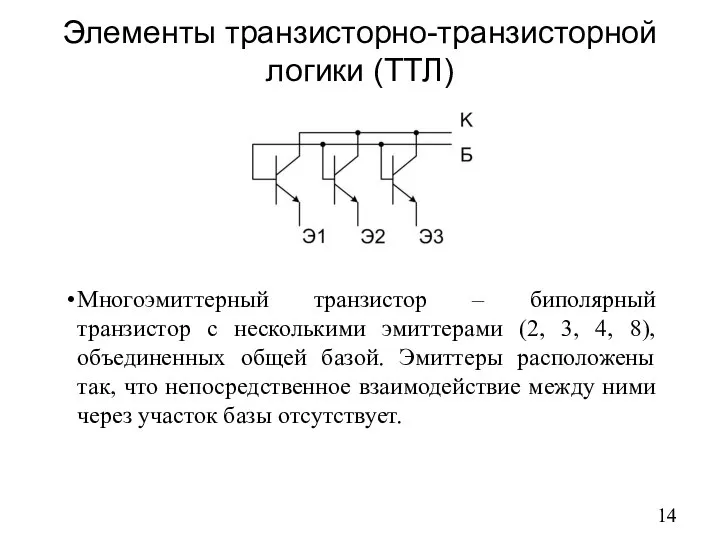

Слайд 14Элементы транзисторно-транзисторной логики (ТТЛ)

Многоэмиттерный транзистор – биполярный транзистор с несколькими эмиттерами (2,

3, 4, 8), объединенных общей базой. Эмиттеры расположены так, что непосредственное взаимодействие между ними через участок базы отсутствует.

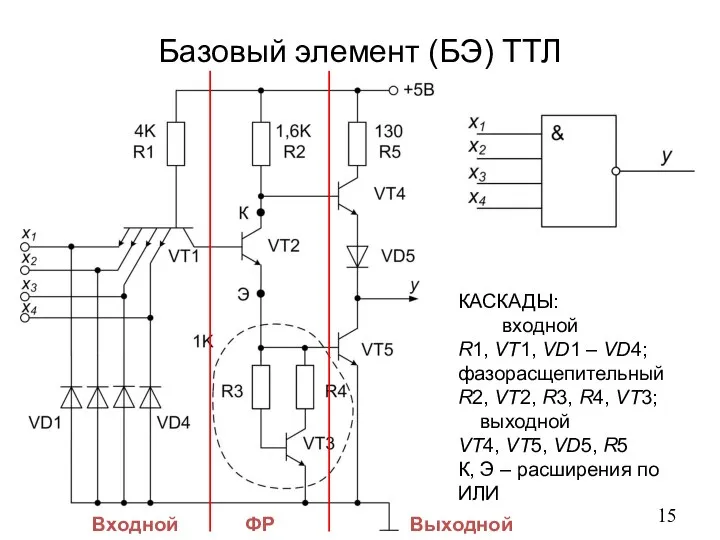

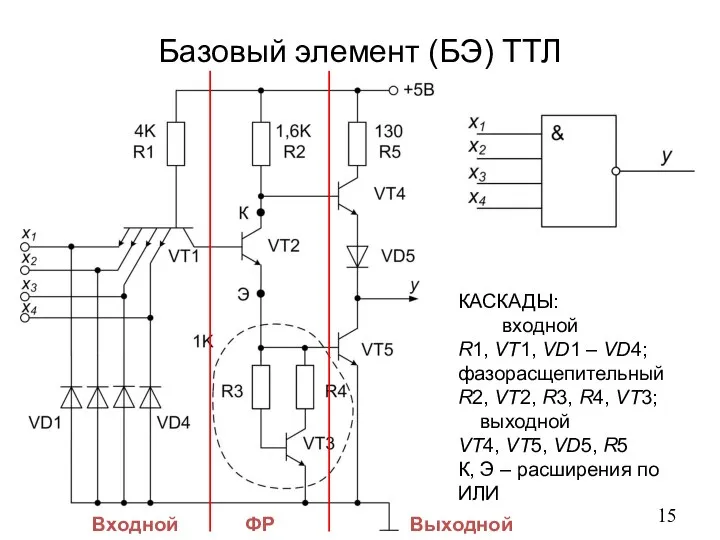

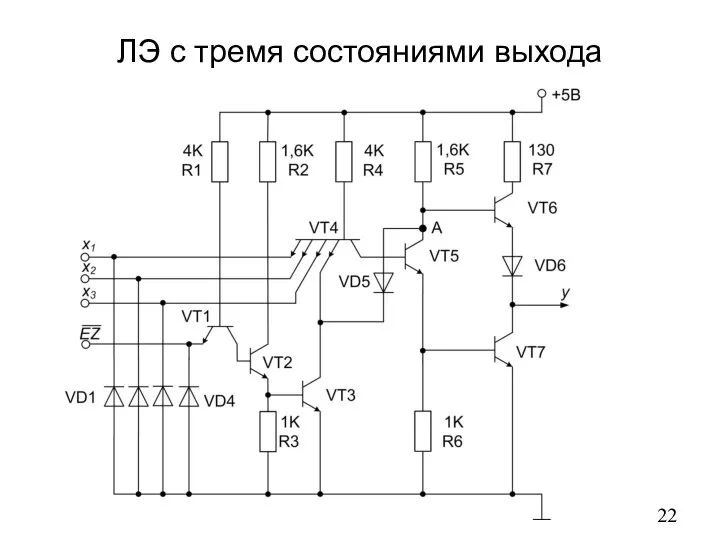

Слайд 15Базовый элемент (БЭ) ТТЛ

Входной

ФР

Выходной

КАСКАДЫ:

входной

R1, VT1, VD1 – VD4;

фазорасщепительный

R2, VT2,

R3, R4, VT3;

выходной

VT4, VT5, VD5, R5

К, Э – расширения по ИЛИ

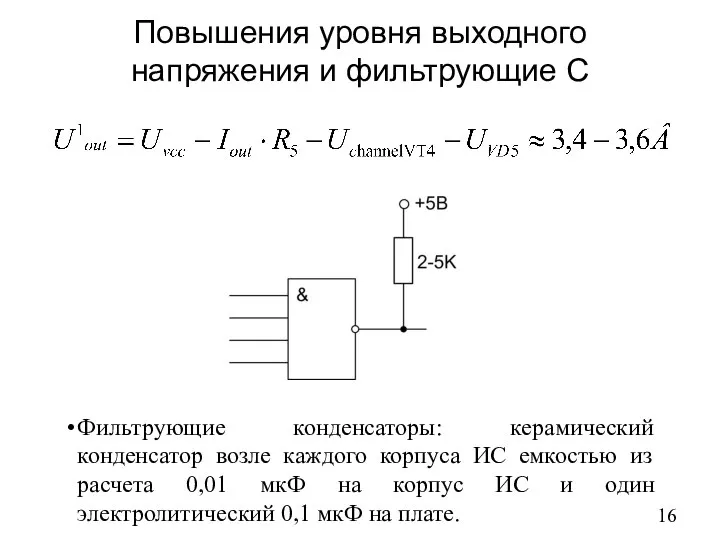

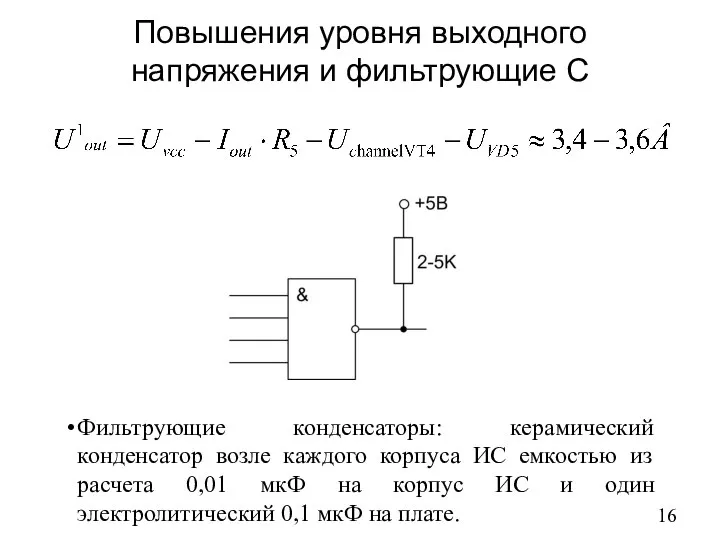

Слайд 16Повышения уровня выходного напряжения и фильтрующие C

Фильтрующие конденсаторы: керамический конденсатор возле каждого

корпуса ИС емкостью из расчета 0,01 мкФ на корпус ИС и один электролитический 0,1 мкФ на плате.

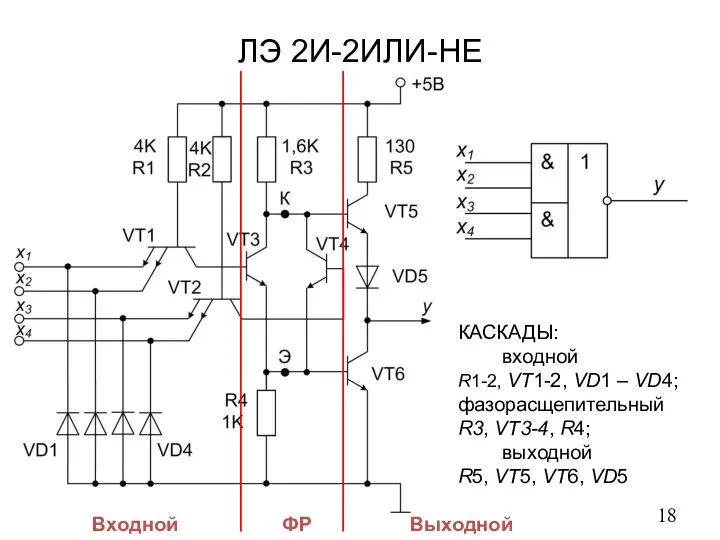

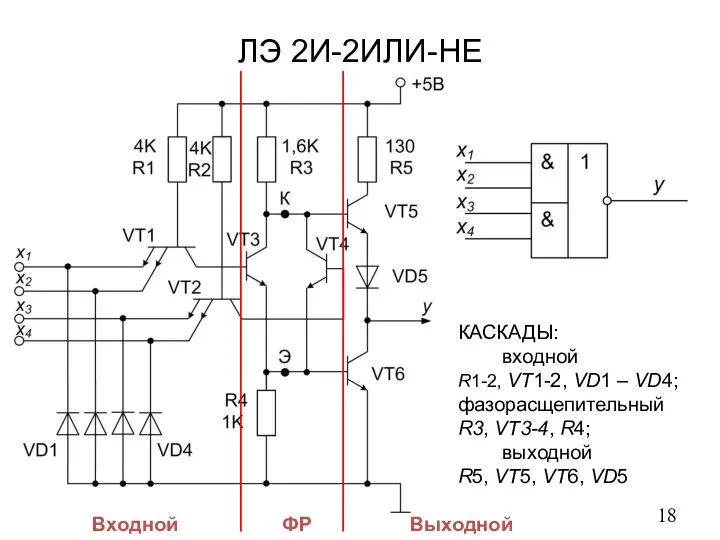

Слайд 18ЛЭ 2И-2ИЛИ-НЕ

Входной

ФР

Выходной

КАСКАДЫ:

входной

R1-2, VT1-2, VD1 – VD4;

фазорасщепительный

R3, VT3-4, R4;

выходной

R5, VT5, VT6, VD5

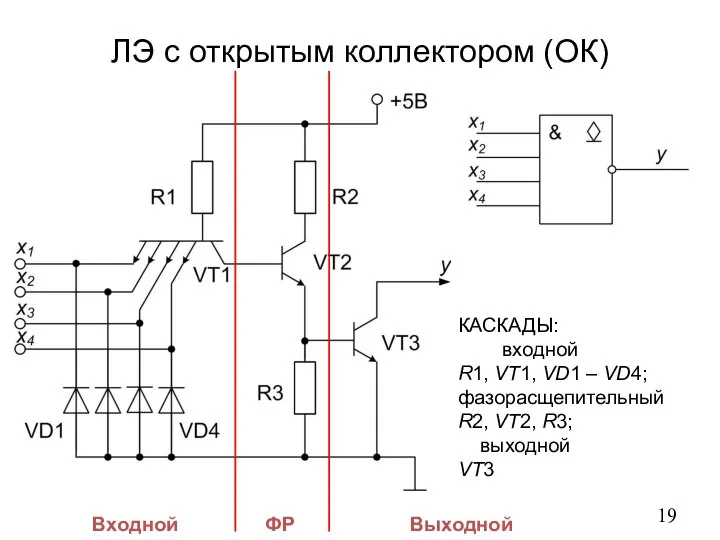

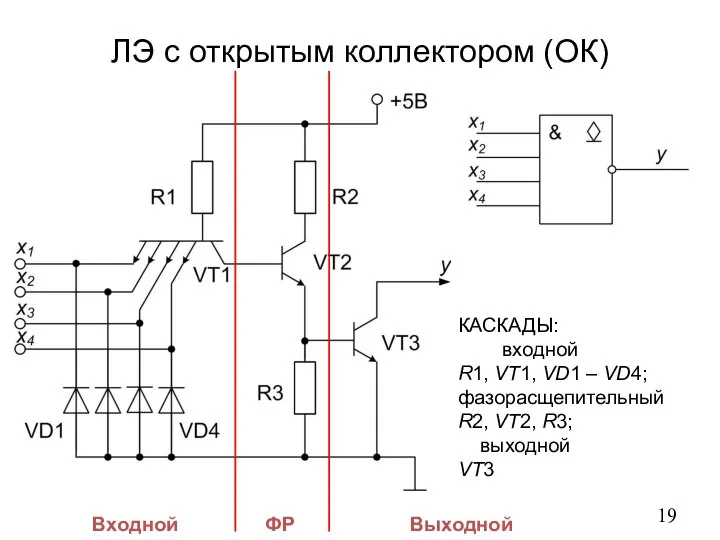

Слайд 19ЛЭ с открытым коллектором (ОК)

Входной

ФР

Выходной

КАСКАДЫ:

входной

R1, VT1, VD1 – VD4;

фазорасщепительный

R2,

VT2, R3;

выходной

VT3

Слайд 23Пример применения ЛЭ с 3-мя состояниями выхода

Асфальтобетонные заводы (АБЗ)

Асфальтобетонные заводы (АБЗ) 1995-1996 учебный год

1995-1996 учебный год Урок гражданственности Донбасса. Береги честь смолоду

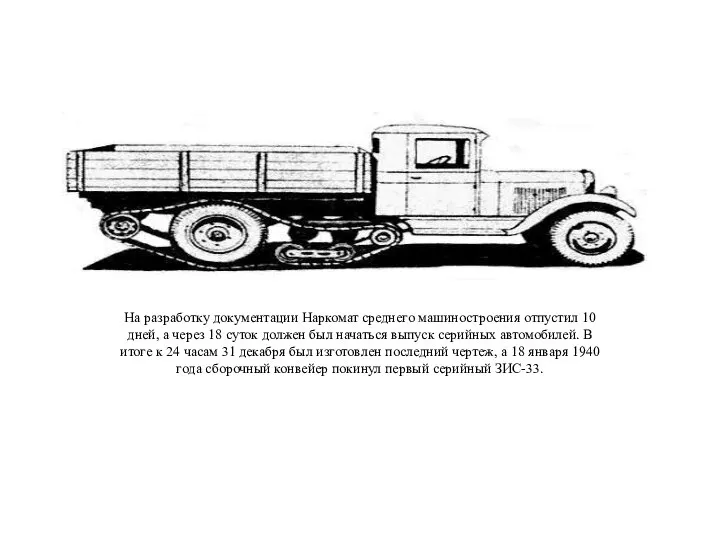

Урок гражданственности Донбасса. Береги честь смолоду Машиностроение

Машиностроение Русская икона IX-XVII веков Виды икон Иконописные сюжеты и образы Символика цвета в иконе.

Русская икона IX-XVII веков Виды икон Иконописные сюжеты и образы Символика цвета в иконе. Основы менеджмента

Основы менеджмента Калужская табачная фабрика. История компании

Калужская табачная фабрика. История компании ОКС Производственноскладское здание

ОКС Производственноскладское здание Презентация на тему Особенности воспитания социальной действительности мальчиками и девочками

Презентация на тему Особенности воспитания социальной действительности мальчиками и девочками Тема

Тема Декорирование современных аксессуаров вышивкой лентами

Декорирование современных аксессуаров вышивкой лентами International. MINE. Awareness day

International. MINE. Awareness day Неопределённая форма глагола

Неопределённая форма глагола ВЛИЯНИЕ ФАМИЛИЙ И ИМЕН КАНДИДАТОВ НА ПРЕДПОЧТЕНИЯ ИЗБИРАТЕЛЕЙ

ВЛИЯНИЕ ФАМИЛИЙ И ИМЕН КАНДИДАТОВ НА ПРЕДПОЧТЕНИЯ ИЗБИРАТЕЛЕЙ Оригами Снеговик

Оригами Снеговик Революция 1905-1907г.г.

Революция 1905-1907г.г. Оборудование для приготовления и продажи напитков

Оборудование для приготовления и продажи напитков Инклюзивное обучение

Инклюзивное обучение Евангелие от Луки 24:13-35

Евангелие от Луки 24:13-35 Коренной перелом в ходе Великой Отечественной войны (9 класс)

Коренной перелом в ходе Великой Отечественной войны (9 класс) Презентация на тему Реакции окисления и восстановления органических соединений

Презентация на тему Реакции окисления и восстановления органических соединений  Международный женский день. Поздравление

Международный женский день. Поздравление Презентация на тему Охрана воды

Презентация на тему Охрана воды  Анализ эффектов реализации КПМО в Республике Карелия

Анализ эффектов реализации КПМО в Республике Карелия Построение треугольников

Построение треугольников Обзор проекта

Обзор проекта Новогодние мероприятия

Новогодние мероприятия Почти круглый стол Макса Вебера

Почти круглый стол Макса Вебера