Содержание

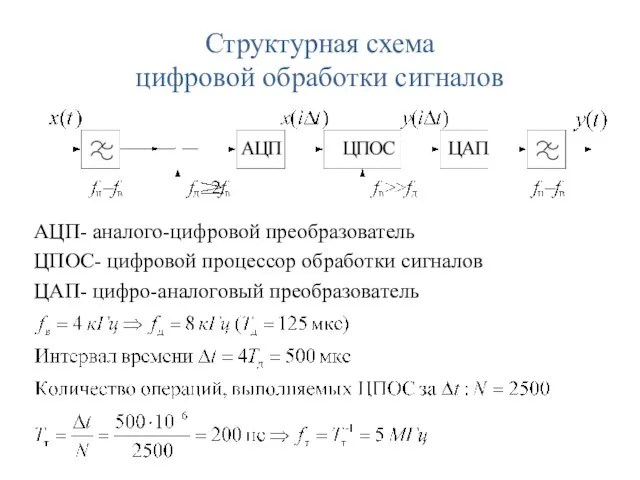

- 2. Структурная схема цифровой обработки сигналов АЦП- аналого-цифровой преобразователь ЦПОС- цифровой процессор обработки сигналов ЦАП- цифро-аналоговый преобразователь

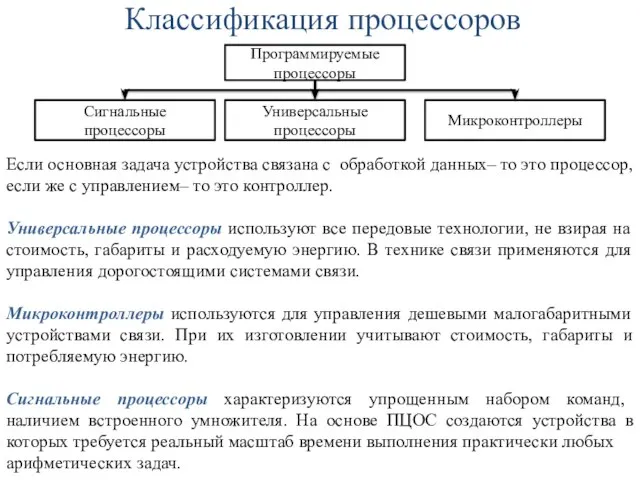

- 3. Если основная задача устройства связана с обработкой данных– то это процессор, если же с управлением– то

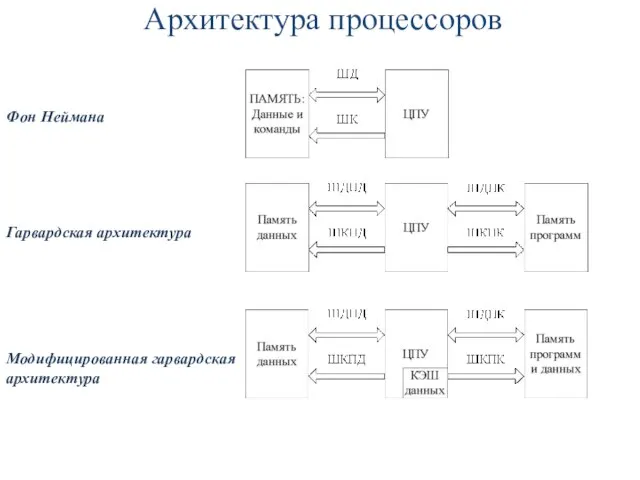

- 4. Архитектура процессоров Фон Неймана Гарвардская архитектура Модифицированная гарвардская архитектура

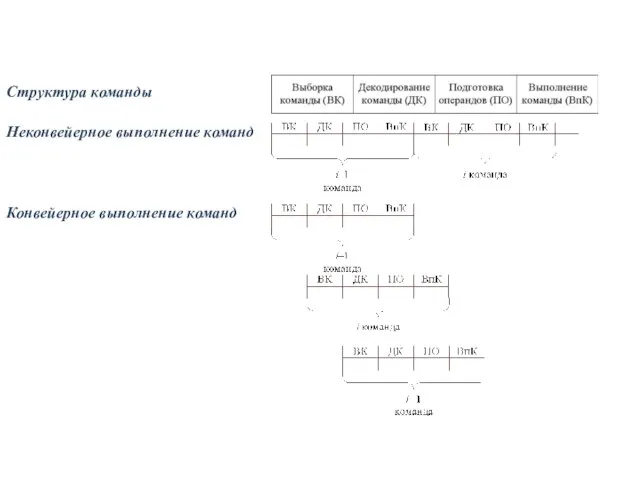

- 5. Неконвейерное выполнение команд Структура команды Конвейерное выполнение команд

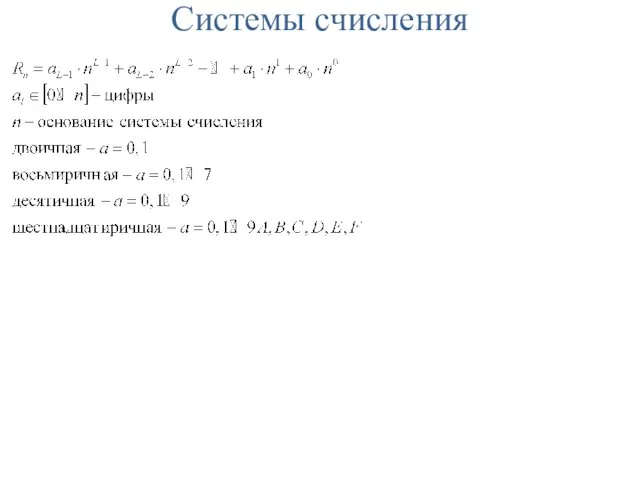

- 6. Системы счисления

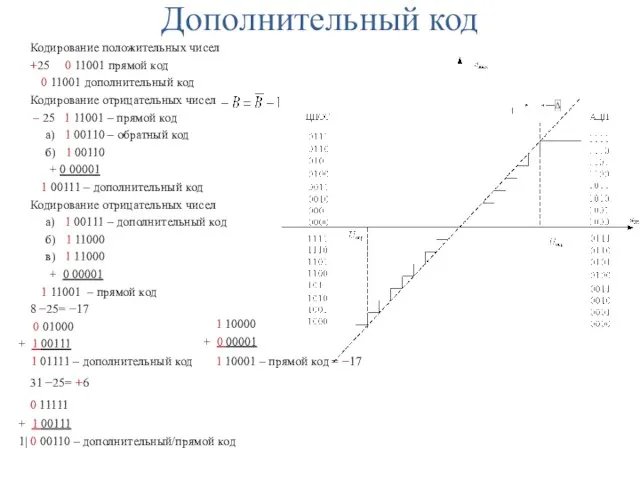

- 7. Дополнительный код Кодирование положительных чисел +25 0 11001 прямой код 0 11001 дополнительный код Кодирование отрицательных

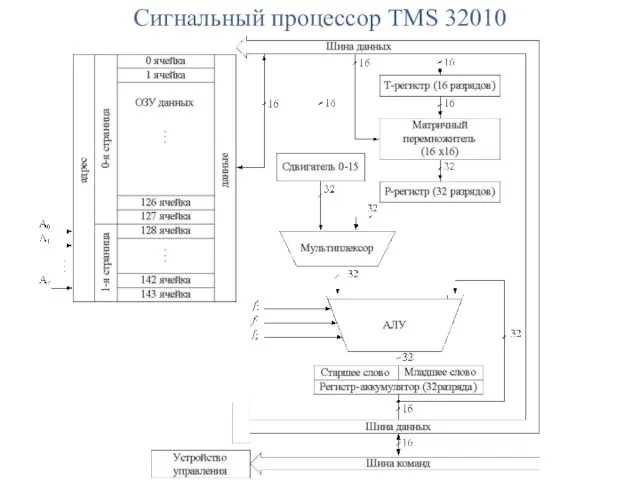

- 8. Сигнальный процессор TMS 32010

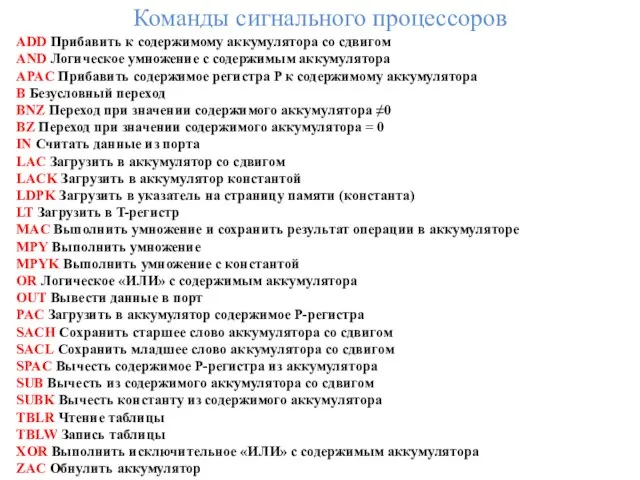

- 9. ADD Прибавить к содержимому аккумулятора со сдвигом AND Логическое умножение с содержимым аккумулятора APAC Прибавить содержимое

- 10. Формирование пилообразного напряжения методом работы накапливающего сумматора

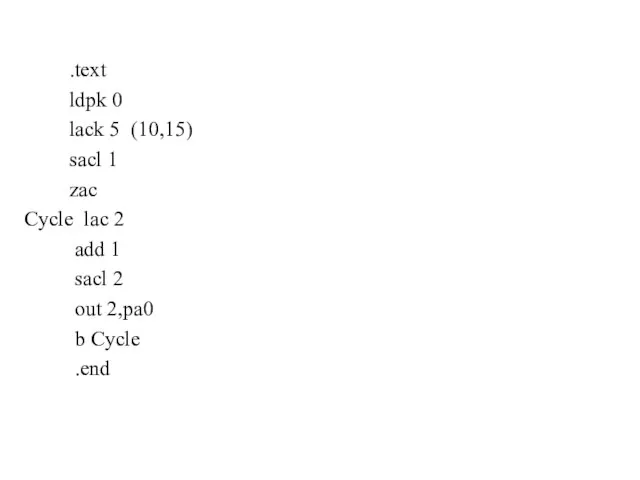

- 11. .text ldpk 0 lack 5 (10,15) sacl 1 zac Cycle lac 2 add 1 sacl 2

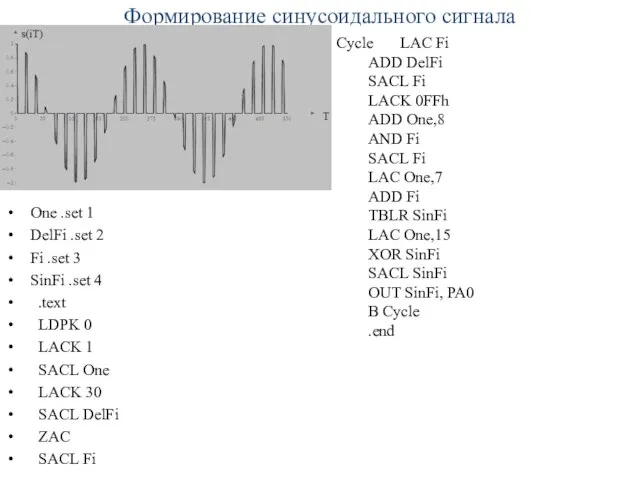

- 12. Формирование синусоидального сигнала One .set 1 DelFi .set 2 Fi .set 3 SinFi .set 4 .text

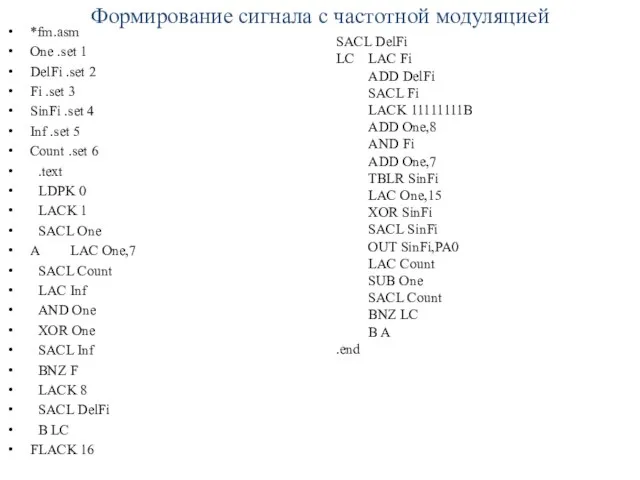

- 13. Формирование сигнала с частотной модуляцией *fm.asm One .set 1 DelFi .set 2 Fi .set 3 SinFi

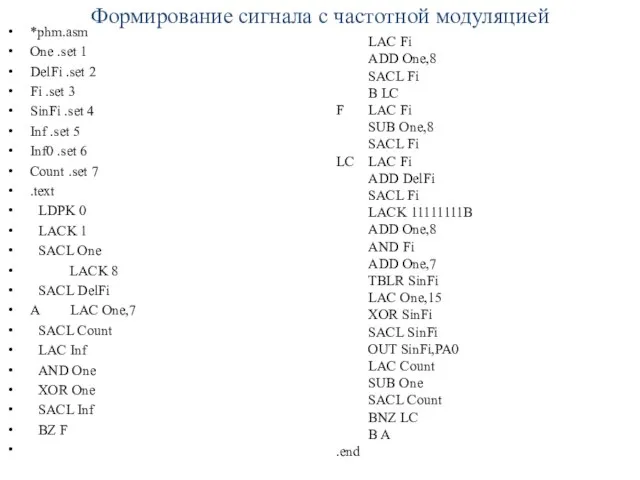

- 14. Формирование сигнала с частотной модуляцией *phm.asm One .set 1 DelFi .set 2 Fi .set 3 SinFi

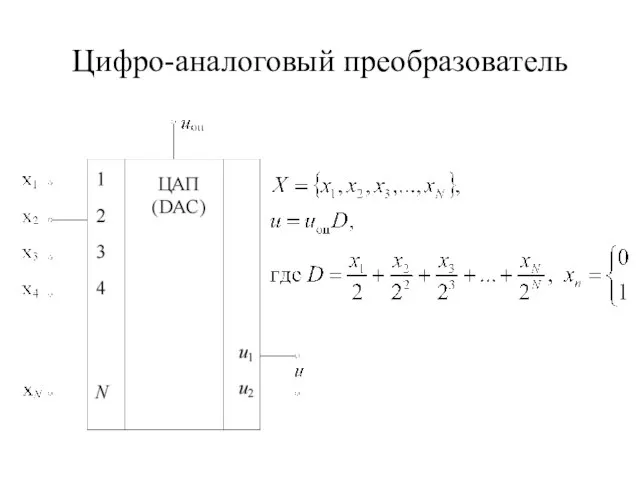

- 15. Цифро-аналоговый преобразователь

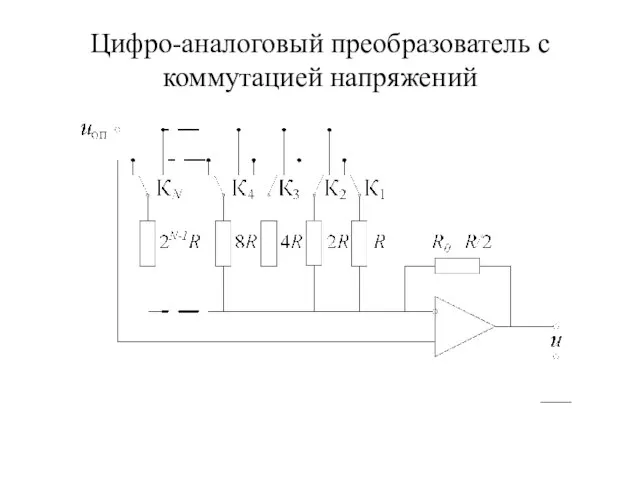

- 16. Цифро-аналоговый преобразователь с коммутацией напряжений

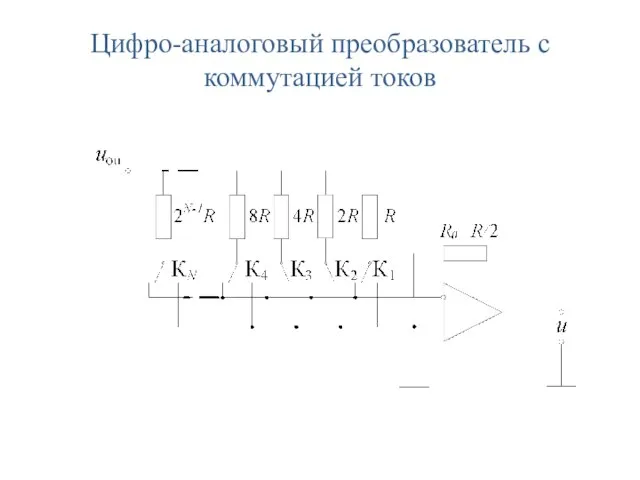

- 17. Цифро-аналоговый преобразователь с коммутацией токов

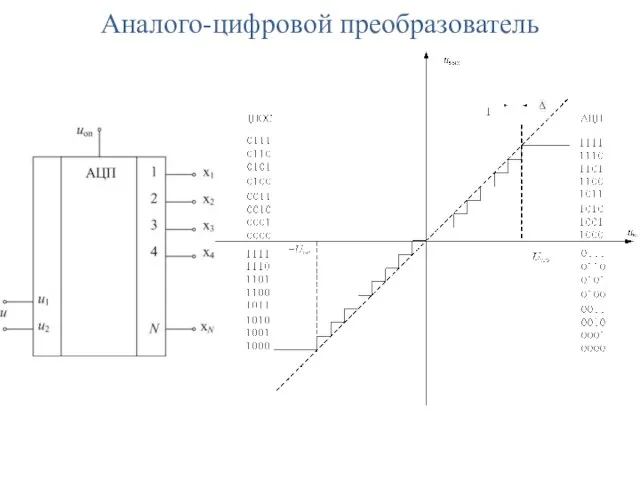

- 18. Аналого-цифровой преобразователь

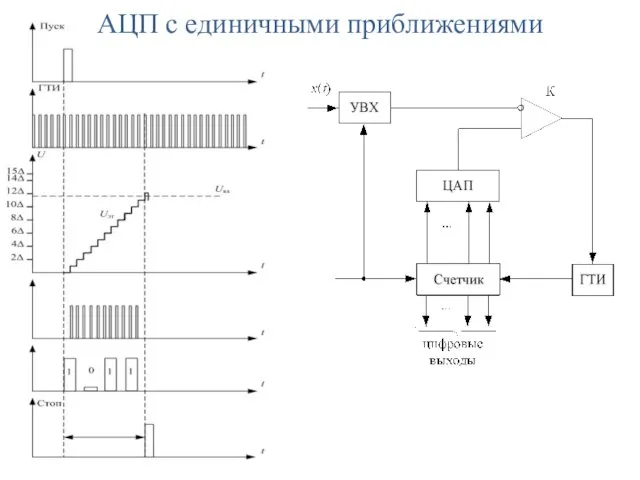

- 19. АЦП с единичными приближениями

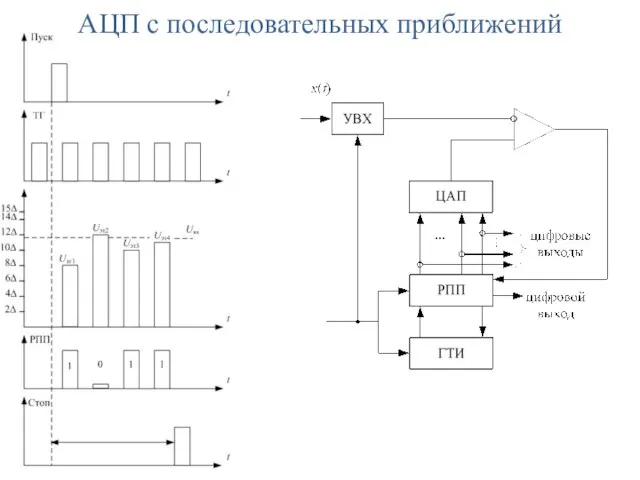

- 20. АЦП с последовательных приближений

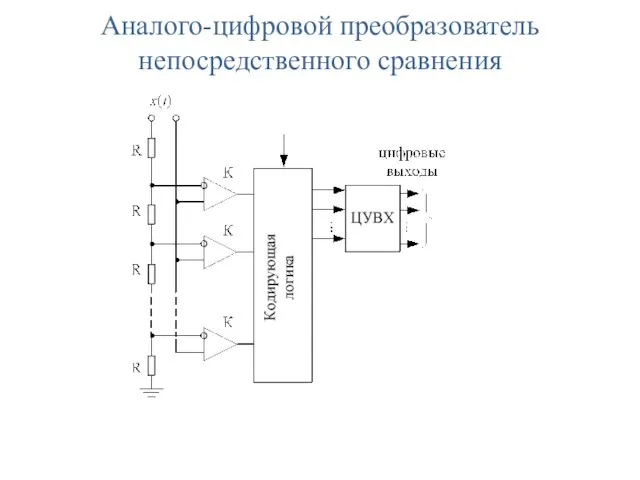

- 21. Аналого-цифровой преобразователь непосредственного сравнения

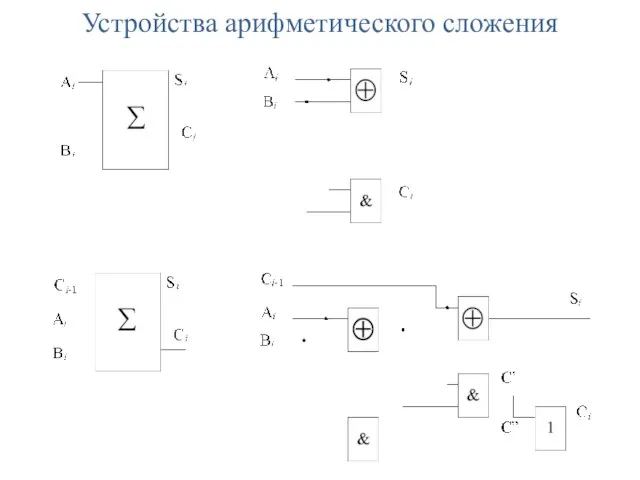

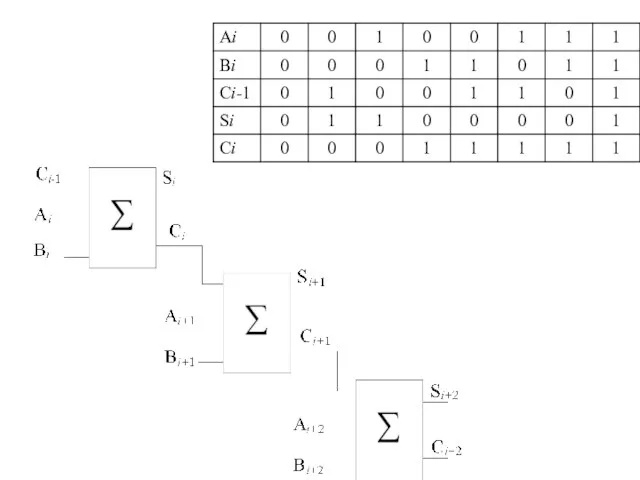

- 22. Устройства арифметического сложения

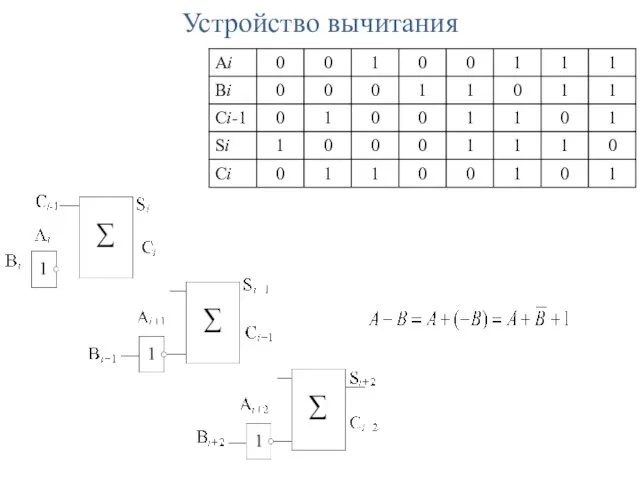

- 24. Устройство вычитания

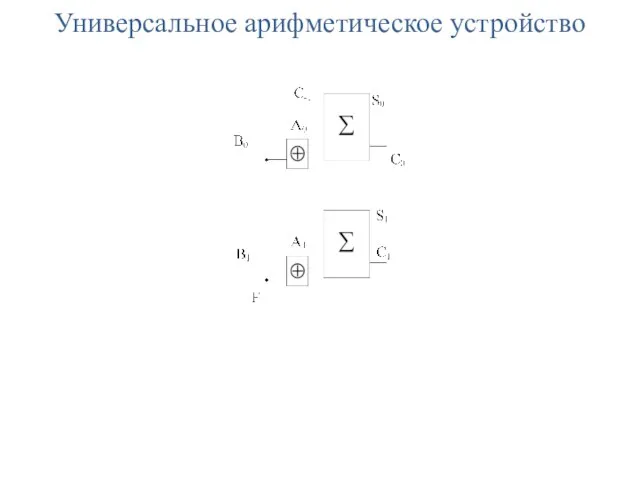

- 25. Универсальное арифметическое устройство

- 26. Арифметико-логическое устройство

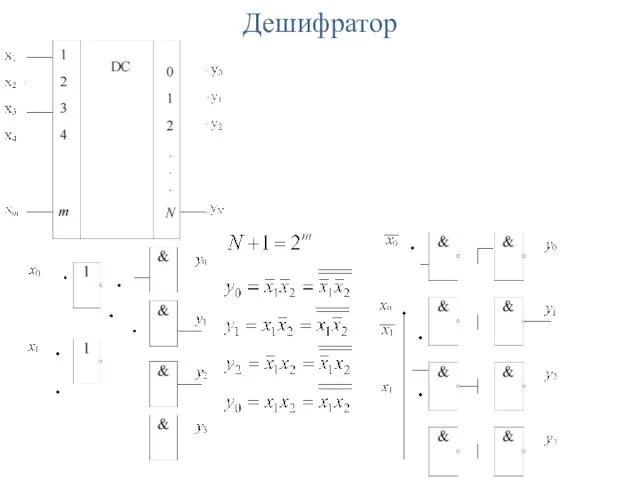

- 27. Дешифратор

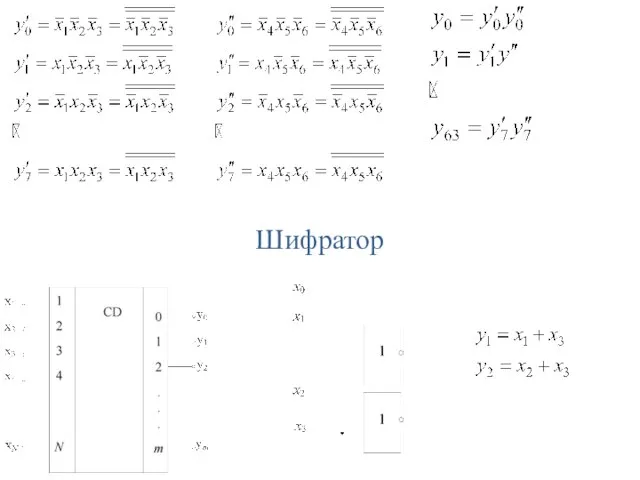

- 28. Шифратор

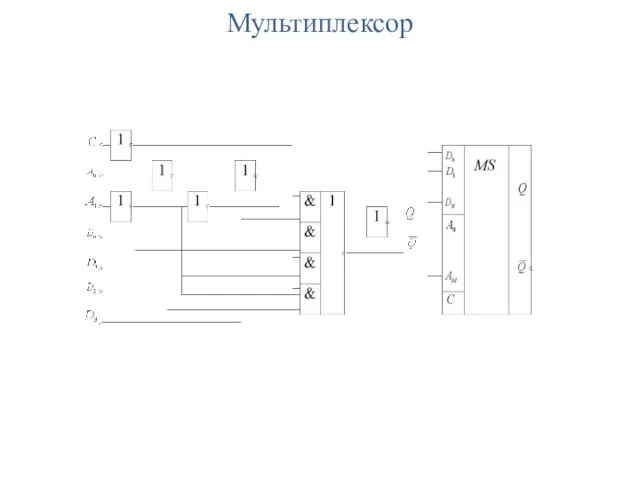

- 29. Мультиплексор

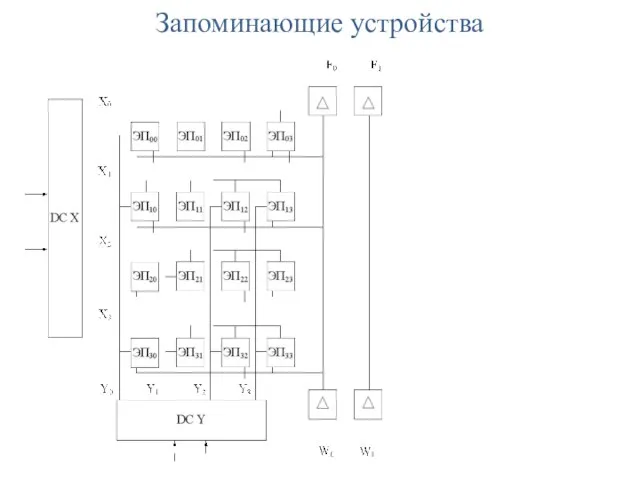

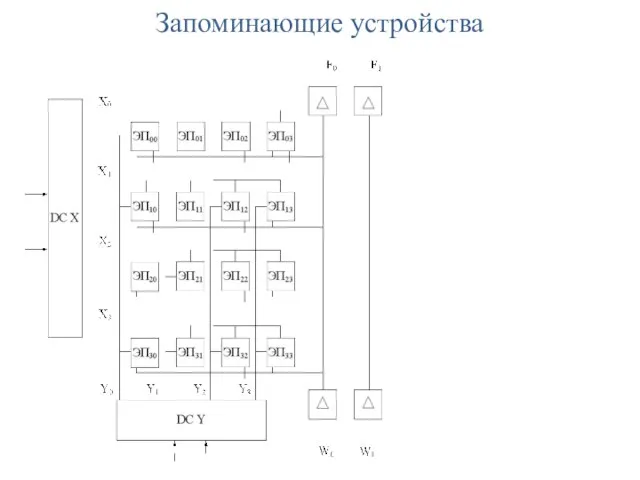

- 30. Запоминающие устройства

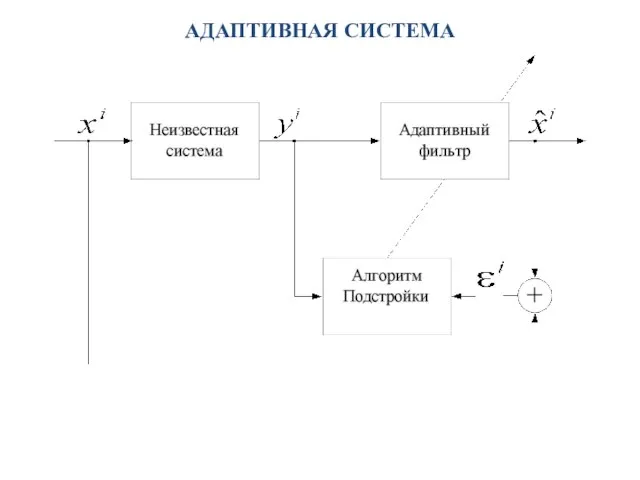

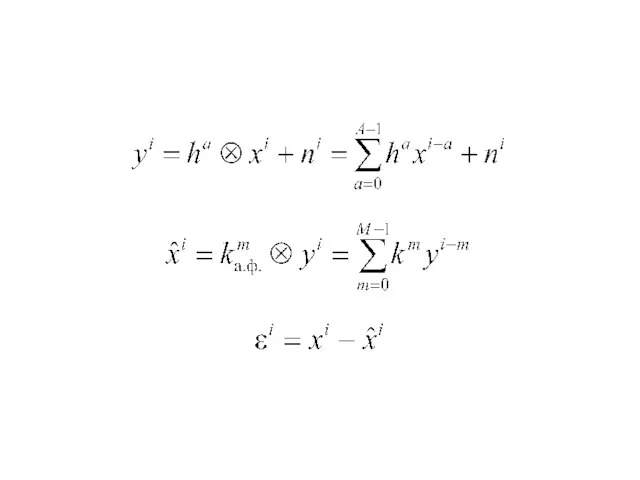

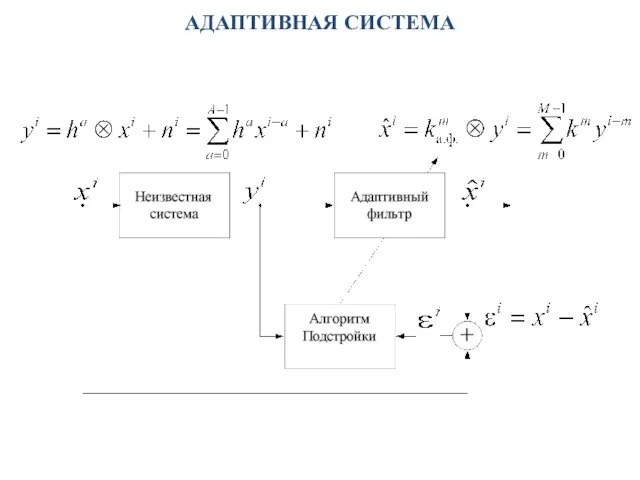

- 31. АДАПТИВНАЯ СИСТЕМА

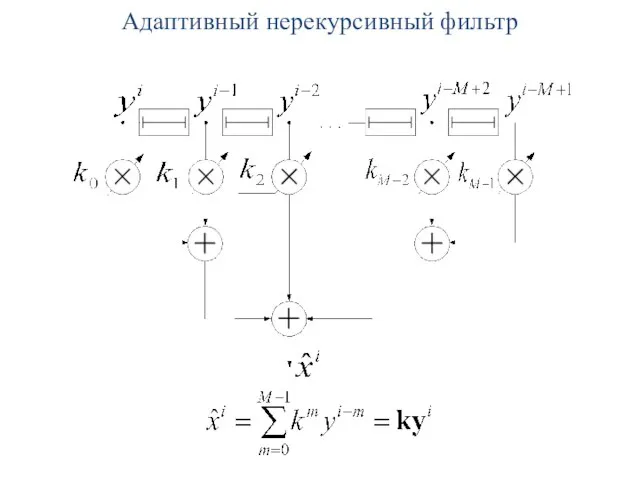

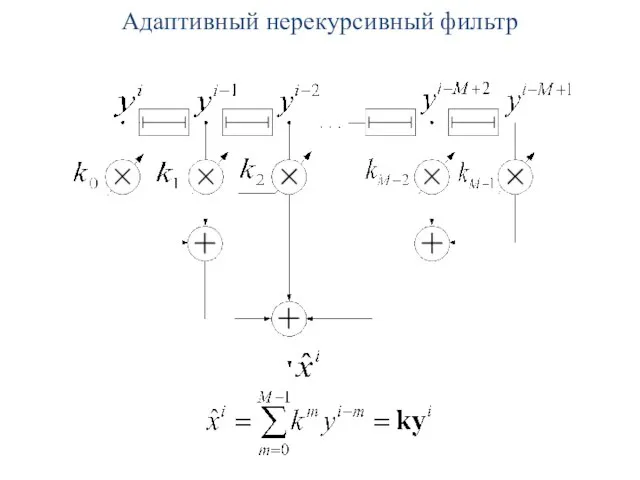

- 33. Адаптивный нерекурсивный фильтр

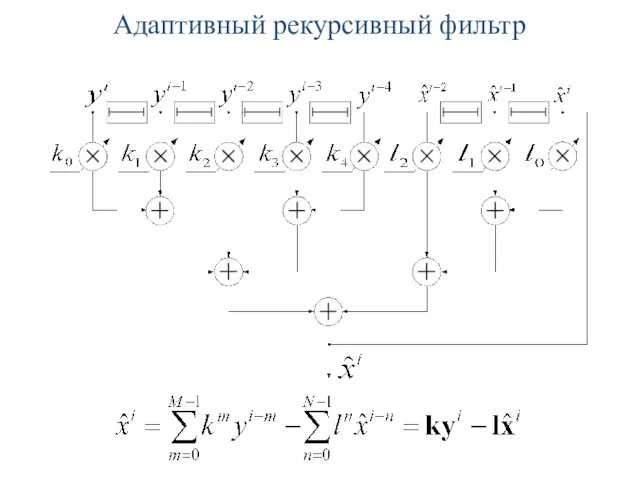

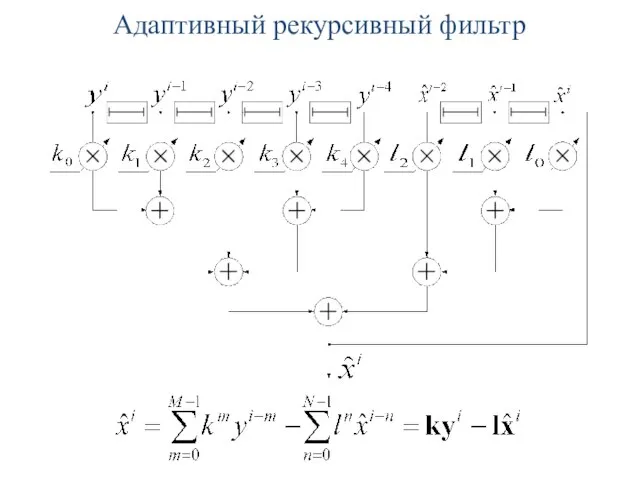

- 34. Адаптивный рекурсивный фильтр

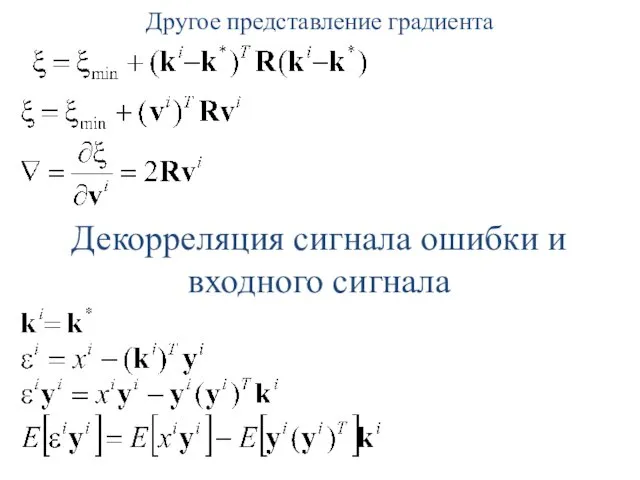

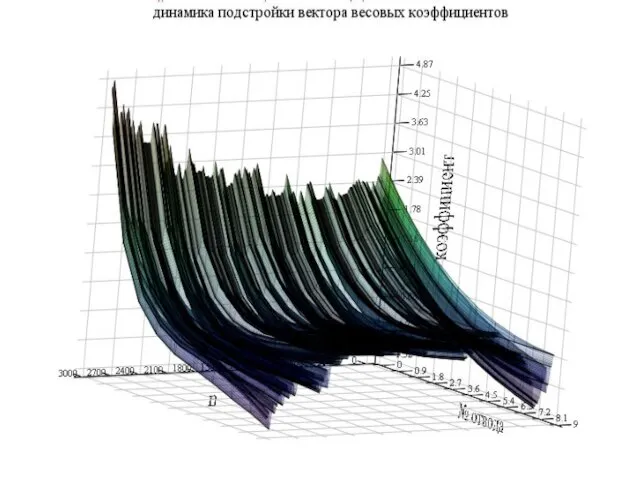

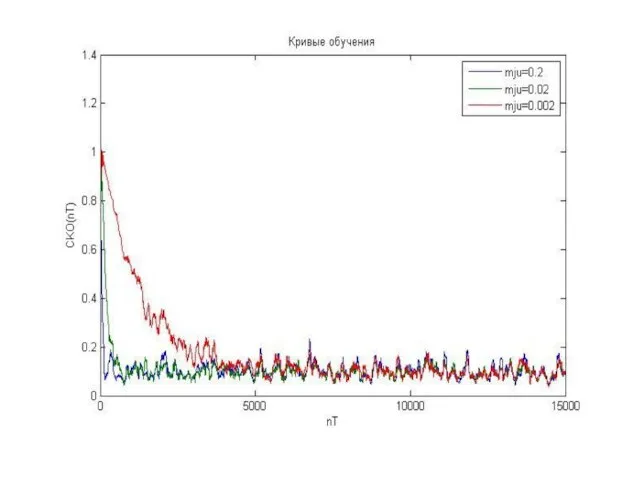

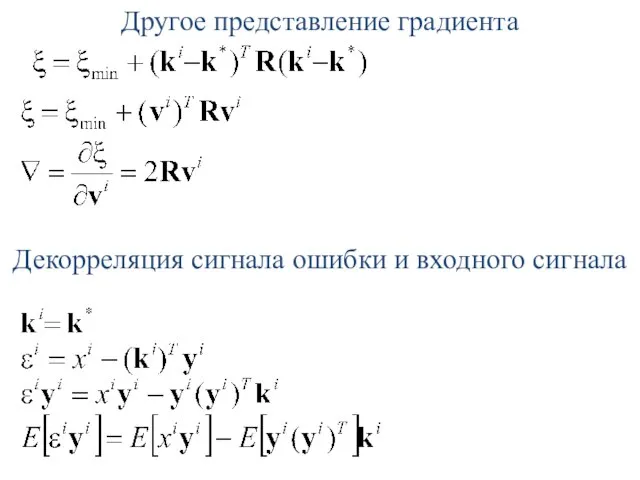

- 36. Другое представление градиента Декорреляция сигнала ошибки и входного сигнала

- 37. Запоминающие устройства

- 38. АДАПТИВНАЯ СИСТЕМА

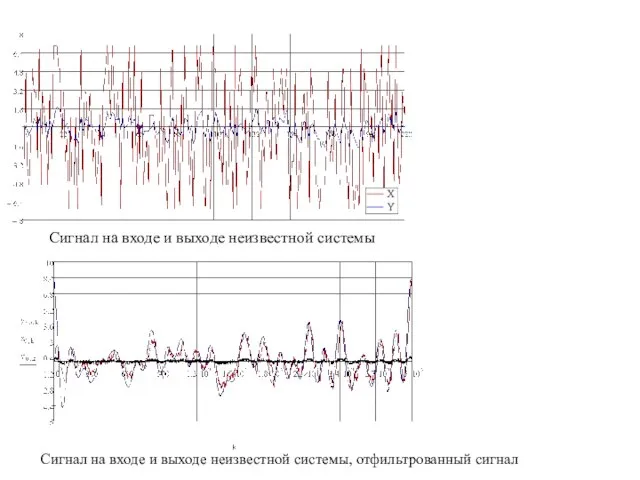

- 39. Сигнал на входе и выходе неизвестной системы Сигнал на входе и выходе неизвестной системы, отфильтрованный сигнал

- 40. Адаптивный нерекурсивный фильтр

- 41. Адаптивный рекурсивный фильтр

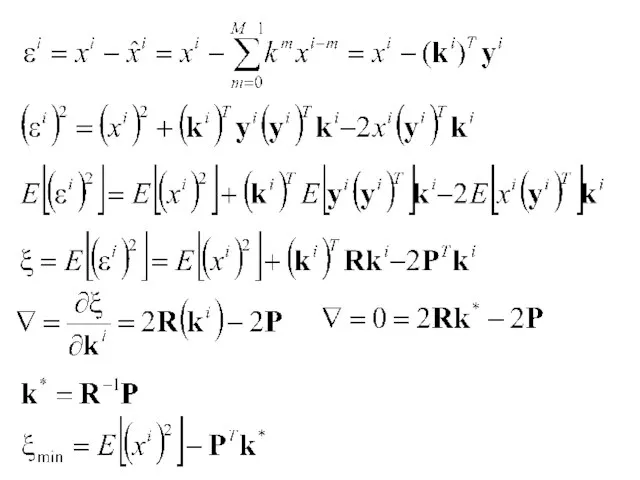

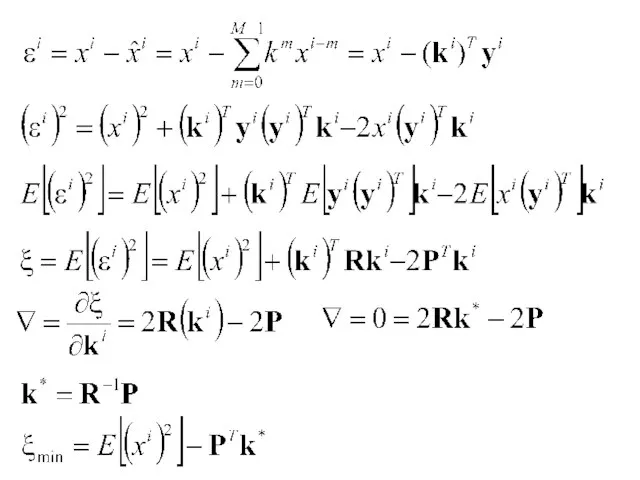

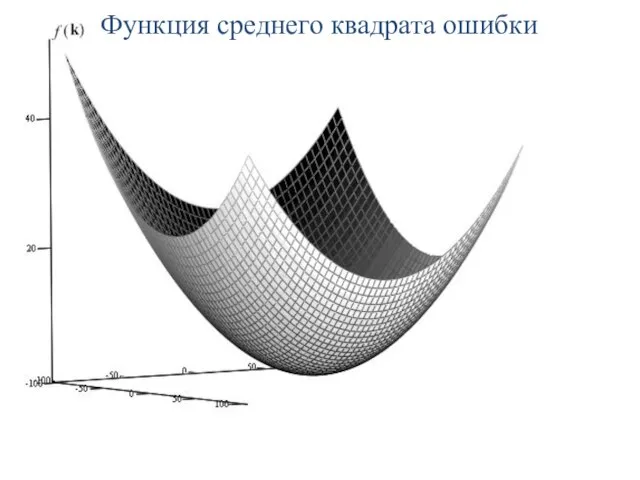

- 43. Функция среднего квадрата ошибки

- 46. Другое представление градиента Декорреляция сигнала ошибки и входного сигнала

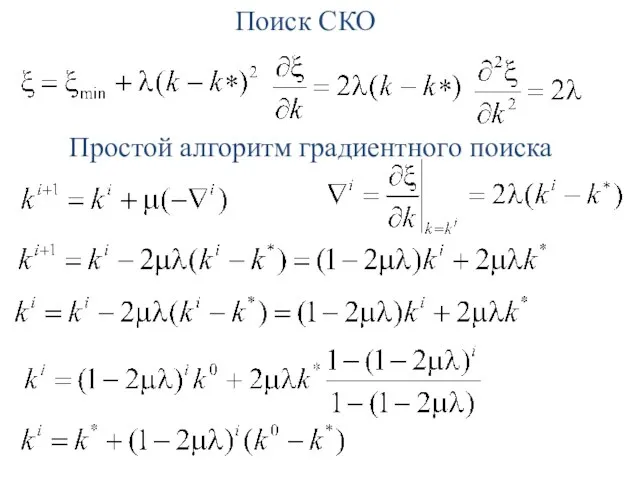

- 47. Поиск СКО Простой алгоритм градиентного поиска

- 49. Скачать презентацию

ПОЛИТИКА КОМПЛЕКТОВАНИЯ ФОНДОВ ЦБС БЕН РАН ОТЕЧЕСТВЕННОЙ ЛИТЕРАТУРОЙ НА СОВРЕМЕННОМ ЭТАПЕ Библиотека по естественным

ПОЛИТИКА КОМПЛЕКТОВАНИЯ ФОНДОВ ЦБС БЕН РАН ОТЕЧЕСТВЕННОЙ ЛИТЕРАТУРОЙ НА СОВРЕМЕННОМ ЭТАПЕ Библиотека по естественным  ГЕОМЕТРИЯ СТРАНЫ ПИРАМИД.

ГЕОМЕТРИЯ СТРАНЫ ПИРАМИД. PrESAGe

PrESAGe Тестирование программных средств

Тестирование программных средств Global Economic Crisis and Belarus

Global Economic Crisis and Belarus Инновации в образовании: мифы и реальность

Инновации в образовании: мифы и реальность Моим стихам, написанным так рано, Что и не знала я, что я - поэт, Сорвавшимся, как брызги из фонтана, Как иск

Моим стихам, написанным так рано, Что и не знала я, что я - поэт, Сорвавшимся, как брызги из фонтана, Как иск 2016-08-08_Ремонт главного насоса

2016-08-08_Ремонт главного насоса Применение ИКТ в мире творчества

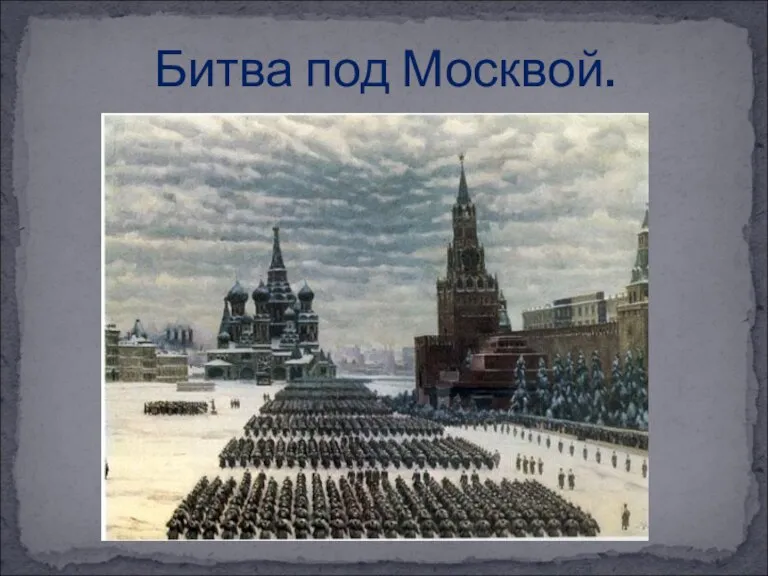

Применение ИКТ в мире творчества Битва под Москвой

Битва под Москвой Мамочка с 8 Марта

Мамочка с 8 Марта Ярославский филиал МИИТ

Ярославский филиал МИИТ Редактор формул Microsoft Equation 3.0

Редактор формул Microsoft Equation 3.0 Логист

Логист 900 дней блокады08.09.1941-2 7.01.1944

900 дней блокады08.09.1941-2 7.01.1944 Презентация на тему Углерод

Презентация на тему Углерод Адаптивная физическая культура для детей специальной медицинской группы здоровья.

Адаптивная физическая культура для детей специальной медицинской группы здоровья. 2011 Год Италии в России

2011 Год Италии в России Виды административно-правовых режимов

Виды административно-правовых режимов Утилизация шлама в оксид магния и карналлит

Утилизация шлама в оксид магния и карналлит Как встречают Новый годи Рождество в разных странах

Как встречают Новый годи Рождество в разных странах «Классный час – одна из ведущих норм деятельности классного руководителя»

«Классный час – одна из ведущих норм деятельности классного руководителя» Химические средства гигиены и косметики

Химические средства гигиены и косметики Презентация на тему Методы географических исследований и основные источники географической информации

Презентация на тему Методы географических исследований и основные источники географической информации  Художественные стили XVII –XVIII веков

Художественные стили XVII –XVIII веков Точная линия

Точная линия Презентация на тему день мира 21 сентября

Презентация на тему день мира 21 сентября  Письмо 5 класс

Письмо 5 класс