Содержание

- 2. Тема: №1 «Арифметические и логические основы цифровых устройств» Тема: №2 «Основы теории цифровых автоматов» Тема: №3

- 3. Тема: №1 «Арифметические и логические основы цифровых устройств» Назад Частный случай цифрового автомата Основные законы алгебры

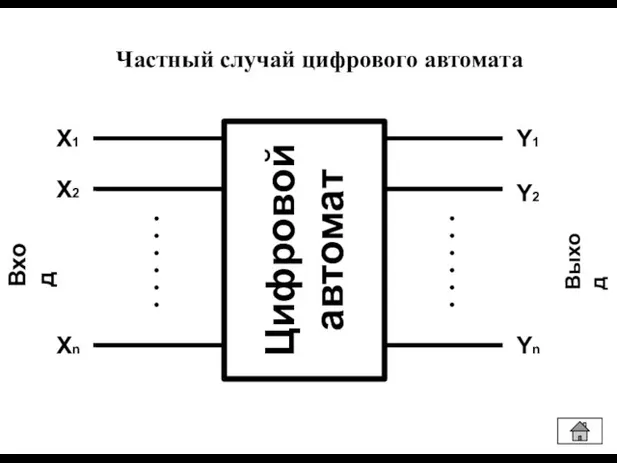

- 4. Частный случай цифрового автомата

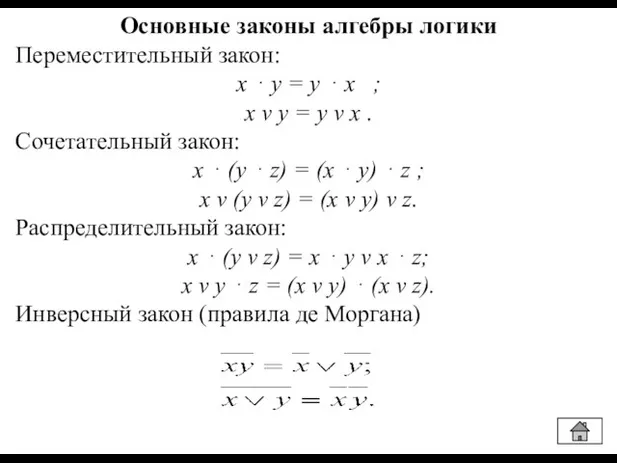

- 5. Основные законы алгебры логики Переместительный закон: x ⋅ у = у ⋅ х ; х v

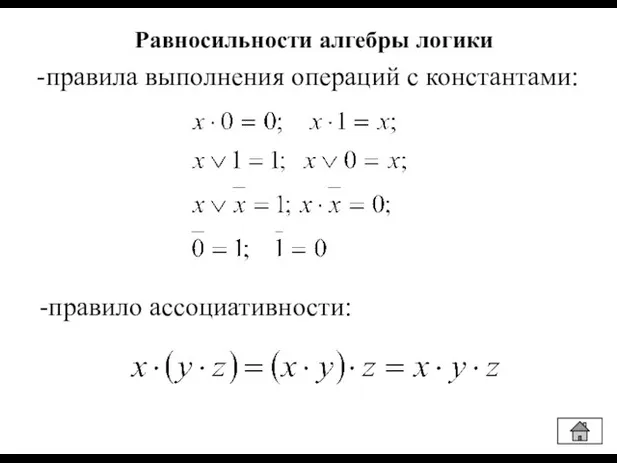

- 6. Равносильности алгебры логики -правила выполнения операций с константами: -правило ассоциативности:

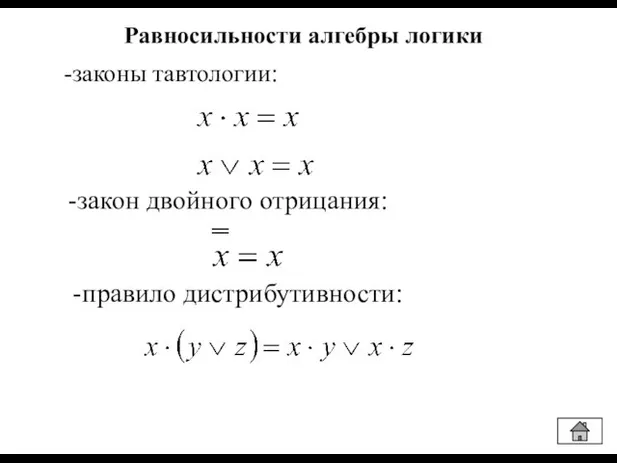

- 7. -законы тавтологии: -закон двойного отрицания: -правило дистрибутивности: Равносильности алгебры логики

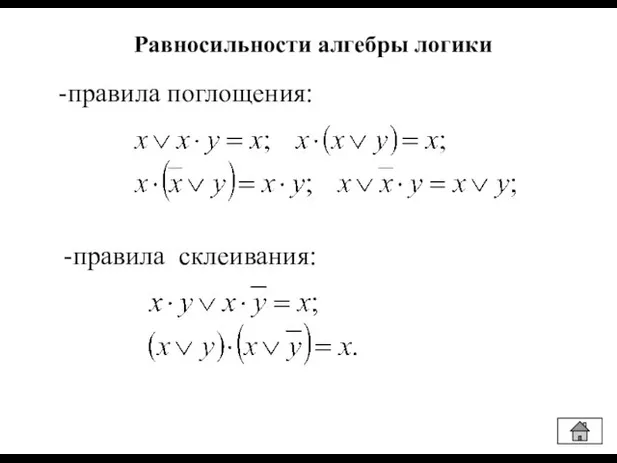

- 8. -правила поглощения: -правила склеивания: Равносильности алгебры логики

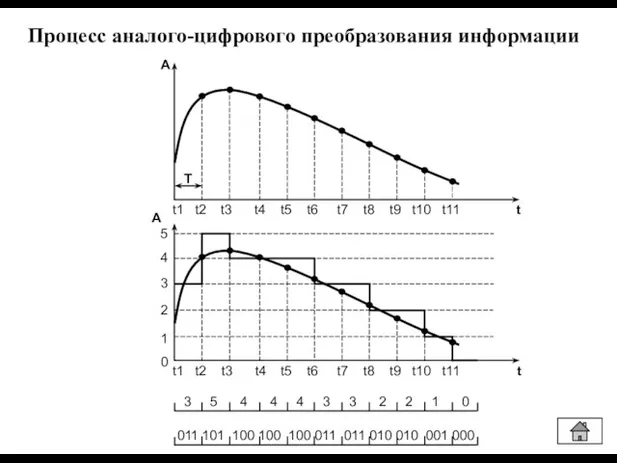

- 9. Процесс аналого-цифрового преобразования информации А t1 t2 t3 t4 t5 t6 t7 t8 t9 t10 t11

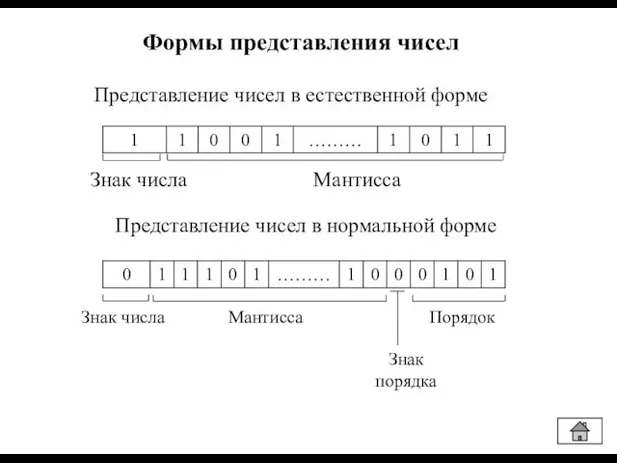

- 10. Формы представления чисел Знак числа Мантисса Знак числа Мантисса Порядок Представление чисел в естественной форме Представление

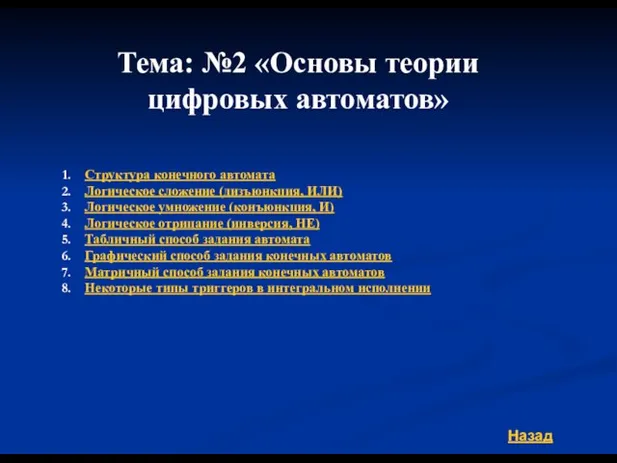

- 11. Тема: №2 «Основы теории цифровых автоматов» Назад Структура конечного автомата Логическое сложение (дизъюнкция, ИЛИ) Логическое умножение

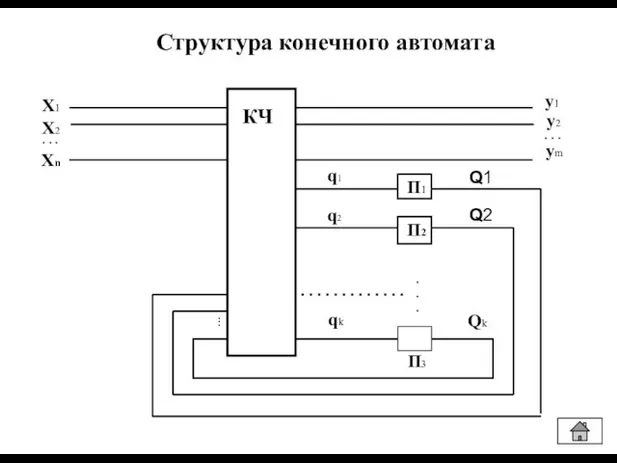

- 12. Структура конечного автомата . . . . . .

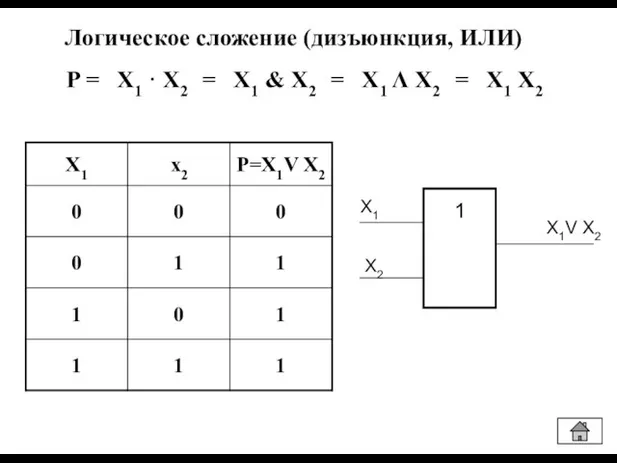

- 13. Логическое сложение (дизъюнкция, ИЛИ) P = X1 · X2 = X1 & X2 = X1 Λ

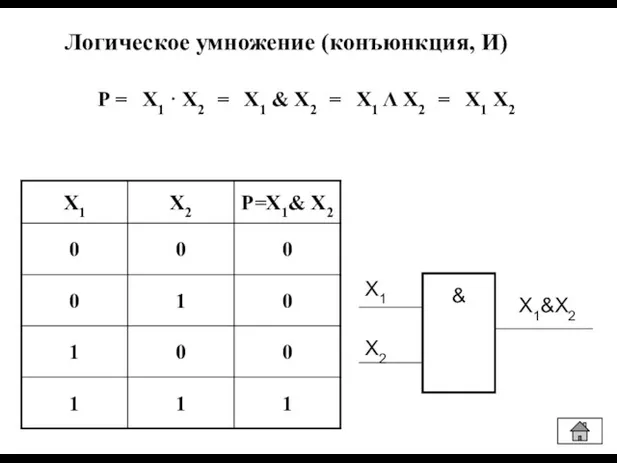

- 14. P = X1 · X2 = X1 & X2 = X1 Λ X2 = X1 X2

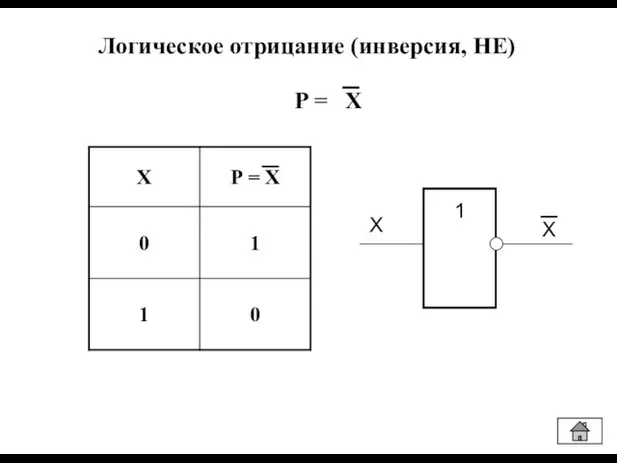

- 15. 1 X P = X Логическое отрицание (инверсия, НЕ)

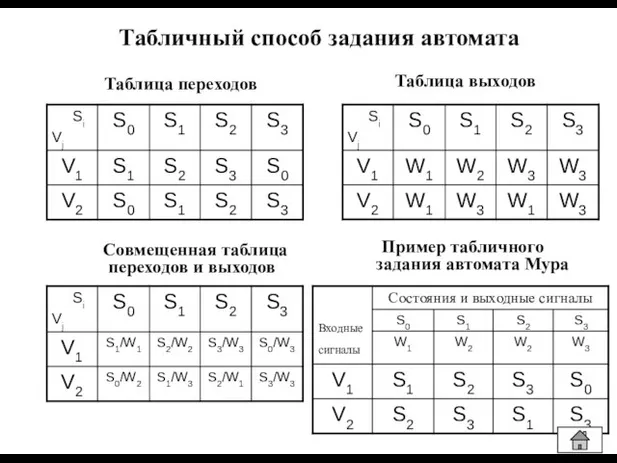

- 16. Табличный способ задания автомата Таблица переходов Таблица выходов Совмещенная таблица переходов и выходов Пример табличного задания

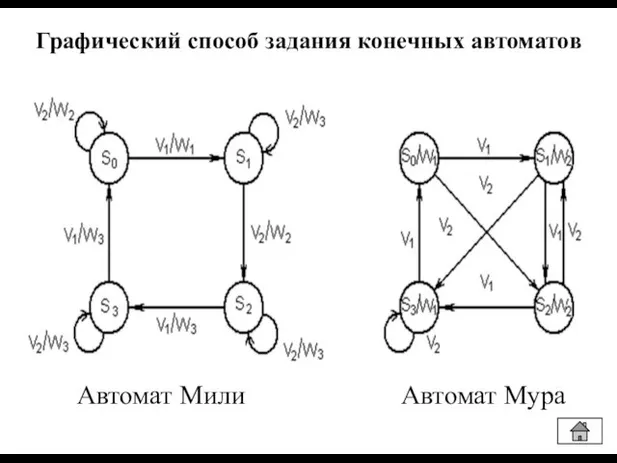

- 17. Автомат Мили Автомат Мура Графический способ задания конечных автоматов

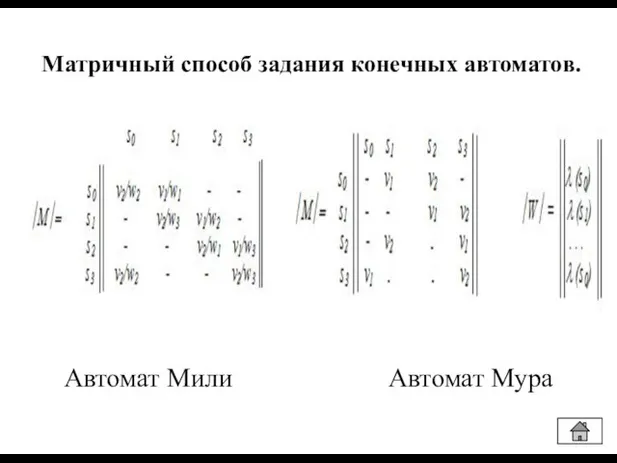

- 18. Матричный способ задания конечных автоматов. Автомат Мили Автомат Мура

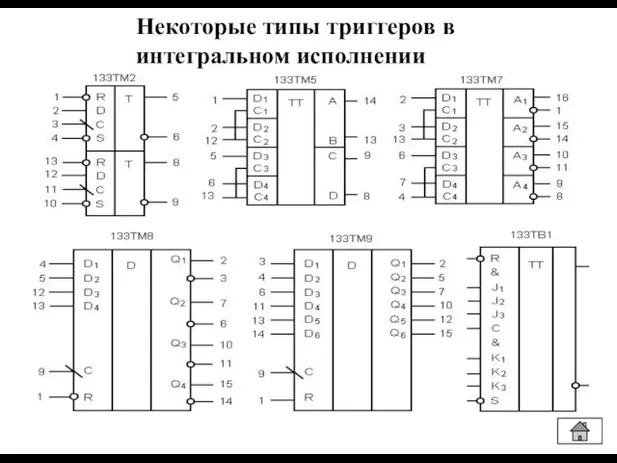

- 19. Некоторые типы триггеров в интегральном исполнении

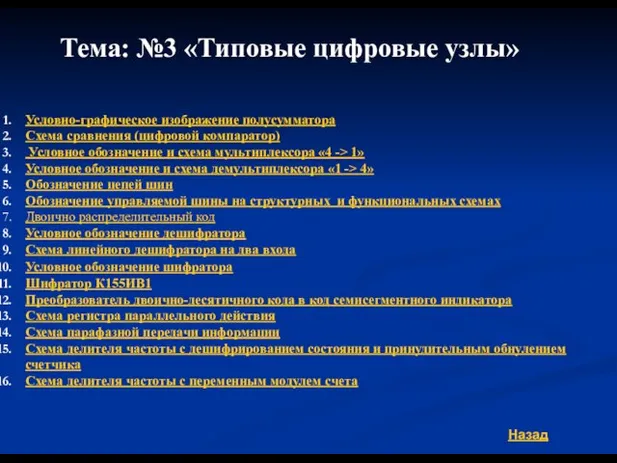

- 20. Тема: №3 «Типовые цифровые узлы» Назад Условно-графическое изображение полусумматора Схема сравнения (цифровой компаратор) Условное обозначение и

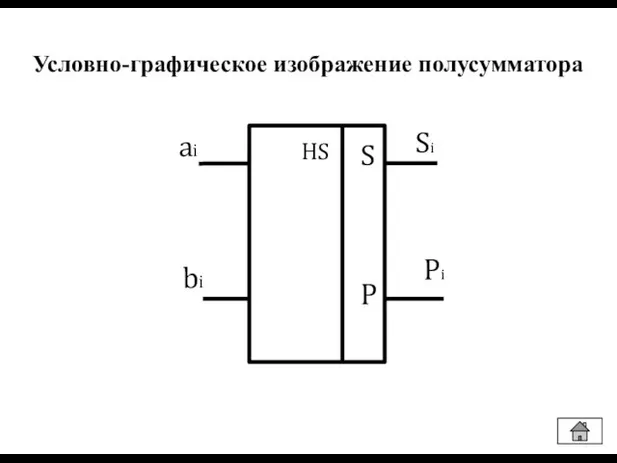

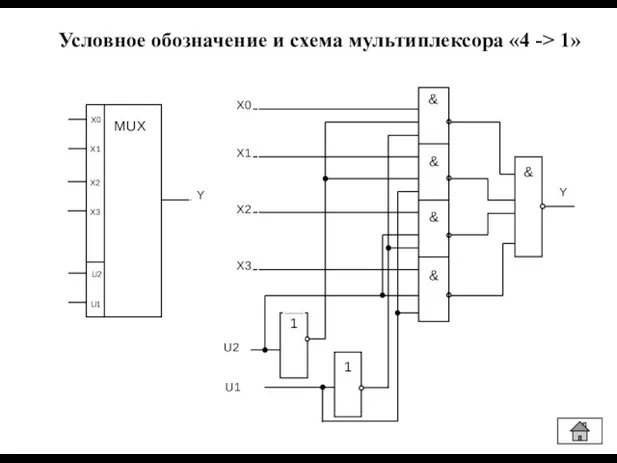

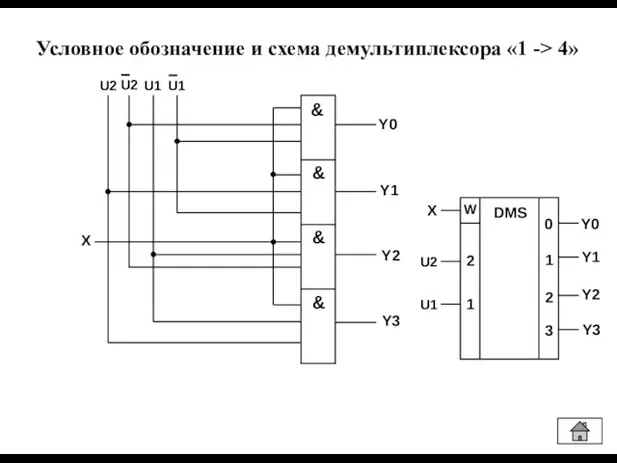

- 21. Условно-графическое изображение полусумматора

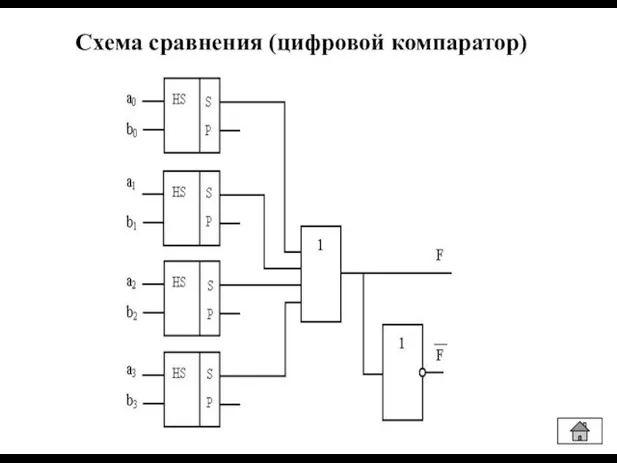

- 22. Схема сравнения (цифровой компаратор)

- 23. Условное обозначение и схема мультиплексора «4 -> 1»

- 24. Условное обозначение и схема демультиплексора «1 -> 4» Х & & & & U2 U2 U1

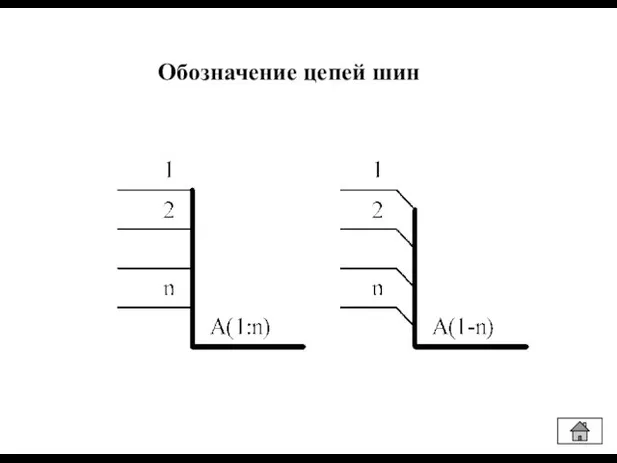

- 25. Обозначение цепей шин

- 26. Обозначение управляемой шины на структурных и функциональных схемах

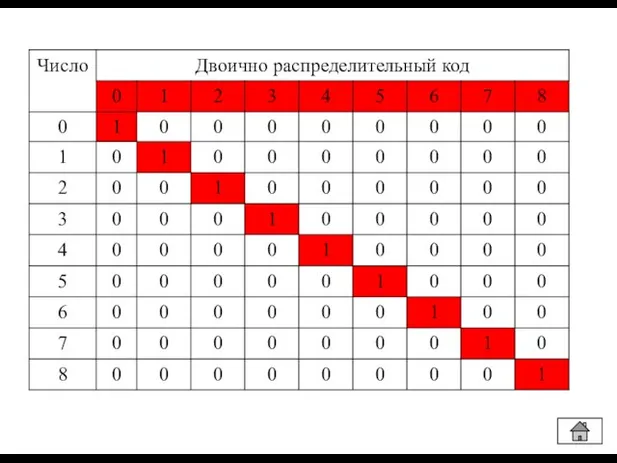

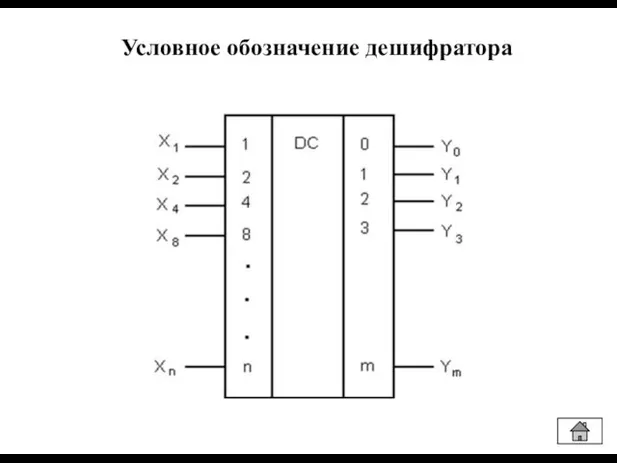

- 28. Условное обозначение дешифратора

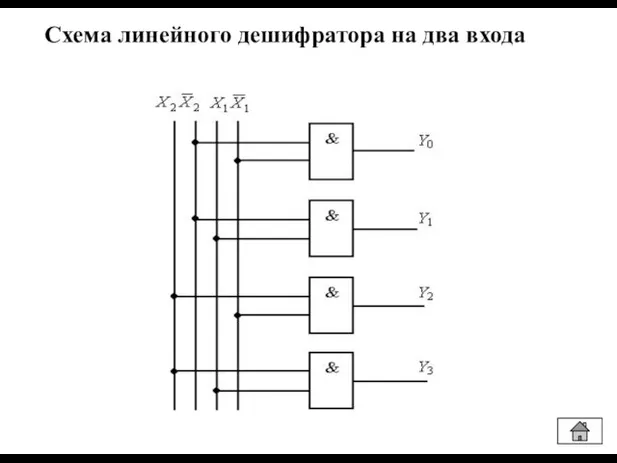

- 29. Схема линейного дешифратора на два входа

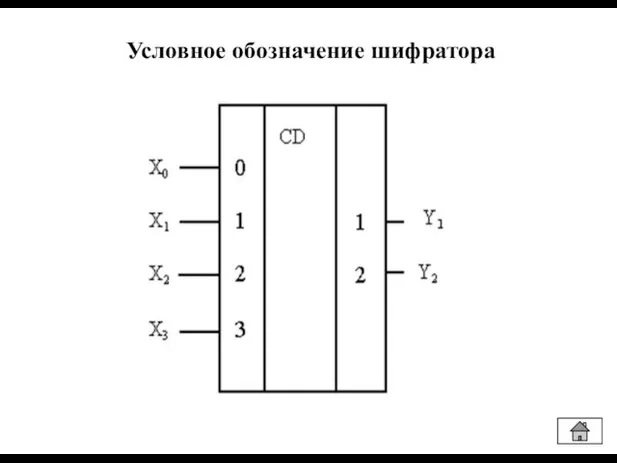

- 30. Условное обозначение шифратора

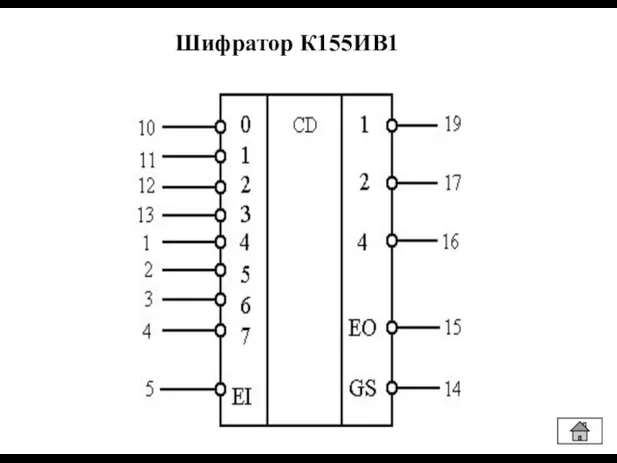

- 31. Шифратор К155ИВ1

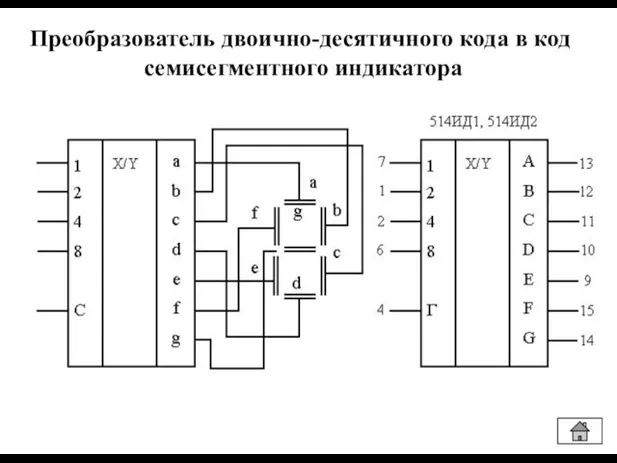

- 32. Преобразователь двоично-десятичного кода в код семисегментного индикатора

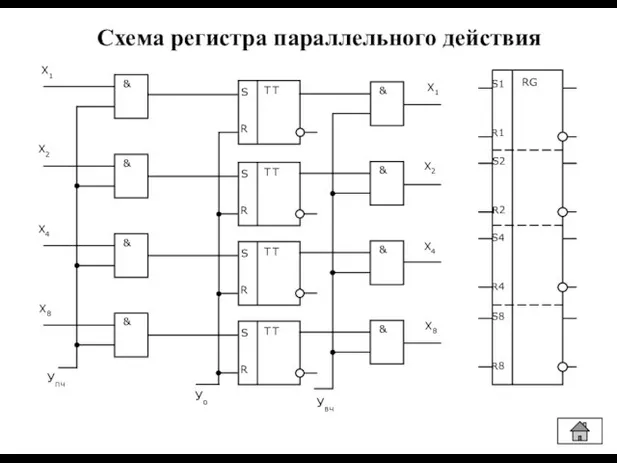

- 33. Схема регистра параллельного действия

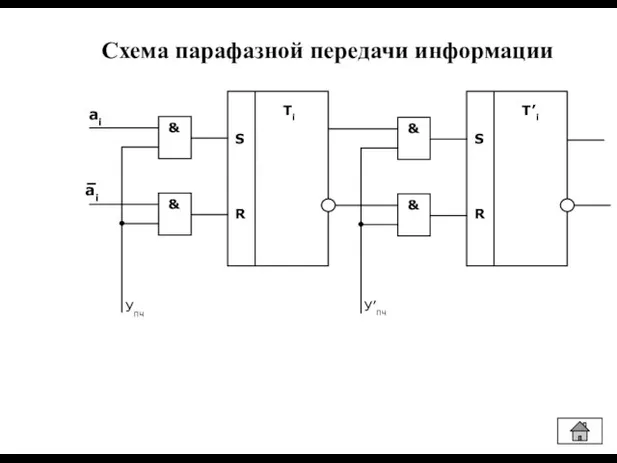

- 34. Схема парафазной передачи информации

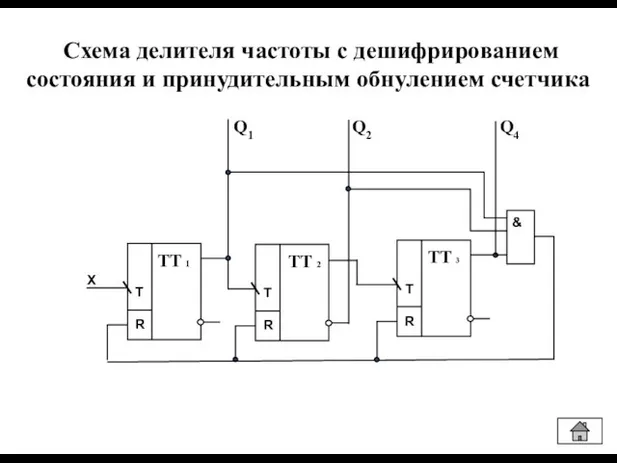

- 35. Схема делителя частоты с дешифрированием состояния и принудительным обнулением счетчика R T TT 1 X R

- 36. Схема делителя частоты с переменным модулем счета

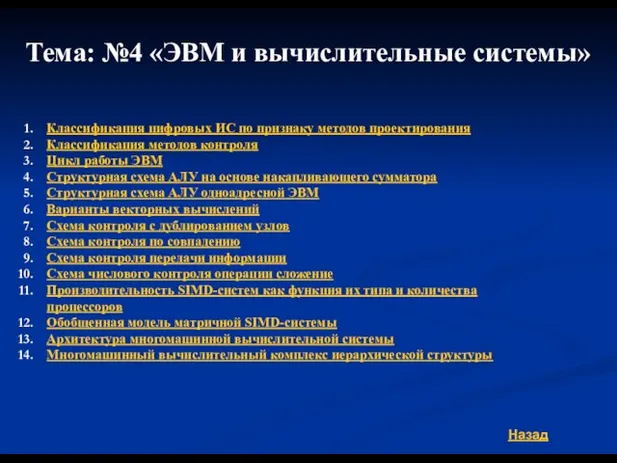

- 37. Тема: №4 «ЭВМ и вычислительные системы» Назад Классификация цифровых ИС по признаку методов проектирования Классификация методов

- 38. Классификация цифровых ИС по признаку методов проектирования Цифровые ИС Стандартные Полузаказные БМК (MPGA) Заказные МИС СИС

- 39. Классификация методов контроля

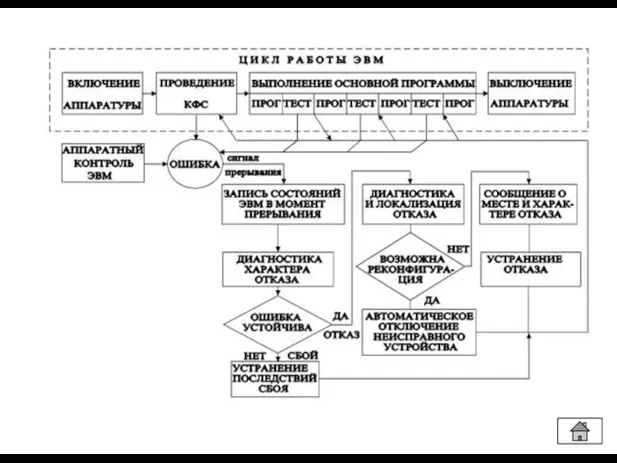

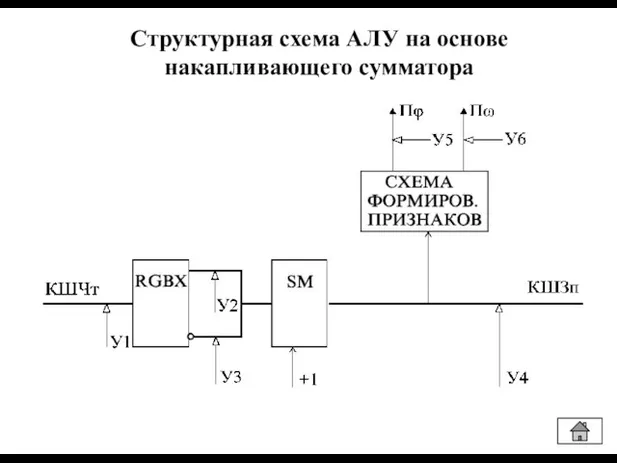

- 41. Структурная схема АЛУ на основе накапливающего сумматора

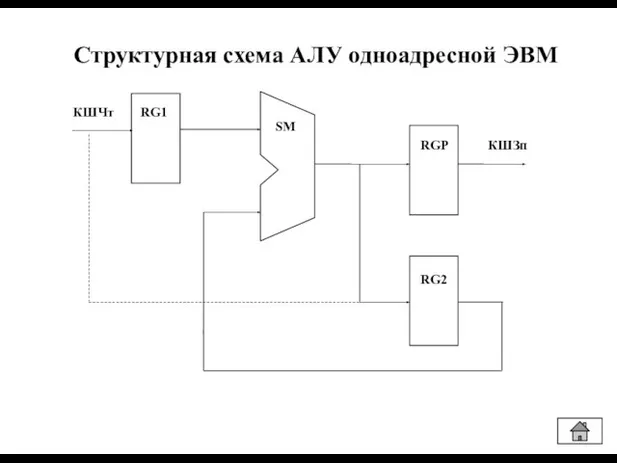

- 42. КШЧт КШЗп RG1 SM RGP RG2 Структурная схема АЛУ одноадресной ЭВМ

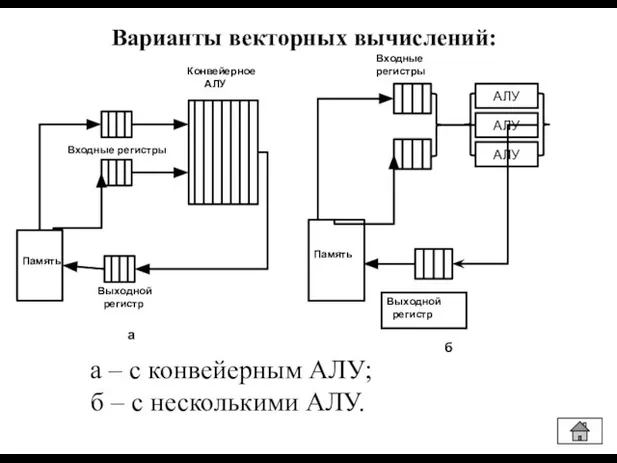

- 43. а – с конвейерным АЛУ; б – с несколькими АЛУ. Варианты векторных вычислений: а б

- 44. Схема контроля с дублированием узлов

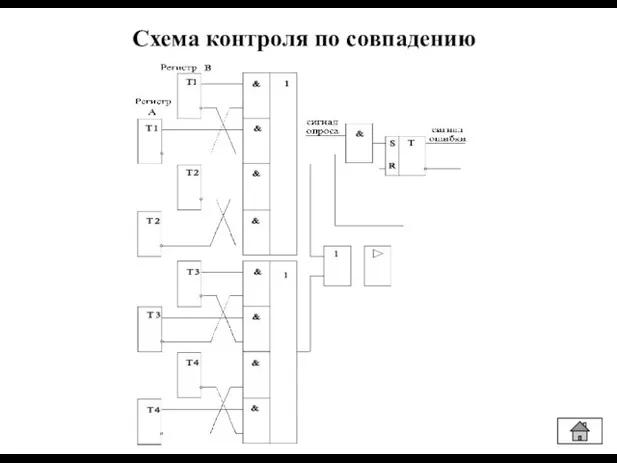

- 45. Схема контроля по совпадению

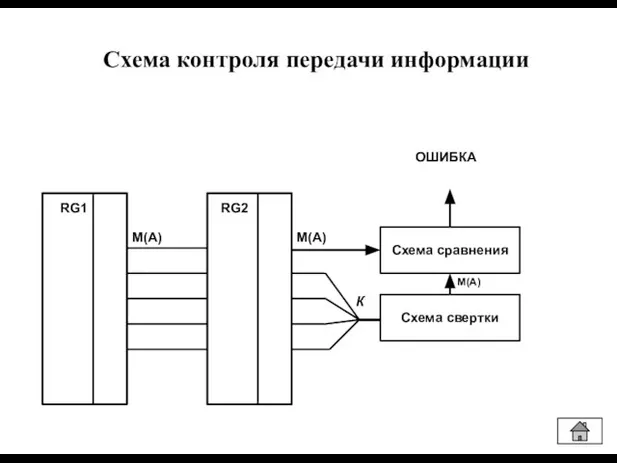

- 46. Схема контроля передачи информации

- 47. Схема числового контроля операции сложение

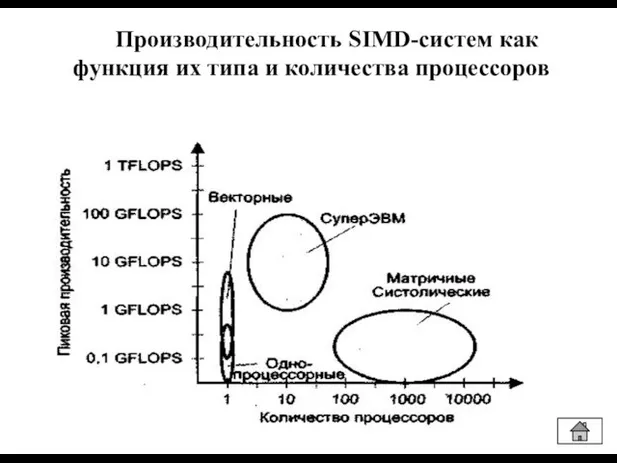

- 48. Производительность SIMD-систем как функция их типа и количества процессоров

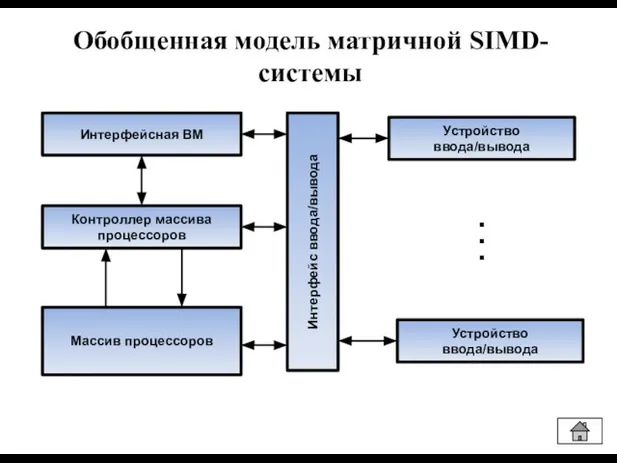

- 49. Обобщенная модель матричной SIMD-системы

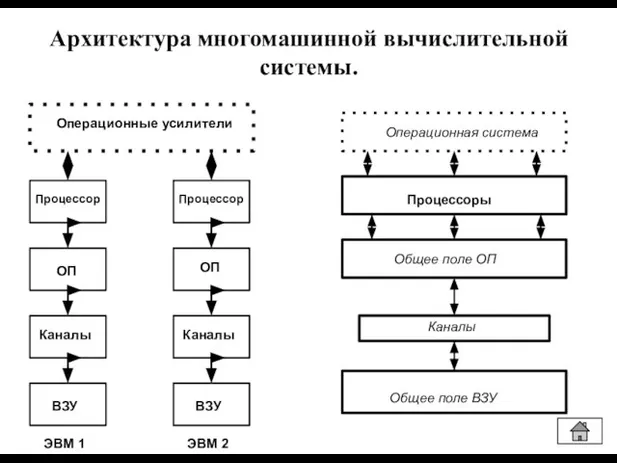

- 50. Архитектура многомашинной вычислительной системы. ЭВМ 1 ЭВМ 2 Операционные усилители Процессор Процессор ОП ОП Каналы Каналы

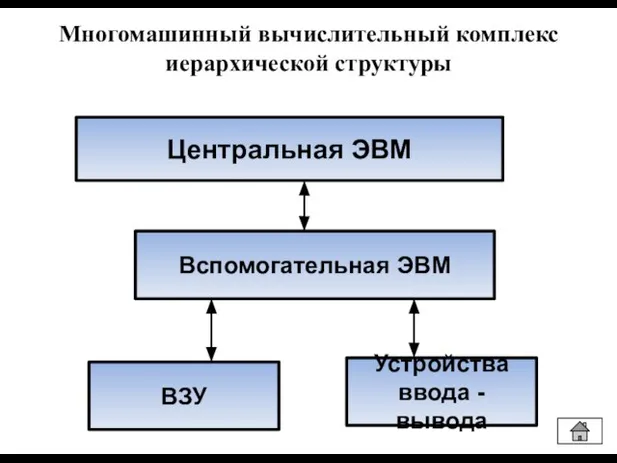

- 51. Многомашинный вычислительный комплекс иерархической структуры

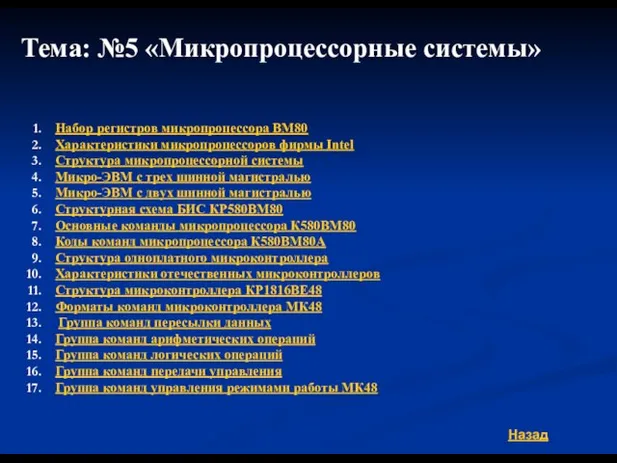

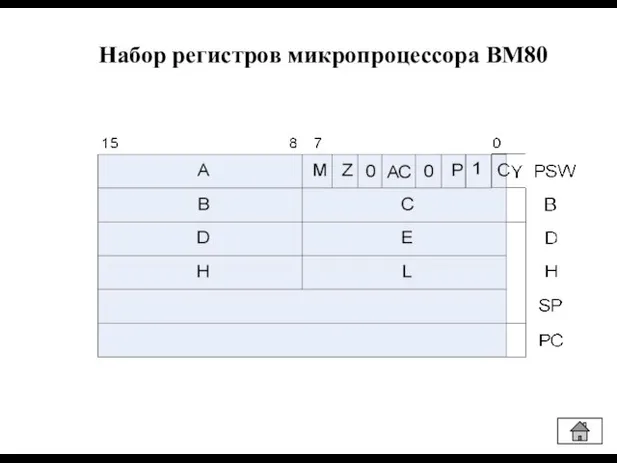

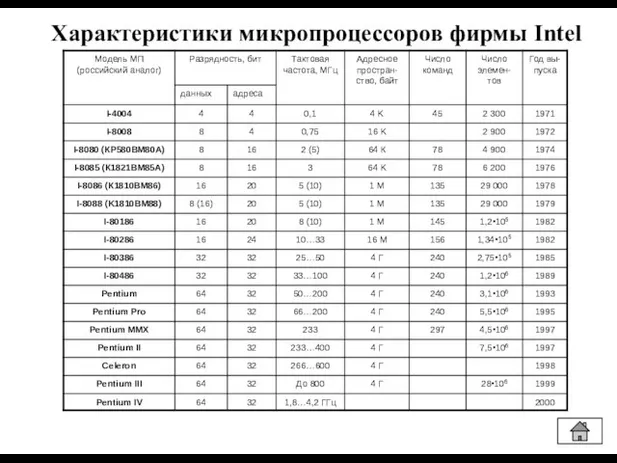

- 52. Тема: №5 «Микропроцессорные системы» Назад Набор регистров микропроцессора ВМ80 Характеристики микропроцессоров фирмы Intel Структура микропроцессорной системы

- 53. Набор регистров микропроцессора ВМ80

- 54. Характеристики микропроцессоров фирмы Intel

- 55. Системная магистраль ЦП память подсистема ввода - вывода Структура микропроцессорной системы

- 56. ЦП память подсистема ввода - вывода шина адреса шина данных шина управления Микро-ЭВМ с трех шинной

- 57. Микро-ЭВМ с двух шинной магистралью

- 58. Внешняя шина данных Внутренняя шина данных Шина адреса Буфер адреса Схема выборки регистров РОН А0…А15 Структурная

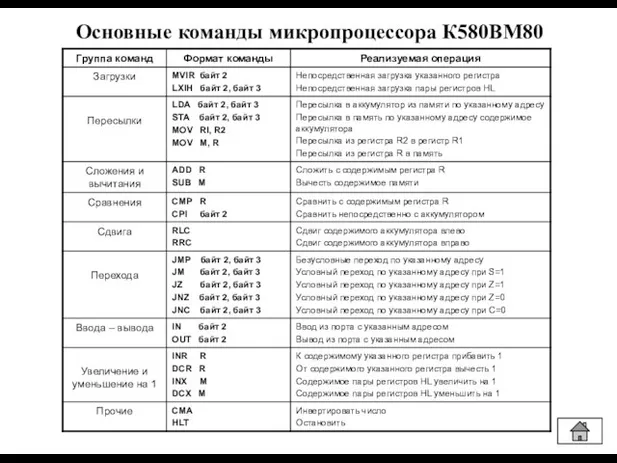

- 59. Основные команды микропроцессора К580ВМ80

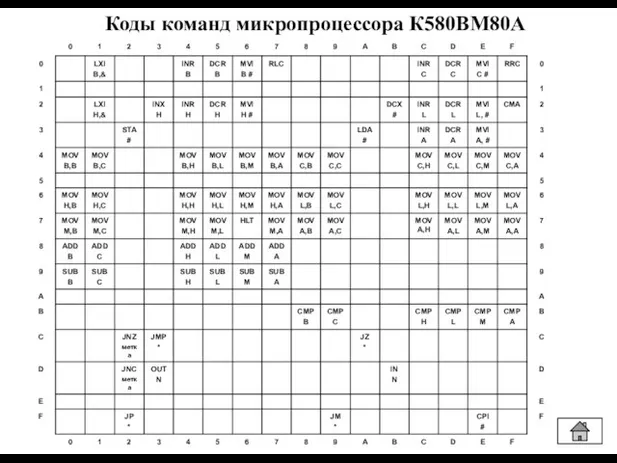

- 60. Коды команд микропроцессора К580ВМ80А

- 61. Структура одноплатного микроконтроллера

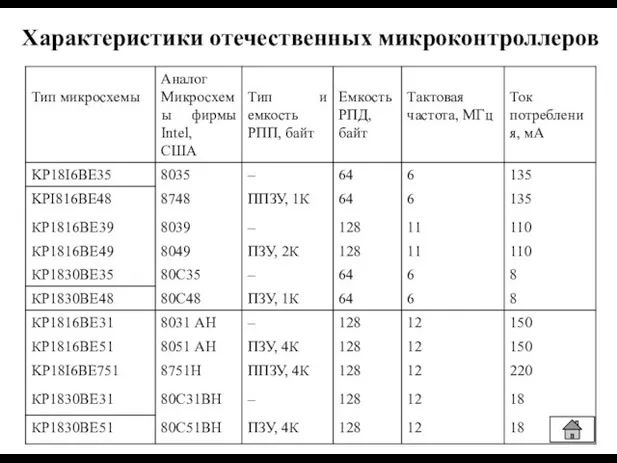

- 62. Характеристики отечественных микроконтроллеров

- 63. R1 R2 A РПП (1К байт) Счетчик Команд (РС) РПД (64 байта) РА Таймер/ счетчик (TCNT)

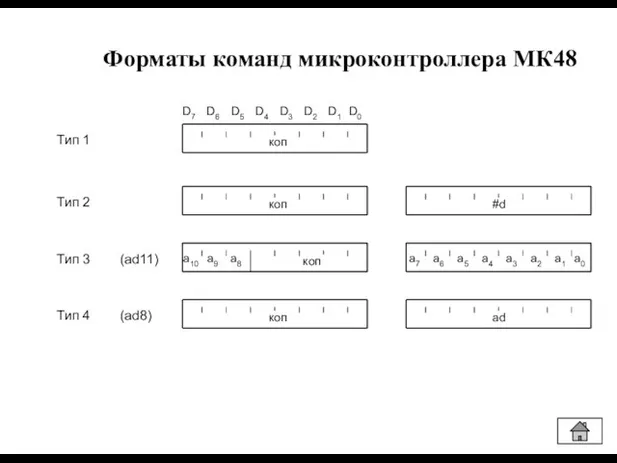

- 64. Форматы команд микроконтроллера МК48

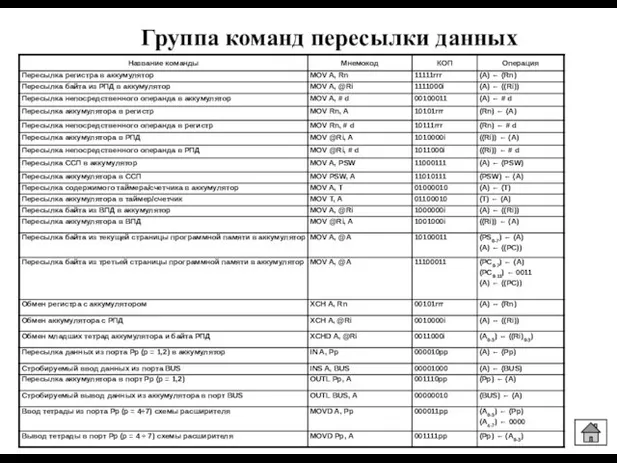

- 65. Группа команд пересылки данных

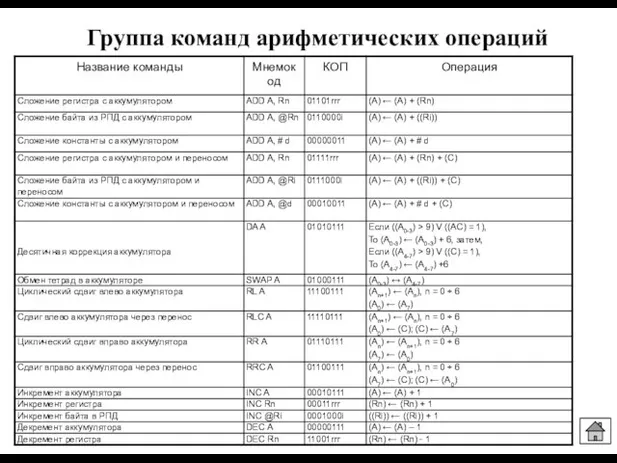

- 66. Группа команд арифметических операций

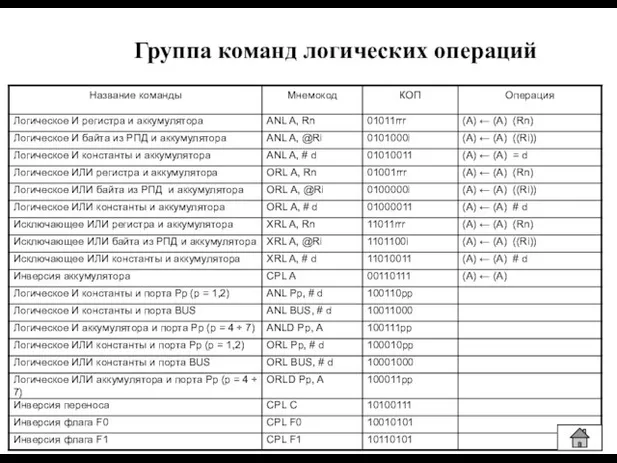

- 67. Группа команд логических операций

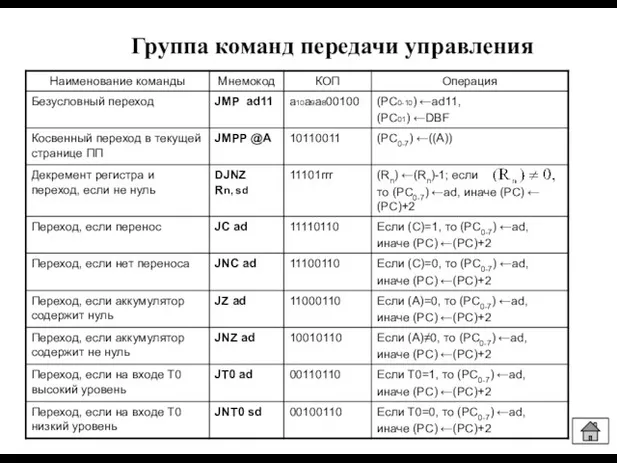

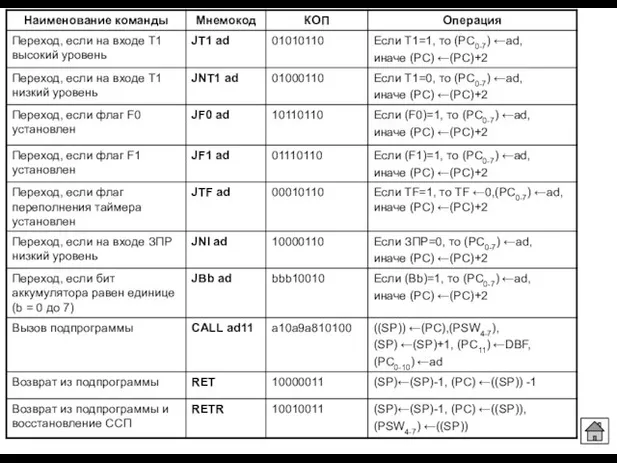

- 68. Группа команд передачи управления

- 71. Скачать презентацию

Понятие векторной и растровой графики

Понятие векторной и растровой графики  Контрольно- проверочные листы. Международный опыт. Предложение

Контрольно- проверочные листы. Международный опыт. Предложение Современные подходы к развитию навыков саморегуляции психических процессов и стрессоустойчивости спортсменов

Современные подходы к развитию навыков саморегуляции психических процессов и стрессоустойчивости спортсменов Саратов - мой город родной

Саратов - мой город родной Информационная система организации деятельности многофункциональных центров на территории Красноярского края

Информационная система организации деятельности многофункциональных центров на территории Красноярского края Уравнение жизни: сперматозоид + яйцеклетка = ребенок

Уравнение жизни: сперматозоид + яйцеклетка = ребенок История систематики

История систематики  Презентация на тему День Матери - особый праздник

Презентация на тему День Матери - особый праздник Prezentatsia_Ponyatie_materii_v_filosofii_Kanyukova_A_R

Prezentatsia_Ponyatie_materii_v_filosofii_Kanyukova_A_R Возрождение памятников истории и культуры острова – града Свияжск

Возрождение памятников истории и культуры острова – града Свияжск 1

1 Кафедра лучевой диагностики и лучевой терапии

Кафедра лучевой диагностики и лучевой терапии Конкурс социально значимых проектов Новосибирской области

Конкурс социально значимых проектов Новосибирской области Э М О

Э М О Ральф Рингер – обувь российского производства с немецким характером. Продажи в интернете

Ральф Рингер – обувь российского производства с немецким характером. Продажи в интернете Учимся отвечать (алгоритм сравнительного анализа)

Учимся отвечать (алгоритм сравнительного анализа) Оновлений розклад руху поїздів

Оновлений розклад руху поїздів Мексика

Мексика Педсовет “Современный урок- как основа эффективного и качественного образования»3 ноября 2011 года

Педсовет “Современный урок- как основа эффективного и качественного образования»3 ноября 2011 года Экосистема озера

Экосистема озера Презентация на тему Иллюстрации Кукрыниксов к роману Салтыкова-Щедрина "История одного города"

Презентация на тему Иллюстрации Кукрыниксов к роману Салтыкова-Щедрина "История одного города" Всеобщность законов композиции. Выбор места, объекта и ракурса съемки

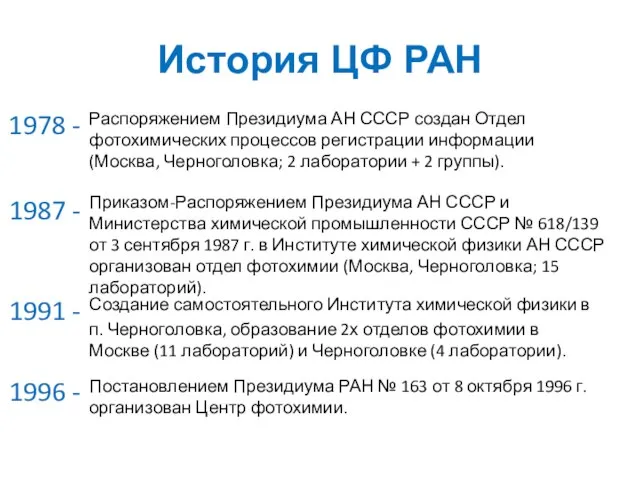

Всеобщность законов композиции. Выбор места, объекта и ракурса съемки История ЦФ РАН

История ЦФ РАН Разработка основной образовательной программы образовательного учреждения

Разработка основной образовательной программы образовательного учреждения CTCS Logistics's business review Q4 2020 - Q1 2021

CTCS Logistics's business review Q4 2020 - Q1 2021 НОУ ВПО Самарский медицинский институт «РЕАВИЗ»

НОУ ВПО Самарский медицинский институт «РЕАВИЗ» Презентация на тему Технология развития критического мышления на уроках истории

Презентация на тему Технология развития критического мышления на уроках истории Организационные диаграммы

Организационные диаграммы