Содержание

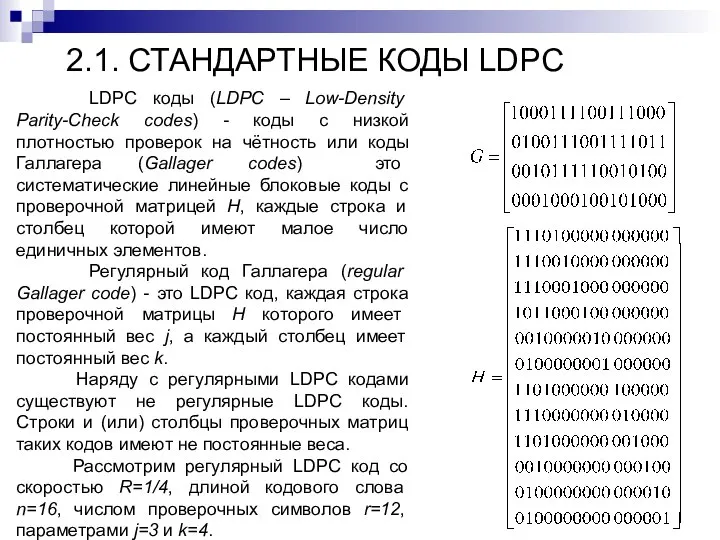

- 2. 2.1. СТАНДАРТНЫЕ КОДЫ LDPC LDPC коды (LDPC – Low-Density Parity-Check codes) - коды с низкой плотностью

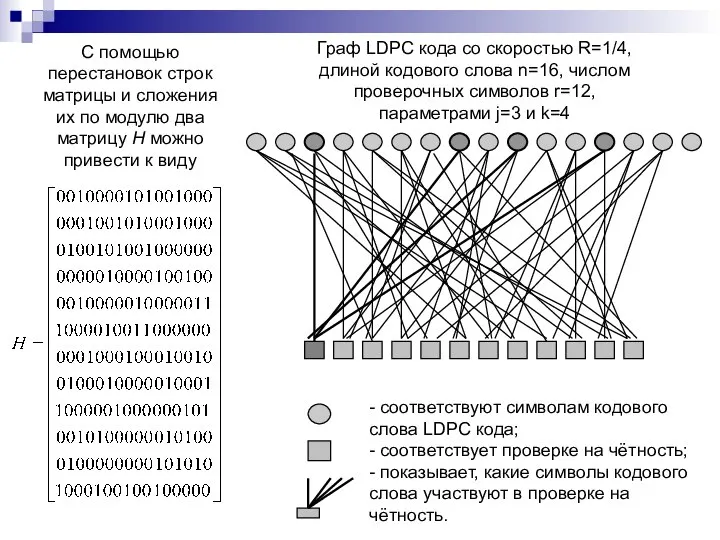

- 3. С помощью перестановок строк матрицы и сложения их по модулю два матрицу H можно привести к

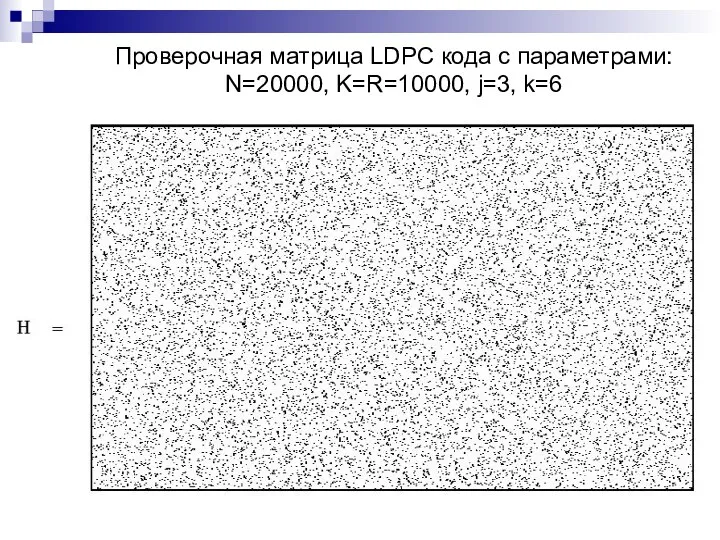

- 4. Проверочная матрица LDPC кода с параметрами: N=20000, K=R=10000, j=3, k=6

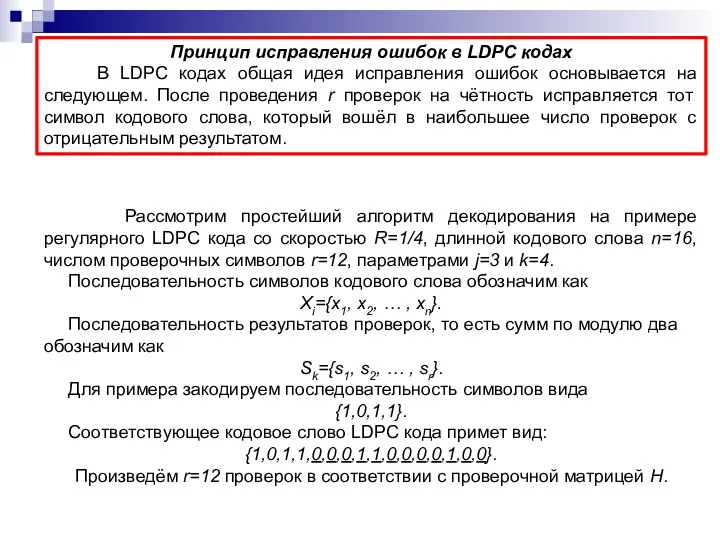

- 5. Принцип исправления ошибок в LDPC кодах В LDPC кодах общая идея исправления ошибок основывается на следующем.

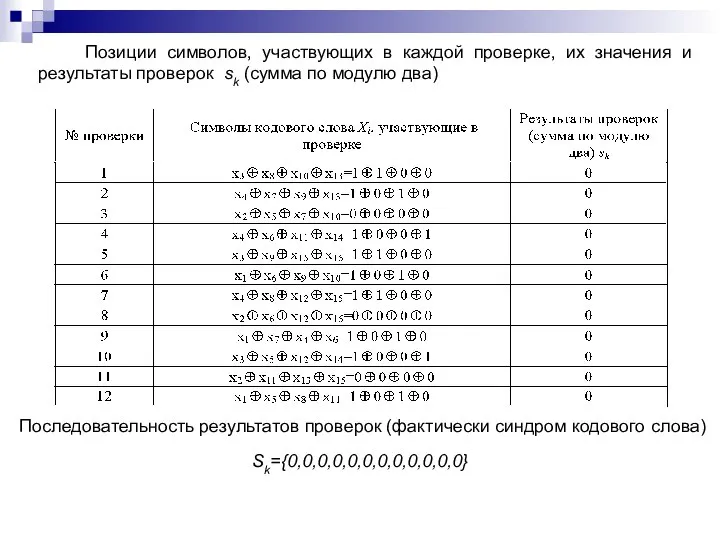

- 6. Позиции символов, участвующих в каждой проверке, их значения и результаты проверок sk (сумма по модулю два)

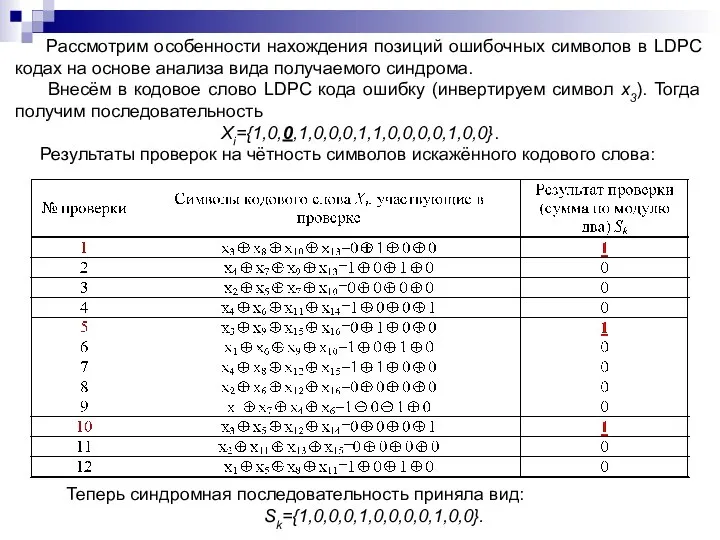

- 7. Рассмотрим особенности нахождения позиций ошибочных символов в LDPC кодах на основе анализа вида получаемого синдрома. Внесём

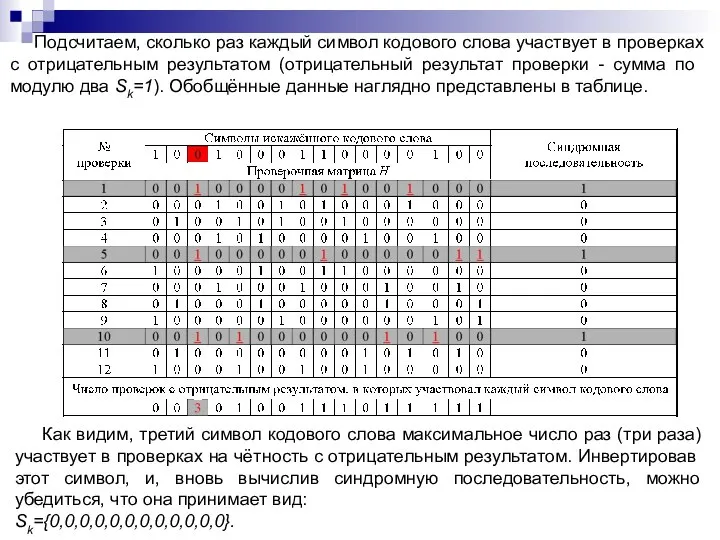

- 8. Подсчитаем, сколько раз каждый символ кодового слова участвует в проверках с отрицательным результатом (отрицательный результат проверки

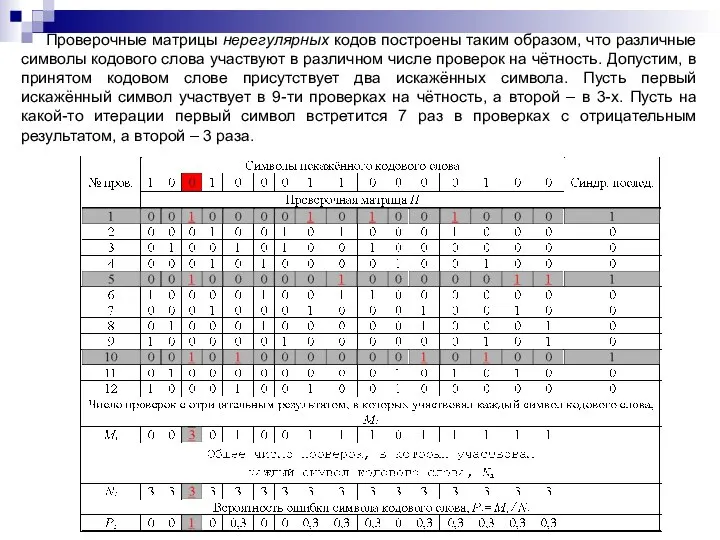

- 9. Проверочные матрицы нерегулярных кодов построены таким образом, что различные символы кодового слова участвуют в различном числе

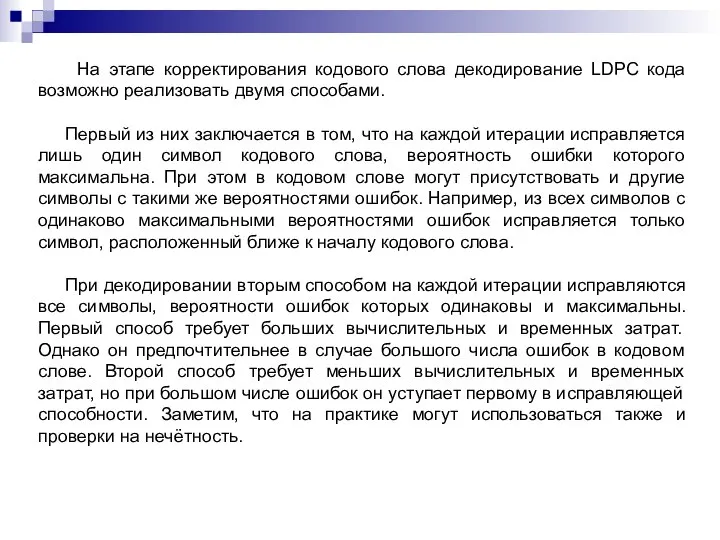

- 10. На этапе корректирования кодового слова декодирование LDPC кода возможно реализовать двумя способами. Первый из них заключается

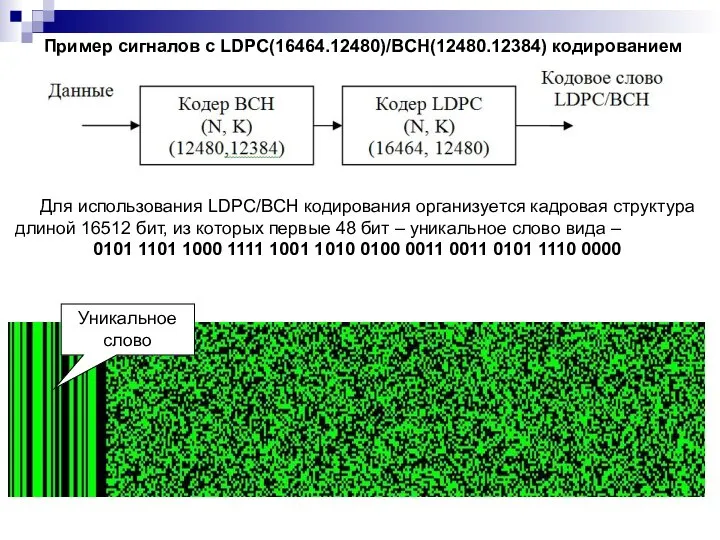

- 11. Пример сигналов с LDPC(16464.12480)/BCH(12480.12384) кодированием Для использования LDPC/BCH кодирования организуется кадровая структура длиной 16512 бит, из

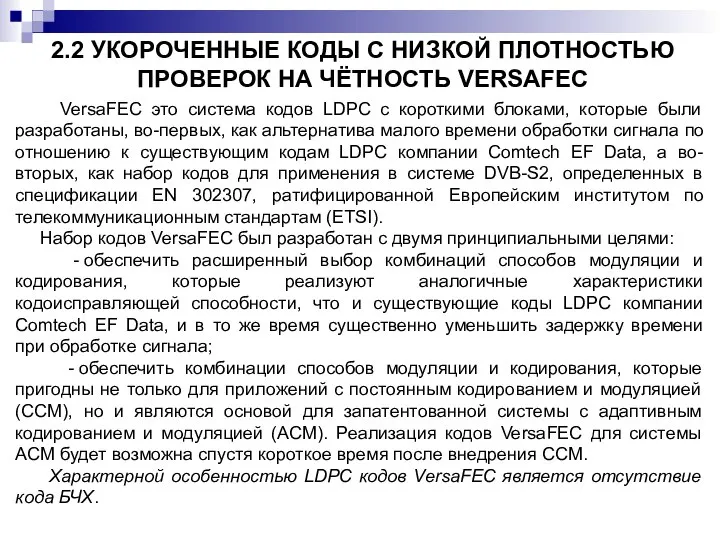

- 12. 2.2 УКОРОЧЕННЫЕ КОДЫ С НИЗКОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЁТНОСТЬ VERSAFEC VersaFEC это система кодов LDPC с

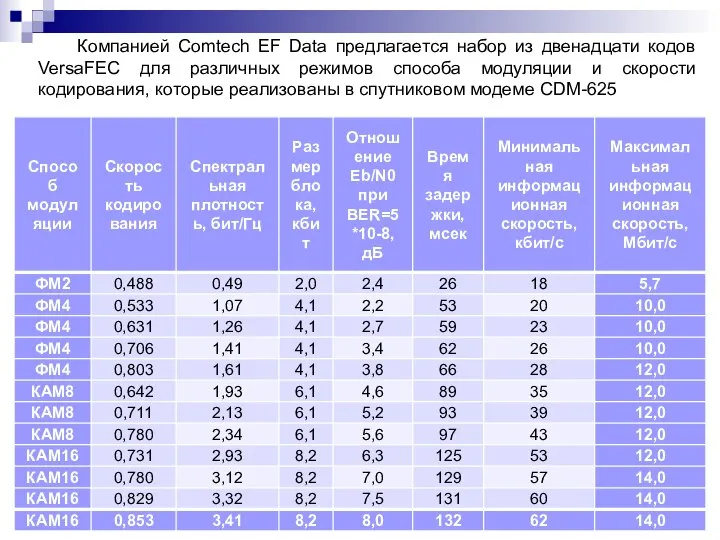

- 13. Компанией Comtech EF Data предлагается набор из двенадцати кодов VersaFEC для различных режимов способа модуляции и

- 14. Основные характеристики LDPC кодов VersaFEC: - синхрокомбинация для всех видов модуляции передаётся за 52 такта модулятора

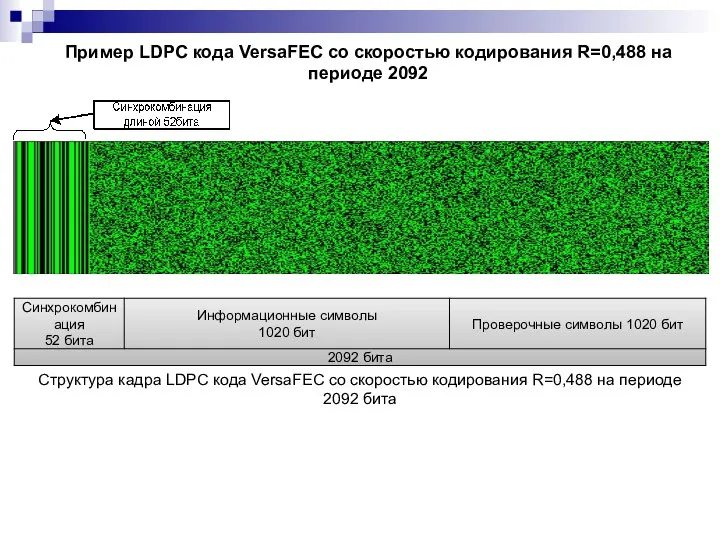

- 15. Пример LDPC кода VersaFEC со скоростью кодирования R=0,488 на периоде 2092 Структура кадра LDPC кода VersaFEC

- 17. Скачать презентацию

Триггеры. Применение

Триггеры. Применение Понятие алгоритма. Примеры алгоритмов из окружающей жизни

Понятие алгоритма. Примеры алгоритмов из окружающей жизни Задачи математического программирования

Задачи математического программирования Примеры библиографического описания

Примеры библиографического описания Обучени таргету в инстаграм

Обучени таргету в инстаграм Биомика регистрация для родителей. Система безналичного питания

Биомика регистрация для родителей. Система безналичного питания Питание в школе. Школа будущего

Питание в школе. Школа будущего Вставка титульных страниц и шаблоны в ПО Smart Notebook

Вставка титульных страниц и шаблоны в ПО Smart Notebook Оптимальное планирование экскурсионных поездок школьников во время каникул

Оптимальное планирование экскурсионных поездок школьников во время каникул Осенний пейзаж. Рисование во встроенных графических редакторах (MS Word, OpenOffice.org Writer)

Осенний пейзаж. Рисование во встроенных графических редакторах (MS Word, OpenOffice.org Writer) Искусственный интеллек ( лекция 1)

Искусственный интеллек ( лекция 1) Эквивалентные состояния и эквивалентные автоматы. Задача минимизации автоматов

Эквивалентные состояния и эквивалентные автоматы. Задача минимизации автоматов Алгоритмы и программы

Алгоритмы и программы On-line сервисы

On-line сервисы Основная память ЭВМ. Способы выделения памяти в программах

Основная память ЭВМ. Способы выделения памяти в программах Консолидация данных

Консолидация данных Объекты в MS Access

Объекты в MS Access ec8f84f81f5c61f5

ec8f84f81f5c61f5 Торговые элементы. Штрих-коды. Этикетки

Торговые элементы. Штрих-коды. Этикетки Проект Витрина

Проект Витрина At the movies

At the movies Понятие модели Что такое модель Виды моделей

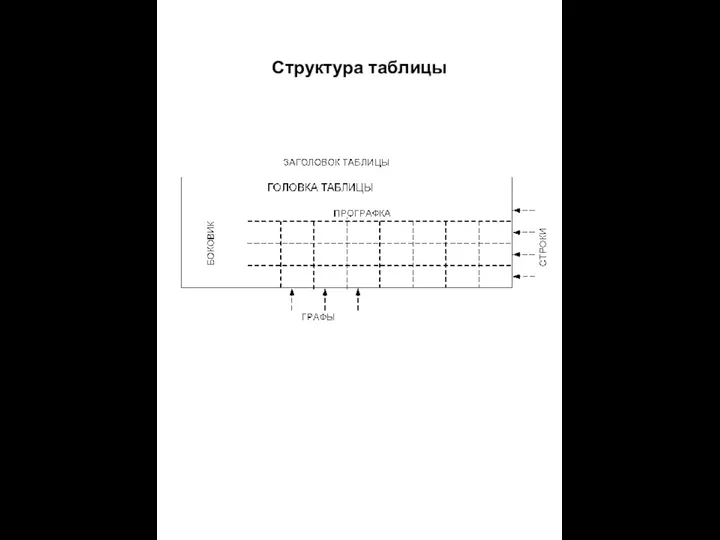

Понятие модели Что такое модель Виды моделей Структура таблицы

Структура таблицы Современный персональный компьютер

Современный персональный компьютер Единая система классификации и кодирования технико-экономической информации

Единая система классификации и кодирования технико-экономической информации Об операционной системе(ОС) Windows

Об операционной системе(ОС) Windows Системы хранения информации. Генератор опорных образов Mind-Surfing (урок 13)

Системы хранения информации. Генератор опорных образов Mind-Surfing (урок 13) Webpack

Webpack