Содержание

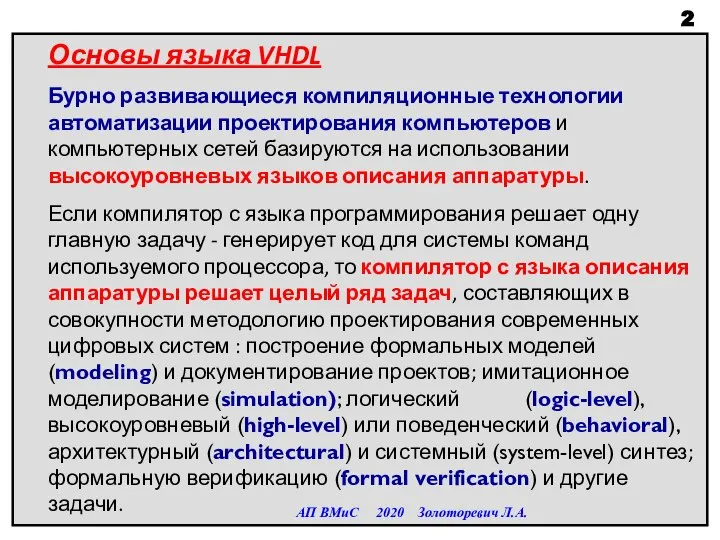

- 2. Основы языка VHDL Бурно развивающиеся компиляционные технологии автоматизации проектирования компьютеров и компьютерных сетей базируются на использовании

- 3. Основы языка VHDL (прдлж) АП ВМиС 2020 Золоторевич Л.А. В настоящее время двумя наиболее широко распространенными

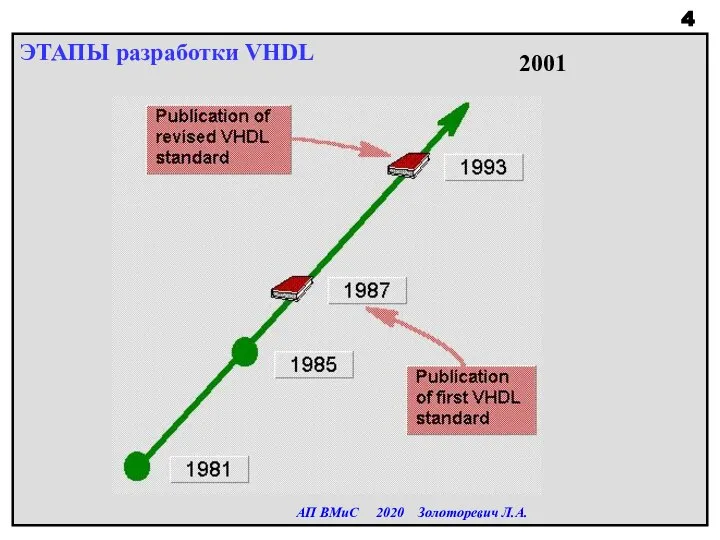

- 4. ЭТАПЫ разработки VHDL АП ВМиС 2020 Золоторевич Л.А. 2001

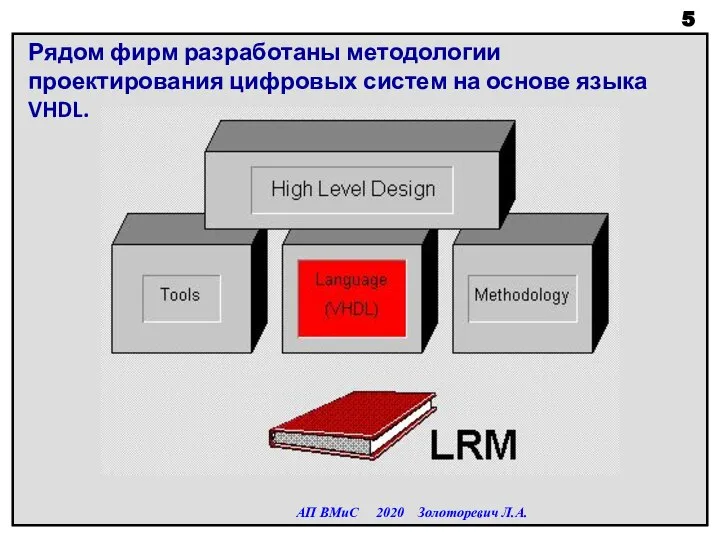

- 5. Рядом фирм разработаны методологии проектирования цифровых систем на основе языка VHDL. АП ВМиС 2020 Золоторевич Л.А.

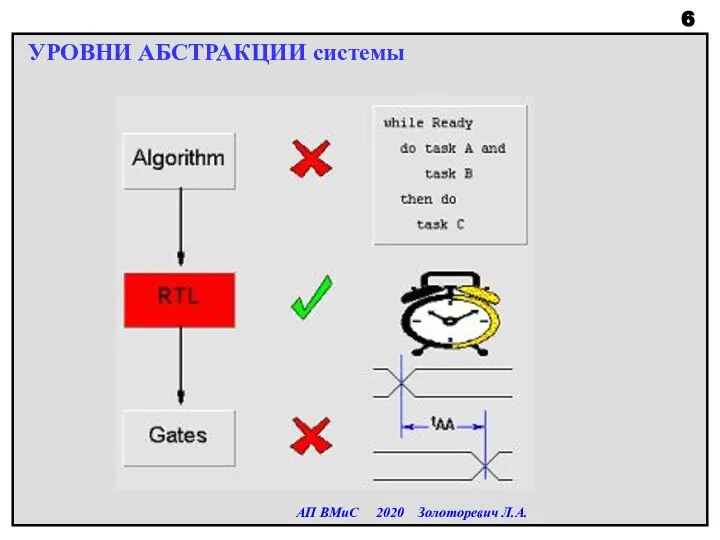

- 6. УРОВНИ АБСТРАКЦИИ системы АП ВМиС 2020 Золоторевич Л.А.

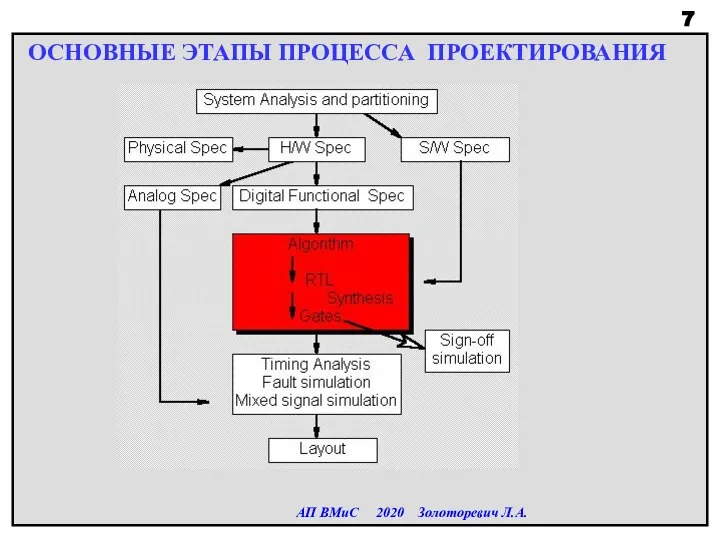

- 7. ОСНОВНЫЕ ЭТАПЫ ПРОЦЕССА ПРОЕКТИРОВАНИЯ АП ВМиС 2020 Золоторевич Л.А.

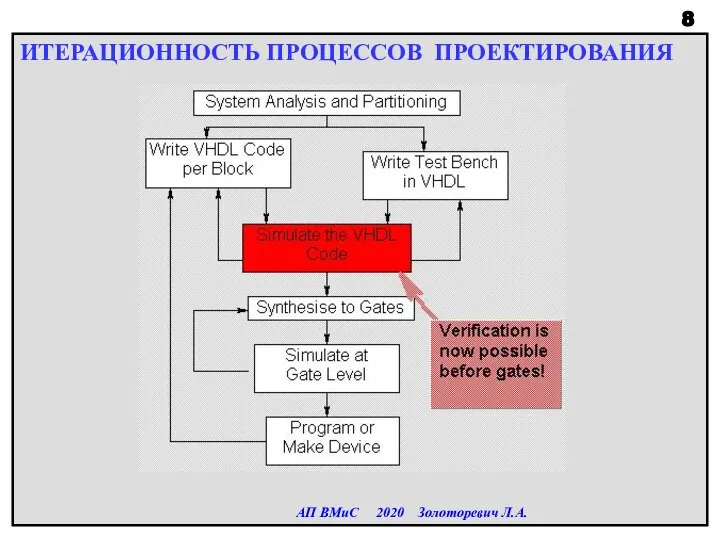

- 8. ИТЕРАЦИОННОСТЬ ПРОЦЕССОВ ПРОЕКТИРОВАНИЯ АП ВМиС 2020 Золоторевич Л.А.

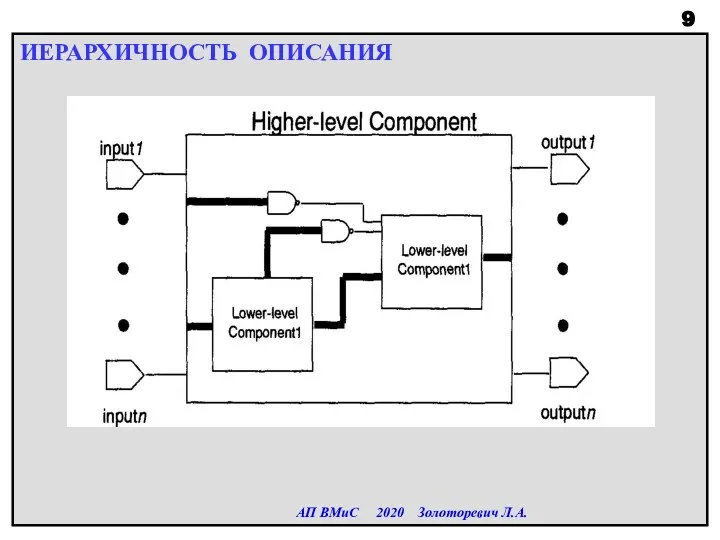

- 9. ИЕРАРХИЧНОСТЬ ОПИСАНИЯ АП ВМиС 2020 Золоторевич Л.А.

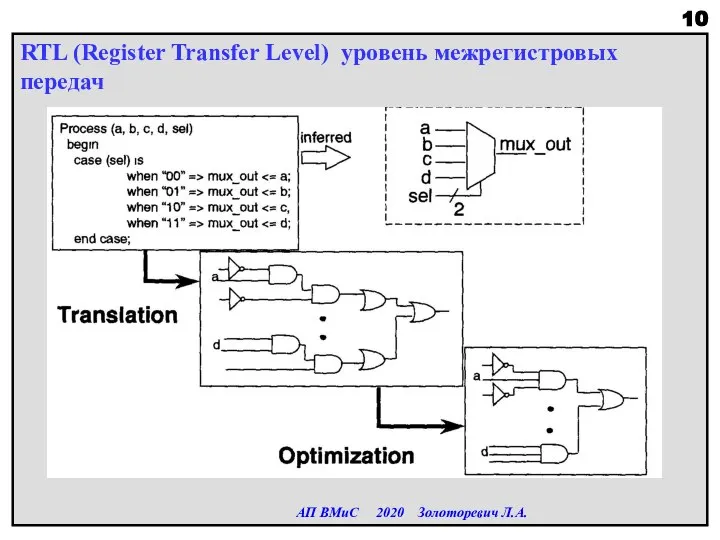

- 10. RTL (Register Transfer Level) уровень межрегистровых передач АП ВМиС 2020 Золоторевич Л.А.

- 11. ОСОБЕННОСТИ VHDL Проекты на VHDL ориентированы на любой инструментарий; VHDL допускает создание проекта, не зависящего от

- 12. ОБЩАЯ ХАРАКТЕРИСТИКА VHDL !!! Построен на базе ключевых слов; !!! НЕ РАЗЛИЧАЕТ в большинстве случаев прописные

- 13. Элементами проекта VHDL являются: Entity (Используется для определения интерфейса модели, т.е. модели с точки зрения ее

- 14. Элементами проекта VHDL являются: Entity Architecture Configuration Package Декларации объекта (entity declaration) представляют внешний интерфейс объекта

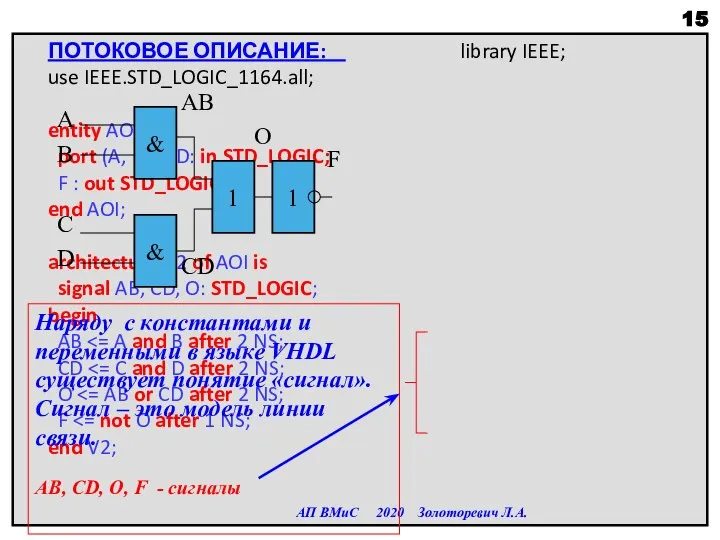

- 15. ПОТОКОВОЕ ОПИСАНИЕ: library IEEE; use IEEE.STD_LOGIC_1164.all; entity AOI is port (A, B, C, D: in STD_LOGIC;

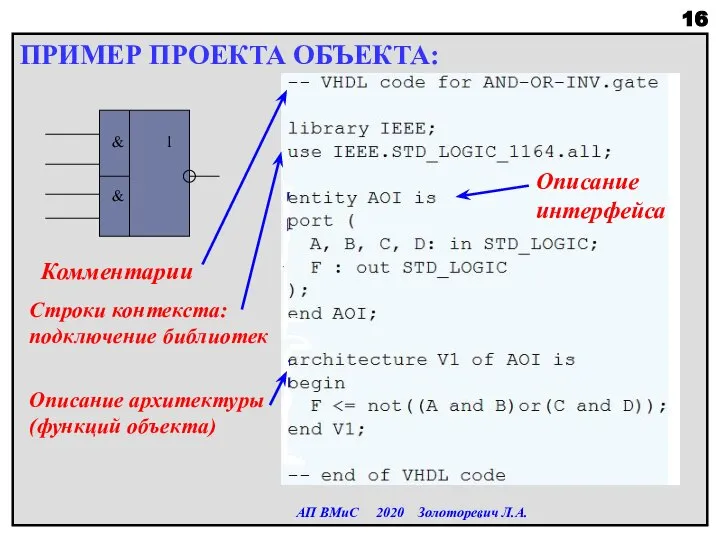

- 16. ПРИМЕР ПРОЕКТА ОБЪЕКТА: АП ВМиС 2020 Золоторевич Л.А. & 1 & Комментарии Строки контекста: подключение библиотек

- 17. Сигналы Архитектура с именем V2 содержит три сигнала AB, CD и O, используемые внутри архитектуры. Сигнал

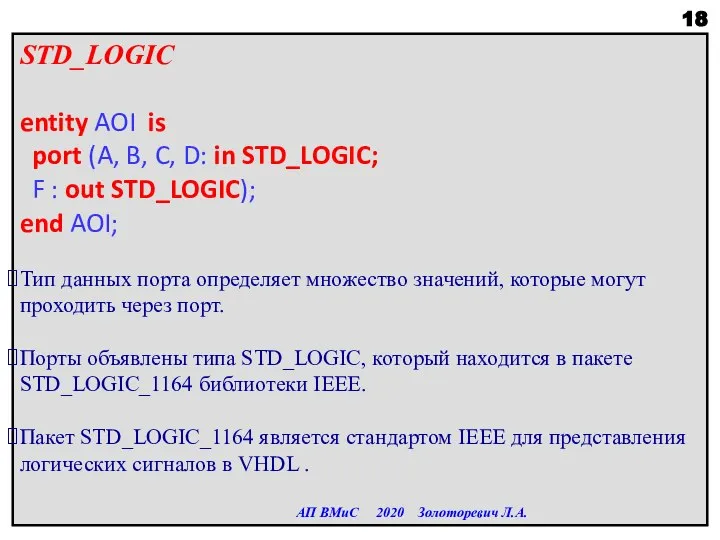

- 18. STD_LOGIC entity AOI is port (A, B, C, D: in STD_LOGIC; F : out STD_LOGIC); end

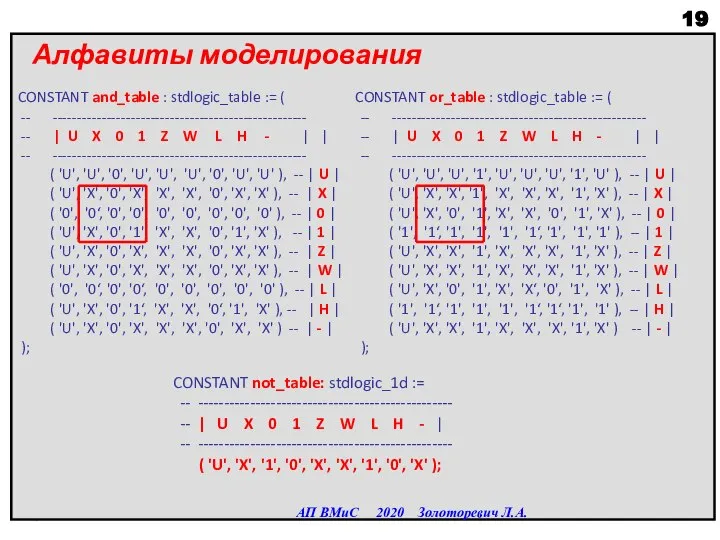

- 19. Алфавиты моделирования АП ВМиС 2020 Золоторевич Л.А. CONSTANT and_table : stdlogic_table := ( -- ---------------------------------------------------- --

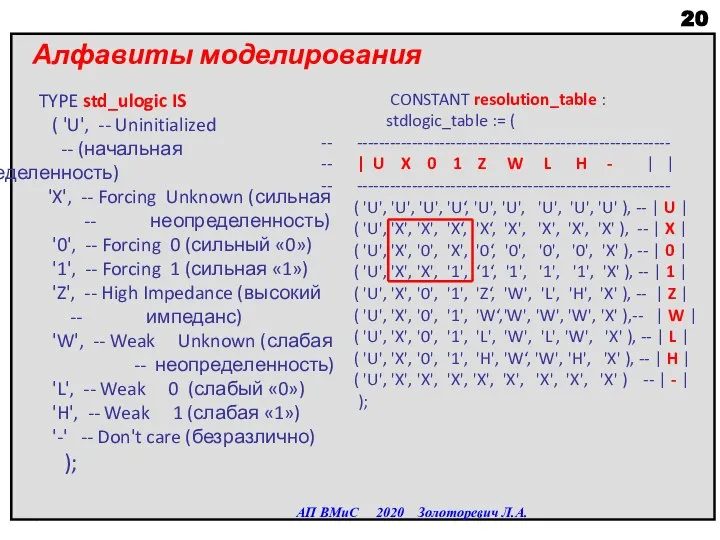

- 20. Алфавиты моделирования АП ВМиС 2020 Золоторевич Л.А. TYPE std_ulogic IS ( 'U', -- Uninitialized -- (начальная

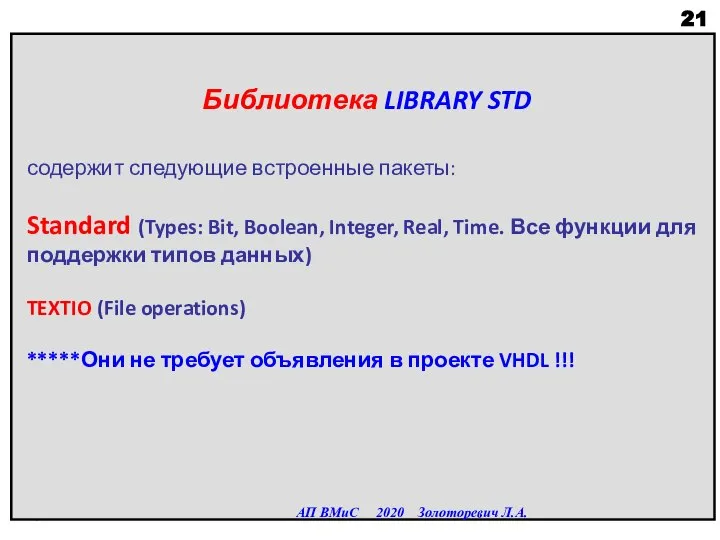

- 21. Библиотека LIBRARY STD содержит следующие встроенные пакеты: Standard (Types: Bit, Boolean, Integer, Real, Time. Все функции

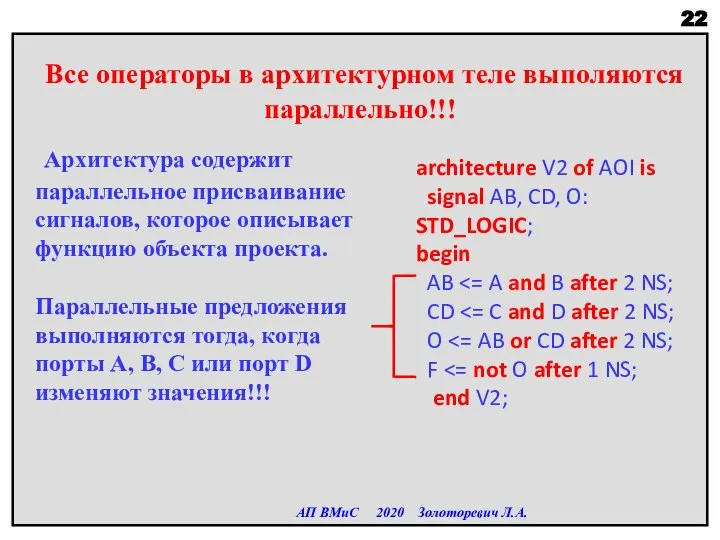

- 22. architecture V2 of AOI is signal AB, CD, O: STD_LOGIC; begin AB CD O F end

- 23. Структурное описание объекта (Структурное моделирование, моделирование на структурном уровне) АП ВМиС 2020 Золоторевич Л.А.

- 24. Структурное описание объекта MUX2 Необходимо описать на языке VHDL объект, который представляет собой некоторую взаимосвязь компонентов.

- 25. Компонентами являются AOI и INV. Моделируемая структура MUX2 состоит из данных компонент. Компонента объявляется внутри архитектуры

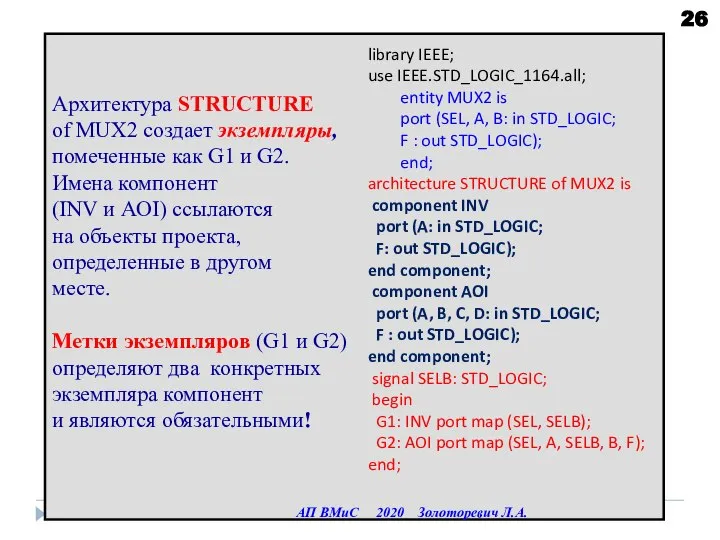

- 26. Архитектура STRUCTURE of MUX2 создает экземпляры, помеченные как G1 и G2. Имена компонент (INV и AOI)

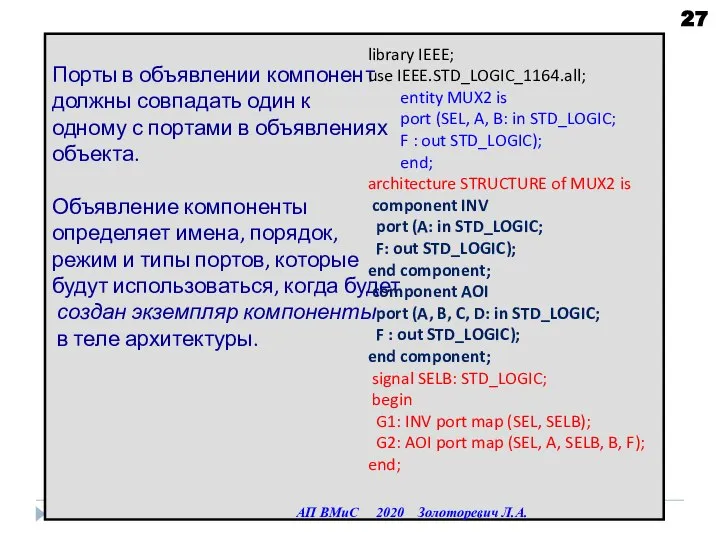

- 27. Порты в объявлении компонент должны совпадать один к одному с портами в объявлениях объекта. Объявление компоненты

- 28. АП ВМиС 2020 Золоторевич Л.А. Создание экземпляров компонент делает возможным создание иерархии проекта по аналогии с

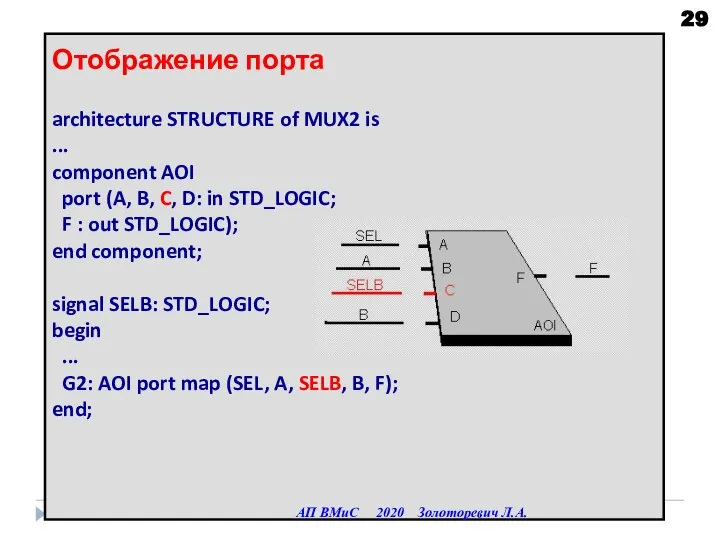

- 29. АП ВМиС 2020 Золоторевич Л.А. Отображение порта architecture STRUCTURE of MUX2 is ... component AOI port

- 30. АП ВМиС 2020 Золоторевич Л.А. Здесь компоненты связываются по умолчанию. architecture STRUCTURE of MUX2 is ...

- 31. АП ВМиС 2020 Золоторевич Л.А. При связывании по умолчанию гнездо чипа (объявление компоненты) несет чип (проект

- 32. КОНФИГУРАЦИЯ Описание VHDL может состоять из многих единиц проекта (каждое со своим архитектурным телом), организованных в

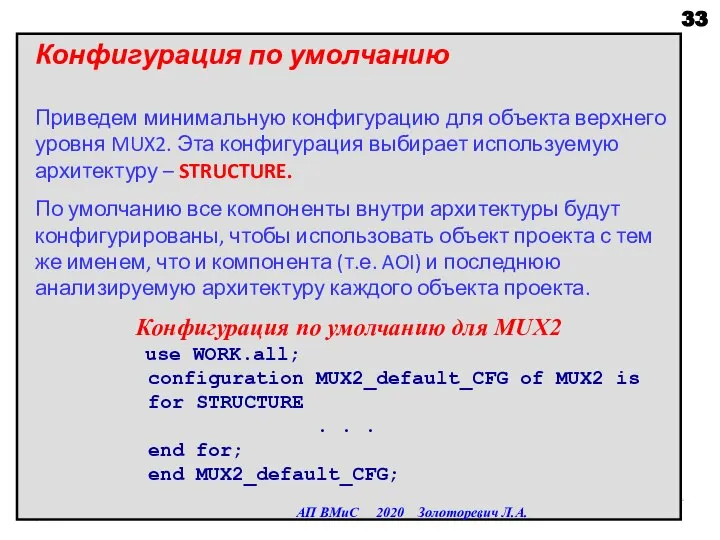

- 33. Конфигурация по умолчанию Приведем минимальную конфигурацию для объекта верхнего уровня MUX2. Эта конфигурация выбирает используемую архитектуру

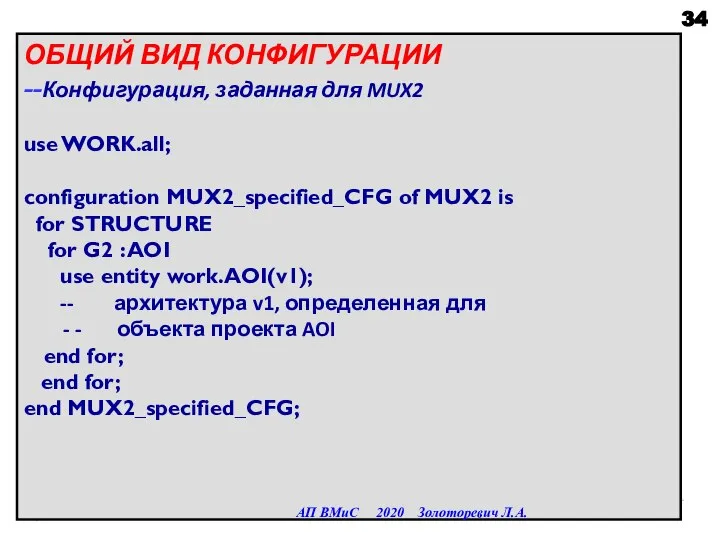

- 34. ОБЩИЙ ВИД КОНФИГУРАЦИИ --Конфигурация, заданная для MUX2 use WORK.all; configuration MUX2_specified_CFG of MUX2 is for STRUCTURE

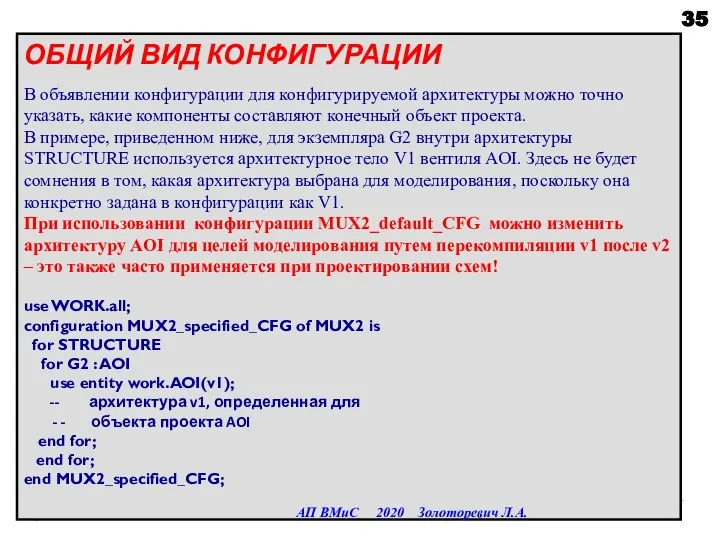

- 35. ОБЩИЙ ВИД КОНФИГУРАЦИИ В объявлении конфигурации для конфигурируемой архитектуры можно точно указать, какие компоненты составляют конечный

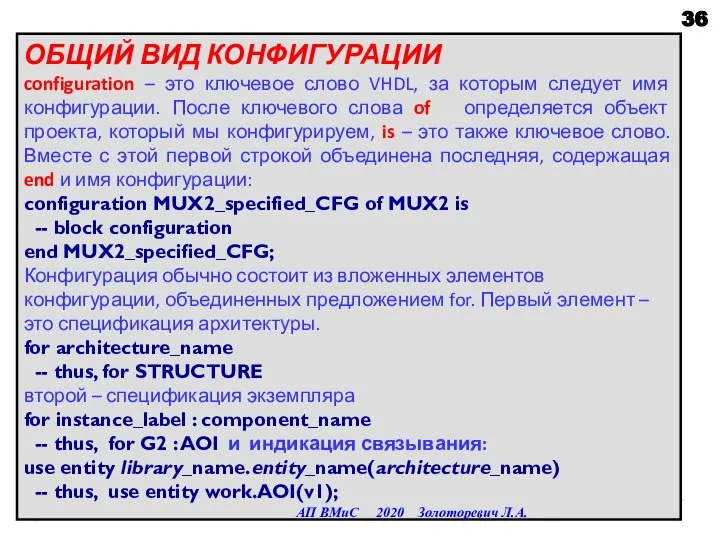

- 36. ОБЩИЙ ВИД КОНФИГУРАЦИИ configuration – это ключевое слово VHDL, за которым следует имя конфигурации. После ключевого

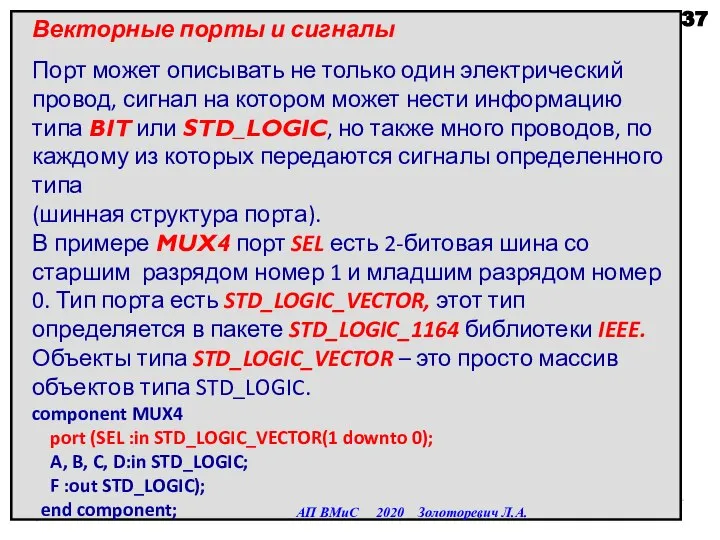

- 37. Векторные порты и сигналы Порт может описывать не только один электрический провод, сигнал на котором может

- 38. Testbench АП ВМиС 2020 Золоторевич Л.А.

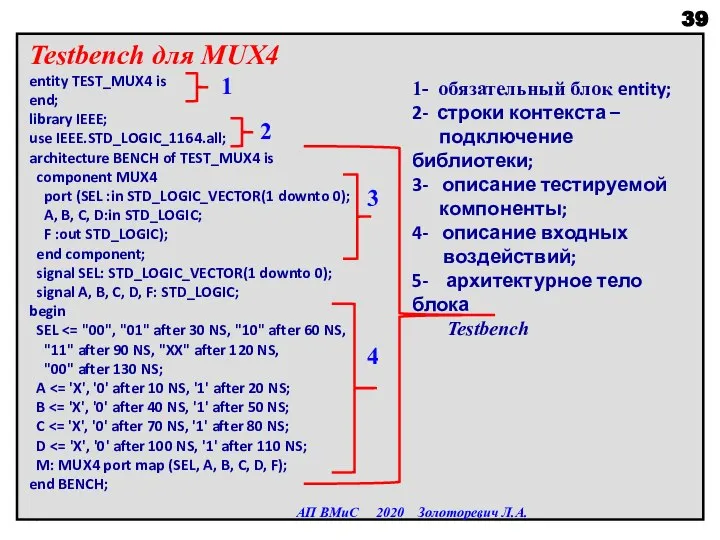

- 39. АП ВМиС 2020 Золоторевич Л.А. Testbench для MUX4 entity TEST_MUX4 is end; library IEEE; use IEEE.STD_LOGIC_1164.all;

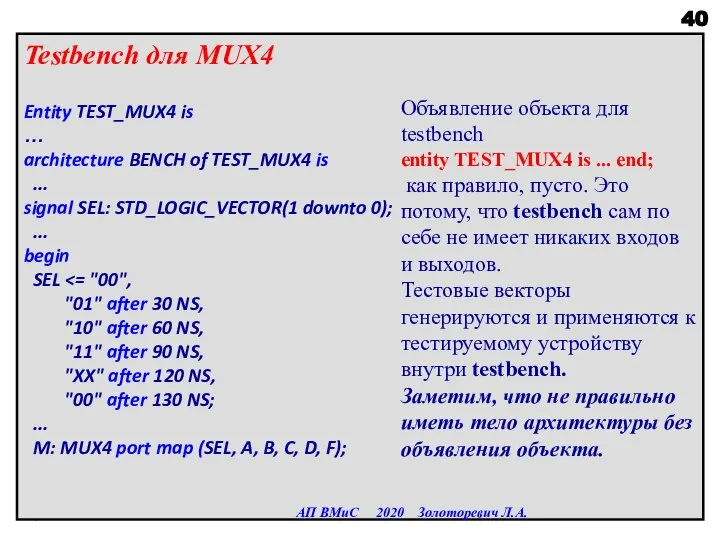

- 40. Testbench для MUX4 Entity TEST_MUX4 is … architecture BENCH of TEST_MUX4 is ... signal SEL: STD_LOGIC_VECTOR(1

- 41. АП ВМиС 2020 Золоторевич Л.А. Общий вид Testbench для MUX4 entity TEST_MUX4 is End; library IEEE;

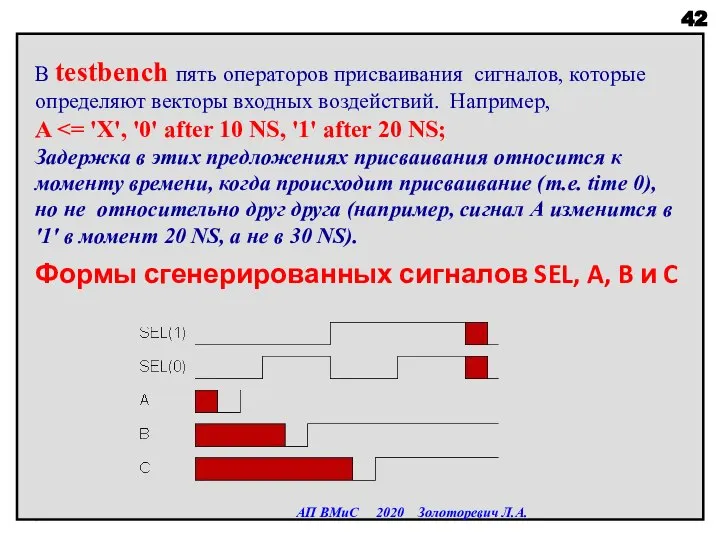

- 42. АП ВМиС 2020 Золоторевич Л.А. В testbench пять операторов присваивания сигналов, которые определяют векторы входных воздействий.

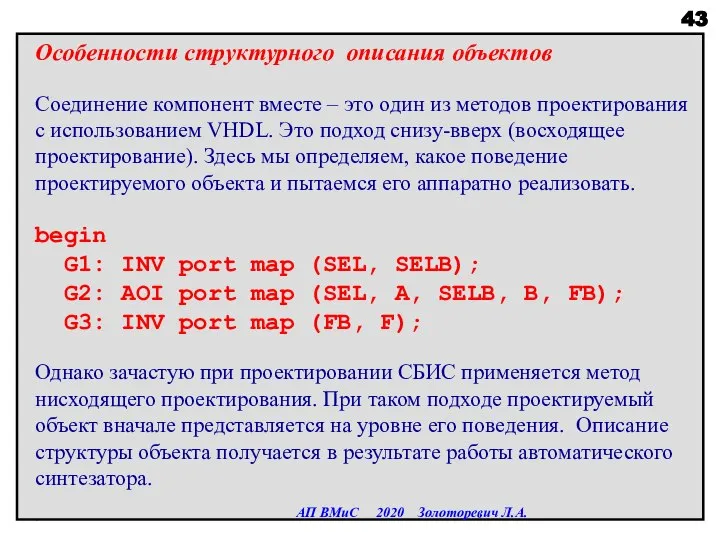

- 43. Особенности структурного описания объектов Соединение компонент вместе – это один из методов проектирования с использованием VHDL.

- 44. Описание объекта на уровне поведения Определив концептуально, чего мы хотим от объекта, мы можем на VHDL

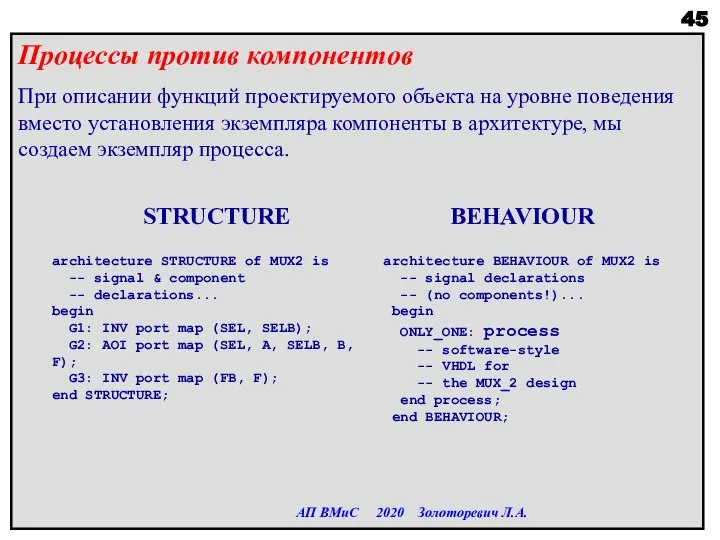

- 45. Процессы против компонентов При описании функций проектируемого объекта на уровне поведения вместо установления экземпляра компоненты в

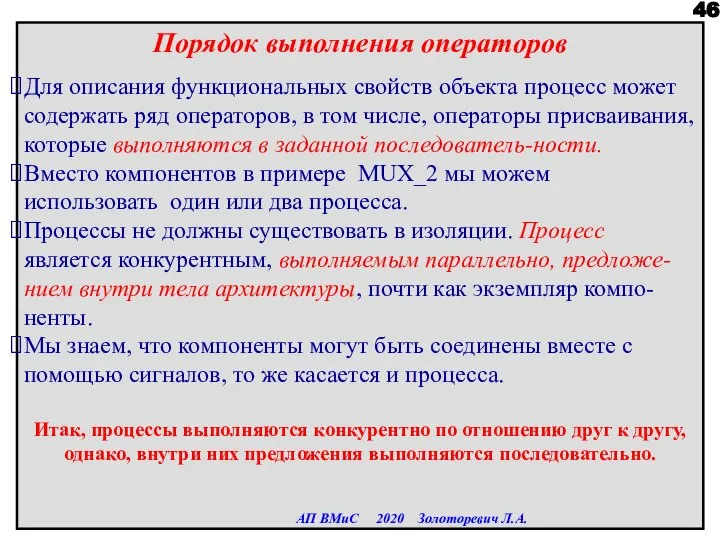

- 46. Порядок выполнения операторов Для описания функциональных свойств объекта процесс может содержать ряд операторов, в том числе,

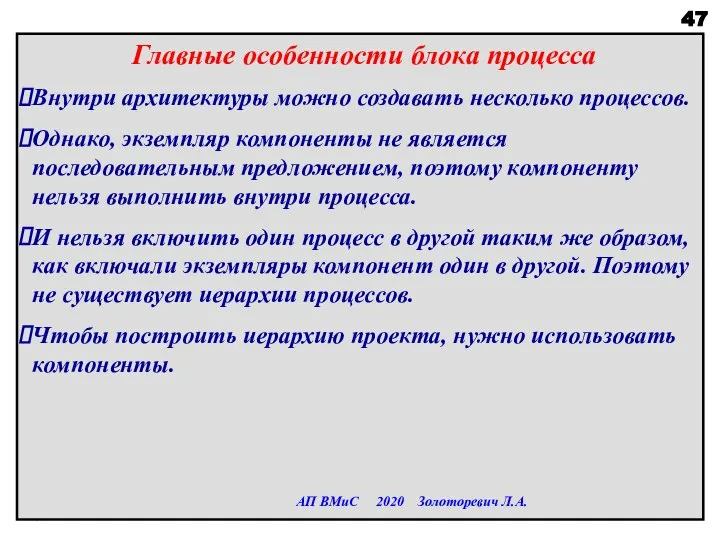

- 47. Главные особенности блока процесса Внутри архитектуры можно создавать несколько процессов. Однако, экземпляр компоненты не является последовательным

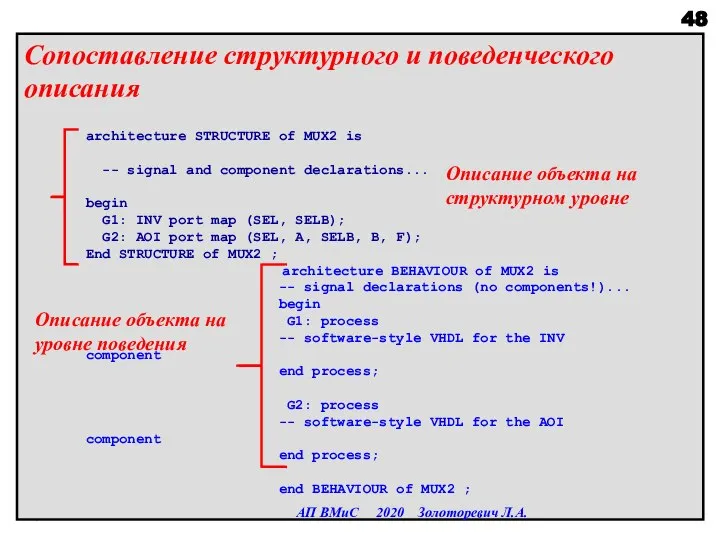

- 48. Сопоставление структурного и поведенческого описания АП ВМиС 2020 Золоторевич Л.А. architecture STRUCTURE of MUX2 is --

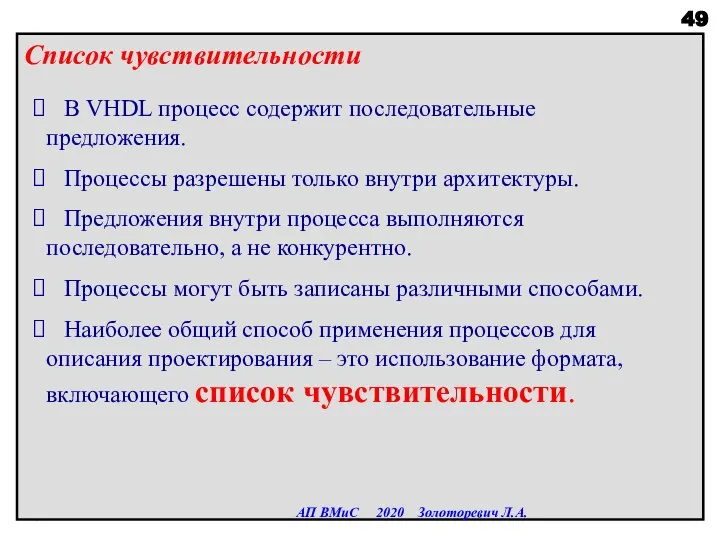

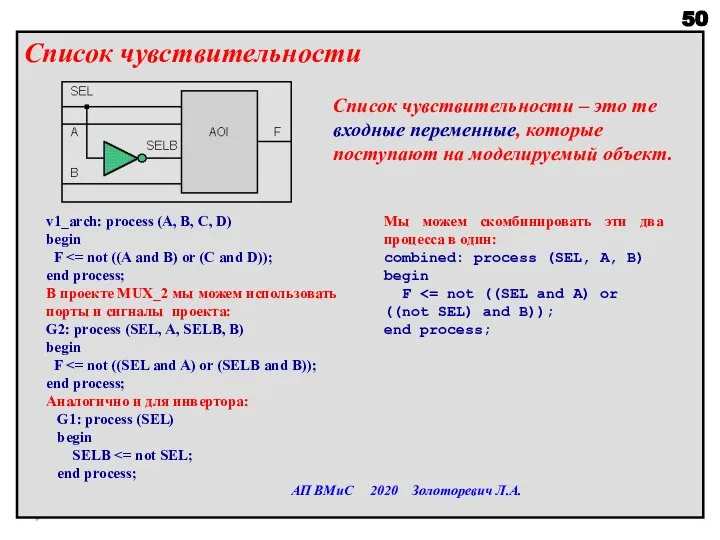

- 49. Список чувствительности АП ВМиС 2020 Золоторевич Л.А. В VHDL процесс содержит последовательные предложения. Процессы разрешены только

- 50. Список чувствительности АП ВМиС 2020 Золоторевич Л.А. v1_arch: process (A, B, C, D) begin F end

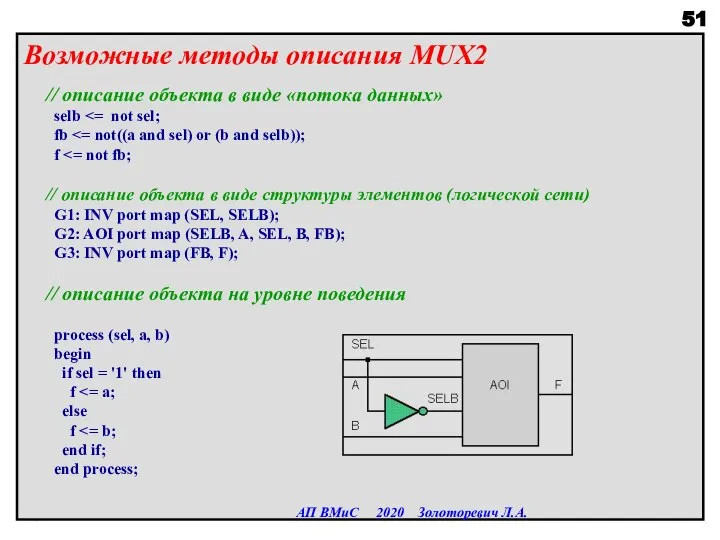

- 51. Возможные методы описания MUX2 АП ВМиС 2020 Золоторевич Л.А. // описание объекта в виде «потока данных»

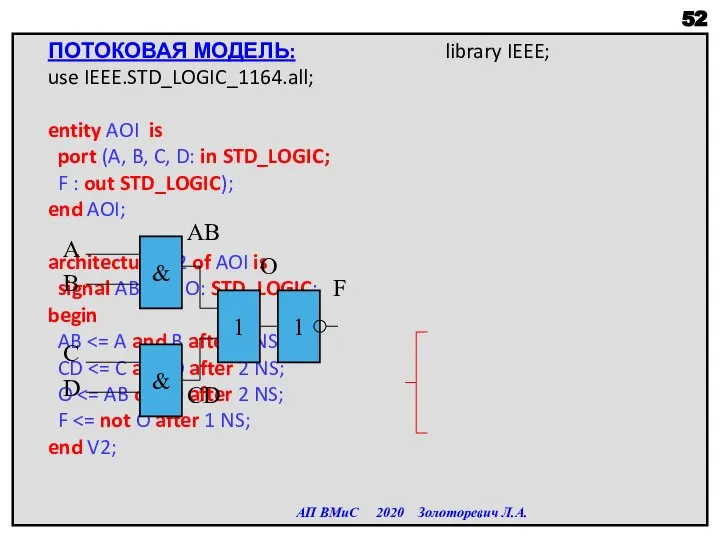

- 52. ПОТОКОВАЯ МОДЕЛЬ: library IEEE; use IEEE.STD_LOGIC_1164.all; entity AOI is port (A, B, C, D: in STD_LOGIC;

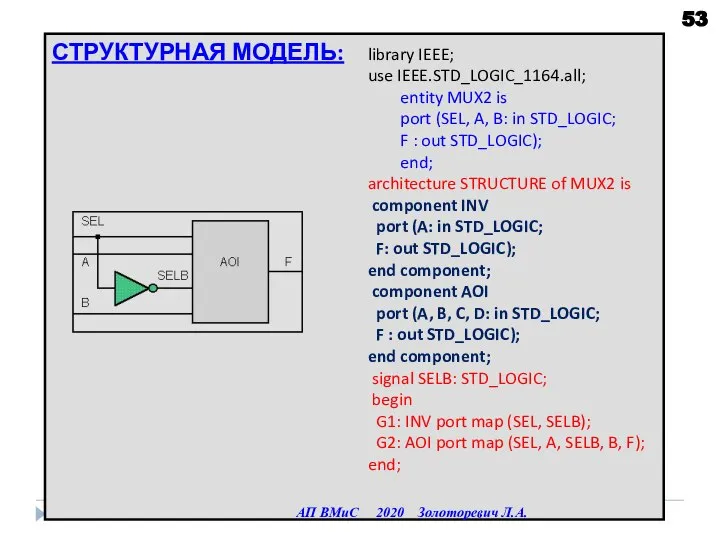

- 53. СТРУКТУРНАЯ МОДЕЛЬ: АП ВМиС 2020 Золоторевич Л.А. library IEEE; use IEEE.STD_LOGIC_1164.all; entity MUX2 is port (SEL,

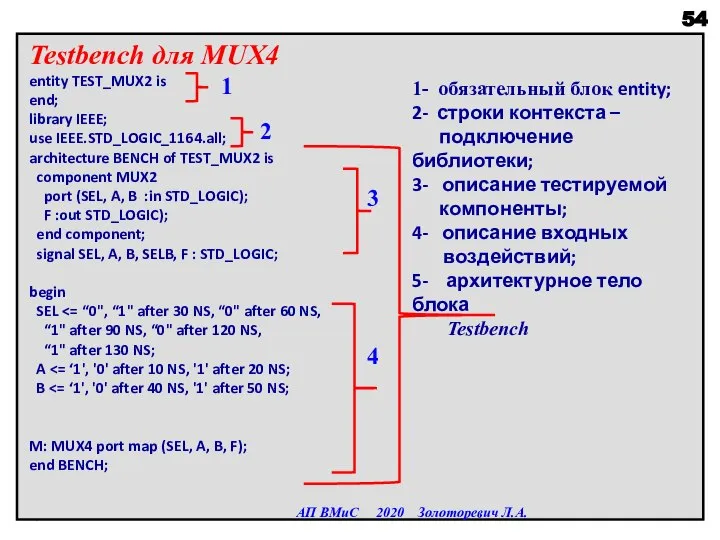

- 54. АП ВМиС 2020 Золоторевич Л.А. Testbench для MUX4 entity TEST_MUX2 is end; library IEEE; use IEEE.STD_LOGIC_1164.all;

- 55. VHDL – строго типизированный язык АП ВМиС 2020 Золоторевич Л.А.

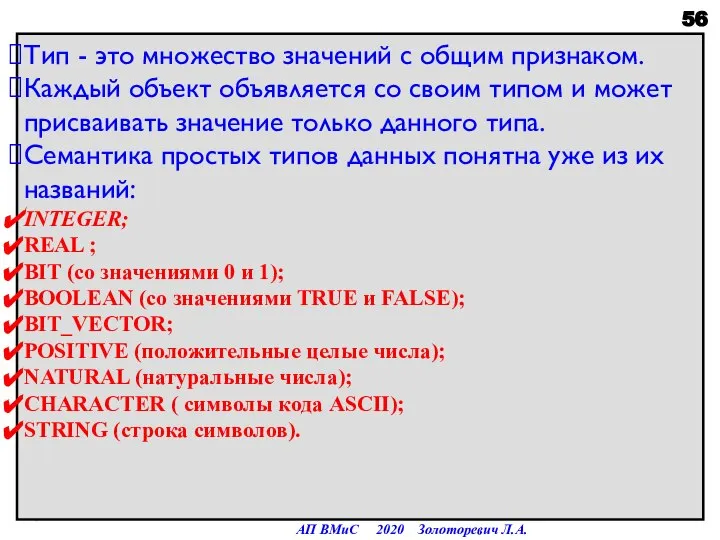

- 56. Тип - это множество значений с общим признаком. Каждый объект объявляется со своим типом и может

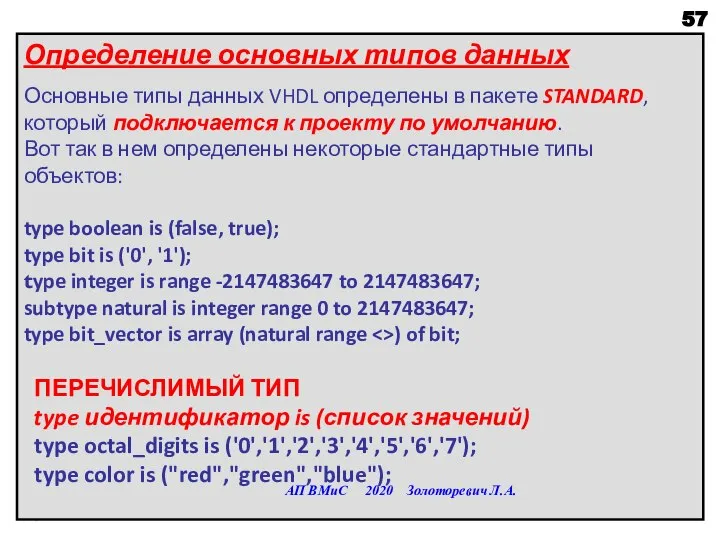

- 57. Определение основных типов данных Основные типы данных VHDL определены в пакете STANDARD, который подключается к проекту

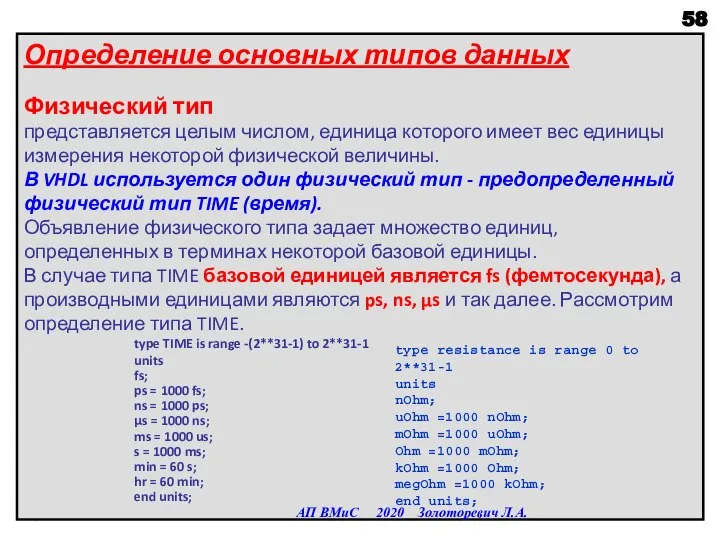

- 58. Определение основных типов данных Физический тип представляется целым числом, единица которого имеет вес единицы измерения некоторой

- 59. Oбъекты языка VHDL Сигнал АП ВМиС 2020 Золоторевич Л.А.

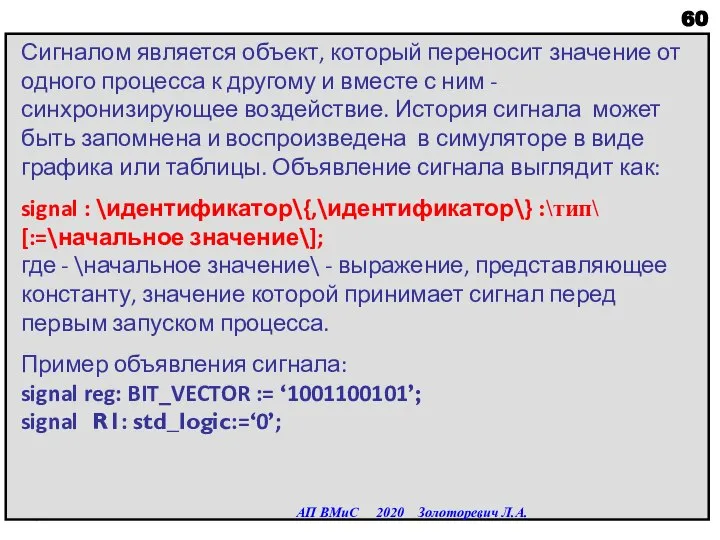

- 60. Сигналом является объект, который переносит значение от одного процесса к другому и вместе с ним -

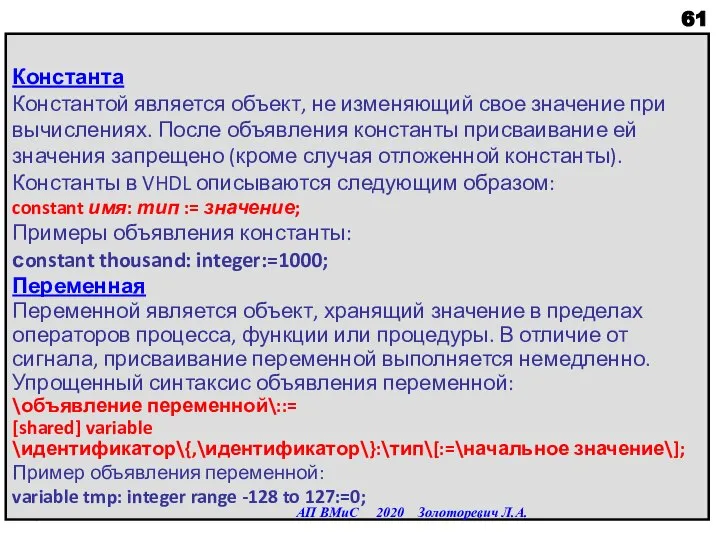

- 61. Константа Константой является объект, не изменяющий свое значение при вычислениях. После объявления константы присваивание ей значения

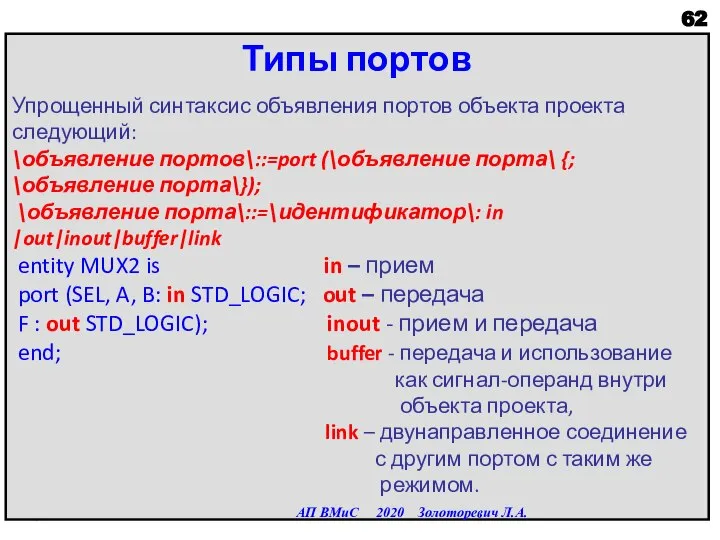

- 62. Типы портов Упрощенный синтаксис объявления портов объекта проекта следующий: \объявление портов\::=port (\объявление порта\ {; \объявление порта\});

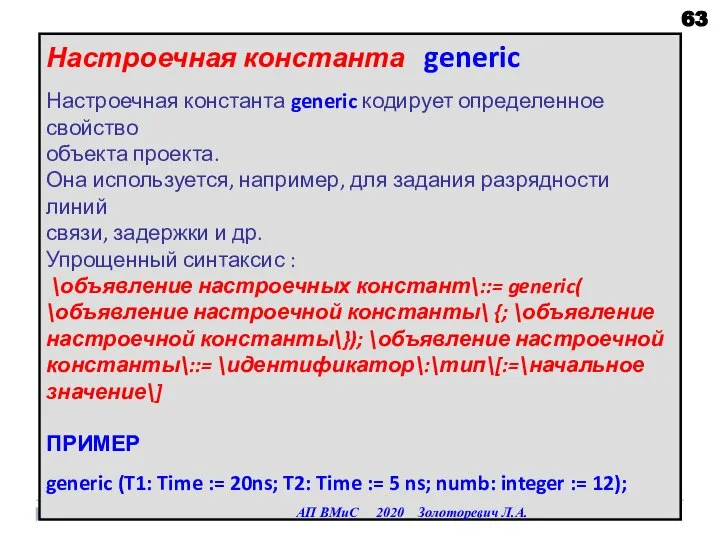

- 63. Настроечная константа generic Настроечная константа generic кодирует определенное свойство объекта проекта. Она используется, например, для задания

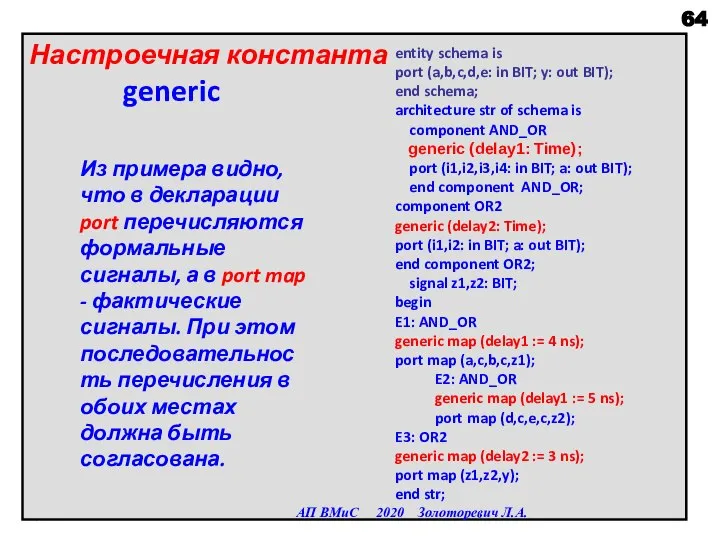

- 64. Настроечная константа generic АП ВМиС 2020 Золоторевич Л.А. entity schema is port (a,b,c,d,e: in BIT; y:

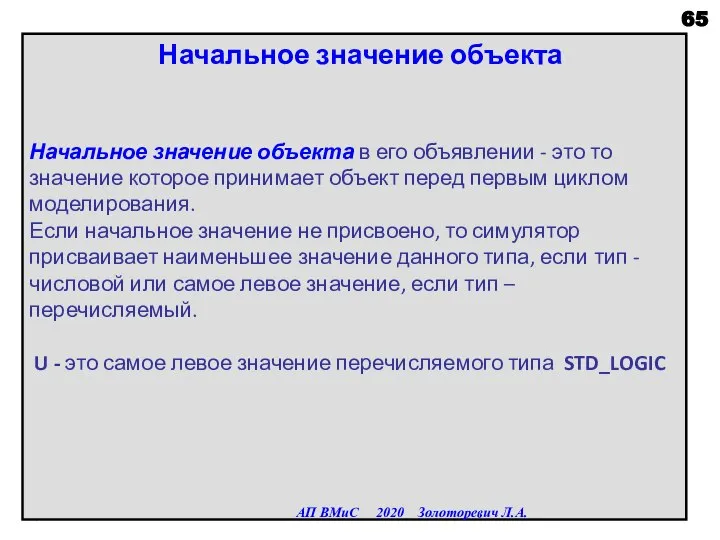

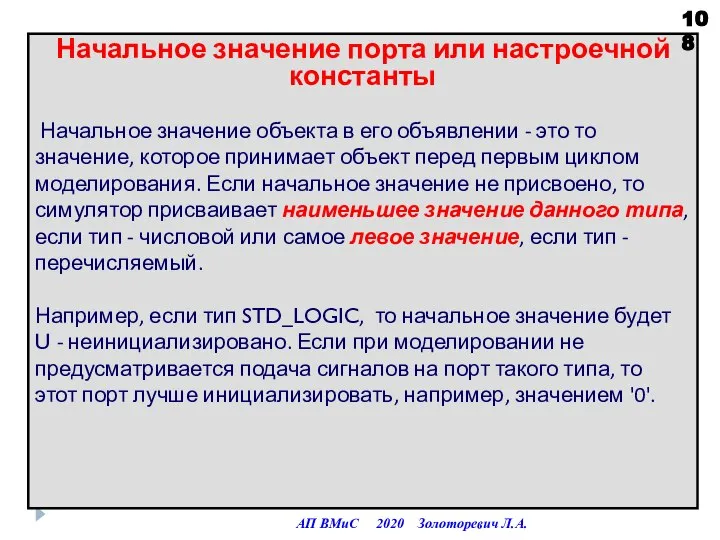

- 65. Начальное значение объекта Начальное значение объекта в его объявлении - это то значение которое принимает объект

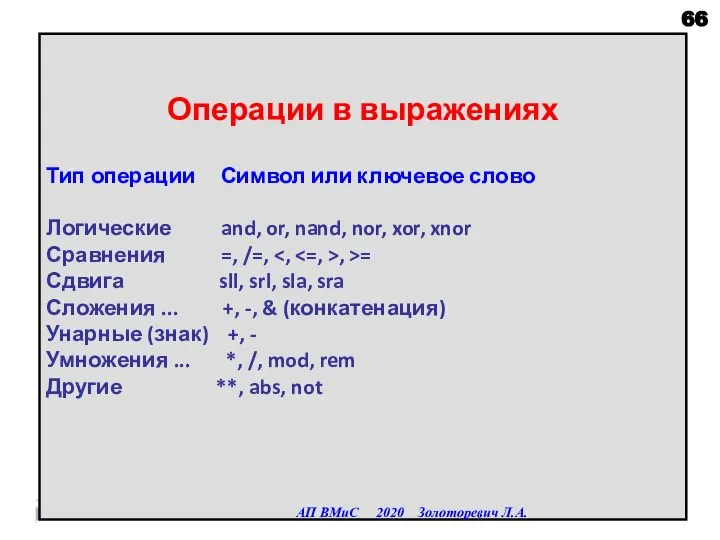

- 66. Операции в выражениях Тип операции Символ или ключевое слово Логические and, or, nand, nor, xor, xnor

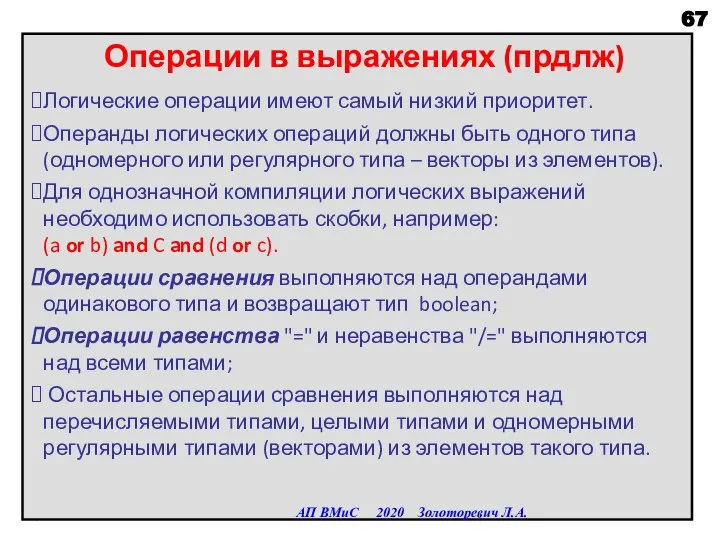

- 67. Операции в выражениях (прдлж) Логические операции имеют самый низкий приоритет. Операнды логических операций должны быть одного

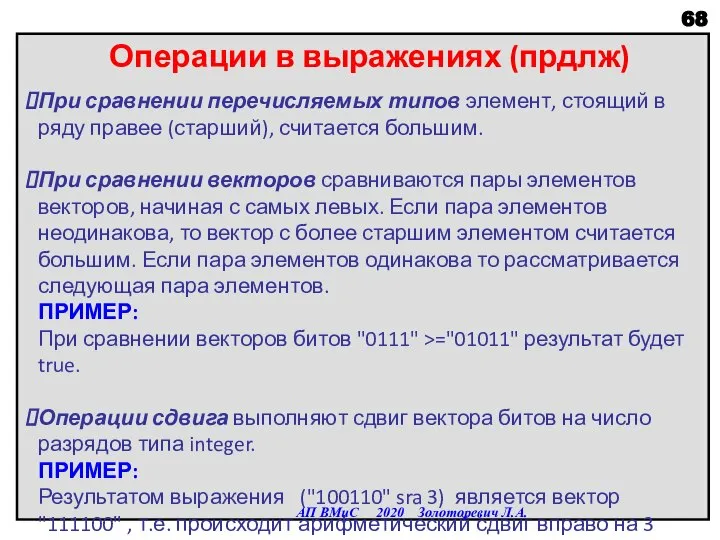

- 68. Операции в выражениях (прдлж) При сравнении перечисляемых типов элемент, стоящий в ряду правее (старший), считается большим.

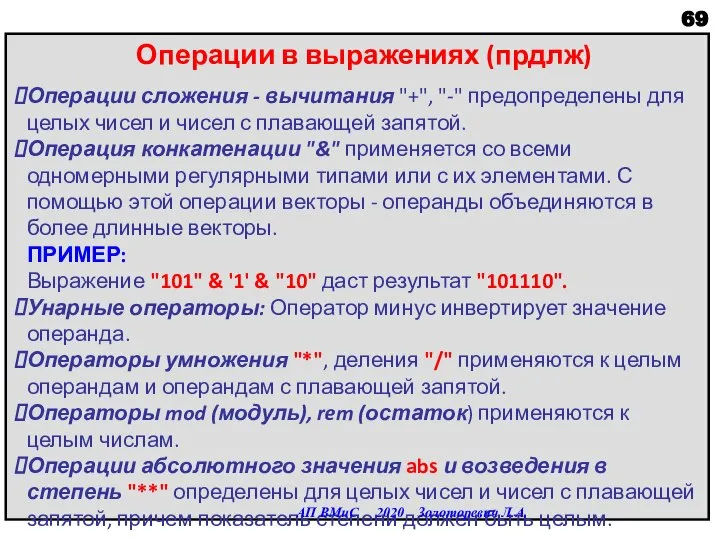

- 69. Операции в выражениях (прдлж) Операции сложения - вычитания "+", "-" предопределены для целых чисел и чисел

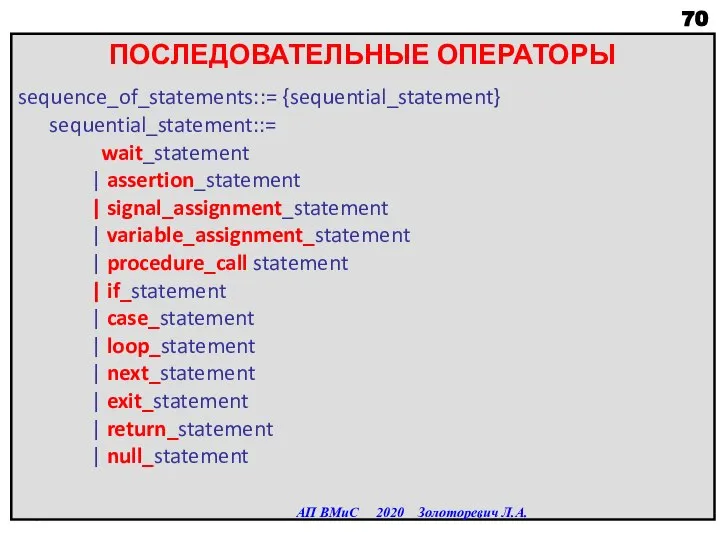

- 70. ПОСЛЕДОВАТЕЛЬНЫЕ ОПЕРАТОРЫ sequence_of_statements::= {sequential_statement} sequential_statement::= wait_statement | assertion_statement | signal_assignment_statement | variable_assignment_statement | procedure_call statement |

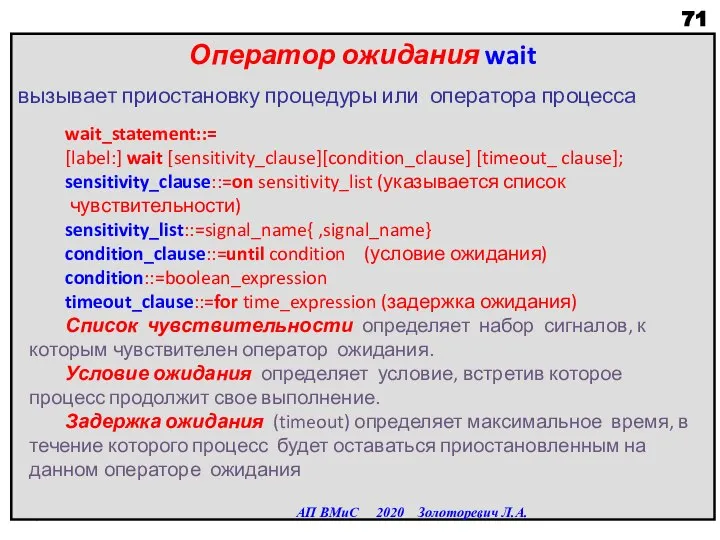

- 71. Оператор ожидания wait вызывает приостановку процедуры или оператора процесса АП ВМиС 2020 Золоторевич Л.А. wait_statement::= [label:]

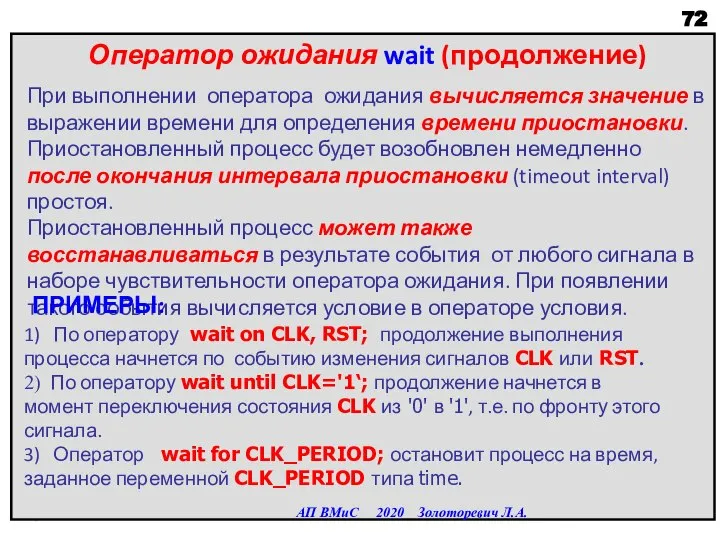

- 72. Оператор ожидания wait (продолжение) При выполнении оператора ожидания вычисляется значение в выражении времени для определения времени

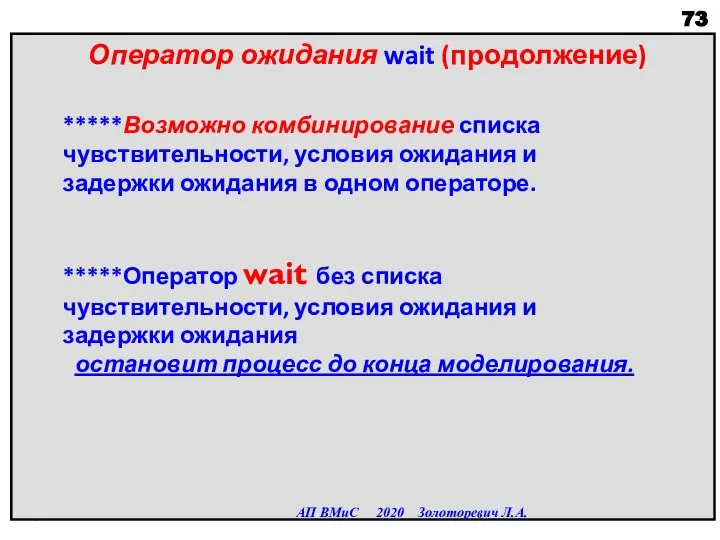

- 73. Оператор ожидания wait (продолжение) АП ВМиС 2020 Золоторевич Л.А. *****Возможно комбинирование списка чувствительности, условия ожидания и

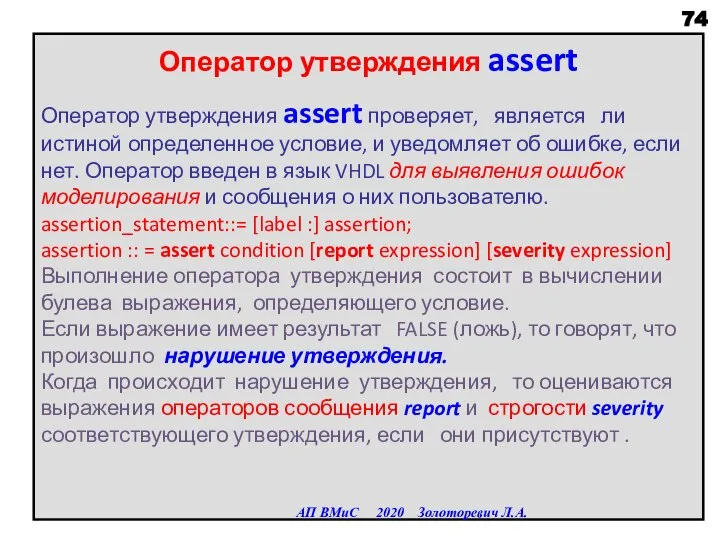

- 74. Оператор утверждения assert Оператор утверждения assert проверяет, является ли истиной определенное условие, и уведомляет об ошибке,

- 75. Оператор утверждения assert (продолжение) assertion_statement::= [label :] assertion; assertion :: = assert condition [report expression] [severity

- 76. Оператор утверждения assert (продолжение) assertion_statement::= [label :] assertion; assertion :: = assert condition [report expression] [severity

- 77. Оператор утверждения assert (продолжение) assertion_statement::= [label :] assertion; assertion :: = assert condition [report expression] [severity

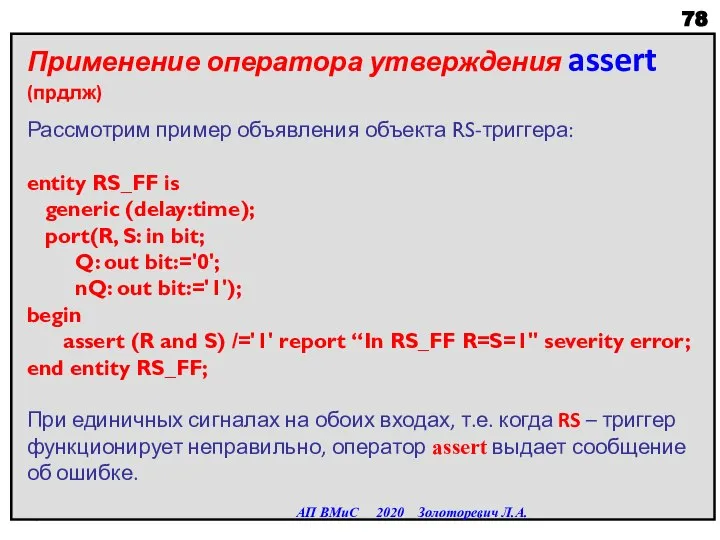

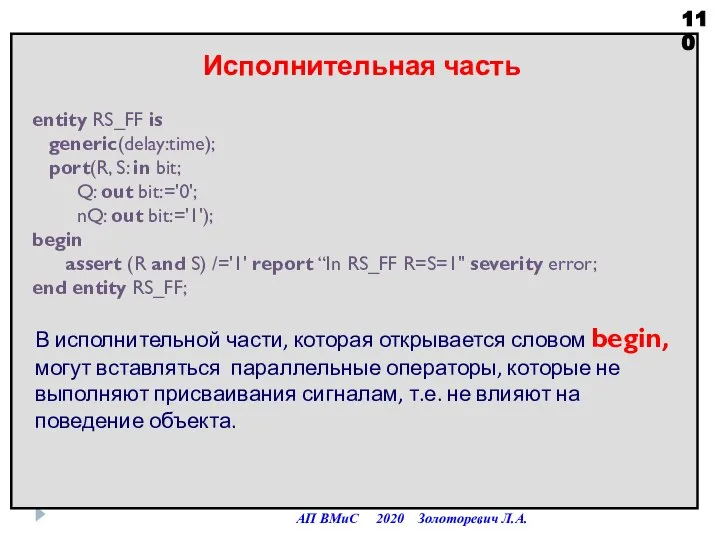

- 78. Применение оператора утверждения assert (прдлж) Рассмотрим пример объявления объекта RS-триггера: entity RS_FF is generic (delay:time); port(R,

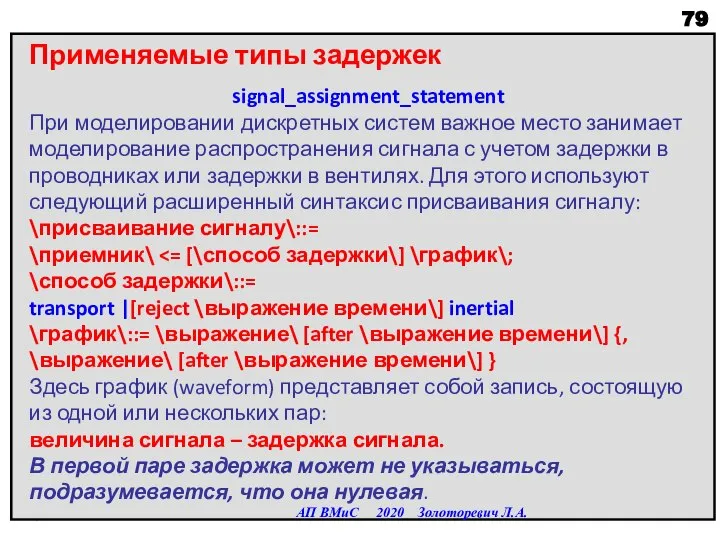

- 79. Применяемые типы задержек signal_assignment_statement При моделировании дискретных систем важное место занимает моделирование распространения сигнала с учетом

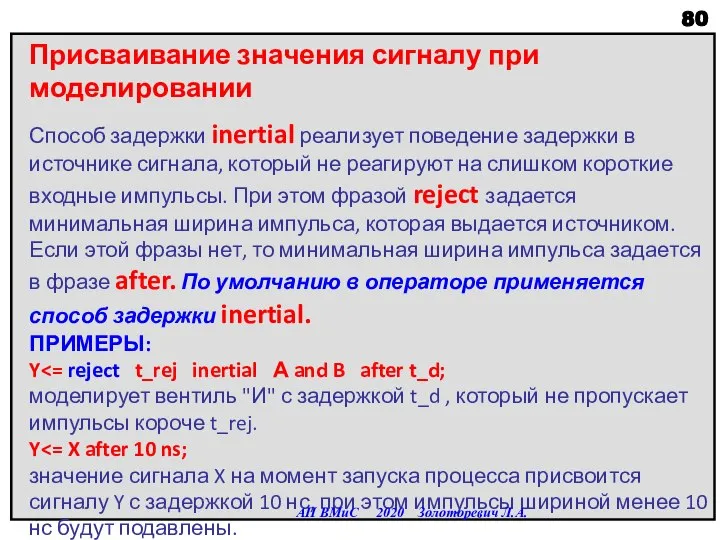

- 80. Присваивание значения сигналу при моделировании Способ задержки inertial реализует поведение задержки в источнике сигнала, который не

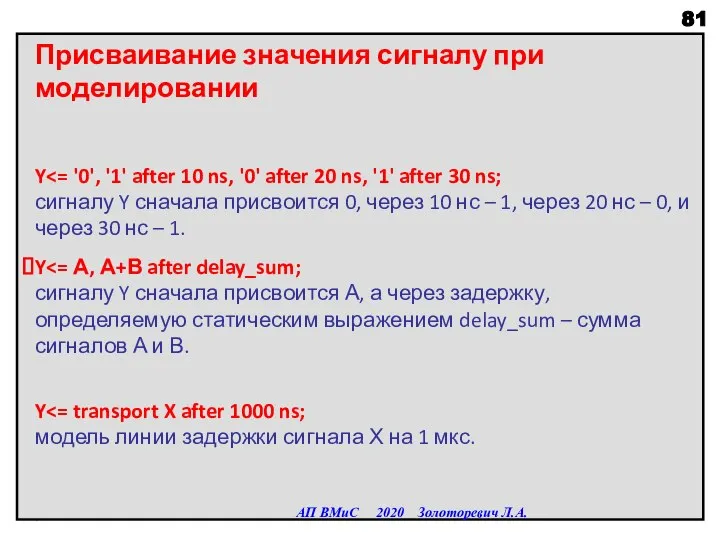

- 81. Присваивание значения сигналу при моделировании Y Y Y АП ВМиС 2020 Золоторевич Л.А.

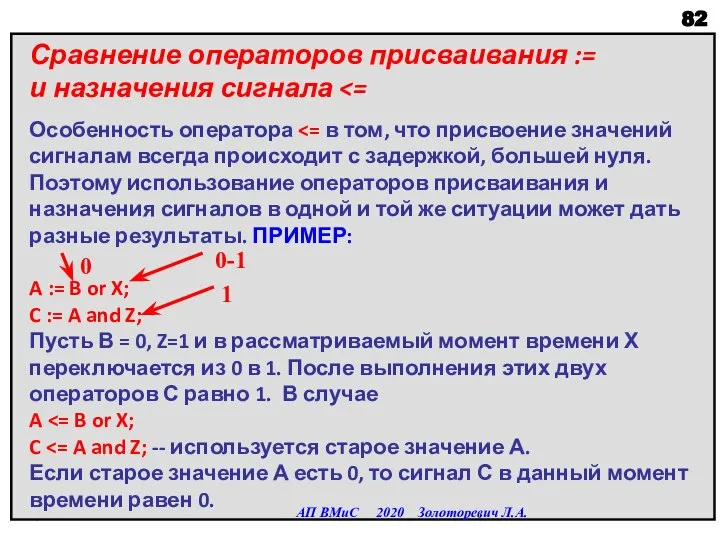

- 82. Сравнение операторов присваивания := и назначения сигнала Особенность оператора Поэтому использование операторов присваивания и назначения сигналов

- 83. ФОРМА БЭКУСА-НАУРА АП ВМиС 2020 Золоторевич Л.А.

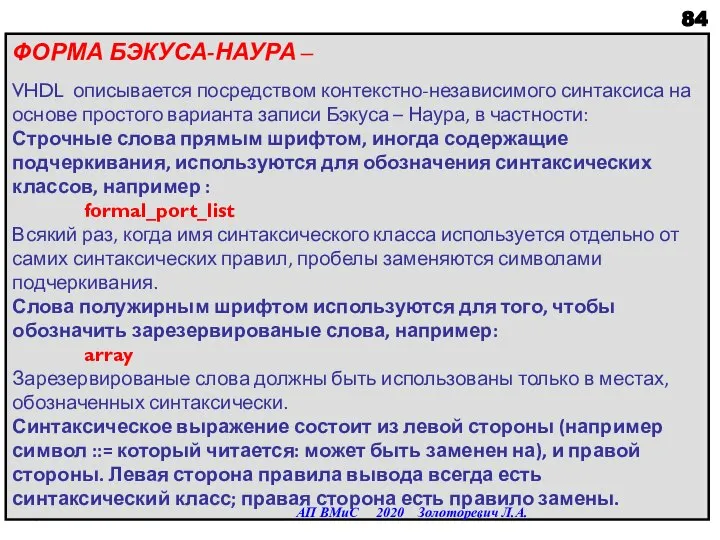

- 84. ФОРМА БЭКУСА-НАУРА – VHDL описывается посредством контекстно-независимого синтаксиса на основе простого варианта записи Бэкуса – Наура,

- 85. ФОРМА БЭКУСА-НАУРА – Синтаксическое выражение подчиняется правилу текстовой замены: любой случай левой стороны может быть заменен

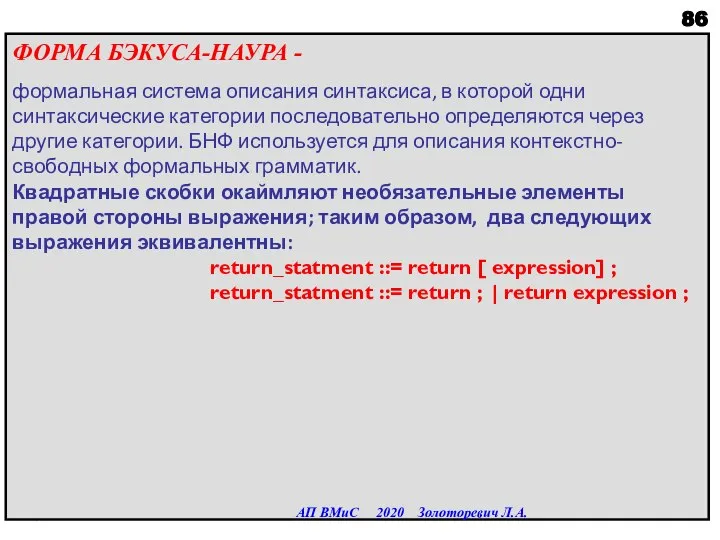

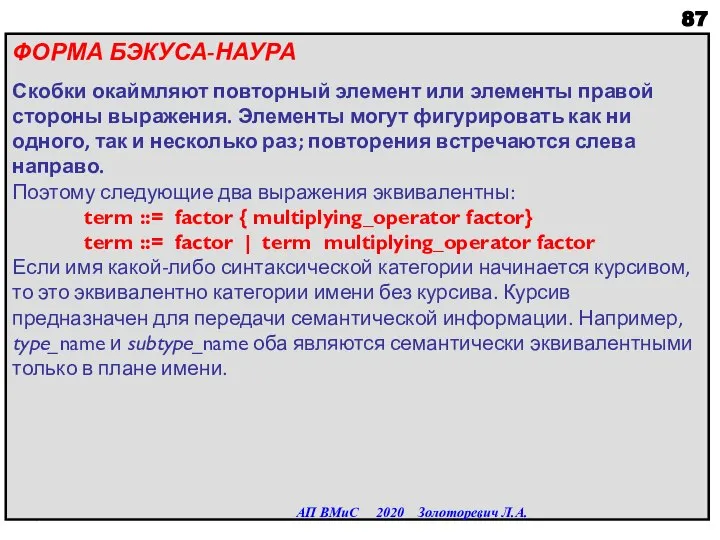

- 86. ФОРМА БЭКУСА-НАУРА - формальная система описания синтаксиса, в которой одни синтаксические категории последовательно определяются через другие

- 87. ФОРМА БЭКУСА-НАУРА Скобки окаймляют повторный элемент или элементы правой стороны выражения. Элементы могут фигурировать как ни

- 88. Оператор case \оператор case\::=case \простое выражение\ is when \альтернативы\ => {\последовательный оператор\} {when \альтернативы\ => {\последовательный

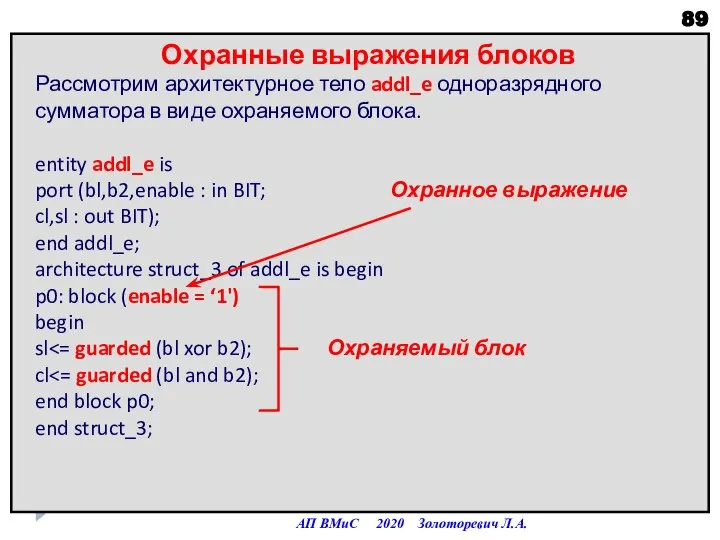

- 89. АП ВМиС 2020 Золоторевич Л.А. Охранные выражения блоков Рассмотрим архитектурное тело addl_e одноразрядного сумматора в виде

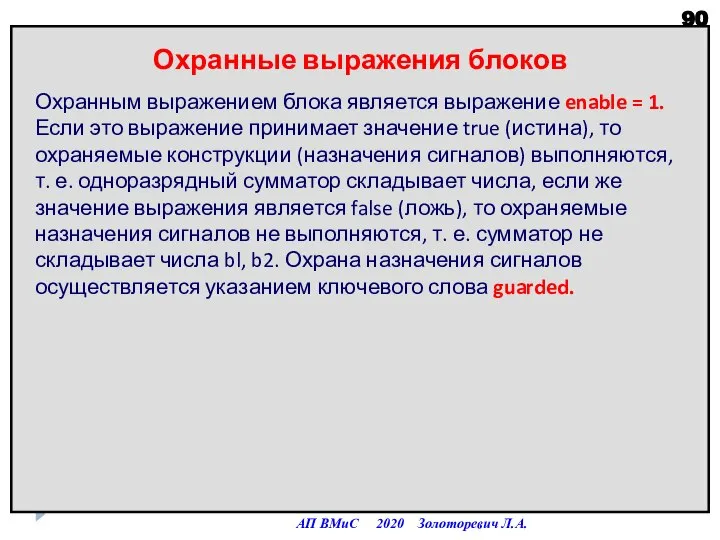

- 90. АП ВМиС 2020 Золоторевич Л.А. Охранные выражения блоков Охранным выражением блока является выражение enable = 1.

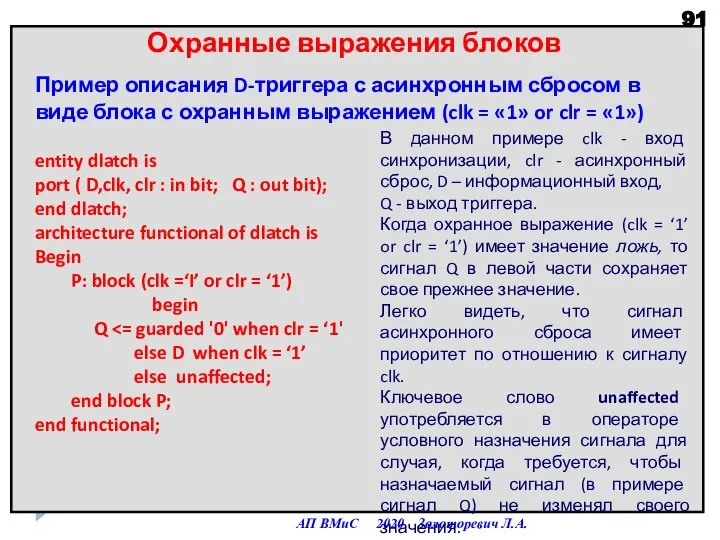

- 91. АП ВМиС 2020 Золоторевич Л.А. Охранные выражения блоков Пример описания D-триггера с асинхронным сбросом в виде

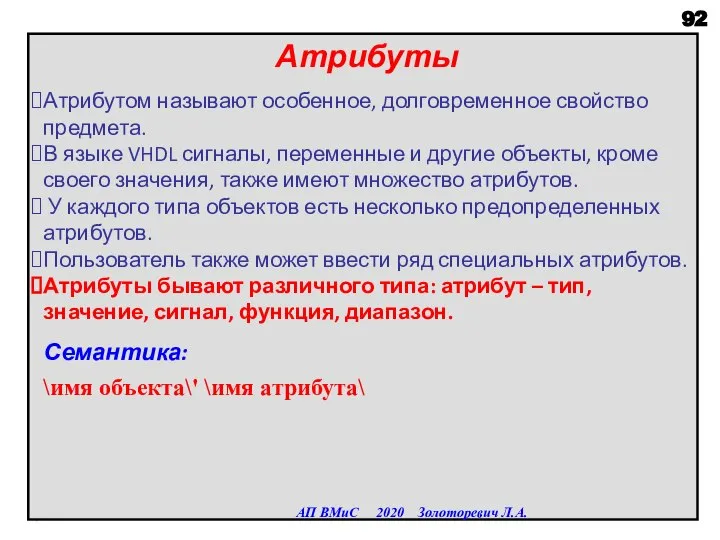

- 92. Атрибуты Атрибутом называют особенное, долговременное свойство предмета. В языке VHDL сигналы, переменные и другие объекты, кроме

- 93. Атрибуты сигналов \имя объекта\' \имя атрибута\ S'stable[(T)] – сигнал, равный true, если за промежуток времени Т

- 94. Атрибуты сигналов АП ВМиС 2020 Золоторевич Л.А. entity signal_ex is end signal_ex; architecture beh of signal_ex

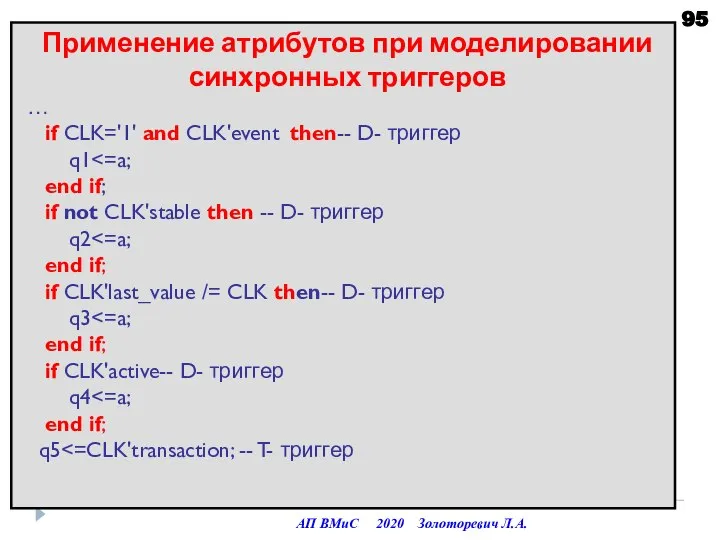

- 95. Применение атрибутов при моделировании синхронных триггеров … if CLK='1' and CLK'event then-- D- триггер q1 end

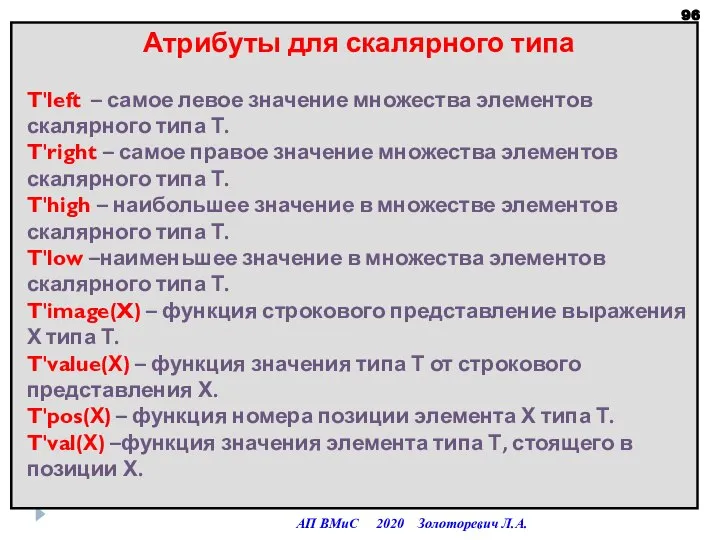

- 96. Атрибуты для скалярного типа T'left – самое левое значение множества элементов скалярного типа Т. T'right –

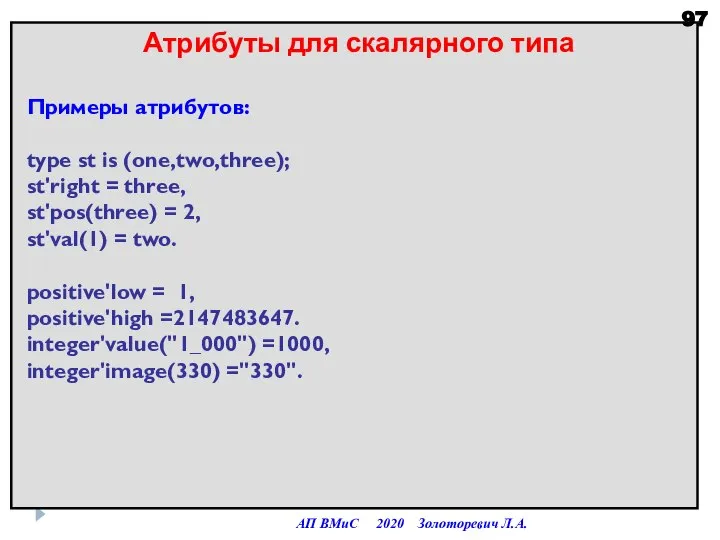

- 97. Атрибуты для скалярного типа Примеры атрибутов: type st is (one,two,three); st'right = three, st'pos(three) = 2,

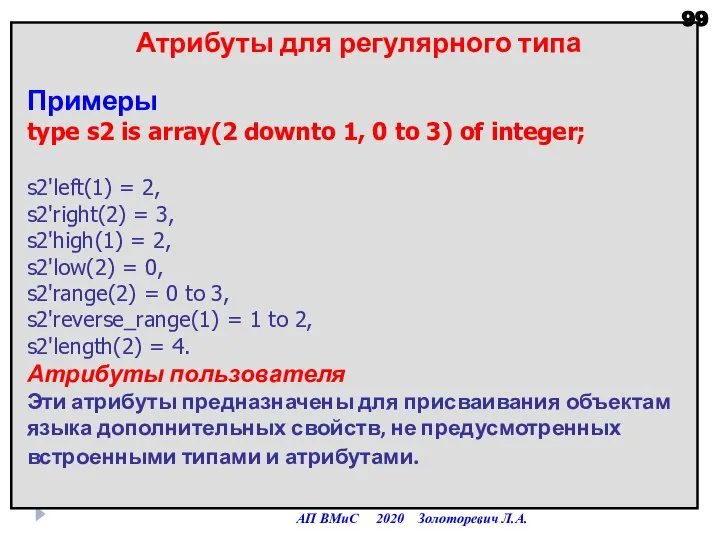

- 98. Атрибуты для регулярного типа A'left[(N)] – левое значение диапазона индексов по N-й размерности. A'right[(N)] - правое

- 99. Атрибуты для регулярного типа Примеры type s2 is array(2 downto 1, 0 to 3) of integer;

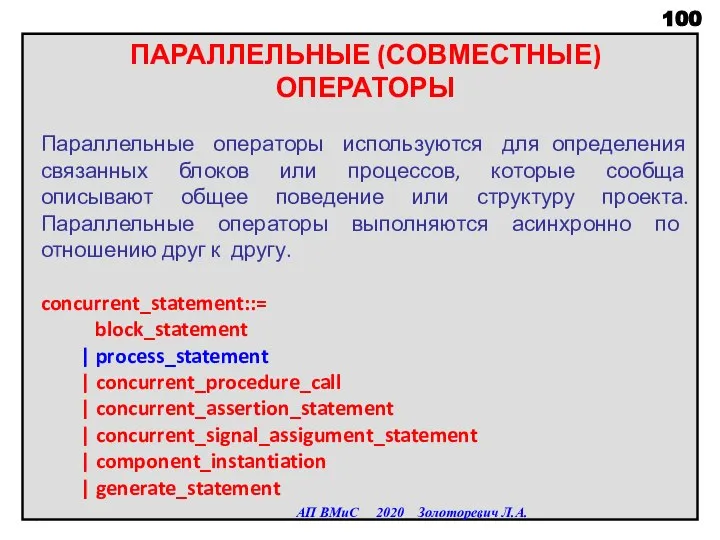

- 100. ПАРАЛЛЕЛЬНЫЕ (СОВМЕСТНЫЕ) ОПЕРАТОРЫ Параллельные операторы используются для определения связанных блоков или процессов, которые сообща описывают общее

- 101. Оператор процесса Упрощенный синтаксис: \оператор процесса\ ::=[postponed] process [(\имя сигнала\ {,\имя сигнала\})] [is] {\объявление в процессе\}

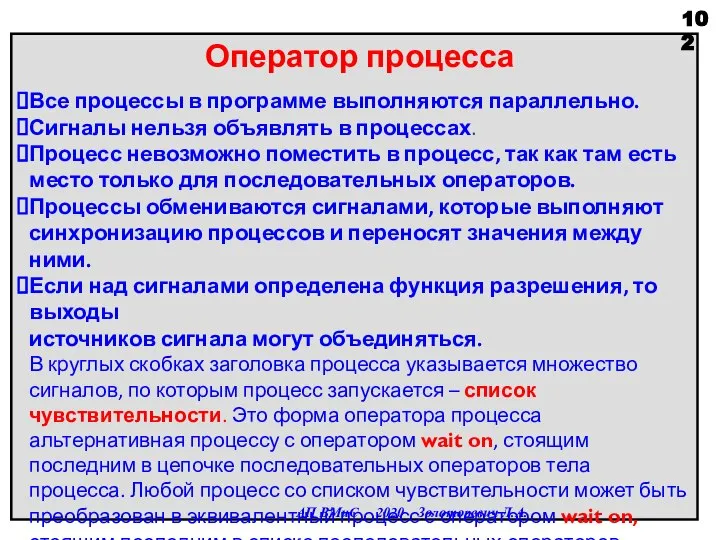

- 102. Оператор процесса Все процессы в программе выполняются параллельно. Сигналы нельзя объявлять в процессах. Процесс невозможно поместить

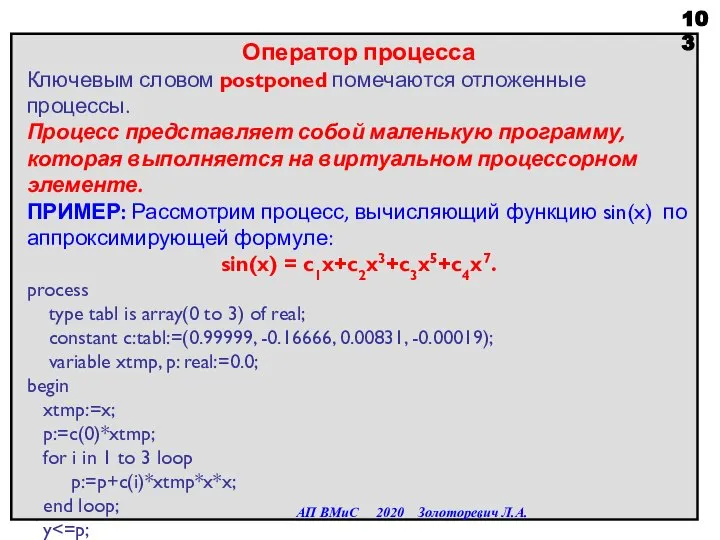

- 103. Оператор процесса Ключевым словом postponed помечаются отложенные процессы. Процесс представляет собой маленькую программу, которая выполняется на

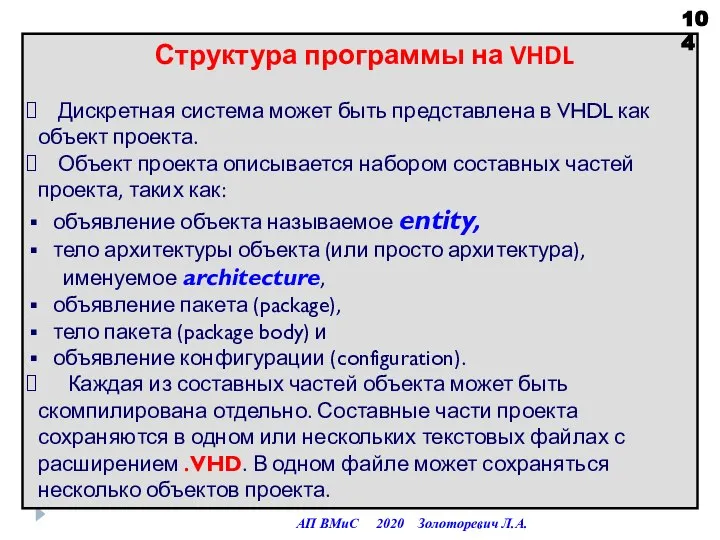

- 104. Структура программы на VHDL Дискретная система может быть представлена в VHDL как объект проекта. Объект проекта

- 105. Объект проекта \объект проекта\::= [\описание library\] [\описание use\] \объявление объекта\ \тело архитектуры\ [\объявление конфигурации\] [\описание library\]::=

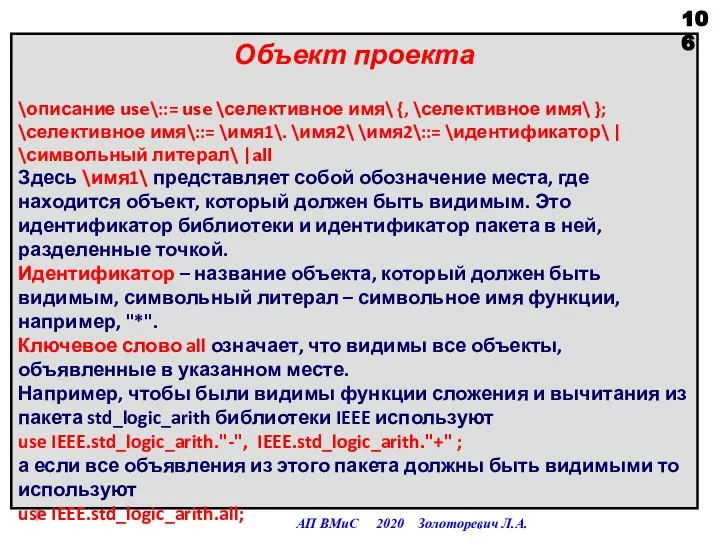

- 106. Объект проекта \описание use\::= use \селективное имя\ {, \селективное имя\ }; \селективное имя\::= \имя1\. \имя2\ \имя2\::=

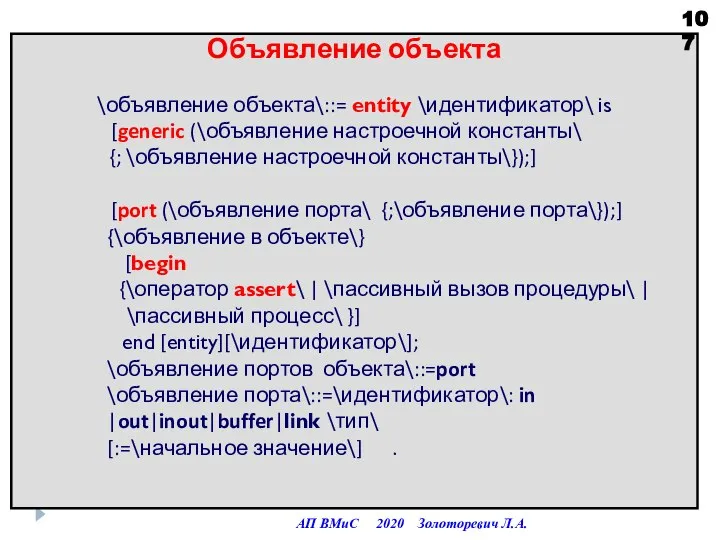

- 107. Объявление объекта \объявление объекта\::= entity \идентификатор\ is [generic (\объявление настроечной константы\ {; \объявление настроечной константы\});] [port

- 108. Начальное значение порта или настроечной константы Начальное значение объекта в его объявлении - это то значение,

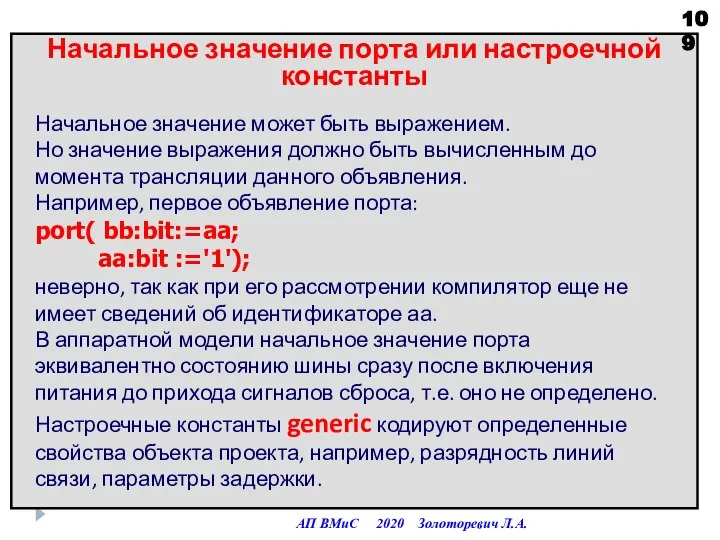

- 109. Начальное значение порта или настроечной константы АП ВМиС 2020 Золоторевич Л.А. Начальное значение может быть выражением.

- 110. АП ВМиС 2020 Золоторевич Л.А. Исполнительная часть В исполнительной части, которая открывается словом begin, могут вставляться

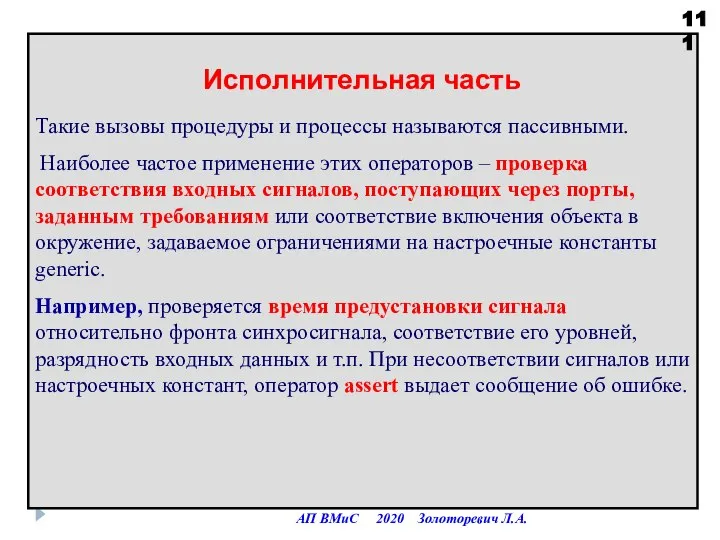

- 111. Такие вызовы процедуры и процессы называются пассивными. Наиболее частое применение этих операторов – проверка соответствия входных

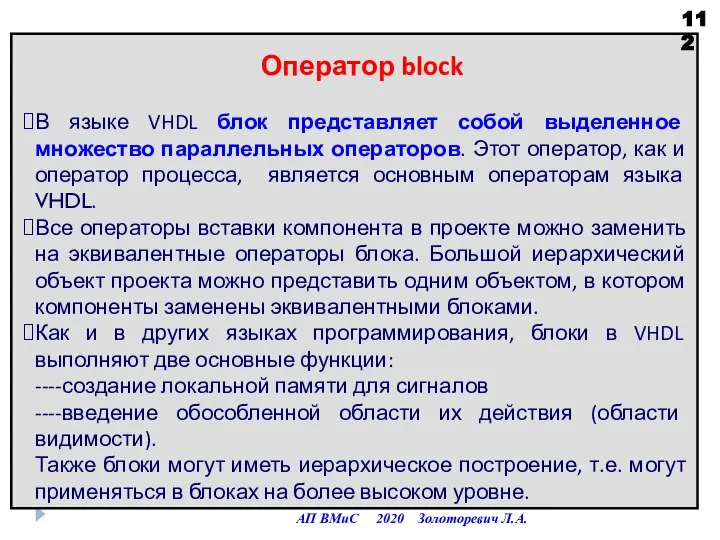

- 112. АП ВМиС 2020 Золоторевич Л.А. Оператор block В языке VHDL блок представляет собой выделенное множество параллельных

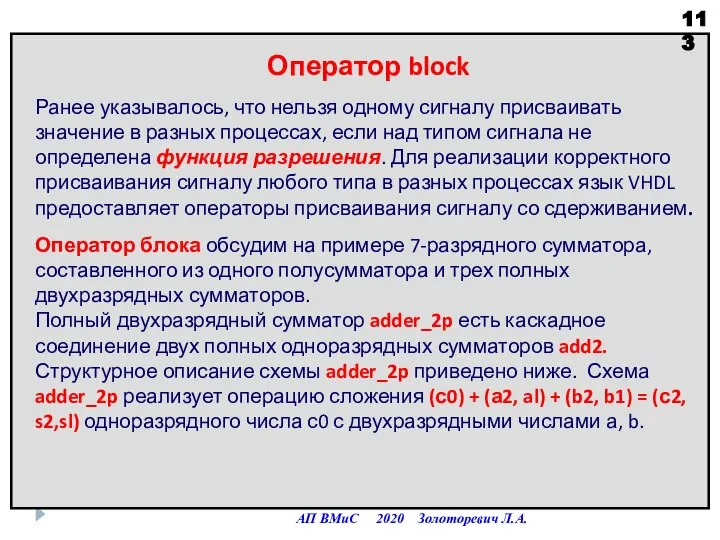

- 113. АП ВМиС 2020 Золоторевич Л.А. Оператор block Ранее указывалось, что нельзя одному сигналу присваивать значение в

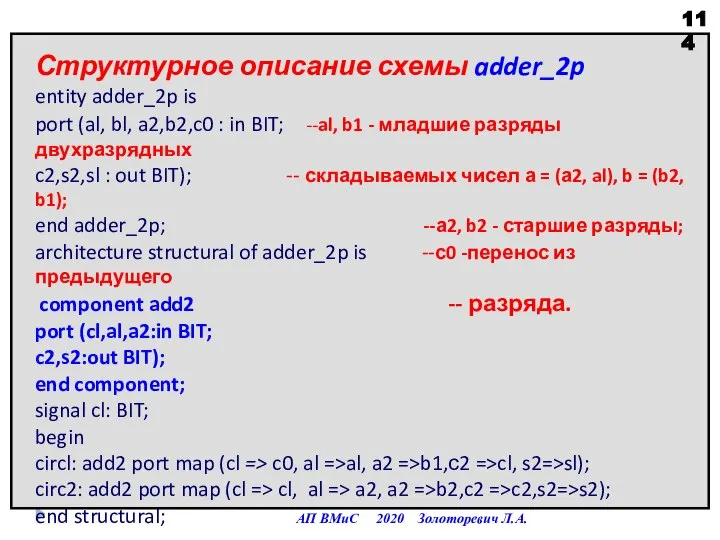

- 114. АП ВМиС 2020 Золоторевич Л.А. Структурное описание схемы adder_2p entity adder_2p is port (al, bl, a2,b2,c0

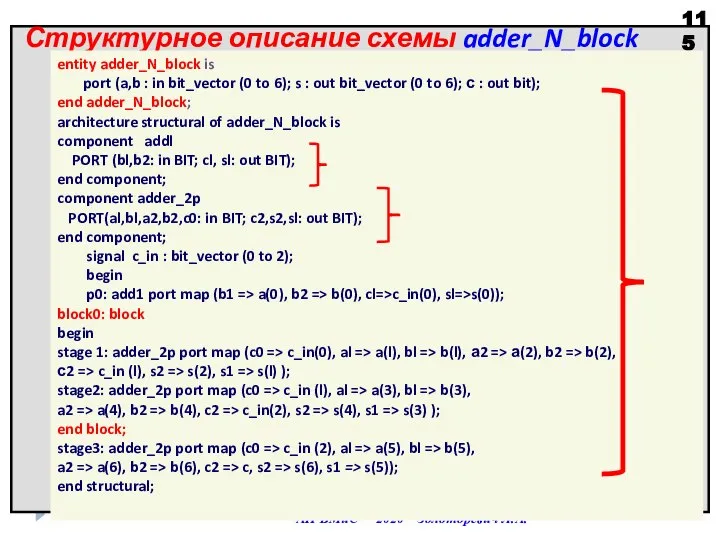

- 115. АП ВМиС 2020 Золоторевич Л.А. Структурное описание схемы adder_N_block entity adder_N_block is port (a,b : in

- 116. Информация для выполнения проекта АП ВМиС 2020 Золоторевич Л.А.

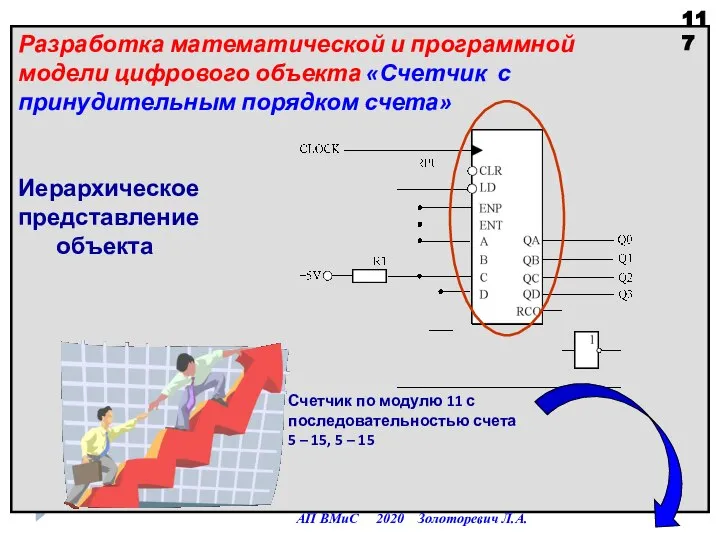

- 117. Разработка математической и программной модели цифрового объекта «Счетчик с принудительным порядком счета» Иерархическое представление объекта АП

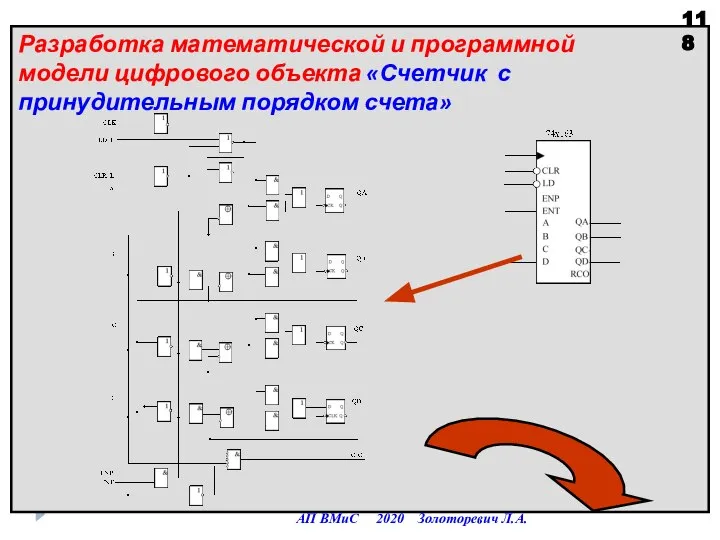

- 118. Разработка математической и программной модели цифрового объекта «Счетчик с принудительным порядком счета» АП ВМиС 2020 Золоторевич

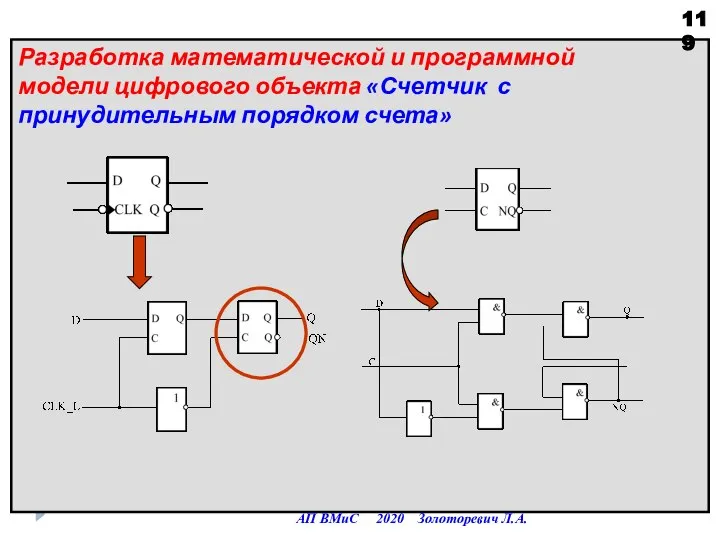

- 119. Разработка математической и программной модели цифрового объекта «Счетчик с принудительным порядком счета» АП ВМиС 2020 Золоторевич

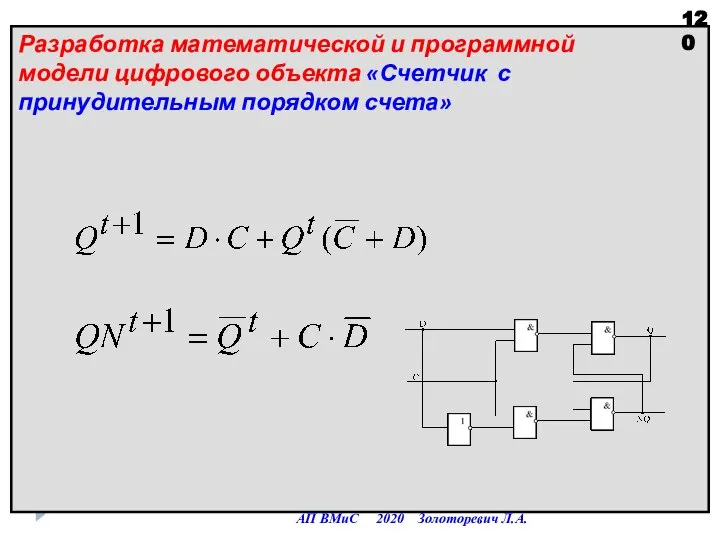

- 120. Разработка математической и программной модели цифрового объекта «Счетчик с принудительным порядком счета» АП ВМиС 2020 Золоторевич

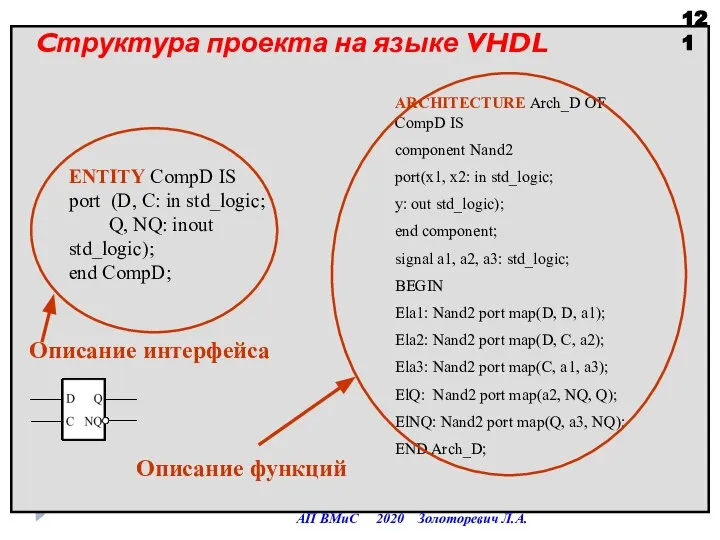

- 121. АП ВМиС 2020 Золоторевич Л.А. Cтруктура проекта на языке VHDL ENTITY CompD IS port (D, C:

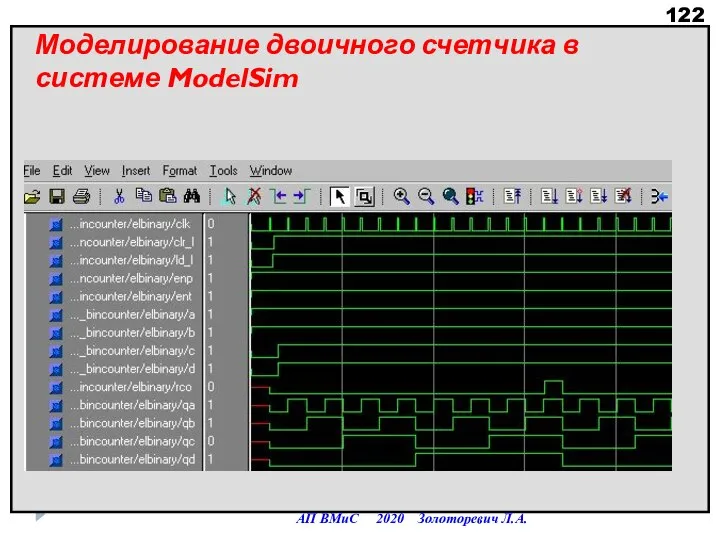

- 122. АП ВМиС 2020 Золоторевич Л.А. Моделирование двоичного счетчика в системе ModelSim

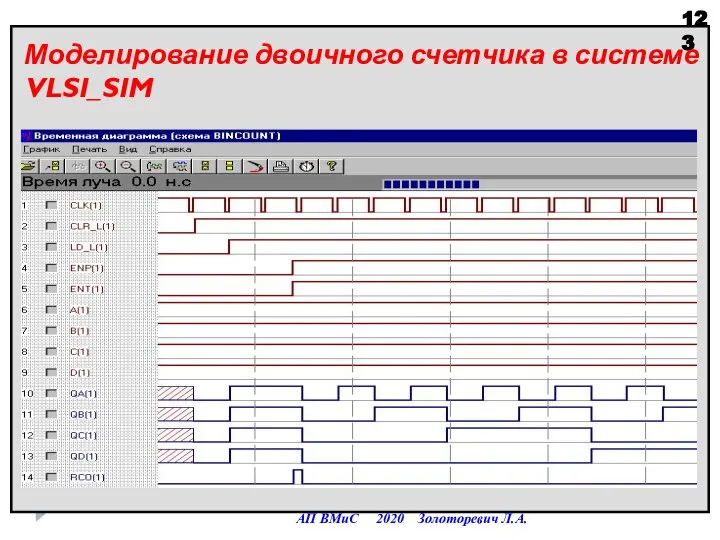

- 123. АП ВМиС 2020 Золоторевич Л.А. Моделирование двоичного счетчика в системе VLSI_SIM

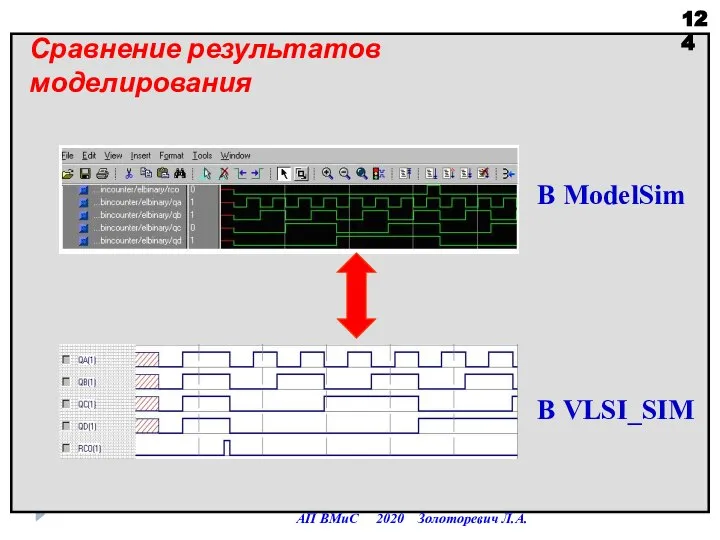

- 124. АП ВМиС 2020 Золоторевич Л.А. Сравнение результатов моделирования В ModelSim В VLSI_SIM

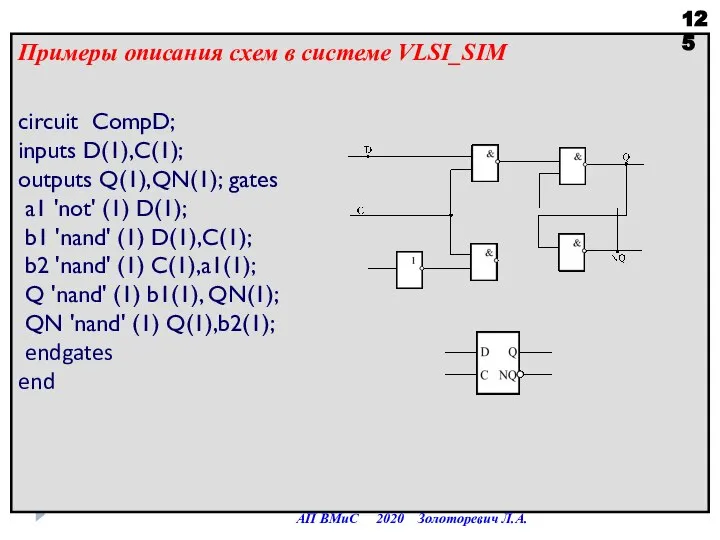

- 125. Примеры описания схем в системе VLSI_SIM circuit CompD; inputs D(1),C(1); outputs Q(1),QN(1); gates a1 'not' (1)

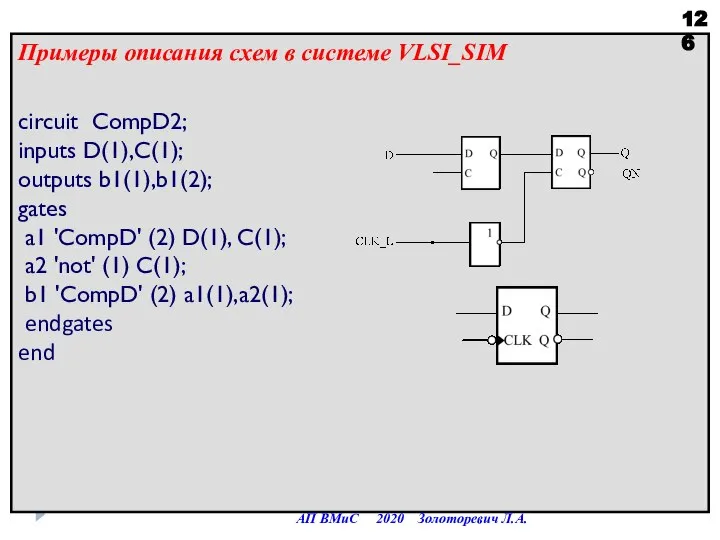

- 126. Примеры описания схем в системе VLSI_SIM circuit CompD2; inputs D(1),C(1); outputs b1(1),b1(2); gates a1 'CompD' (2)

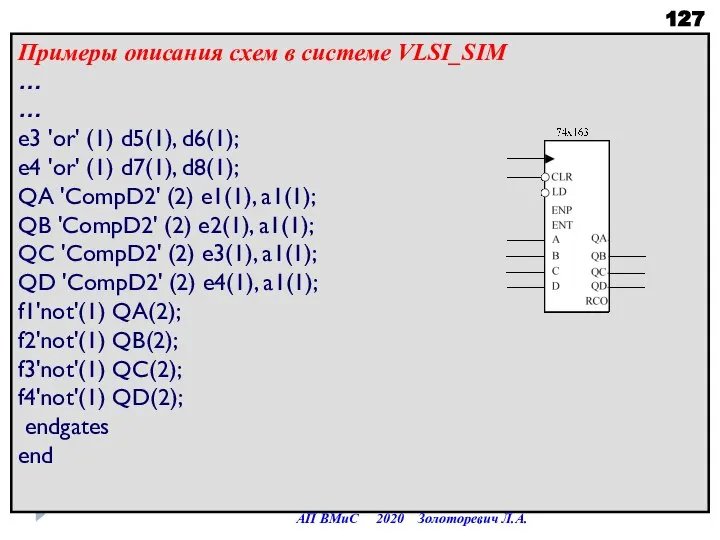

- 127. Примеры описания схем в системе VLSI_SIM … … e3 'or' (1) d5(1), d6(1); e4 'or' (1)

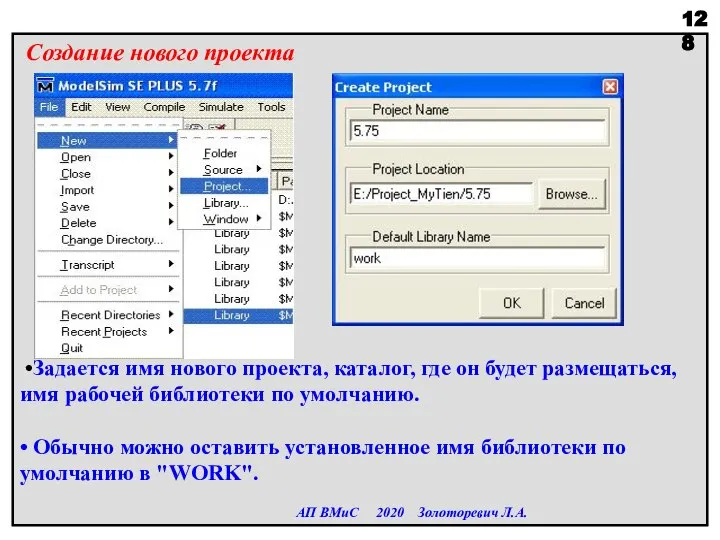

- 128. Создание нового проекта •Задается имя нового проекта, каталог, где он будет размещаться, имя рабочей библиотеки по

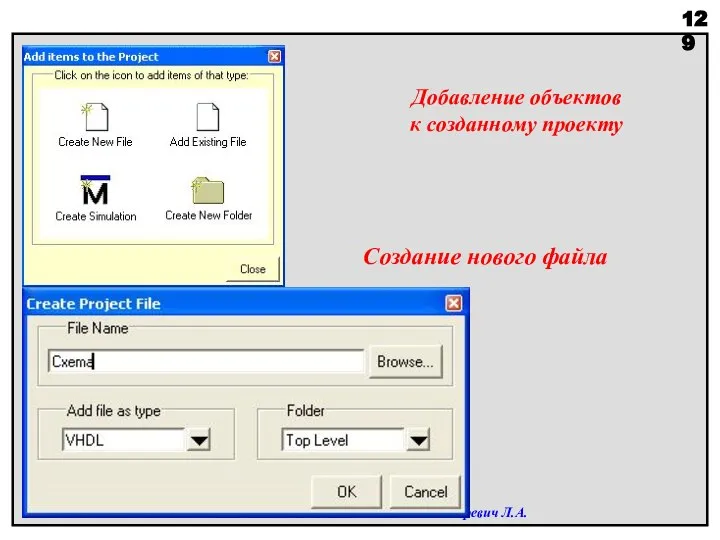

- 129. АП ВМиС 2020 Золоторевич Л.А. Добавление объектов к созданному проекту Создание нового файла

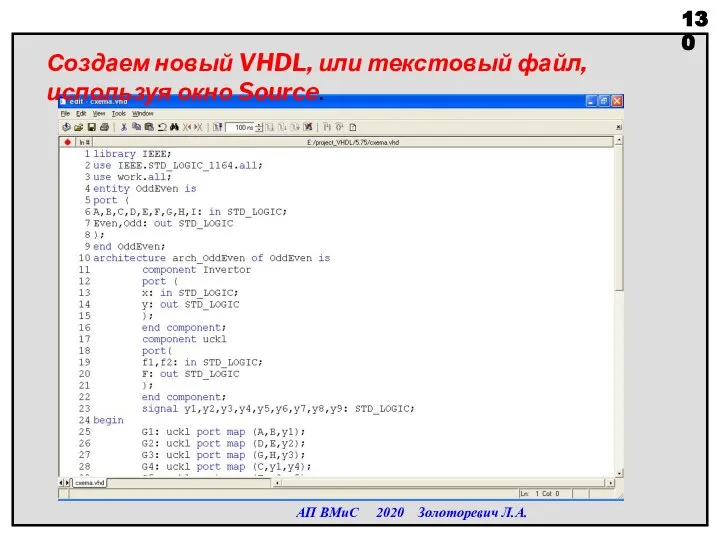

- 130. АП ВМиС 2020 Золоторевич Л.А. Создаем новый VHDL, или текстовый файл, используя окно Source.

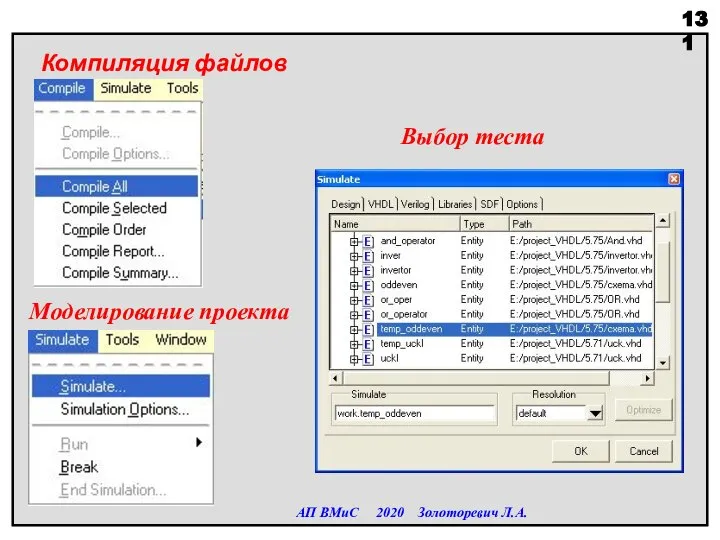

- 131. АП ВМиС 2020 Золоторевич Л.А. Компиляция файлов Моделирование проекта Выбор теста

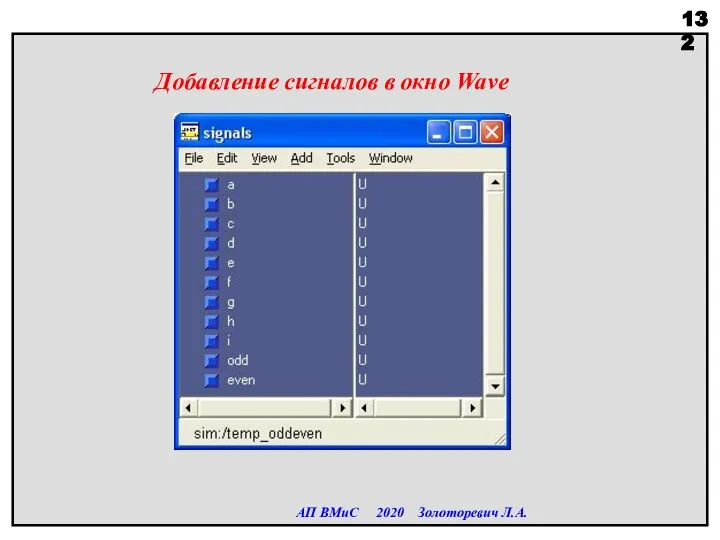

- 132. АП ВМиС 2020 Золоторевич Л.А. Добавление сигналов в окно Wave

- 134. Скачать презентацию

![Оператор утверждения assert (продолжение) assertion_statement::= [label :] assertion; assertion :: = assert](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-74.jpg)

![Оператор утверждения assert (продолжение) assertion_statement::= [label :] assertion; assertion :: = assert](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-75.jpg)

![Оператор утверждения assert (продолжение) assertion_statement::= [label :] assertion; assertion :: = assert](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-76.jpg)

![Атрибуты сигналов \имя объекта\' \имя атрибута\ S'stable[(T)] – сигнал, равный true, если](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-92.jpg)

![Атрибуты для регулярного типа A'left[(N)] – левое значение диапазона индексов по N-й](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-97.jpg)

![Оператор процесса Упрощенный синтаксис: \оператор процесса\ ::=[postponed] process [(\имя сигнала\ {,\имя сигнала\})]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-100.jpg)

![Объект проекта \объект проекта\::= [\описание library\] [\описание use\] \объявление объекта\ \тело архитектуры\](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1011846/slide-104.jpg)

Решение проблем входа пользователя профессионального программного обеспечения в систему

Решение проблем входа пользователя профессионального программного обеспечения в систему Online mic test

Online mic test Реализация инновационных проектов в общеобразовательной практике с использованием цифровых решений

Реализация инновационных проектов в общеобразовательной практике с использованием цифровых решений Табулирование функций (без подпрограмм)

Табулирование функций (без подпрограмм) L_6_2

L_6_2 Исполнитель Черепашка

Исполнитель Черепашка Анализ информационных моделей

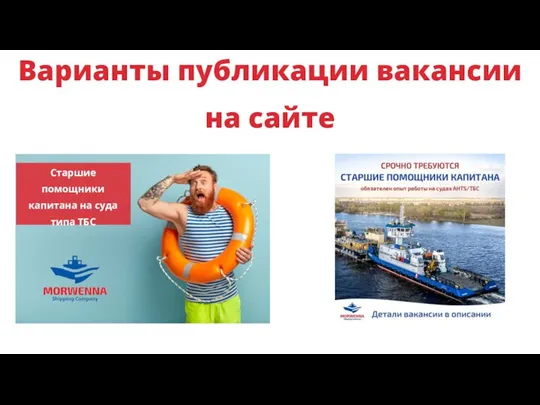

Анализ информационных моделей Варианты публикации вакансии на сайте

Варианты публикации вакансии на сайте Сайт знакомств BezDebilov

Сайт знакомств BezDebilov Работа с файлами, каталогами и стандартными программами

Работа с файлами, каталогами и стандартными программами Художественный текст – основной источник информации

Художественный текст – основной источник информации Моделирование причёски

Моделирование причёски Критерии оценки дизайна сайтов

Критерии оценки дизайна сайтов Циклические алгоритмы (2)

Циклические алгоритмы (2) Bil-481. Veri depolama. Face Detection App

Bil-481. Veri depolama. Face Detection App How to make people happy

How to make people happy Что такое компьютерная графика

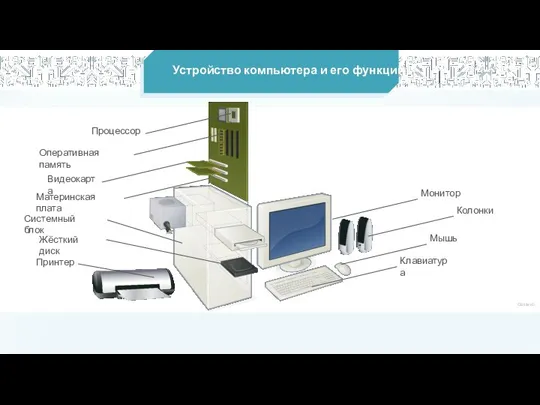

Что такое компьютерная графика Устройство компьютера и его функции

Устройство компьютера и его функции Информатика, основные понятия

Информатика, основные понятия Прикладное программное обеспечение. 1 занятие

Прикладное программное обеспечение. 1 занятие Презентация на тему Компьютерная графика

Презентация на тему Компьютерная графика  Гигатест

Гигатест Программирование на языке Python. Циклические алгоритмы

Программирование на языке Python. Циклические алгоритмы Квалификационная работа: методы и средства защиты информации в сетях на примере ООО Дестени медиа

Квалификационная работа: методы и средства защиты информации в сетях на примере ООО Дестени медиа Класс. Описание класса

Класс. Описание класса Кластеризация текстов

Кластеризация текстов Разработка печати 3D модели

Разработка печати 3D модели Кейс. Интернет-магазин мужской одежды Bismark-shop

Кейс. Интернет-магазин мужской одежды Bismark-shop