Слайд 2Размещение многобайтной команды в памяти

Адрес команды в памяти – это адрес ее

первого байта (байт СОР).

Каждый последующий байт команды располагается в памяти по адресу, на 1 больше предыдущего

Пример: Пусть, CS:0007 - адрес 4-байтной команды (0007 - 16–разрядный внутрисегментный адрес)

Адреса байтов памяти, которые занимает команда? Байты памяти с адреса CS:0007 по CS: 000A

Слайд 3Основные группы команд

Команды пересылки данных. Перемещают (копируют) данные между регистрами процессора, памятью

и портами. Не влияют на флаги.

Команды двоичной арифметики. Устанавливают арифметические флаги.

Команды логических операций. Выполняют операции булевой алгебры. Устанавливаются некоторые флаги.

Команды сдвигов. Выполняют сдвиг кода в регистре или памяти на заданное количество бит. Влияют на флаг CF.

Команды битовых операций. Манипулируют с отдельным битом регистра или памяти

Команды передачи управления, вызова процедур, прерываний. Их назначение - нарушить линейную последовательность чтения процессором команд из памяти.

Слайд 4Операнды в командах

Команды без операндов

CLC ; сброс флага CF

◻ Команды с 1-м

операндом

INC BX ; увеличить на 1 код в регистре ВХ

Команды с 2-мя операндами.

Результат записывается на место 1-го операнда

ADD AL, BL ; AL ← AL + BL

ADD AL, 3 ; AL ← AL + 3

ADD ds:[7], BL ; ds:[0007]←ds:[0007]+BL

!! Недопустимое сочетание двух операндов: “память - память“

Слайд 5Типы операндов в командах

Операнд

Регистр

Память

Непосредственный операнд

Что указывается в команде?

→ Имя регистра

→

Адрес памяти

→ числовой или символьный код

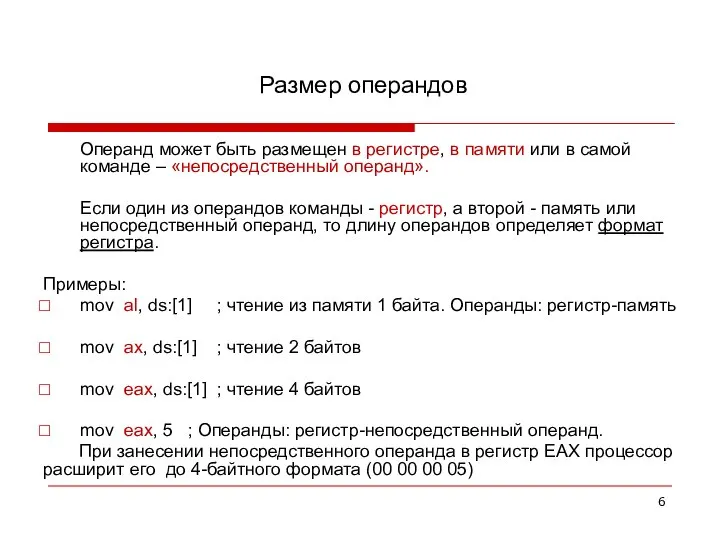

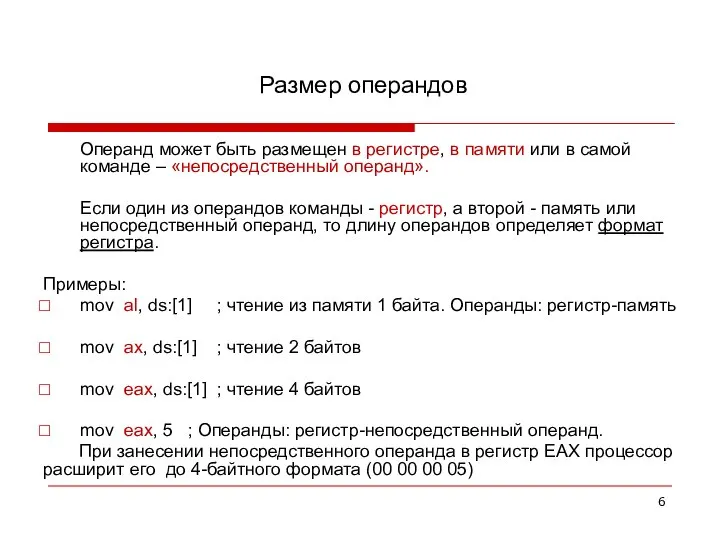

Слайд 6Размер операндов

Операнд может быть размещен в регистре, в памяти или в самой

команде – «непосредственный операнд».

Если один из операндов команды - регистр, а второй - память или непосредственный операнд, то длину операндов определяет формат регистра.

Примеры:

mov al, ds:[1] ; чтение из памяти 1 байта. Операнды: регистр-память

mov aх, ds:[1] ; чтение 2 байтов

mov еaх, ds:[1] ; чтение 4 байтов

mov еaх, 5 ; Операнды: регистр-непосредственный операнд.

При занесении непосредственного операнда в регистр ЕАХ процессор расширит его до 4-байтного формата (00 00 00 05)

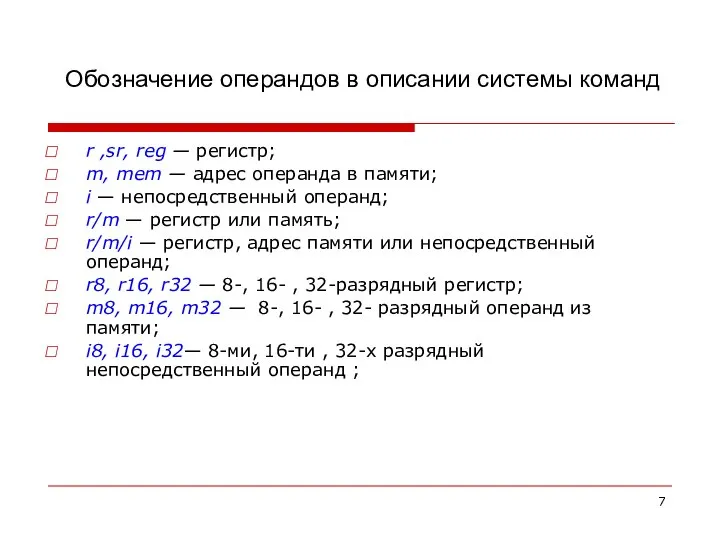

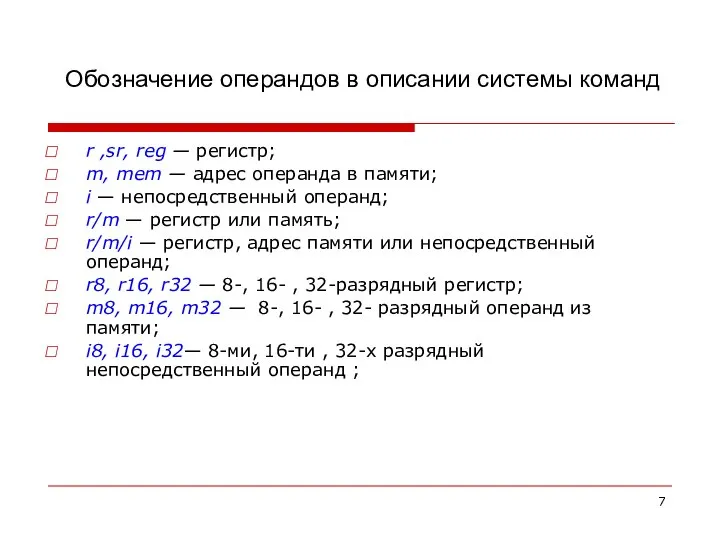

Слайд 7Обозначение операндов в описании системы команд

r ,sr, reg — регистр;

m, mem —

адрес операнда в памяти;

i — непосредственный операнд;

r/m — регистр или память;

r/m/i — регистр, адрес памяти или непосредственный операнд;

r8, r16, r32 — 8-, 16- , 32-разрядный регистр;

m8, m16, m32 — 8-, 16- , 32- разрядный операнд из памяти;

i8, i16, i32— 8-ми, 16-ти , 32-х разрядный непосредственный операнд ;

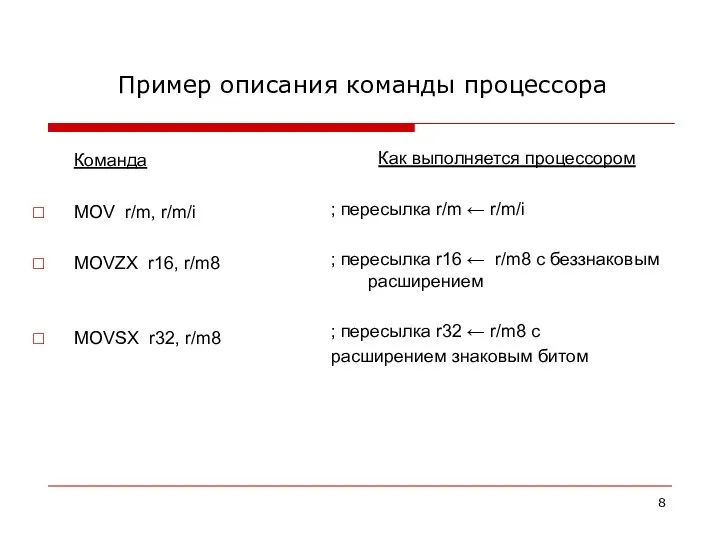

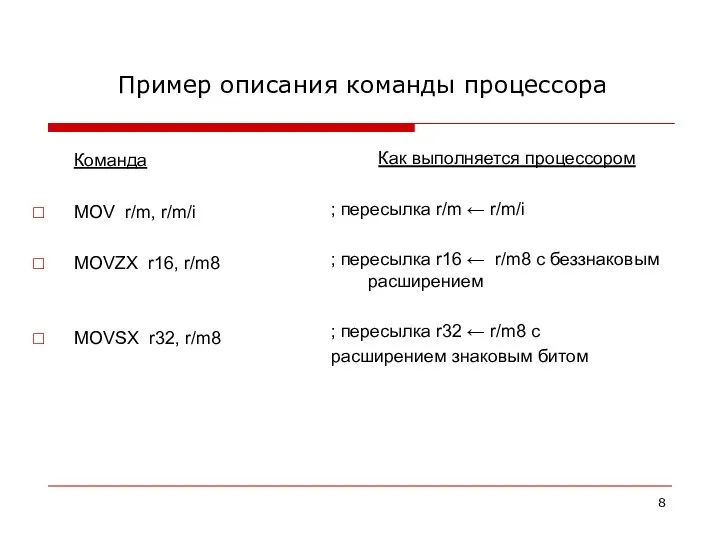

Слайд 8Пример описания команды процессора

Команда

MOV r/m, r/m/i

MOVZX r16, r/m8

MOVSX r32, r/m8

Как выполняется

процессором

; пересылка r/m ← r/m/i

; пересылка r16 ← r/m8 с беззнаковым расширением

; пересылка r32 ← r/m8 с

расширением знаковым битом

Слайд 9Способы задания внутрисегментного адреса операнда

1. Прямая адресация

Внутрисегментный адрес операнда в команде

задаете явно:

mov bx, es:[2]

2. Косвенная адресация

Внутрисегментный адрес (или его часть) записан в регистре. Процессор будет извлекать адрес из регистра и , возможно, вычислять окончательный внутрисегментный адрес

mov bx, es:[si] - внутрисегментный адрес будет взят процессором из регистра SI

mov bx, es:[si+5] - внутрисегментный адрес будет вычислен процессором, как сумма содержимого регистра SI и 5

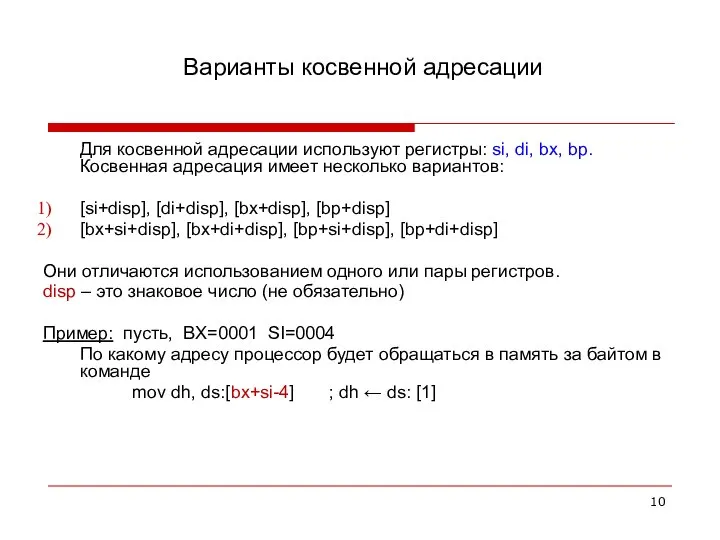

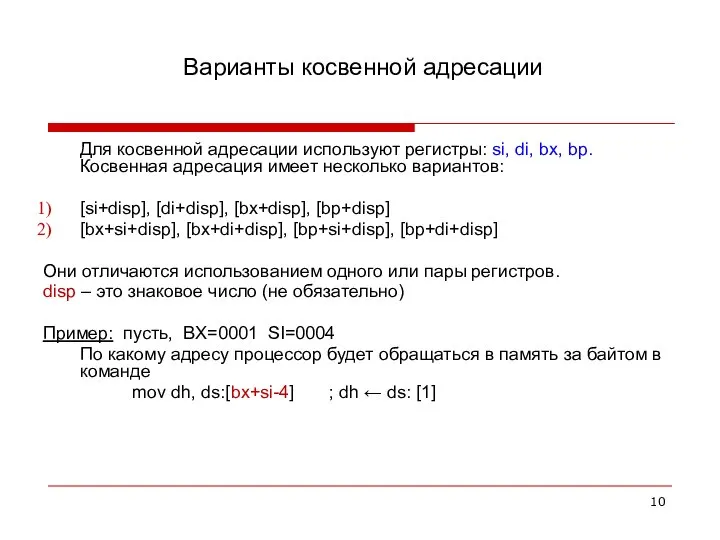

Слайд 10Варианты косвенной адресации

Для косвенной адресации используют регистры: si, di, bx, bp. Косвенная

адресация имеет несколько вариантов:

[si+disp], [di+disp], [bx+disp], [bp+disp]

[bx+si+disp], [bx+di+disp], [bp+si+disp], [bp+di+disp]

Они отличаются использованием одного или пары регистров.

disp – это знаковое число (не обязательно)

Пример: пусть, BХ=0001 SI=0004

По какому адресу процессор будет обращаться в память за байтом в команде

mov dh, ds:[bx+si-4] ; dh ← ds: [1]

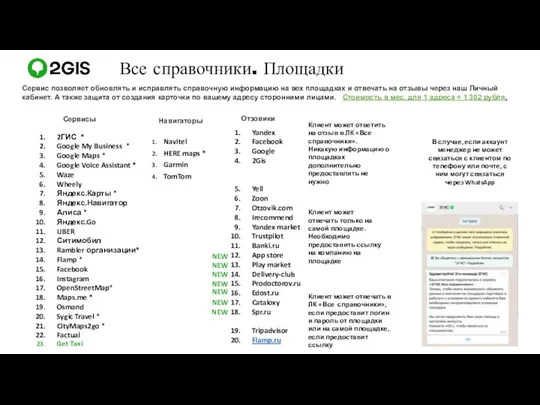

Все справочники. Площадки

Все справочники. Площадки Software. Operating system

Software. Operating system 10 класс 3 тема

10 класс 3 тема Базы данных

Базы данных Размещение графики на Web-страницах

Размещение графики на Web-страницах Знакомство с нейросетями и немного магии на JavaScript

Знакомство с нейросетями и немного магии на JavaScript Оценка количественных параметров текстовых документов

Оценка количественных параметров текстовых документов База данных. Банк данных

База данных. Банк данных Обратная польская запись (ОПЗ). Тема 4

Обратная польская запись (ОПЗ). Тема 4 Подготовка к ЕГЭ по обществознанию, работа с заданиями В-5. Дифференциация в социальной информации фактов и мнений

Подготовка к ЕГЭ по обществознанию, работа с заданиями В-5. Дифференциация в социальной информации фактов и мнений CASE-средства

CASE-средства База данных как модель предметной области

База данных как модель предметной области Переход от реального объекта к 3Д-анимации

Переход от реального объекта к 3Д-анимации 2D-платформер. FairnSquare

2D-платформер. FairnSquare Знатоки информатики. Игра

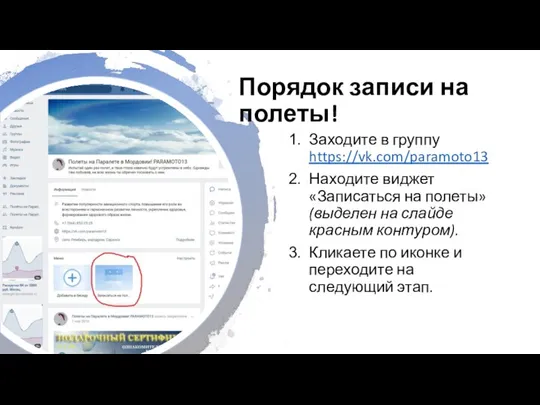

Знатоки информатики. Игра Порядок записи на полеты

Порядок записи на полеты Реализация инновационных проектов в общеобразовательной практике с использованием цифровых решений

Реализация инновационных проектов в общеобразовательной практике с использованием цифровых решений 1_3

1_3 Памятка по информационной безопасности

Памятка по информационной безопасности Установка и настройка серверов DNS, WINS, DHCP

Установка и настройка серверов DNS, WINS, DHCP Osnovnye_ponyatia_i_klassifikatsia_BD

Osnovnye_ponyatia_i_klassifikatsia_BD История развития вычислительной техники

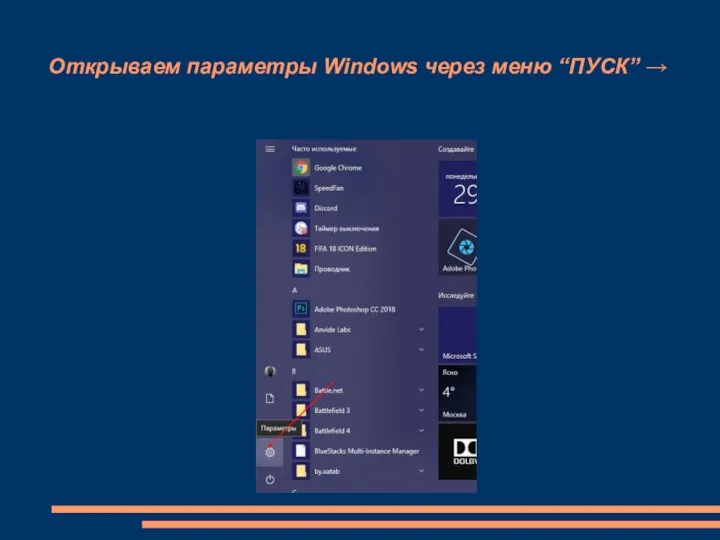

История развития вычислительной техники Настройка интернета

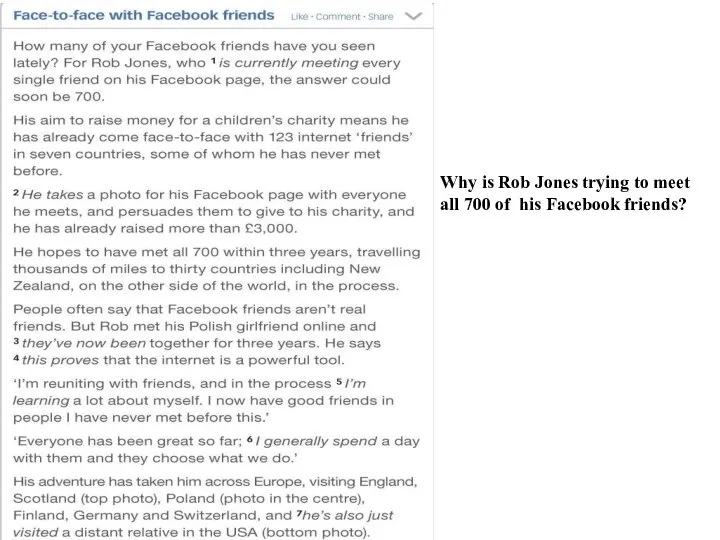

Настройка интернета Trends. Why is Rob Jones trying to meet all 700 of his Facebook friends?

Trends. Why is Rob Jones trying to meet all 700 of his Facebook friends? Персональные ЭВМ

Персональные ЭВМ Библиотека села Ныр

Библиотека села Ныр IDEF0

IDEF0 Linux now and forever

Linux now and forever