- Главная

- Информатика

- Rozproszone systemy komputerowe

Содержание

- 2. Problemy przedstawiane na kolejnych wykładach: Struktura i działanie komputera o wewnętrznym sterowaniu: główne części składowe i

- 3. Współbieżne wykonywanie programów - transakcje współbieżne - zakleszczenia przy synchronizacji. Graf oczekiwania - zagłodzenia - wzajemne

- 4. Zdalne wywoływanie procedur (RPC) - motywacje, problemy, ograniczenia - przykład działania mechanizmu RPC Awarie w systemie

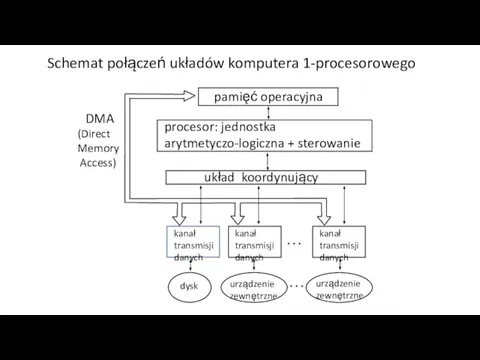

- 5. Literatura G. Coulouris, J. Dollimore, T. Kindberg: Systemy rozproszone, WNT 1999. L. Czaja: Zasady systemów rozproszonych

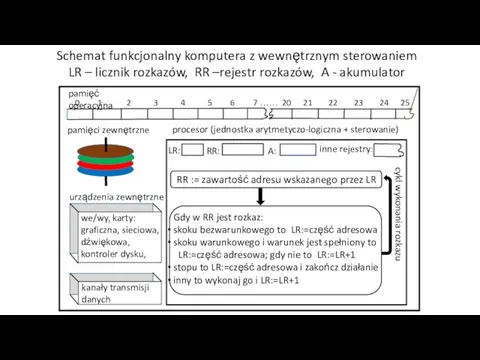

- 6. Wykład 1 Zasada wewnętrznego (von Neumann) vs. zewnętrznego sterowania, uniwersalność – programowalność. Schemat funkcjonalny komputera z

- 7. procesor: jednostka arytmetyczo-logiczna + sterowanie pamięć operacyjna układ koordynujący kanał transmisji danych kanał transmisji danych kanał

- 8. Prześlij do Prześlij do 0 1 2 3 4 5 6 7 …… 20 21 22

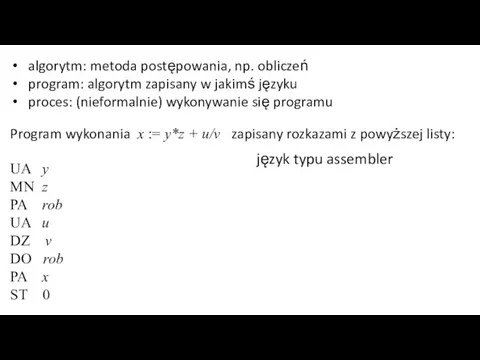

- 10. algorytm: metoda postępowania, np. obliczeń program: algorytm zapisany w jakimś języku proces: (nieformalnie) wykonywanie się programu

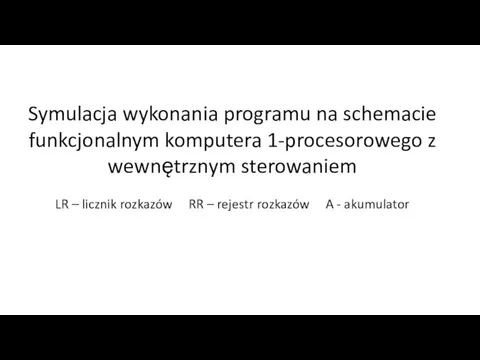

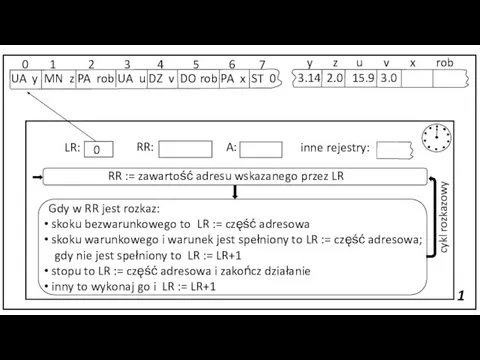

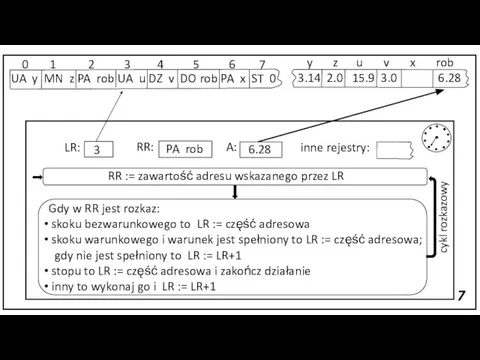

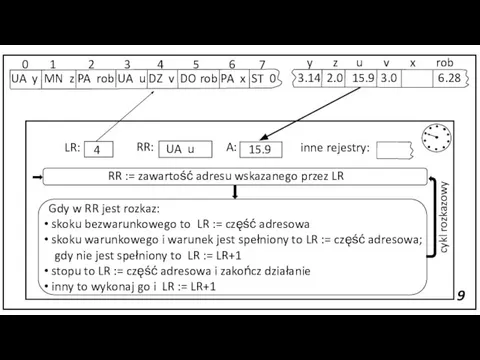

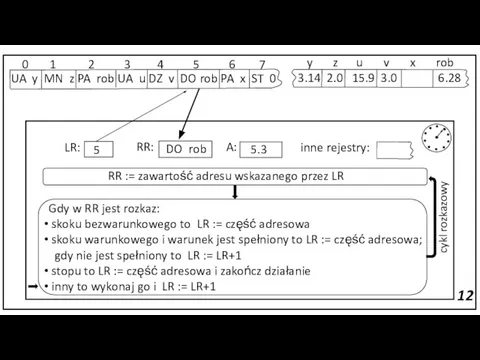

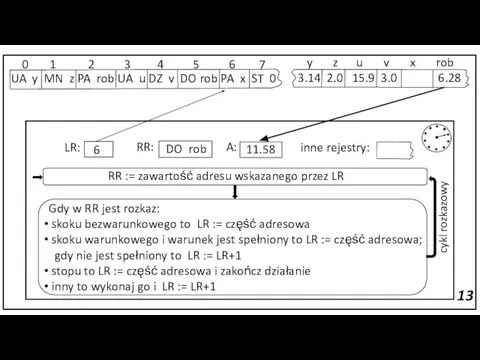

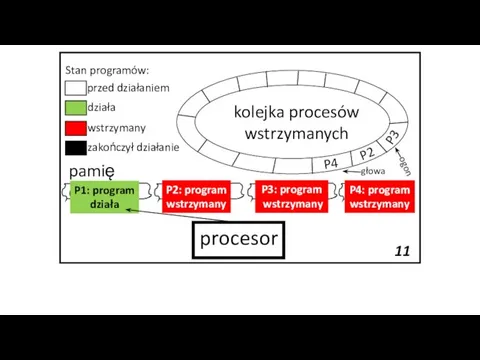

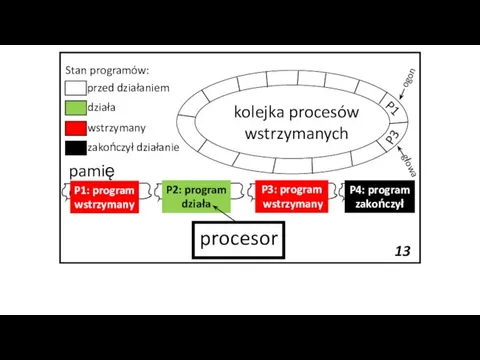

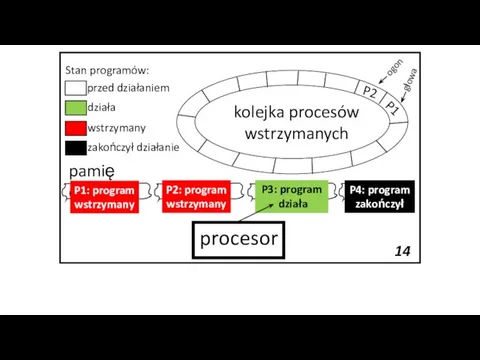

- 11. Symulacja wykonania programu na schemacie funkcjonalnym komputera 1-procesorowego z wewnętrznym sterowaniem LR – licznik rozkazów RR

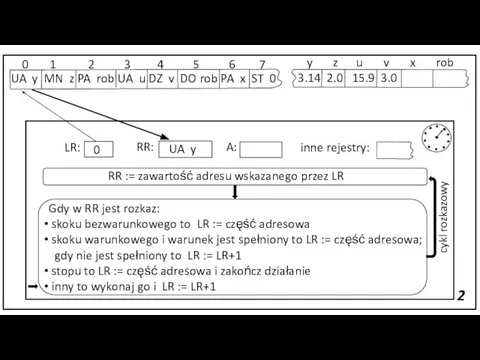

- 12. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

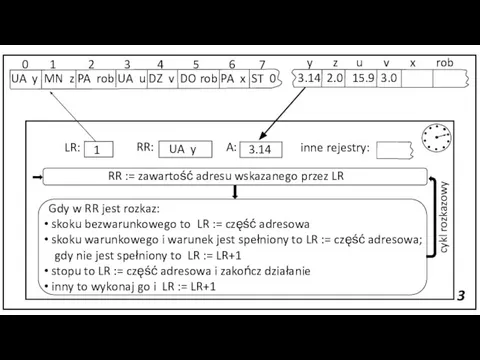

- 13. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

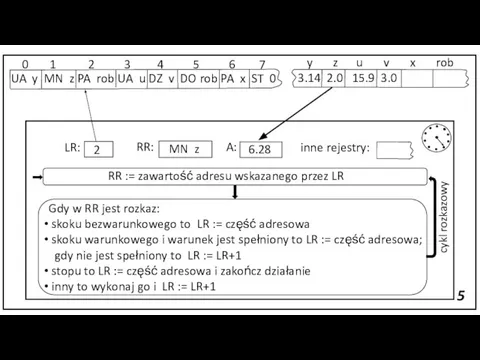

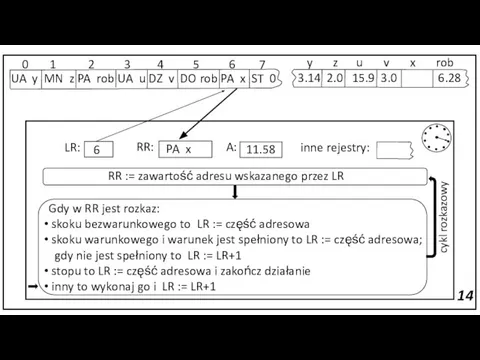

- 14. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 15. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 16. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 17. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 18. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 19. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 20. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 21. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 22. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 23. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 24. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 25. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 26. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 27. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

- 28. Prześlij do 0 1 2 3 4 5 6 7 y z u v x rob

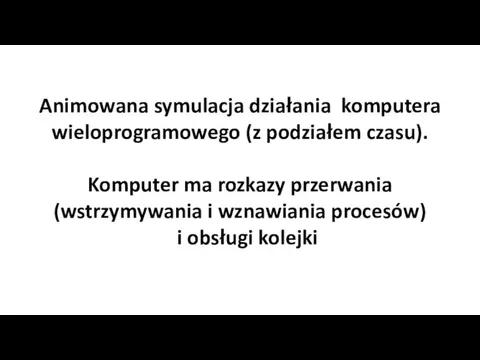

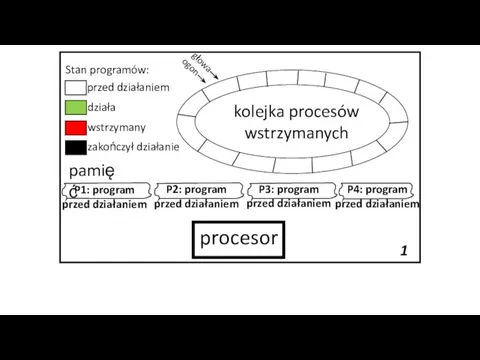

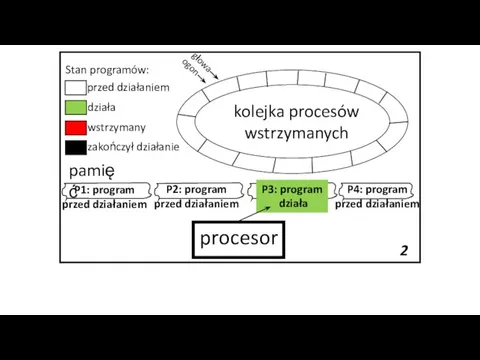

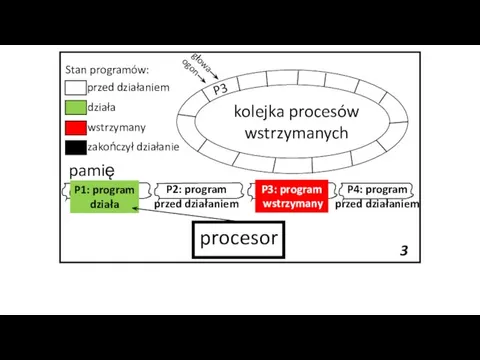

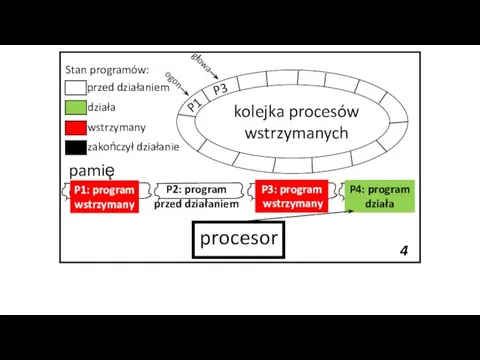

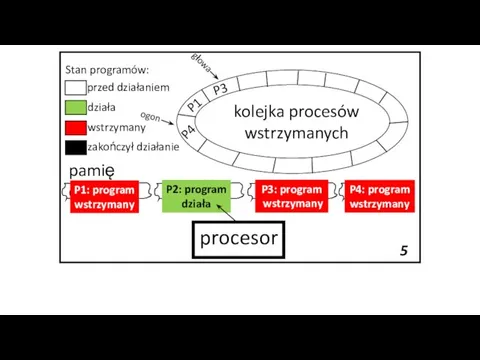

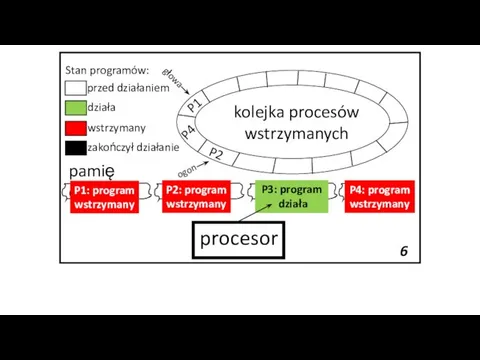

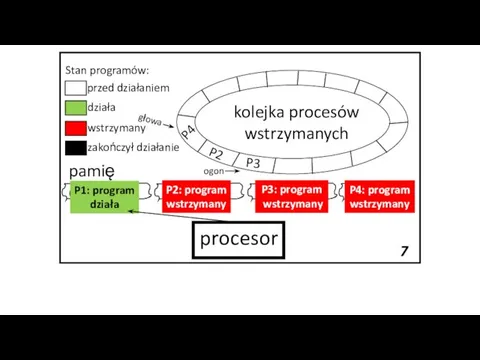

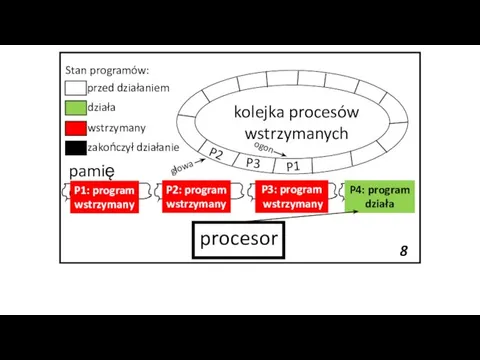

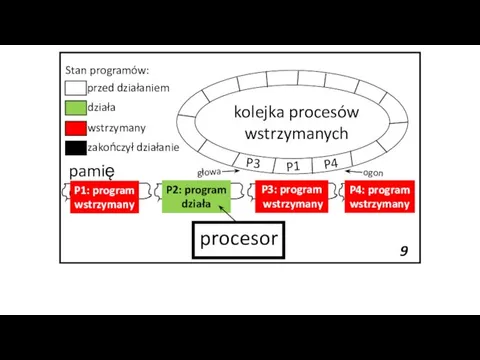

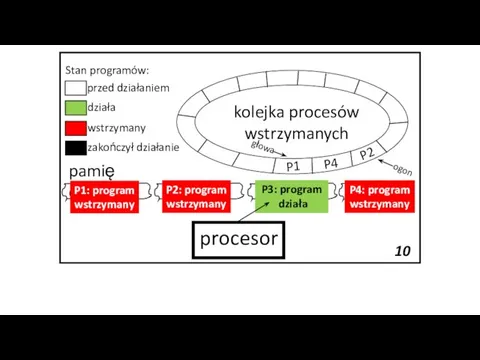

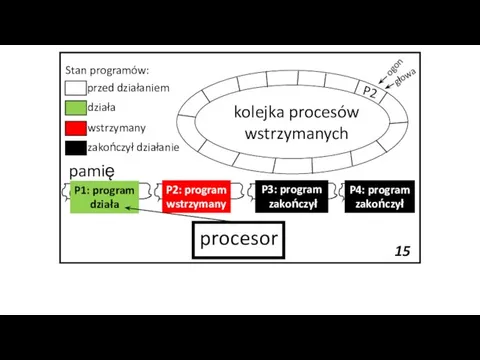

- 29. Animowana symulacja działania komputera wieloprogramowego (z podziałem czasu). Komputer ma rozkazy przerwania (wstrzymywania i wznawiania procesów)

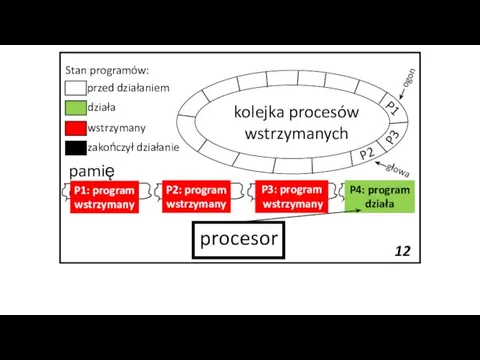

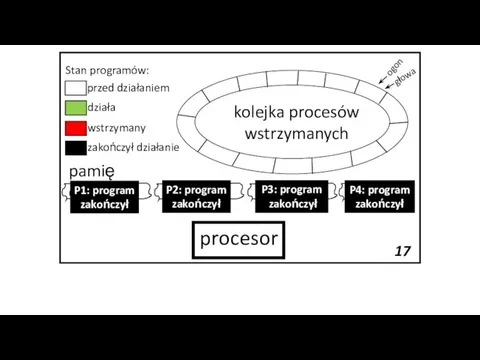

- 41. pamięć P1: program wstrzymany kolejka procesów wstrzymanych wstrzymany działa przed działaniem zakończył działanie ogon Stan programów:

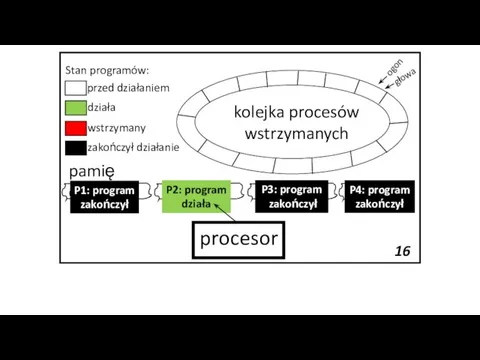

- 45. pamięć P1: program zakończył kolejka procesów wstrzymanych wstrzymany działa przed działaniem zakończył działanie ogon Stan programów:

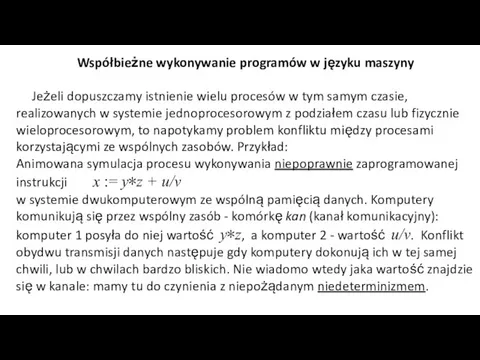

- 47. Współbieżne wykonywanie programów w języku maszyny Jeżeli dopuszczamy istnienie wielu procesów w tym samym czasie, realizowanych

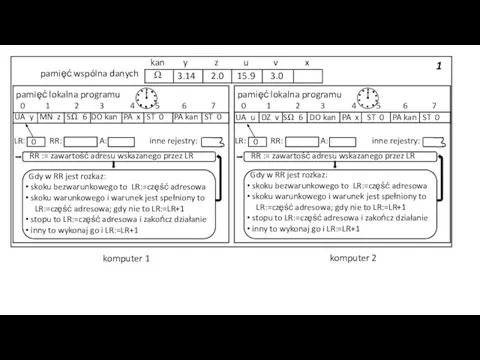

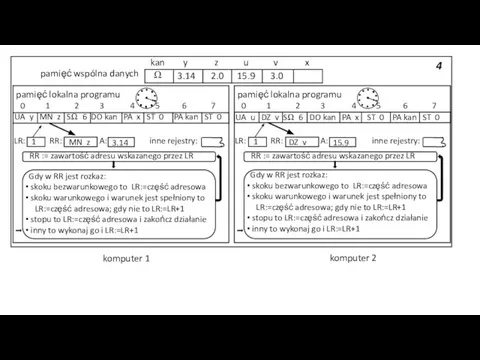

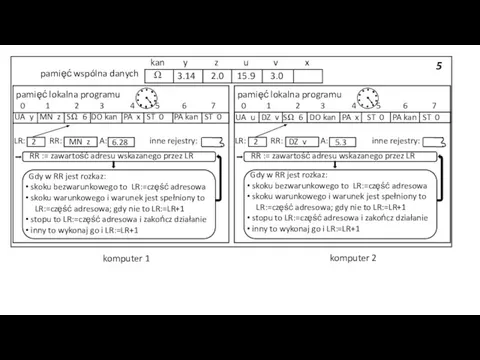

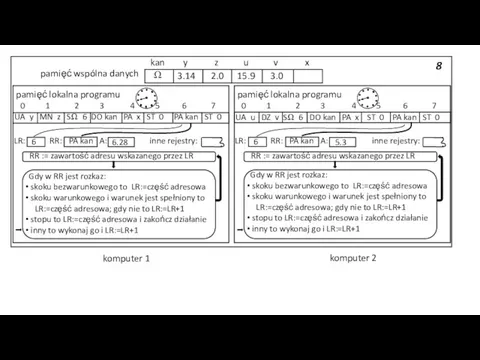

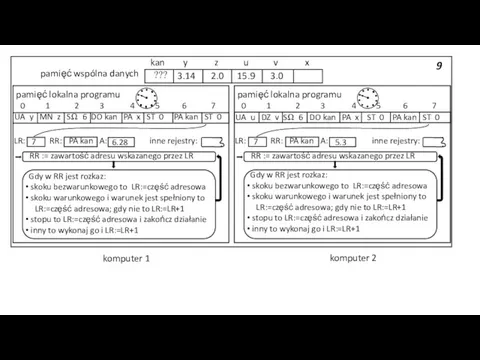

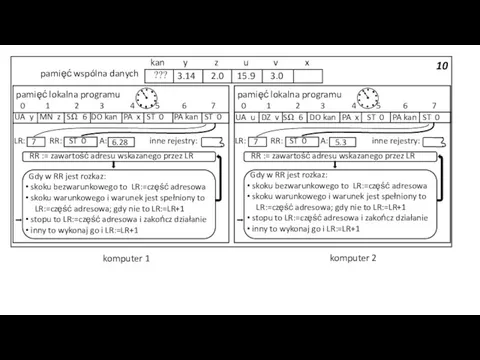

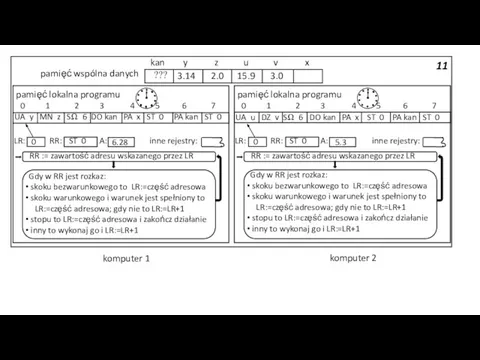

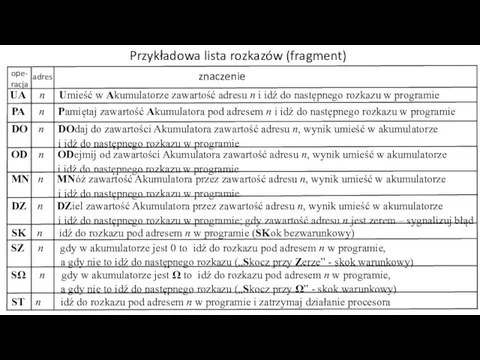

- 48. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 49. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

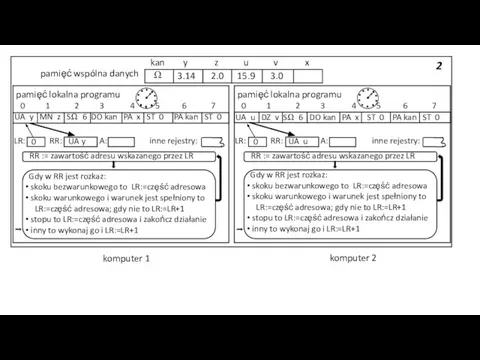

- 50. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 51. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

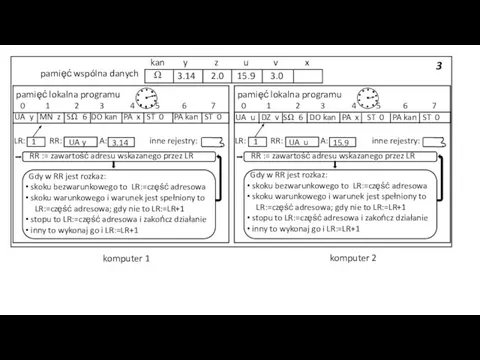

- 52. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

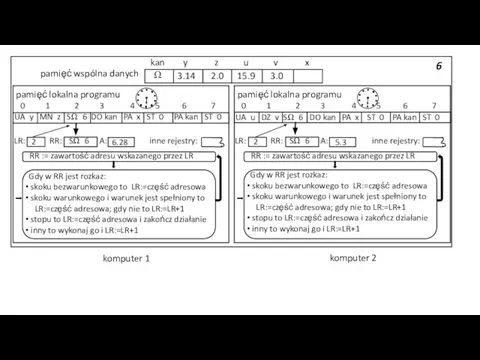

- 53. SΩ 6 6.28 5.3 SΩ 6

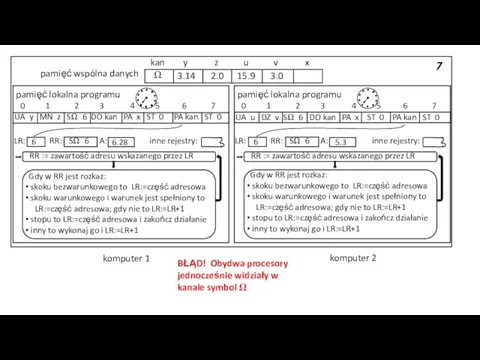

- 54. SΩ 6 6.28 5.3 SΩ 6 BŁĄD! Obydwa procesory jednocześnie widziały w kanale symbol Ω

- 55. PA kan 6.28 5.3 PA kan

- 56. PA kan 6.28 5.3 PA kan

- 57. ST 0 6.28 5.3 ST 0 ???

- 58. ST 0 6.28 5.3 ST 0 ???

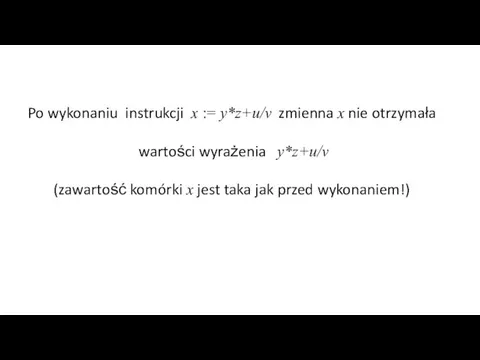

- 59. Po wykonaniu instrukcji x := y*z+u/v zmienna x nie otrzymała wartości wyrażenia y*z+u/v (zawartość komórki x

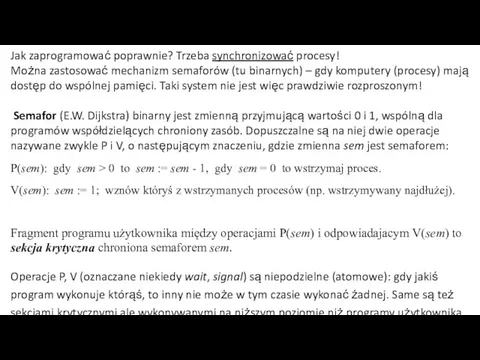

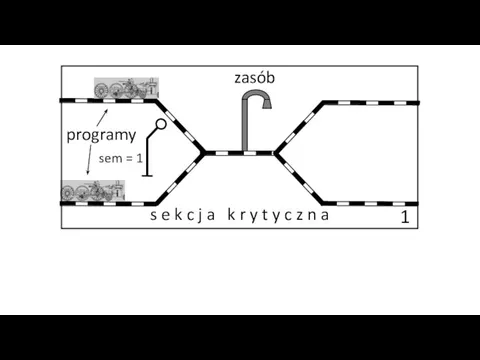

- 60. Jak zaprogramować poprawnie? Trzeba synchronizować procesy! Można zastosować mechanizm semaforów (tu binarnych) – gdy komputery (procesy)

- 61. sem = 1 programy zasób s e k c j a k r y t y

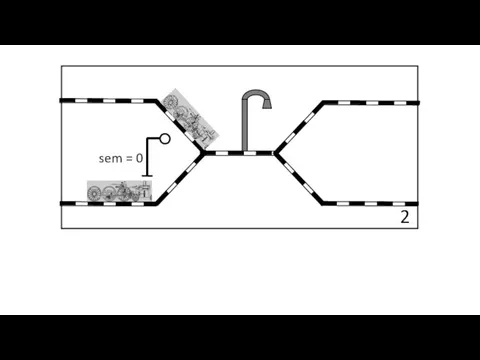

- 62. sem = 0 2

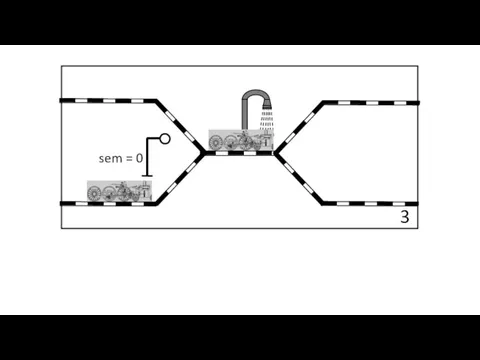

- 63. sem = 0 3

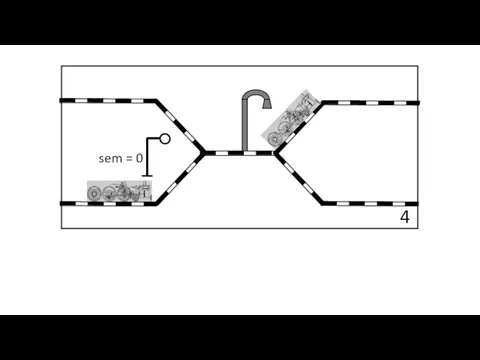

- 64. sem = 0 4

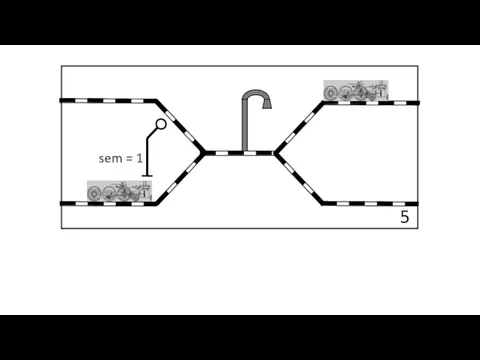

- 65. sem = 1 5

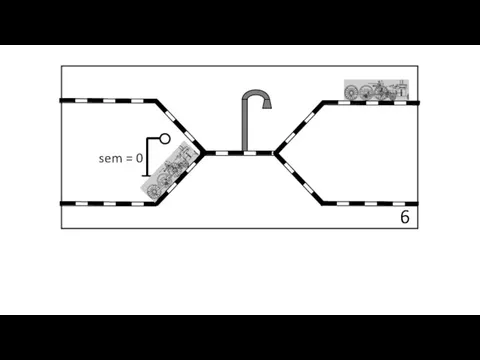

- 66. sem = 0 6

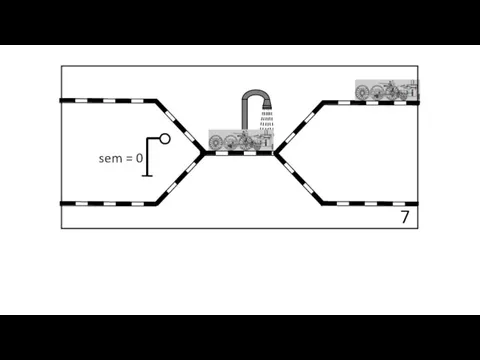

- 67. sem = 0 7

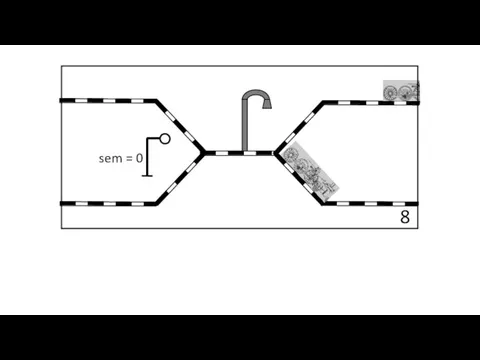

- 68. sem = 0 8

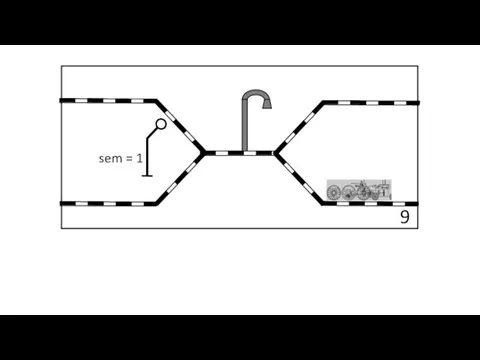

- 69. sem = 1 9

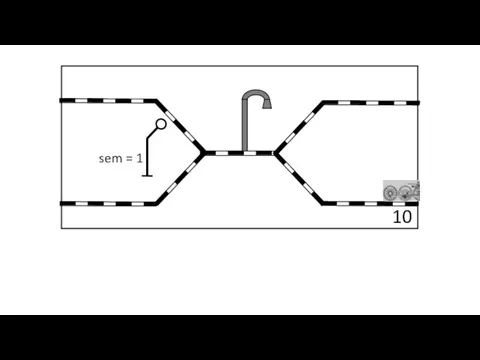

- 70. sem = 1 10

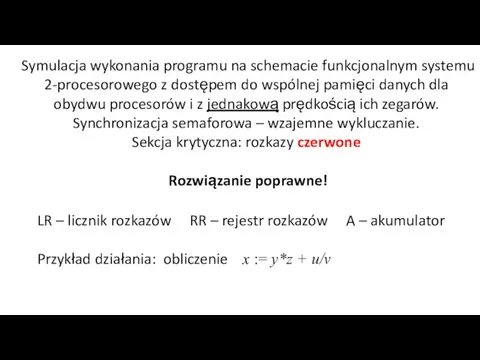

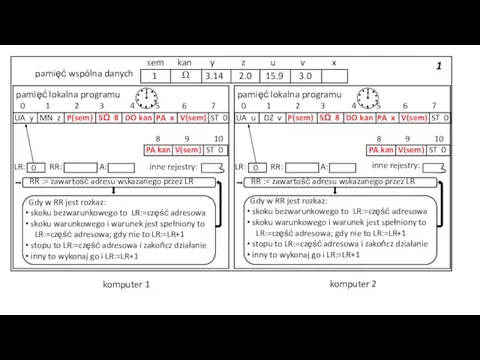

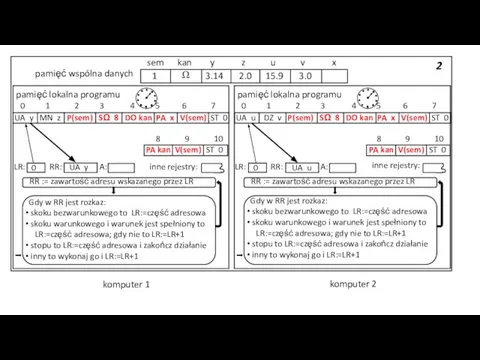

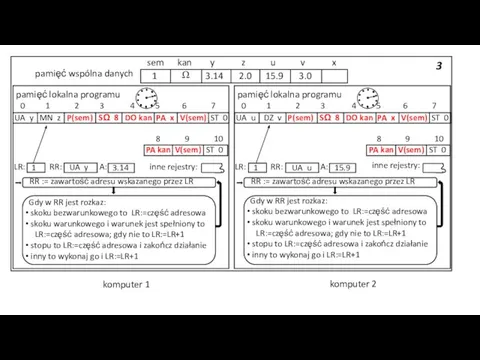

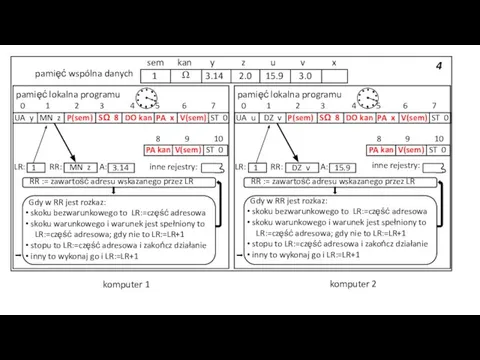

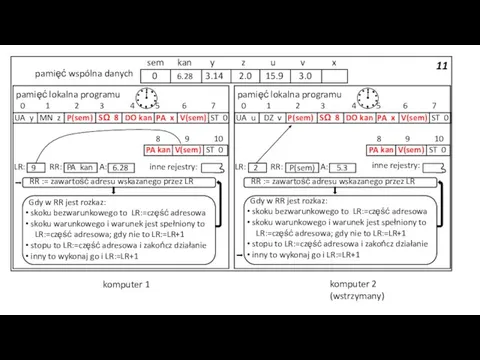

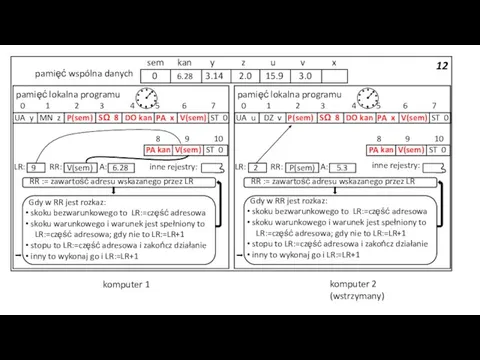

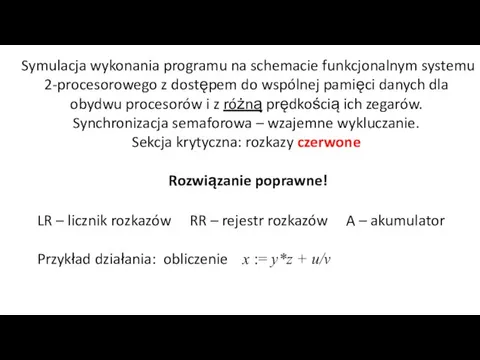

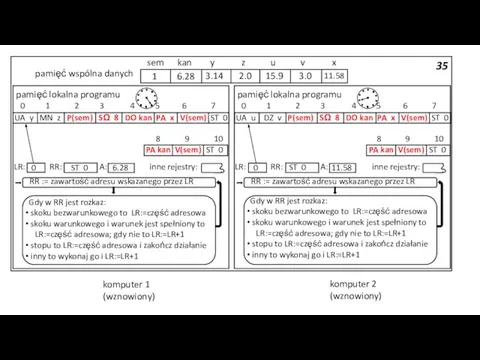

- 71. Symulacja wykonania programu na schemacie funkcjonalnym systemu 2-procesorowego z dostępem do wspólnej pamięci danych dla obydwu

- 72. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 73. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 74. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 75. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 76. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 77. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 78. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 79. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 80. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 81. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 82. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 83. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 84. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 85. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 86. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 87. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 88. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 89. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 90. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 91. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 92. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 93. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 94. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 95. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 96. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

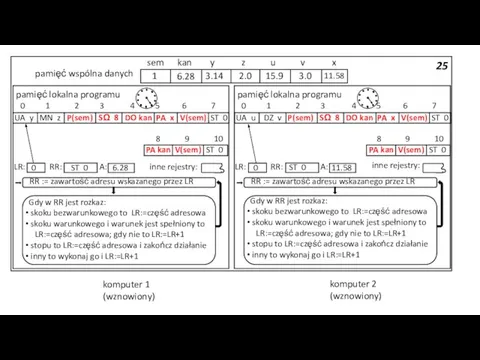

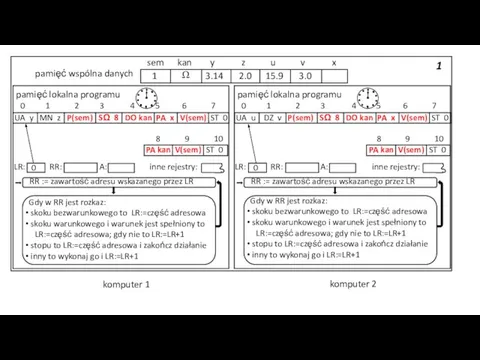

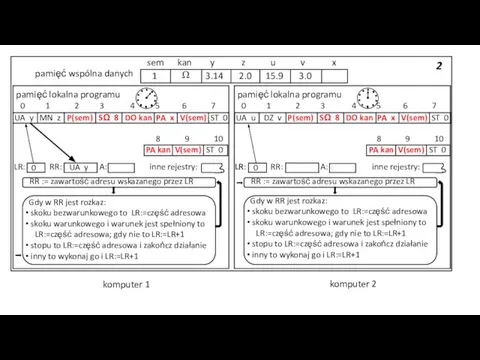

- 97. Symulacja wykonania programu na schemacie funkcjonalnym systemu 2-procesorowego z dostępem do wspólnej pamięci danych dla obydwu

- 98. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

- 99. Gdy w RR jest rozkaz: skoku bezwarunkowego to LR:=część adresowa skoku warunkowego i warunek jest spełniony

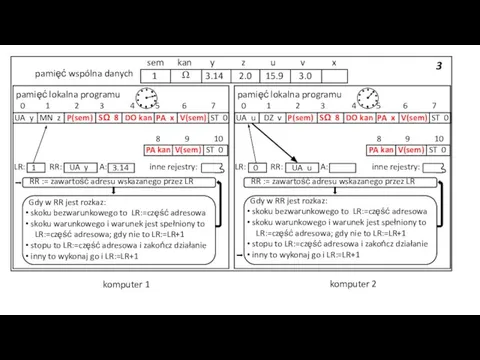

- 100. 3 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

- 101. 4 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

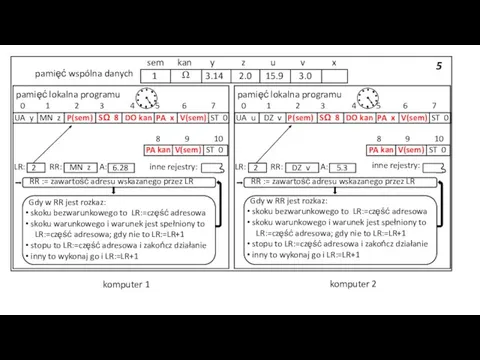

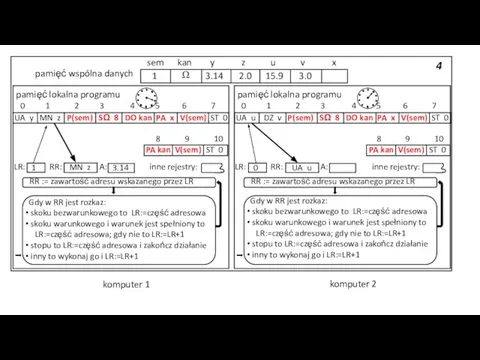

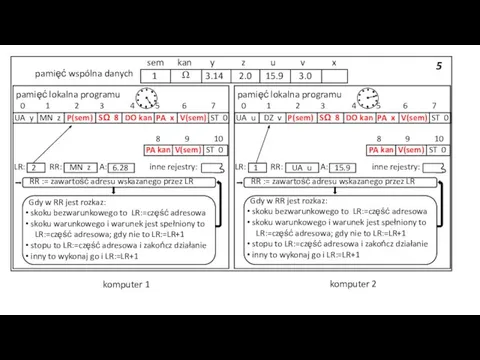

- 102. 5 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

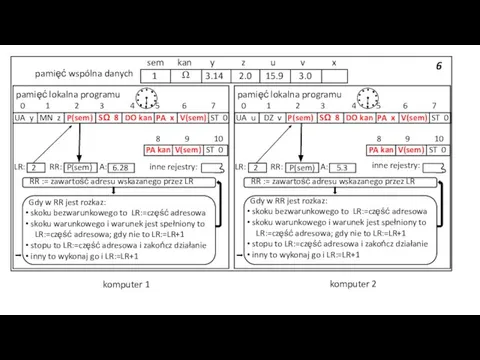

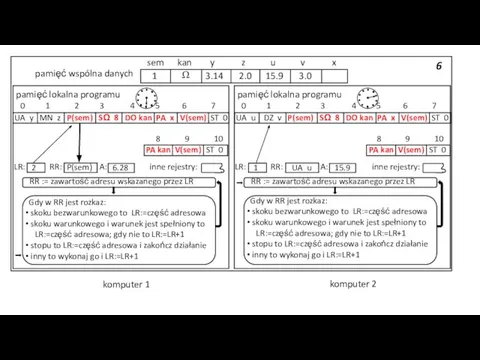

- 103. 6 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

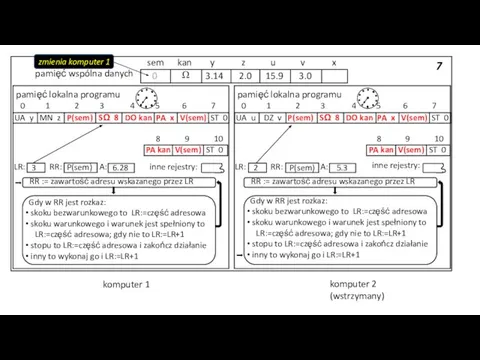

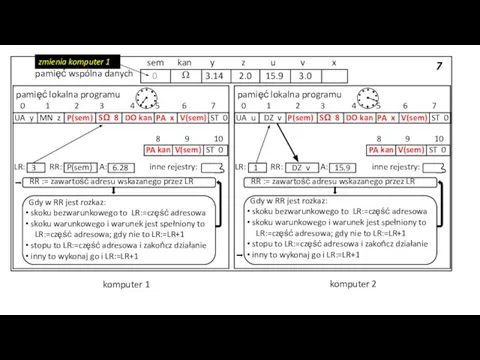

- 104. 7 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

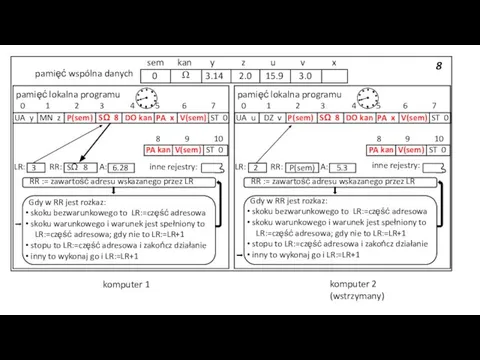

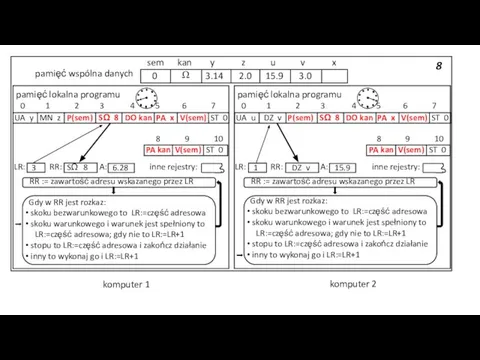

- 105. 8 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

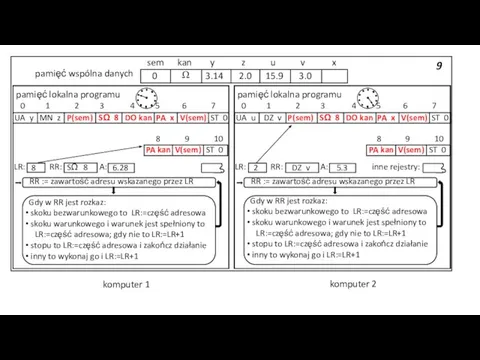

- 106. 9 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

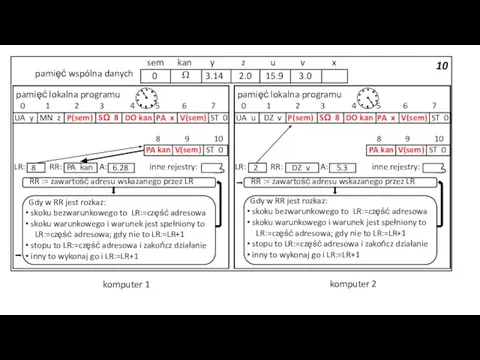

- 107. 10 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Ω

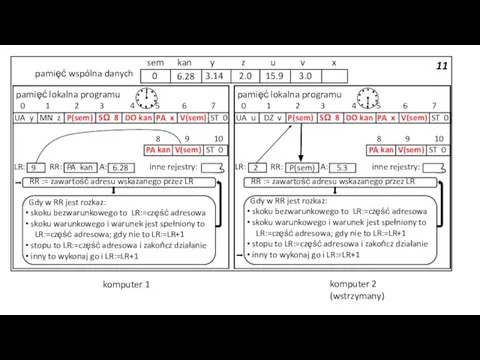

- 108. 11 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x 0

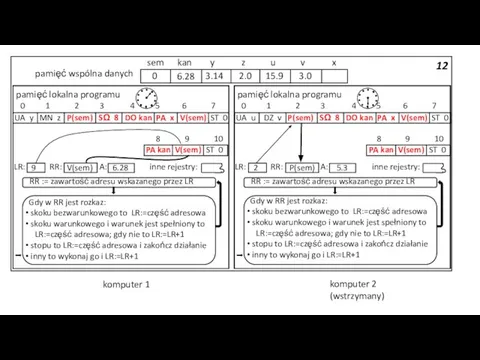

- 109. 12 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x 0

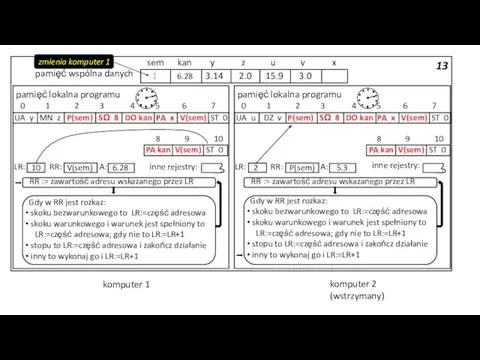

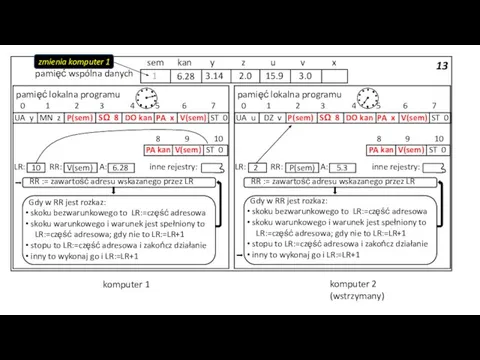

- 110. 13 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x 1

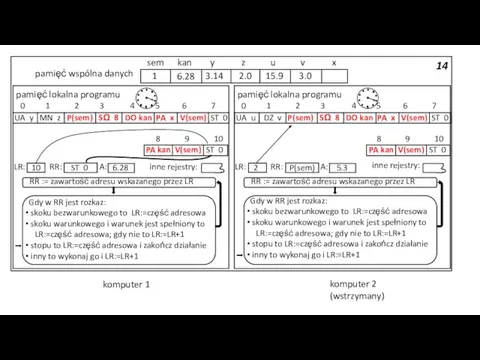

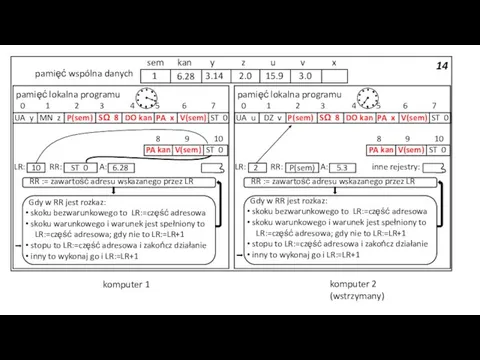

- 111. 14 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x 1

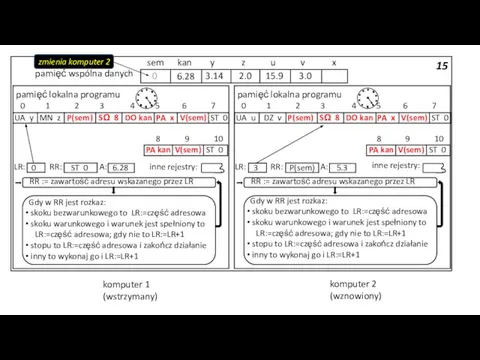

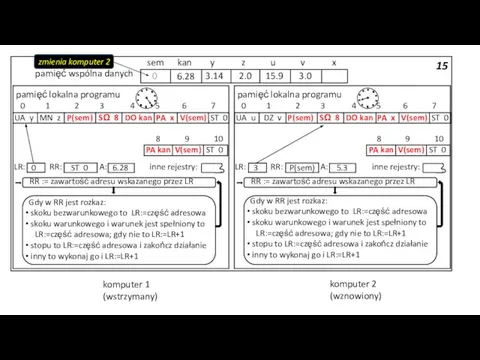

- 112. 15 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

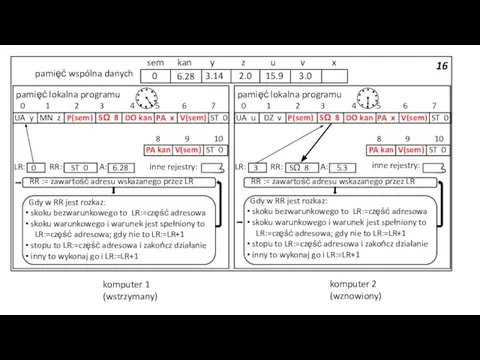

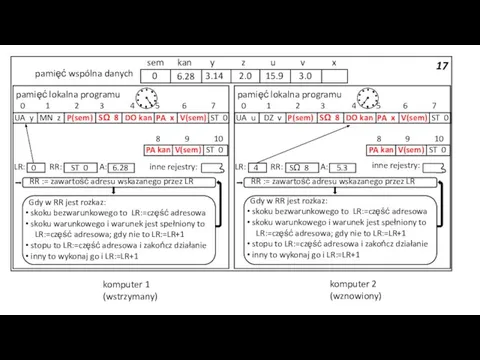

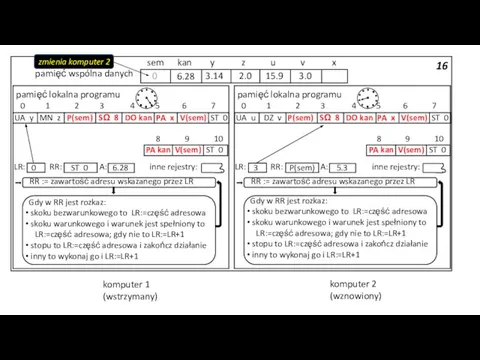

- 113. 16 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

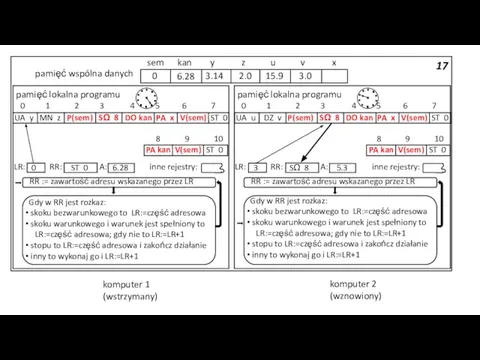

- 114. 17 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

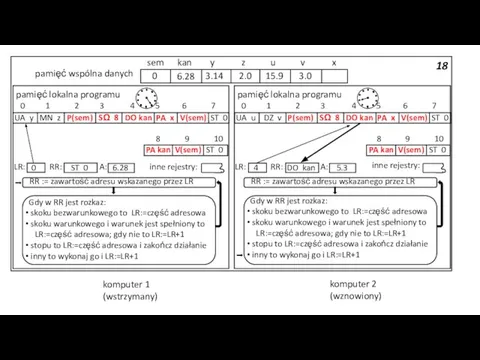

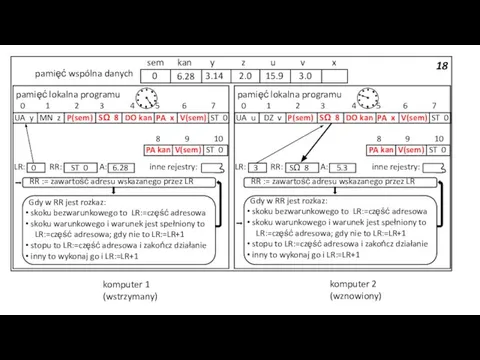

- 115. 18 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

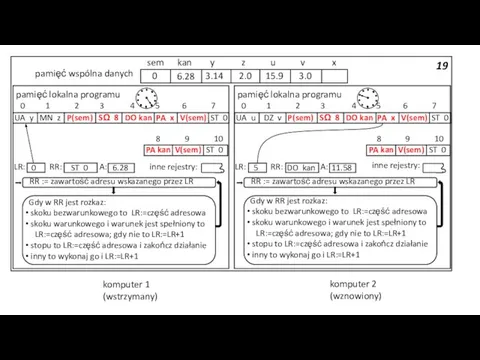

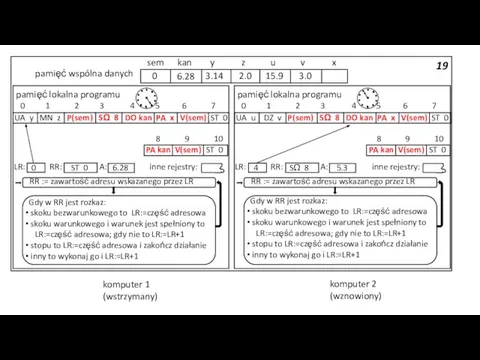

- 116. 19 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

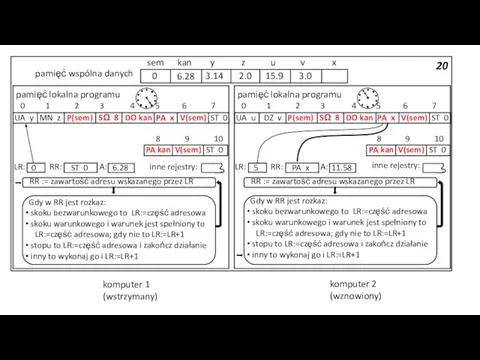

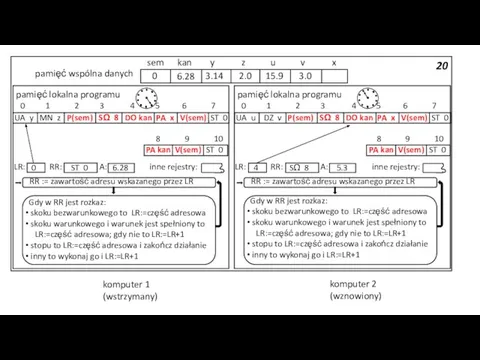

- 117. 20 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

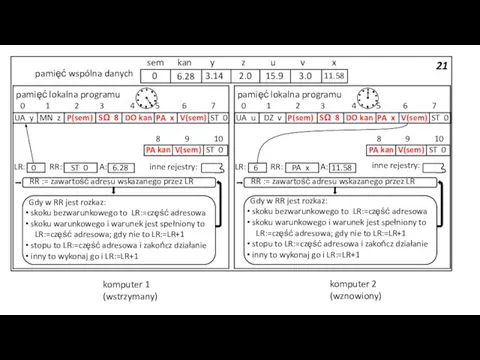

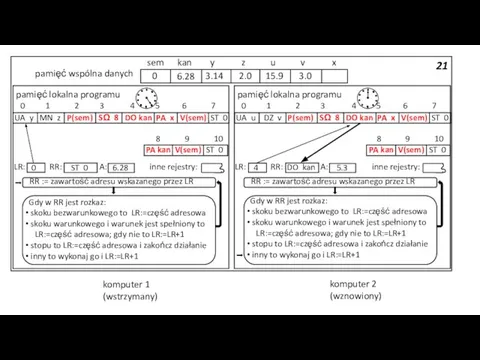

- 118. 21 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

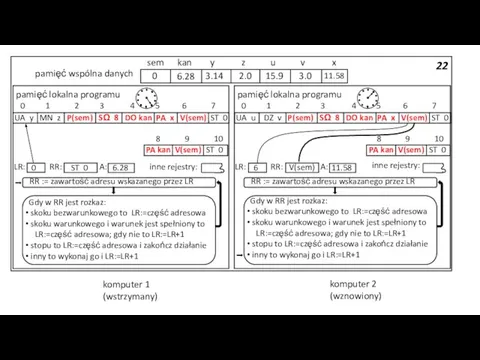

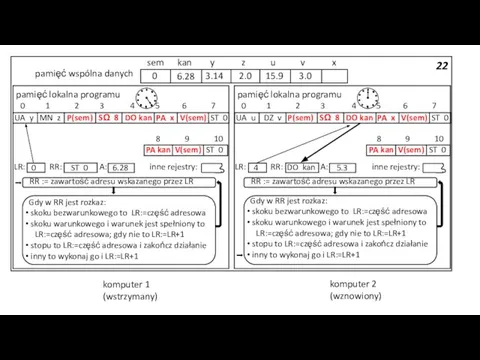

- 119. 22 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

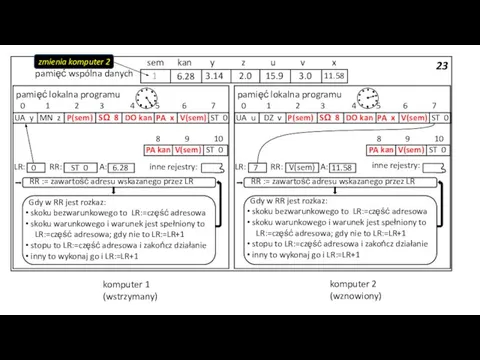

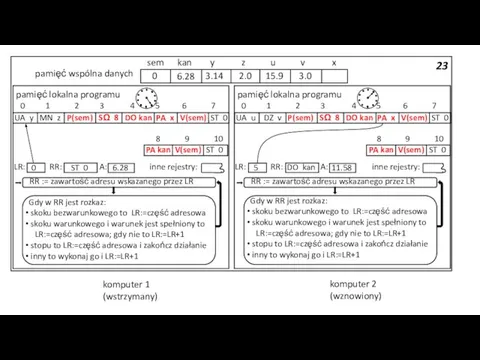

- 120. 23 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

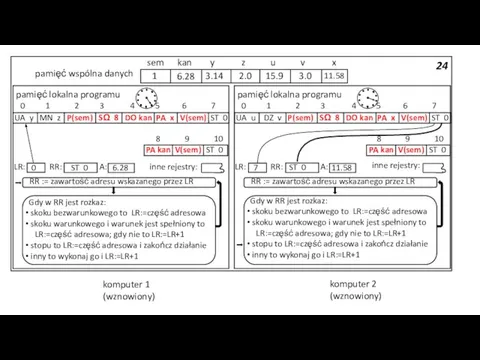

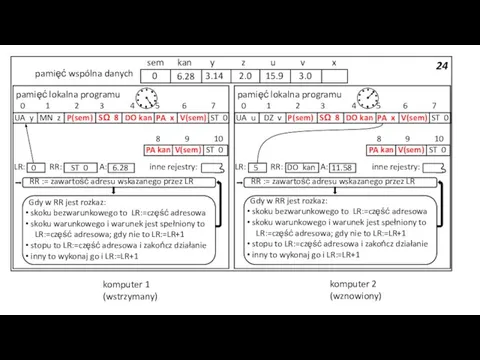

- 121. 24 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

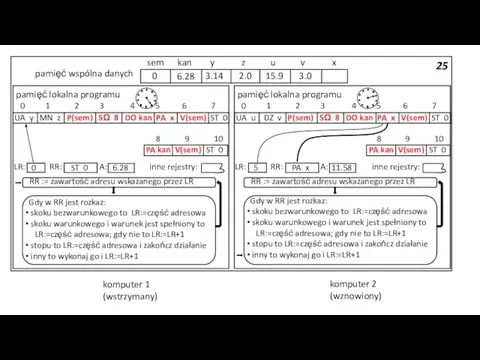

- 122. 25 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

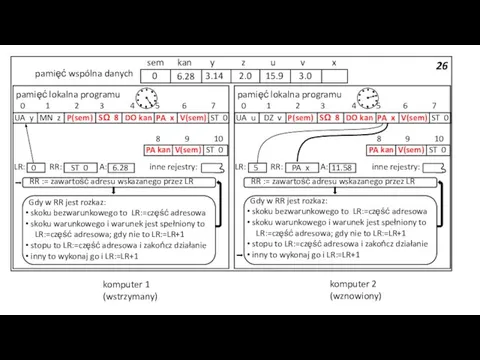

- 123. 26 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

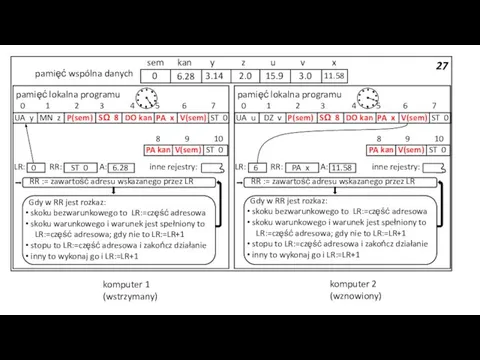

- 124. 27 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

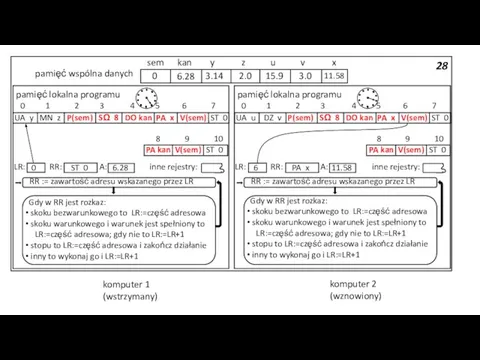

- 125. 28 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

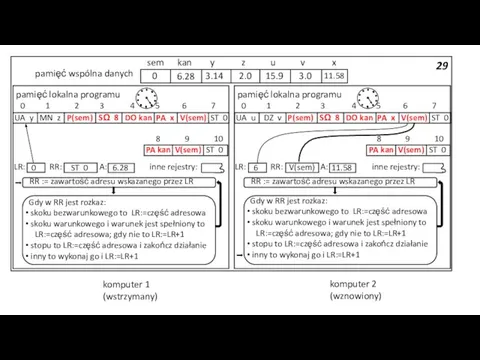

- 126. 29 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

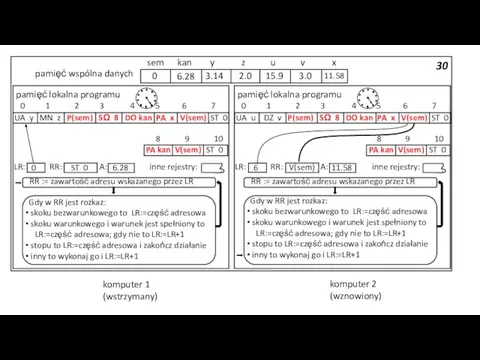

- 127. 30 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

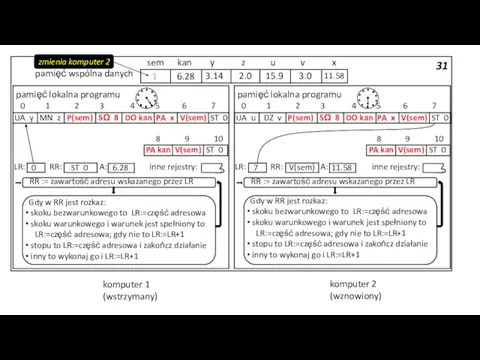

- 128. 31 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

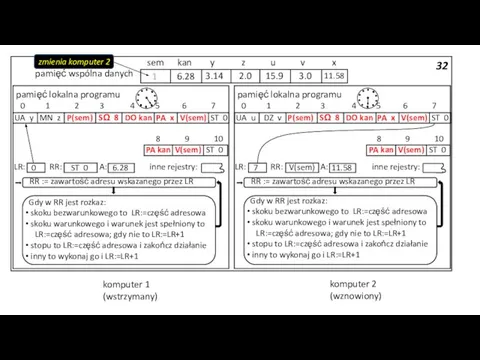

- 129. 32 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

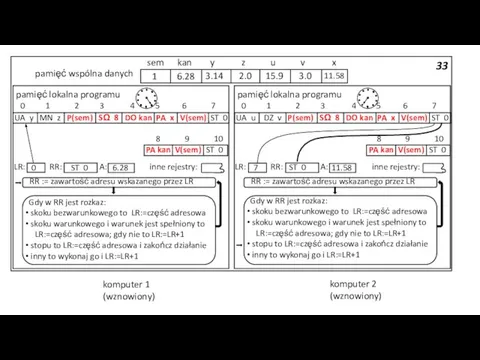

- 130. 33 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

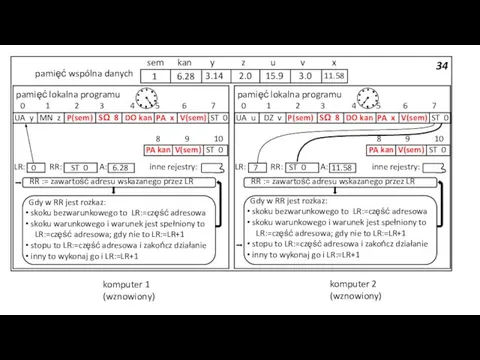

- 131. 34 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

- 132. 35 pamięć wspólna danych 3.14 2.0 15.9 3.0 sem kan y z u v x Gdy

- 134. Скачать презентацию

Слайд 2Problemy przedstawiane na kolejnych wykładach:

Struktura i działanie komputera o wewnętrznym sterowaniu:

Problemy przedstawiane na kolejnych wykładach:

Struktura i działanie komputera o wewnętrznym sterowaniu:

wykonania rozkazu, przykładowa lista rozkazów, przykłady wykonania prostych programów

w przykładowych rozkazach – symulacja animowana

Pojęcie procesu. Mechanizmy synchronizacji i komunikacji międzyprocesowej.

Scentralizowane systemy wieloprocesowe symulowane (wieloprogramowe, podział

czasu, przerwania) i rzeczywiste (z wieloma fizycznymi procesorami). Przykłady działania

takich systemów (m.in. synchronicznych: wektorowych, macierzowych) – symulacja

animowana. Zjawiska patologiczne w systemach wieloprocesowych: zakleszczenie,

zagłodzenie, niesprawiedliwy przydział zasobów

Od systemów scentralizowanych symulujących pewne funkcje systemów

rozproszonych do systemów fizycznie rozproszonych. Przegląd różnych rodzajów

systemów relacji między nimi. Pewna klasyfikacja – tzw. taksonomia Flynn’a

Systemy rozproszone: definicje (nieformalne), cele, cechy

Слайд 3 Współbieżne wykonywanie programów

- transakcje współbieżne

- zakleszczenia przy synchronizacji. Graf

Współbieżne wykonywanie programów

- transakcje współbieżne

- zakleszczenia przy synchronizacji. Graf

- zagłodzenia

- wzajemne wykluczanie w systemach rozproszonych: z serwerem nadzorczym oraz

algorytm pierścienia z żetonem

Czas, koordynacja, wykluczanie bez nadzorcy, zagadnienia:

- czas fizyczny i synchronizacja zegarów: metoda Cristiana, metoda

Berkeley – „demon czasu”, metoda NTP (Network Time Protocol)

- czas logiczny

- wzajemne wykluczanie bez zewnętrznych usług dla procesów

Komunikacja międzyprocesowa

- podstawowe zagadnienia komunikacji

- zadania protokołów komunikacyjnych – przykłady

- wysyłanie i odbiór, rodzaje transmitowania komunikatów

- warstwowe struktury protokołów

Слайд 4Zdalne wywoływanie procedur (RPC)

- motywacje, problemy, ograniczenia

- przykład działania mechanizmu

Zdalne wywoływanie procedur (RPC)

- motywacje, problemy, ograniczenia

- przykład działania mechanizmu

Awarie w systemie rozproszonym

- twierdzenia o szeregach liczbowych

- reakcja na sytuacje awaryjne i ich szanse

- problemy uzgodnień (problem „dwóch armii”, problem „bizantyjskich generałów”)

- wybór nowego koordynatora po awarii: algorytm tyrana, pierścieniowy algorytm elekcji

Rozproszona pamięć dzielona

- motywacje, problemy, cechy korzystne i niekorzystne

- przeplotowy model działania systemu

- współbieżność operacji dostępu do pamięci DSM

- zdarzenia inicjacji i zakończeń czytania i pisania

- formalne definicje spójności ścisłej i sekwencyjnej, inne rodzaje spójności pamięci

Слайд 5Literatura

G. Coulouris, J. Dollimore, T. Kindberg: Systemy rozproszone, WNT 1999.

L. Czaja:

Literatura

G. Coulouris, J. Dollimore, T. Kindberg: Systemy rozproszone, WNT 1999.

L. Czaja:

L. Czaja: Introduction to Distributed Systems. Principles and Features, Springer-Verlag, 2018

L. Czaja: Cause-Effect Structures, An Algebra of Nets with Examples of Applications, Springer-Verlag 2019

5. A.S. Tanenbaum: Rozproszone systemy operacyjne, WNT 1997

M. Ben-Ari: Podstawy programowania współbieżnego i rozproszonego,

WNT 1996

Слайд 6Wykład 1

Zasada wewnętrznego (von Neumann) vs. zewnętrznego sterowania,

uniwersalność – programowalność.

Schemat

Wykład 1

Zasada wewnętrznego (von Neumann) vs. zewnętrznego sterowania,

uniwersalność – programowalność.

Schemat

z przykładową listą rozkazów, przykład działania - symulacja

(program w języku maszyny).

3. Wieloprogramowość z jednym procesorem.

Systemy wieloprocesorowe ze wspólną pamięcią.

Przykład działania systemu 2-procesorowego (symulacja), zyski i zagrożenia.

Слайд 7procesor: jednostka

arytmetyczo-logiczna + sterowanie

pamięć operacyjna

układ koordynujący

kanał

transmisji

danych

kanał

transmisji

danych

kanał

procesor: jednostka

arytmetyczo-logiczna + sterowanie

pamięć operacyjna

układ koordynujący

kanał

transmisji

danych

kanał

transmisji

danych

kanał

transmisji

danych

…

dysk

urządzenie

zewnętrzne

…

urządzenie

zewnętrzne

DMA

(Direct

Memory

Access)

Schemat połączeń układów komputera 1-procesorowego

Слайд 8Prześlij do

Prześlij do

0 1 2 3 4 5 6 7 ……

Prześlij do

Prześlij do

0 1 2 3 4 5 6 7 ……

20

LR:

RR:

A:

inne rejestry:

pamięć operacyjna

procesor (jednostka arytmetyczo-logiczna + sterowanie)

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

cykl wykonania rozkazu

pamięci zewnętrzne

we/wy, karty:

graficzna, sieciowa,

dźwiękowa, kontroler dysku,

urządzenia zewnętrzne

kanały transmisji

danych

Schemat funkcjonalny komputera z wewnętrznym sterowaniem

LR – licznik rozkazów, RR –rejestr rozkazów, A - akumulator

Слайд 10algorytm: metoda postępowania, np. obliczeń

program: algorytm zapisany w jakimś języku

proces: (nieformalnie) wykonywanie

algorytm: metoda postępowania, np. obliczeń

program: algorytm zapisany w jakimś języku

proces: (nieformalnie) wykonywanie

Program wykonania x := y*z + u/v zapisany rozkazami z powyższej listy:

UA y

MN z

PA rob

UA u

DZ v

DO rob

PA x

ST 0

język typu assembler

Слайд 11Symulacja wykonania programu na schemacie funkcjonalnym komputera 1-procesorowego z wewnętrznym sterowaniem

LR –

Symulacja wykonania programu na schemacie funkcjonalnym komputera 1-procesorowego z wewnętrznym sterowaniem LR –

Слайд 12Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0

1

0

cykl rozkazowy

Слайд 13Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

0

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0

UA y

2

cykl rozkazowy

Слайд 14Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

1

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0

UA y

3

3.14

cykl rozkazowy

Слайд 15Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

1

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0

MN z

4

3.14

cykl rozkazowy

Слайд 16Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

2

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0

MN z

5

6.28

cykl rozkazowy

Слайд 17Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

2

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0

PA rob

6

6.28

cykl rozkazowy

Слайд 18Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

3

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

PA rob

7

6.28

cykl rozkazowy

Слайд 19Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

3

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

UA u

8

6.28

cykl rozkazowy

Слайд 20Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

4

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

UA u

9

15.9

cykl rozkazowy

Слайд 21Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

4

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

DZ v

10

15.9

cykl rozkazowy

Слайд 22Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

5

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

DZ v

11

5.3

cykl rozkazowy

Слайд 23Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

5

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

DO rob

12

5.3

cykl rozkazowy

Слайд 24Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

6

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

DO rob

13

11.58

cykl rozkazowy

Слайд 25Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

6

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 6.28

PA x

14

11.58

cykl rozkazowy

Слайд 26Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

7

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 11.58 6.28

PA x

15

11.58

cykl rozkazowy

Слайд 27Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

7

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 11.58 6.28

ST 0

16

11.58

cykl rozkazowy

Слайд 28Prześlij do

0 1 2 3 4 5 6 7

y z

Prześlij do

0 1 2 3 4 5 6 7

y z

20

LR:

RR:

A:

inne rejestry:

UA y MN z PA rob UA u DZ v DO rob PA x ST 0

0

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR := część adresowa

skoku warunkowego i warunek jest spełniony to LR := część adresowa;

gdy nie jest spełniony to LR := LR+1

stopu to LR := część adresowa i zakończ działanie

inny to wykonaj go i LR := LR+1

3.14 2.0 15.9 3.0 11.58 6.28

ST 0

17

11.58

cykl rozkazowy

Слайд 29Animowana symulacja działania komputera wieloprogramowego (z podziałem czasu).

Komputer ma rozkazy przerwania

(wstrzymywania

Animowana symulacja działania komputera wieloprogramowego (z podziałem czasu).

Komputer ma rozkazy przerwania

(wstrzymywania

i obsługi kolejki

Слайд 41pamięć

P1: program

wstrzymany

kolejka procesów wstrzymanych

wstrzymany

działa

przed działaniem

zakończył działanie

ogon

Stan programów:

P4: program

działa

P3:

pamięć

P1: program

wstrzymany

kolejka procesów wstrzymanych

wstrzymany

działa

przed działaniem

zakończył działanie

ogon

Stan programów:

P4: program

działa

P3:

wstrzymany

P2: program

wstrzymany

P2

P3

głowa

P1

Prześlij do

procesor

12

Слайд 45pamięć

P1: program

zakończył

kolejka procesów wstrzymanych

wstrzymany

działa

przed działaniem

zakończył działanie

ogon

Stan programów:

P4: program

zakończył

P3:

pamięć

P1: program

zakończył

kolejka procesów wstrzymanych

wstrzymany

działa

przed działaniem

zakończył działanie

ogon

Stan programów:

P4: program

zakończył

P3:

zakończył

P2: program

działa

głowa

Prześlij do

procesor

16

Слайд 47Współbieżne wykonywanie programów w języku maszyny

Jeżeli dopuszczamy istnienie wielu procesów w

Współbieżne wykonywanie programów w języku maszyny

Jeżeli dopuszczamy istnienie wielu procesów w

Animowana symulacja procesu wykonywania niepoprawnie zaprogramowanej instrukcji x := y∗z + u/v

w systemie dwukomputerowym ze wspólną pamięcią danych. Komputery komunikują się przez wspólny zasób - komórkę kan (kanał komunikacyjny): komputer 1 posyła do niej wartość y∗z, a komputer 2 - wartość u/v. Konflikt obydwu transmisji danych następuje gdy komputery dokonują ich w tej samej chwili, lub w chwilach bardzo bliskich. Nie wiadomo wtedy jaka wartość znajdzie się w kanale: mamy tu do czynienia z niepożądanym niedeterminizmem.

Слайд 48Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

1

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

UA y MN z SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

0

0

0 1 2 3 4 5 6 7

UA u DZ v SΩ 6 DO kan PA x ST 0 PA kan ST 0

Слайд 49Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

UA y MN z SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

0

0

UA u DZ v SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

UA y

UA u

Слайд 50Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

3

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

UA y MN z SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

1

1

3.14 2.0 15.9 3.0

kan y z u v x

Ω

UA u DZ v SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

UA y

UA u

3.14

15.9

Слайд 51Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

4

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

UA y MN z SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

1

1

UA u DZ v SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

MN z

DZ v

3.14

15.9

Слайд 52Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

5

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

UA y MN z SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

2

2

UA u DZ v SΩ 6 DO kan PA x ST 0 PA kan ST 0

0 1 2 3 4 5 6 7

MN z

DZ v

6.28

5.3

Слайд 53SΩ 6

6.28

5.3

SΩ 6

SΩ 6

6.28

5.3

SΩ 6

Слайд 54SΩ 6

6.28

5.3

SΩ 6

BŁĄD! Obydwa procesory jednocześnie widziały w kanale symbol Ω

SΩ 6

6.28

5.3

SΩ 6

BŁĄD! Obydwa procesory jednocześnie widziały w kanale symbol Ω

Слайд 55PA kan

6.28

5.3

PA kan

PA kan

6.28

5.3

PA kan

Слайд 56PA kan

6.28

5.3

PA kan

PA kan

6.28

5.3

PA kan

Слайд 57ST 0

6.28

5.3

ST 0

???

ST 0

6.28

5.3

ST 0

???

Слайд 58ST 0

6.28

5.3

ST 0

???

ST 0

6.28

5.3

ST 0

???

Слайд 59Po wykonaniu instrukcji x := y*z+u/v zmienna x nie otrzymała

wartości wyrażenia

Po wykonaniu instrukcji x := y*z+u/v zmienna x nie otrzymała

wartości wyrażenia

(zawartość komórki x jest taka jak przed wykonaniem!)

Слайд 60Jak zaprogramować poprawnie? Trzeba synchronizować procesy!

Można zastosować mechanizm semaforów (tu binarnych) –

Jak zaprogramować poprawnie? Trzeba synchronizować procesy!

Można zastosować mechanizm semaforów (tu binarnych) –

Semafor (E.W. Dijkstra) binarny jest zmienną przyjmującą wartości 0 i 1, wspólną dla programów współdzielących chroniony zasób. Dopuszczalne są na niej dwie operacje nazywane zwykle P i V, o następującym znaczeniu, gdzie zmienna sem jest semaforem:

P(sem): gdy sem > 0 to sem := sem - 1, gdy sem = 0 to wstrzymaj proces.

V(sem): sem := 1; wznów któryś z wstrzymanych procesów (np. wstrzymywany najdłużej).

Fragment programu użytkownika między operacjami P(sem) i odpowiadajacym V(sem) to sekcja krytyczna chroniona semaforem sem.

Operacje P, V (oznaczane niekiedy wait, signal) są niepodzielne (atomowe): gdy jakiś program wykonuje którąś, to inny nie może w tym czasie wykonać żadnej. Same są też sekcjami krytycznymi ale wykonywanymi na niższym poziomie niż programy użytkownika (np. w układach elektronicznych komputera lub w jądrze systemu operacyjnego).

Слайд 62sem = 0

2

sem = 0

2

Слайд 63sem = 0

3

sem = 0

3

Слайд 64sem = 0

4

sem = 0

4

Слайд 65sem = 1

5

sem = 1

5

Слайд 66sem = 0

6

sem = 0

6

Слайд 67sem = 0

7

sem = 0

7

Слайд 68sem = 0

8

sem = 0

8

Слайд 69sem = 1

9

sem = 1

9

Слайд 70sem = 1

10

sem = 1

10

Слайд 71Symulacja wykonania programu na schemacie funkcjonalnym systemu

2-procesorowego z dostępem do wspólnej

Symulacja wykonania programu na schemacie funkcjonalnym systemu

2-procesorowego z dostępem do wspólnej

Synchronizacja semaforowa – wzajemne wykluczanie.

Sekcja krytyczna: rozkazy czerwone

Rozwiązanie poprawne!

LR – licznik rozkazów RR – rejestr rozkazów A – akumulator

Przykład działania: obliczenie x := y*z + u/v

Слайд 72Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

1

pamięć lokalna programu

LR:

RR:

A:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

0 1 2 3 4 5 6 7

0

0

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

PA kan

V(sem)

ST 0

PA kan

V(sem)

ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

8 9 10

inne rejestry:

Слайд 73Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

2

pamięć lokalna programu

LR:

RR:

A:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

0

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

UA y

UA u

inne rejestry:

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 74Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

3

pamięć lokalna programu

LR:

RR:

A:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

0 1 2 3 4 5 6 7

1

1

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

UA y

UA u

3.14

15.9

inne rejestry:

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 75Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

4

pamięć lokalna programu

LR:

RR:

A:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

0 1 2 3 4 5 6 7

1

1

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

MN z

DZ v

3.14

15.9

inne rejestry:

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 76Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

5

pamięć lokalna programu

LR:

RR:

A:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

0 1 2 3 4 5 6 7

2

2

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

MN z

DZ v

6.28

5.3

inne rejestry:

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 77Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

6

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

0 1 2 3 4 5 6 7

2

2

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

P(sem)

P(sem)

6.28

5.3

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 78Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

7

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

3

2

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

P(sem)

P(sem)

6.28

5.3

zmienia komputer 1

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 79Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

8

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

3

2

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

SΩ 8

P(sem)

6.28

5.3

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 80Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

9

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

8

2

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

SΩ 8

P(sem)

6.28

5.3

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 81Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

10

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

8

2

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

PA kan

P(sem)

6.28

5.3

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 82Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

11

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

9

2

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

PA kan

P(sem)

6.28

5.3

6.28

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 83Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

12

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

9

2

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

P(sem)

6.28

5.3

6.28

V(sem)

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 84Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

13

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

10

2

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

P(sem)

6.28

5.3

6.28

V(sem)

zmienia komputer 1

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 85Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

14

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

(wstrzymany)

pamięć wspólna danych

0 1 2 3 4 5 6 7

10

2

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

P(sem)

6.28

5.3

6.28

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 86Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

15

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

3

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

6.28

5.3

6.28

ST 0

zmienia komputer 2

P(sem)

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 87Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

16

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

3

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

SΩ 8

6.28

5.3

6.28

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 88Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

17

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

4

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

SΩ 8

6.28

5.3

6.28

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 89Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

18

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

4

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

DO kan

6.28

5.3

6.28

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 90Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

19

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

5

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

DO kan

6.28

11.58

6.28

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 91Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

20

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

5

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

PA x

6.28

11.58

6.28

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 92Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

21

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

6

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

PA x

6.28

11.58

6.28

ST 0

11.58

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 93Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

22

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

6

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

0

8 9 10

ST 0

ST 0

8 9 10

V(sem)

6.28

11.58

6.28

ST 0

11.58

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 94Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

23

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wstrzymany)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

7

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

8 9 10

V(sem)

6.28

11.58

6.28

ST 0

11.58

zmienia komputer 2

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 95Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

24

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wznowiony)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

7

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

8 9 10

ST 0

6.28

11.58

6.28

ST 0

11.58

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 96Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

25

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

(wznowiony)

komputer 2

(wznowiony)

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

0

3.14 2.0 15.9 3.0

sem kan y z u v x

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

8 9 10

ST 0

6.28

11.58

6.28

ST 0

11.58

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 97Symulacja wykonania programu na schemacie funkcjonalnym systemu

2-procesorowego z dostępem do wspólnej

Symulacja wykonania programu na schemacie funkcjonalnym systemu

2-procesorowego z dostępem do wspólnej

Synchronizacja semaforowa – wzajemne wykluczanie.

Sekcja krytyczna: rozkazy czerwone

Rozwiązanie poprawne!

LR – licznik rozkazów RR – rejestr rozkazów A – akumulator

Przykład działania: obliczenie x := y*z + u/v

Слайд 98Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

1

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 1

komputer 2

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

0

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

0 1 2 3 4 5 6 7

1

8 9 10

ST 0

ST 0

8 9 10

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 99Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

2

LR:

komputer 1

pamięć wspólna danych

0 1 2 3 4 5 6 7

0

3.14 2.0 15.9 3.0

sem kan y z u v x

Ω

1

8 9 10

ST 0

UA y

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 2

0

0 1 2 3 4 5 6 7

ST 0

8 9 10

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 100 3

pamięć wspólna danych

3.14 2.0 15.9 3.0

sem kan y z u v

3

pamięć wspólna danych

3.14 2.0 15.9 3.0

sem kan y z u v

Ω

1

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 2

0

0 1 2 3 4 5 6 7

ST 0

8 9 10

UA u

2

pamięć lokalna programu

LR:

RR:

A:

komputer 1

0 1 2 3 4 5 6 7

1

8 9 10

UA y

3.14

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

RR := zawartość adresu wskazanego przez LR

inne rejestry:

ST 0

UA y MN z P(sem) SΩ 8 DO kan PA x V(sem) ST 0

UA u DZ v P(sem) SΩ 8 DO kan PA x V(sem) ST 0

PA kan

V(sem)

PA kan

V(sem)

Слайд 101 4

pamięć wspólna danych

3.14 2.0 15.9 3.0

sem kan y z u v

4

pamięć wspólna danych

3.14 2.0 15.9 3.0

sem kan y z u v

Ω

1

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

2

pamięć lokalna programu

LR:

RR:

A:

inne rejestry:

RR := zawartość adresu wskazanego przez LR

komputer 2

0

0 1 2 3 4 5 6 7

ST 0

8 9 10

UA u

2

pamięć lokalna programu

LR:

RR:

A:

komputer 1

0 1 2 3 4 5 6 7

1

8 9 10

MN z

3.14

Gdy w RR jest rozkaz:

skoku bezwarunkowego to LR:=część adresowa

skoku warunkowego i warunek jest spełniony to

LR:=część adresowa; gdy nie to LR:=LR+1

stopu to LR:=część adresowa i zakończ działanie

inny to wykonaj go i LR:=LR+1

RR := zawartość adresu wskazanego przez LR

inne rejestry:

ST 0