Содержание

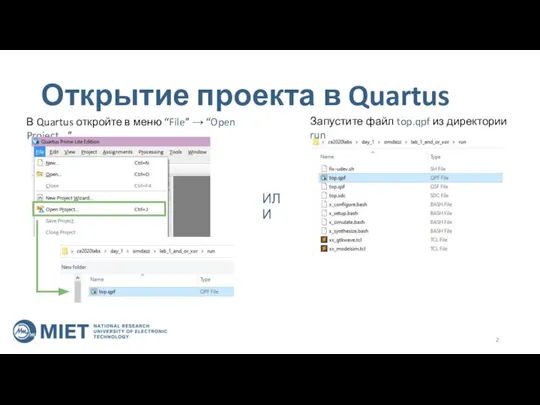

- 2. Открытие проекта в Quartus В Quartus откройте в меню “File” → “Open Project...” ИЛИ Запустите файл

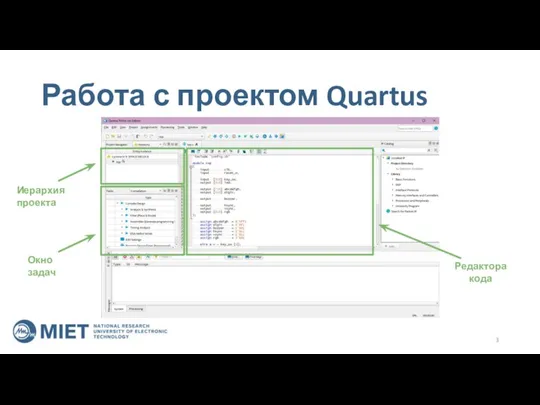

- 3. Работа с проектом Quartus Иерархия проекта Редактора кода Окно задач

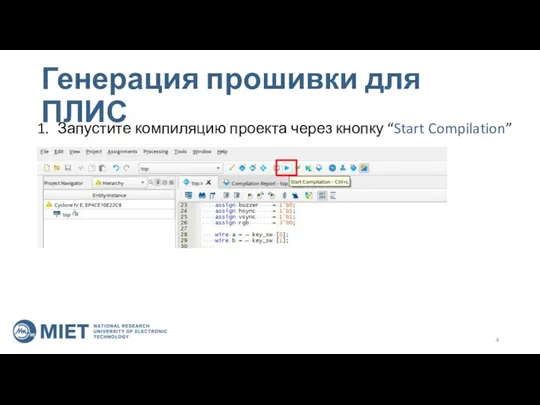

- 4. Генерация прошивки для ПЛИС 1. Запустите компиляцию проекта через кнопку “Start Compilation”

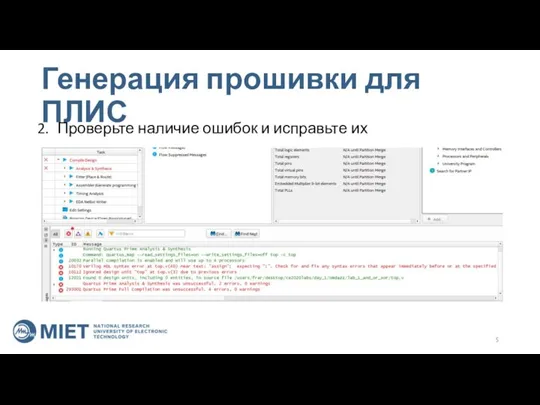

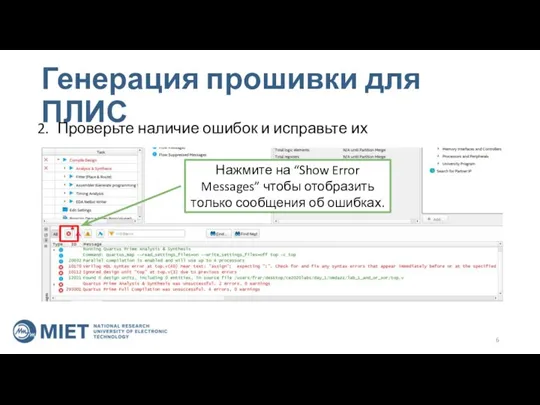

- 5. Генерация прошивки для ПЛИС 2. Проверьте наличие ошибок и исправьте их

- 6. Генерация прошивки для ПЛИС 2. Проверьте наличие ошибок и исправьте их Нажмите на “Show Error Messages”

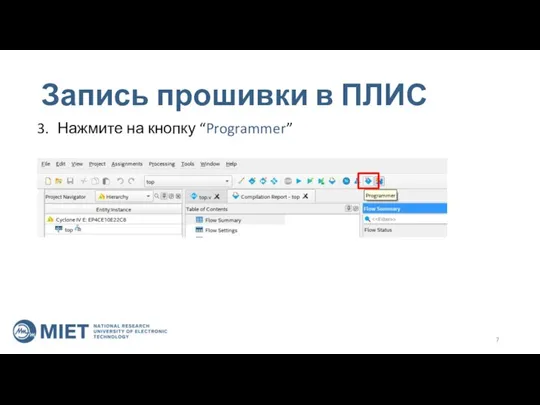

- 7. Запись прошивки в ПЛИС 3. Нажмите на кнопку “Programmer”

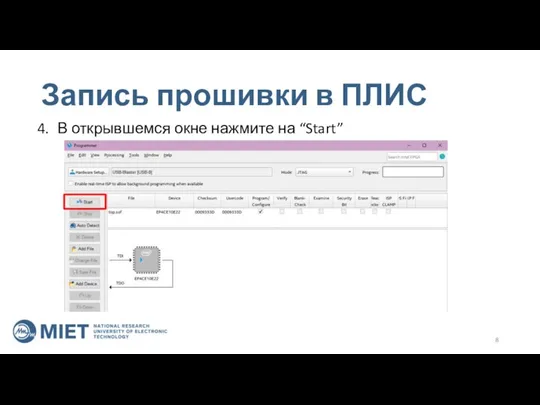

- 8. Запись прошивки в ПЛИС 4. В открывшемся окне нажмите на “Start”

- 9. Упражнение с логическими элементами Altera Cyclone IV EP4CE6 FPGA Вывод результатов логических операций над входными воздействиями

- 10. Упражнение с логическими элементами module top ( … input [3:0] key_sw, output [3:0] led, … );

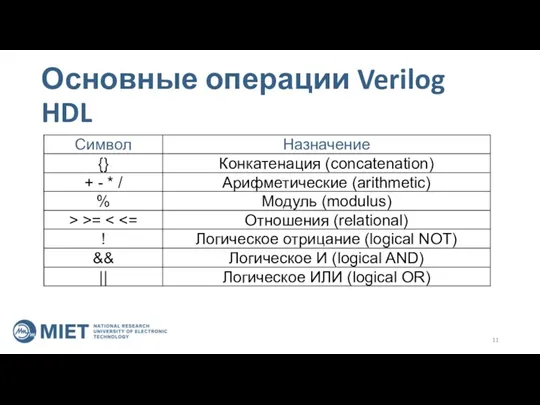

- 11. Основные операции Verilog HDL

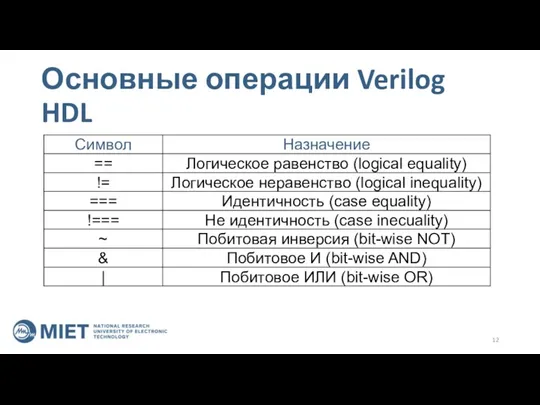

- 12. Основные операции Verilog HDL

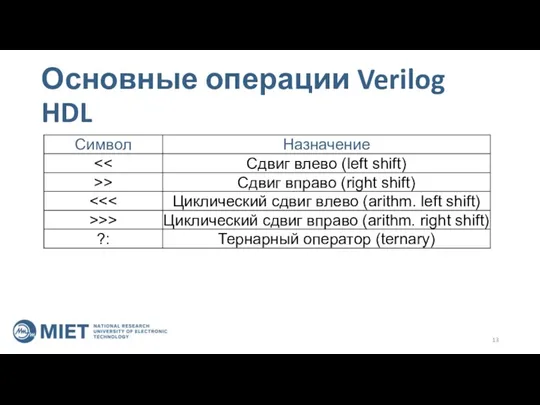

- 13. Основные операции Verilog HDL

- 14. Упражнение с логическими элементами Присвойте led[2] результат операции И (AND). Присвойте led[3] результат операции исключающего ИЛИ

- 15. Упражнение с логическими элементами

- 16. Упражнение с выводом буквы на семисегментный индикатор Altera Cyclone IV EP4CE6 FPGA Вывод статичных значений на

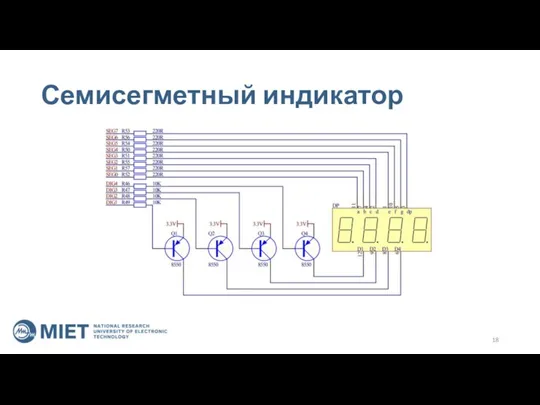

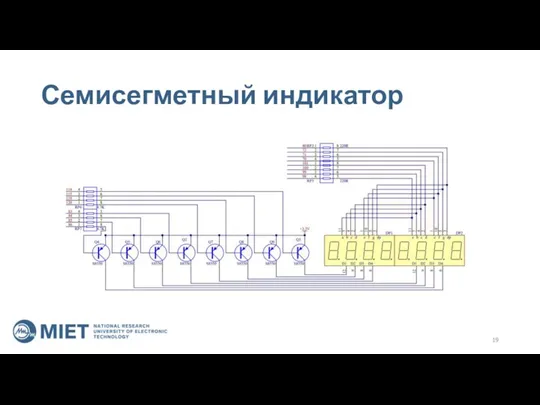

- 17. Семисегметный индикатор

- 18. Семисегметный индикатор

- 19. Семисегметный индикатор

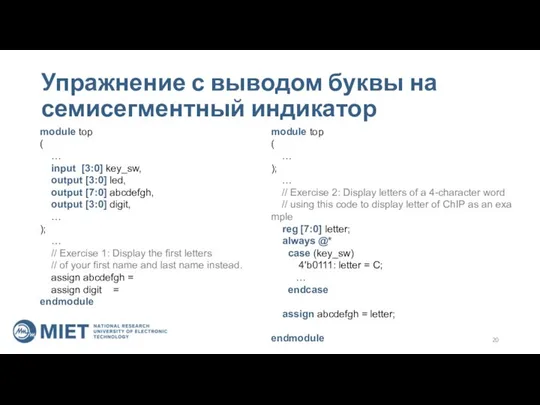

- 20. Упражнение с выводом буквы на семисегментный индикатор module top ( … input [3:0] key_sw, output [3:0]

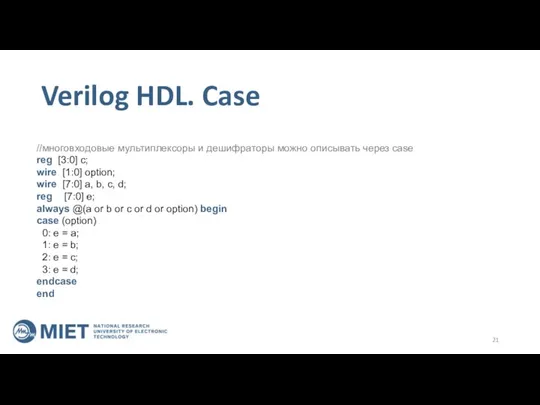

- 21. Verilog HDL. Case //многовходовые мультиплексоры и дешифраторы можно описывать через case reg [3:0] c; wire [1:0]

- 22. Упражнение с выводом буквы на семисегментный индикатор Выведите первые буквы своего имени и фамилии на семисегментный

- 23. Упражнение с выводом буквы на семисегментный индикатор

- 24. Последовательностная логика Входы Выходы Комбинационная логика

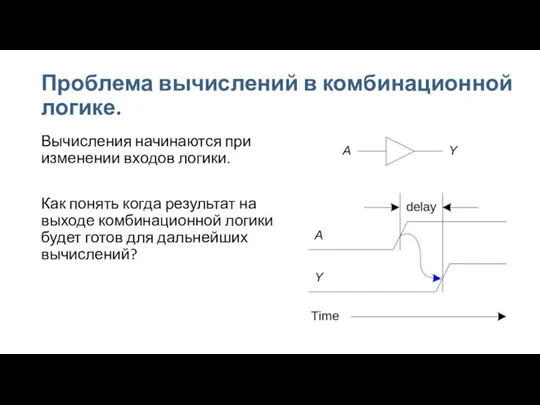

- 25. Проблема вычислений в комбинационной логике. Вычисления начинаются при изменении входов логики. Как понять когда результат на

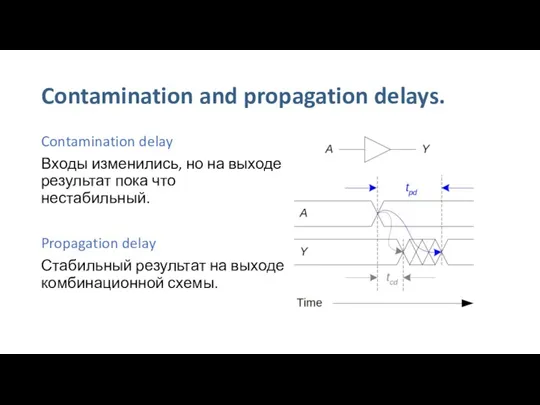

- 26. Contamination and propagation delays. Contamination delay Входы изменились, но на выходе результат пока что нестабильный. Propagation

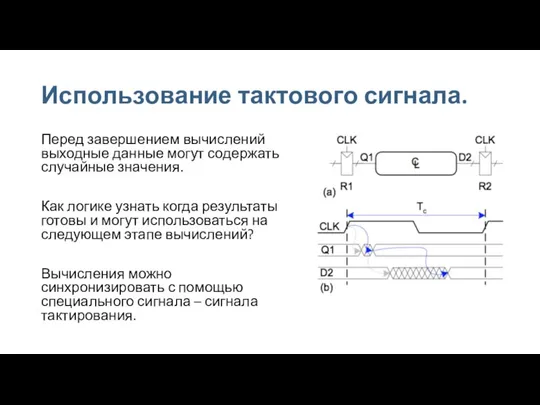

- 27. Использование тактового сигнала. Перед завершением вычислений выходные данные могут содержать случайные значения. Как логике узнать когда

- 28. Последовательностная логика Входы Выходы ПЛ ПЛ Комбинационная логика Тактирование Тактирование

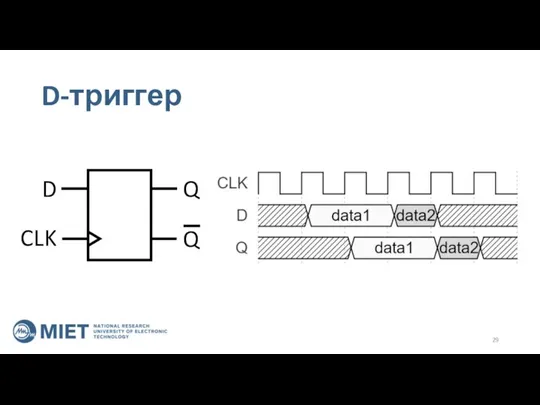

- 29. D-триггер D CLK Q Q

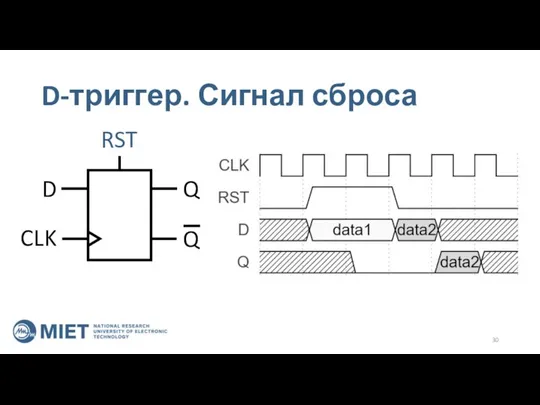

- 30. D-триггер. Сигнал сброса D CLK Q Q RST

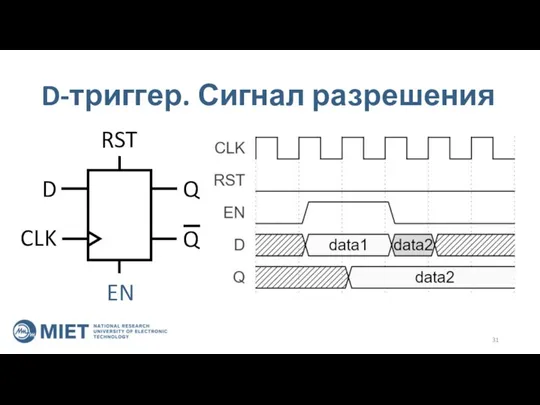

- 31. D-триггер. Сигнал разрешения D CLK Q Q RST EN

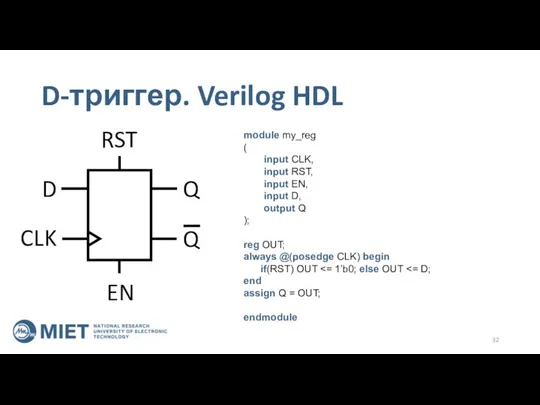

- 32. D-триггер. Verilog HDL D CLK Q Q RST EN module my_reg ( input CLK, input RST,

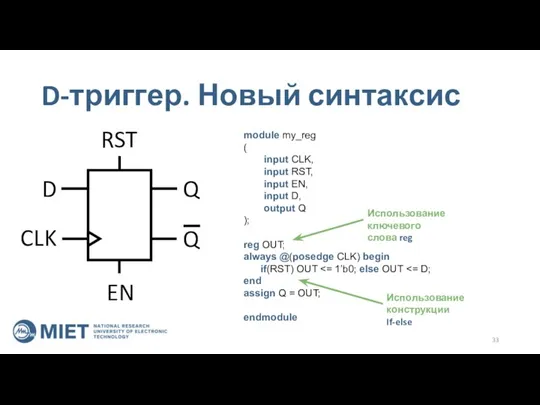

- 33. D-триггер. Новый синтаксис D CLK Q Q RST EN module my_reg ( input CLK, input RST,

- 34. Упражнение со счетчиком Altera Cyclone IV EP4CE6 FPGA Вывод значений счетчика на светодиоды. Использование кнопок для

- 35. Упражнение со счетчиком module top ( … ); … reg [31:0] cnt; always @ (posedge clk

- 36. Упражнение со счетчиком Свободно запустите счетчик. Как изменить скорость мигания светодиодов? Измените дизайн. Например, добавьте управление

- 37. Упражнение со счетчиком

- 38. Упражнение со сдвиговым регистром Altera Cyclone IV EP4CE6 FPGA Управление мерцанием светодиодов и семисегментоного индикатора при

- 39. Упражнение со сдвиговым регистром module top ( … ); … reg [31:0] cnt; always @ (posedge

- 40. Упражнение со сдвиговым регистром “Заставьте” светодиоды изменить направление мерцания. Зациклите мерцание светодиодов. Измените состояние семисегментного индикатора,

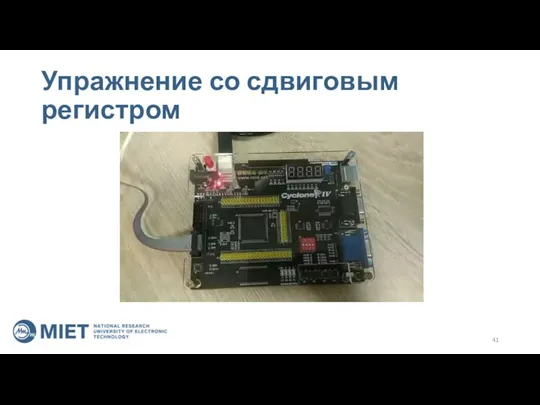

- 41. Упражнение со сдвиговым регистром

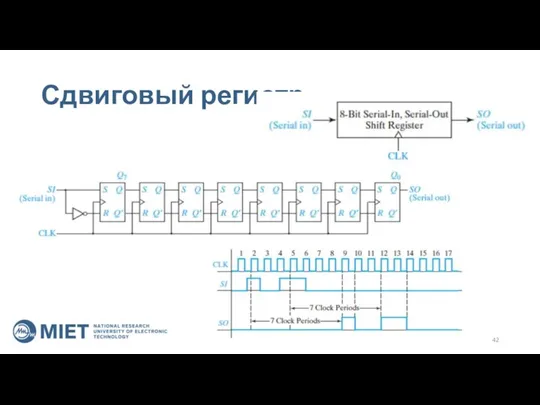

- 42. Сдвиговый регистр

- 43. Упражнение: вывод слова на семисегментый индикатор Altera Cyclone IV EP4CE6 FPGA Вывод слова на семисегментный индикатор

- 44. Семисегметный индикатор

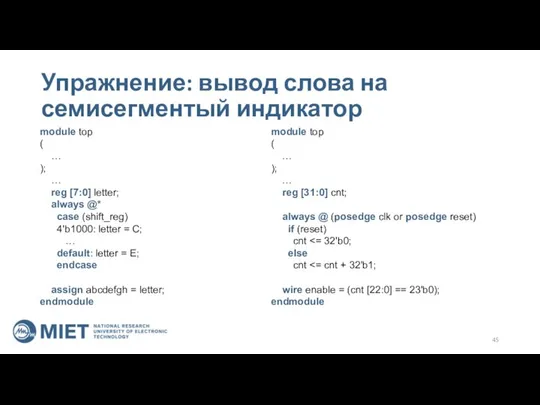

- 45. Упражнение: вывод слова на семисегментый индикатор module top ( … ); … reg [7:0] letter; always

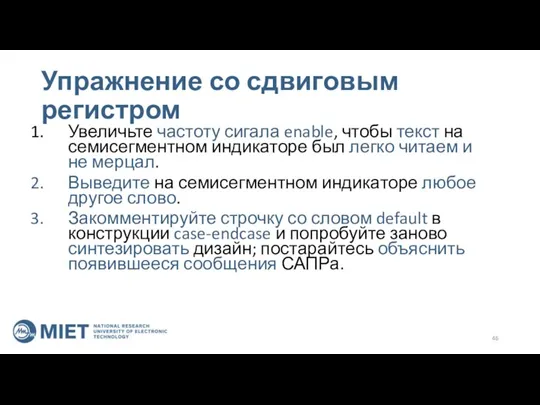

- 46. Упражнение со сдвиговым регистром Увеличьте частоту сигала enable, чтобы текст на семисегментном индикаторе был легко читаем

- 47. Упражнение: вывод слова на семисегментый индикатор

- 49. Скачать презентацию

![Упражнение с логическими элементами module top ( … input [3:0] key_sw, output](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1160592/slide-9.jpg)

![Упражнение с логическими элементами Присвойте led[2] результат операции И (AND). Присвойте led[3]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1160592/slide-13.jpg)

![Упражнение со счетчиком module top ( … ); … reg [31:0] cnt;](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1160592/slide-34.jpg)

![Упражнение со сдвиговым регистром module top ( … ); … reg [31:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1160592/slide-38.jpg)

ВКР: Оценка защиты web-ресурсов от кибератак

ВКР: Оценка защиты web-ресурсов от кибератак 06 Коммуникационные протоколы

06 Коммуникационные протоколы Позиционная система счисления

Позиционная система счисления Web-конструирование. Практическое занятие. Создание многостраничного сайта. 2 занятие

Web-конструирование. Практическое занятие. Создание многостраничного сайта. 2 занятие Этапы проектирования ИС с применением UML

Этапы проектирования ИС с применением UML Вычисление рекуррентных выражений (Задние 16)

Вычисление рекуррентных выражений (Задние 16) MPA1000 sw-master Doxygen documentation

MPA1000 sw-master Doxygen documentation Виды моделей ЖЦ ПО

Виды моделей ЖЦ ПО 3. Formalar

3. Formalar Обзор сервиса

Обзор сервиса Алгоритмический язык стрелок для создания циклического алгоритма

Алгоритмический язык стрелок для создания циклического алгоритма Онлайн система ERP.travel

Онлайн система ERP.travel Part 3

Part 3 Киберспорт

Киберспорт Представление и кодирование информации с помощью знаковых систем

Представление и кодирование информации с помощью знаковых систем Installation testing mentoring program for manual QA

Installation testing mentoring program for manual QA Низкоуровневое программирование. Интерпретация, компиляция, компоновка

Низкоуровневое программирование. Интерпретация, компиляция, компоновка Что такое информация?

Что такое информация? Что называется компьютером?

Что называется компьютером? Повторяем переменную

Повторяем переменную Ресурсы для защиты информации в веке IT технологий

Ресурсы для защиты информации в веке IT технологий Интерактивный плакат по дисциплине Конструирование ювелирных изделий

Интерактивный плакат по дисциплине Конструирование ювелирных изделий Архитектура ПК

Архитектура ПК История развития вычислительной техники (часть 1)

История развития вычислительной техники (часть 1) Актуальные проблемы информатизации образования Материал подготовила: учитель английского языка высшей категории Ведь

Актуальные проблемы информатизации образования Материал подготовила: учитель английского языка высшей категории Ведь  Прикладное программирование на Java СКБ-лаб

Прикладное программирование на Java СКБ-лаб Техника безопасности. Правила работы на компьютере

Техника безопасности. Правила работы на компьютере Устройство компьютера

Устройство компьютера