Содержание

- 2. Упрощенная модель вычислительной системы с многозадачной ОС Современная ЭВМ представляет собой комплекс автономных устройств, каждое из

- 3. «Зона внимания» центрального процессора Во время работы вычислительной системы к ЦП поступает от других устройств или

- 4. Пример. Пусть «зону внимания» программы кроме 2-х регистров данных составляет еще и регистр флагов ЦП., то

- 5. Проблема! Пусть «зону внимания» программы кроме 2-х регистров данных составляет еще и регистр флагов ЦП., то

- 6. Попытка устранения проблемы. И НОВЫЕ ПРОБЛЕМЫ … Если попробовать включить все заслуживающие внимания события в зону

- 7. Выход есть! Для того чтобы ЦП, выполняя свою работу, имел возможность реагировать на события, происходящие вне

- 8. Цель введения прерываний Идея прерываний была предложена в середине 50-х годов. Основные цели введения прерываний: 1.

- 9. Прерывание и его суть Прерывания представляют собой механизм, позволяющий координировать параллельное функционирование отдельных устройств вычислительной системы

- 10. Механизм прерываний Механизм прерываний реализуется аппаратно-программными средствами и независимо от архитектуры вычислительной системы включает 7 шагов.

- 11. 7 шагов механизма прерываний 1. Установление факта прерывания (прием сигнала на прерывание) и идентификация прерывания (в

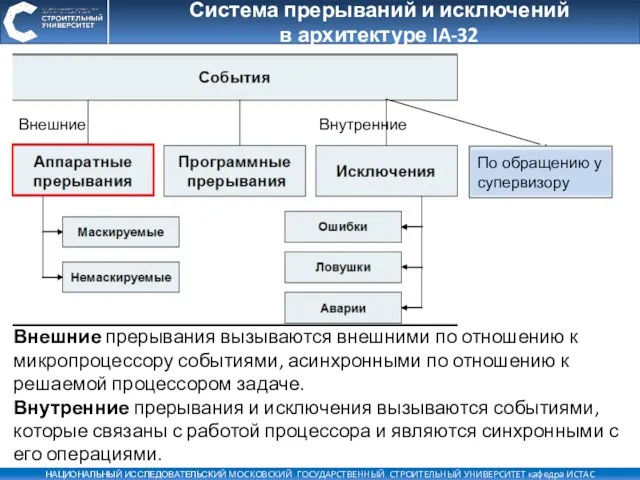

- 12. Система прерываний и исключений в архитектуре IA-32 Внешние прерывания вызываются внешними по отношению к микропроцессору событиями,

- 13. Внешние прерывания Внешние прерывания вызываются внешними по отношению к микропроцессору событиями, асинхронными по отношению к решаемой

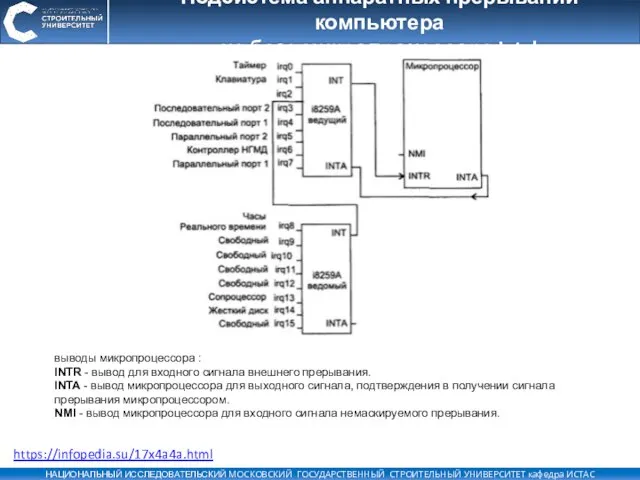

- 14. Подсистема аппаратных прерываний компьютера на базе микропроцессора Intel https://infopedia.su/17x4a4a.html выводы микропроцессора : INTR - вывод для

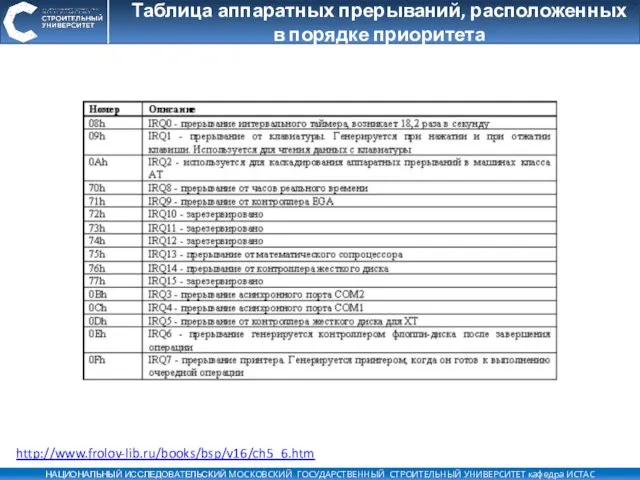

- 15. Таблица аппаратных прерываний, расположенных в порядке приоритета http://www.frolov-lib.ru/books/bsp/v16/ch5_6.htm

- 16. Исключения Исключения вызываются событиями, которые связаны с работой процессора и являются синхронными с его операциями. Примеры:

- 17. Программные прерывания и прерывания по обращению к супервизору. Программные прерывания относятся к внутренними событиям. Эти прерывания

- 18. Приоритеты прерываний и исключений Сигналы, вызывающие прерывания и исключения, формируются вне процессора или в самом процессоре;

- 19. Маски и механизм маскИрования Обычно внешние прерывание обрабатывается только после завершения выполнения текущей команды. Наличие сигнала

- 20. Механизм маскирования и дисциплины обслуживания Программное управление специальными регистрами маски (маскирование сигналов прерывания) позволяет реализовать различные

- 21. Механизм маскирования и обслуживание с относительным приоритетом Обслуживание принятого на обработку запроса не прерывается даже при

- 22. Механизм маскирования и обслуживание с абсолютным приоритетом Всегда обслуживается прерывание с наивысшим приоритетом! Обслуживание принятого на

- 23. Механизм маскирования и внешние прерывания Внешние прерывания делятся на немаскируемые и маскируемые. Запрос немаскируемого прерывания, поступающий

- 24. Способы запрета и разрешения внешних прерываний сброс или установка соответствующих биты INTE (Interrupt Enable) регистров состояний

- 25. Система прерываний и исключений в архитектуре IA-32 Внешние прерывания вызываются внешними по отношению к микропроцессору событиями,

- 26. Исключения в прерываний персональных компьютеров типа IBM PC ОТКАЗЫ (faults) - выявляются и обслуживаются перед выполнением

- 27. Примеры исключений типа «ловушка» 1h - ОТЛАДКА возникает при пошаговом выполнении; при обращении к сегменту состояния

- 28. Примеры исключений типа «отказ» 0h - ОШИБКА ДЕЛЕНИЯ генерируется сразу после выполнения команд деления DIV и

- 29. Примеры исключений типа «отказ» Ah - НЕРАЗРЕШЕННЫЙ СЕГМЕНТ TSS возникает при переключении задач при неверном TSS;

- 30. Примеры исключений типа «отказ» Eh - ОТСУТСТВИЕ ДОСТУПА К СТРАНИЦЕ имеет место при страничной адресации если

- 31. Примеры исключений типа «выход из процесса» 8h - ДВОЙНАЯ ОШИБКА фиксируется, если при обслуживании исключений Ah..Dh

- 32. Последовательность проверки исключений и прерываний Команда i Текущая Команда i+1 Следующая Внешнее прерывание Запросы на обработку

- 33. Последовательность проверок исключений и прерываний 2. Проверяются отказы следующей команды по значениям регистров отладки; 3. Проверяется

- 34. Последовательность проверок исключений и прерываний 5. Проверяются отказы страничной организации (исключение Eh); 6. Проверяются отказы дешифрации

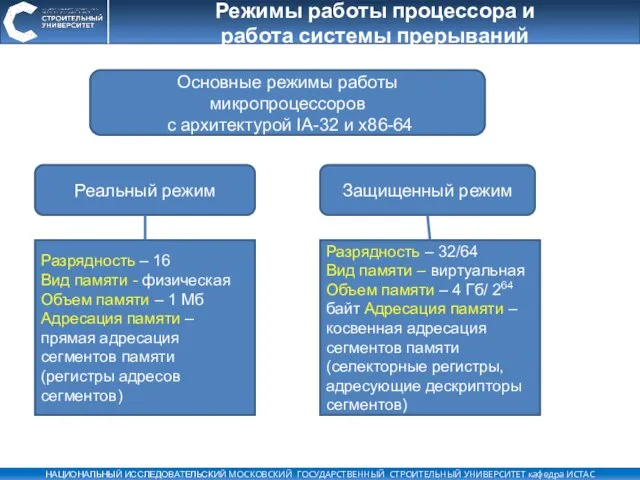

- 35. Режимы работы процессора и работа системы прерываний Основные режимы работы микропроцессоров с архитектурой IA-32 и x86-64

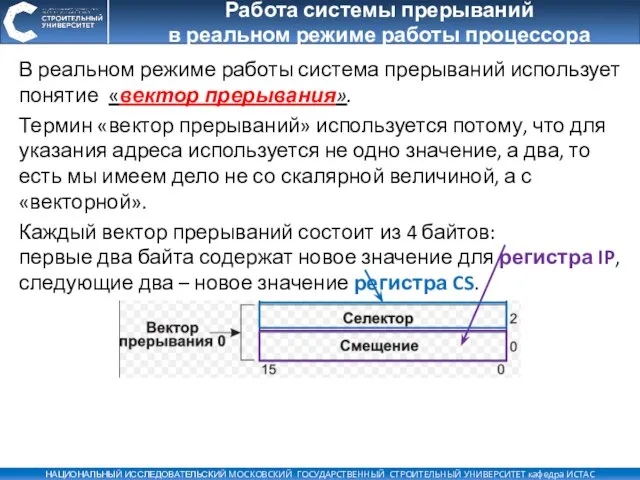

- 36. Работа системы прерываний в реальном режиме работы процессора В реальном режиме работы система прерываний использует понятие

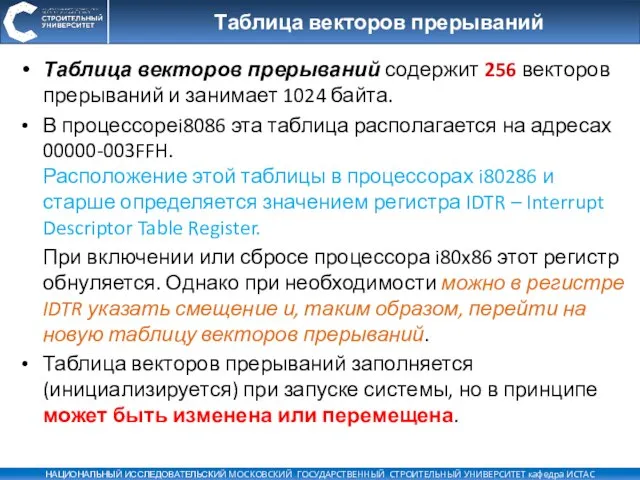

- 37. Таблица векторов прерываний Таблица векторов прерываний содержит 256 векторов прерываний и занимает 1024 байта. В процессореi8086

- 38. Как найти нужный вектор прерываний в таблице Каждый вектор прерывания имеет свой номер, называемый номером прерывания,

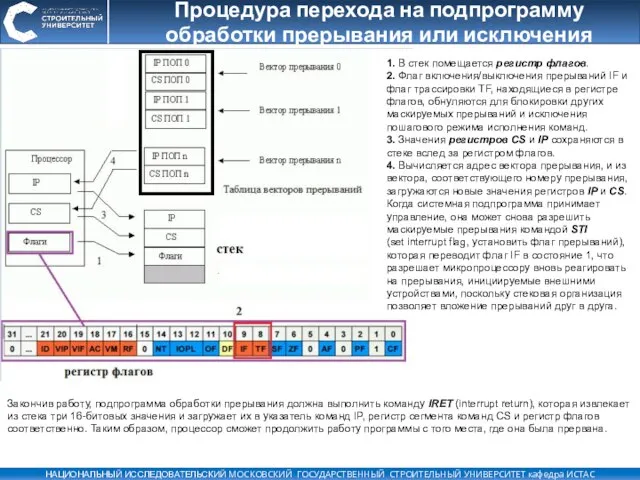

- 39. Процедура перехода на подпрограмму обработки прерывания или исключения 1. В стек помещается регистр флагов. 2. Флаг

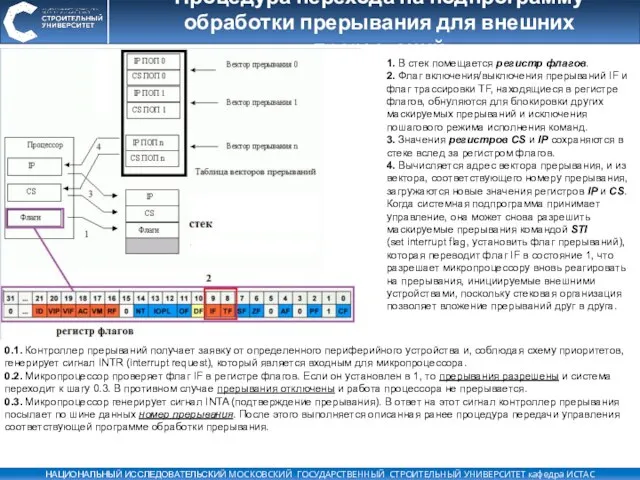

- 40. Процедура перехода на подпрограмму обработки прерывания для внешних прерываний 1. В стек помещается регистр флагов. 2.

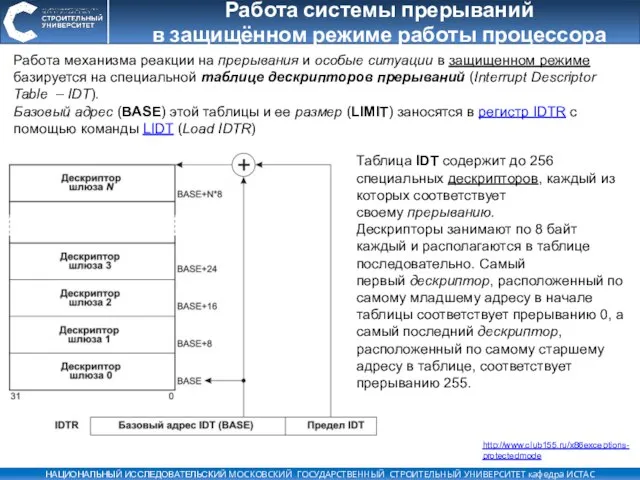

- 41. Работа системы прерываний в защищённом режиме работы процессора http://www.club155.ru/x86exceptions-protectedmode Работа механизма реакции на прерывания и особые

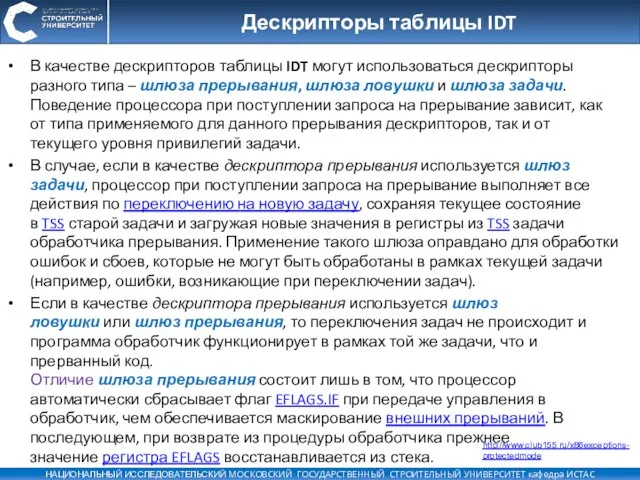

- 42. Дескрипторы таблицы IDT http://www.club155.ru/x86exceptions-protectedmode В качестве дескрипторов таблицы IDT могут использоваться дескрипторы разного типа – шлюза

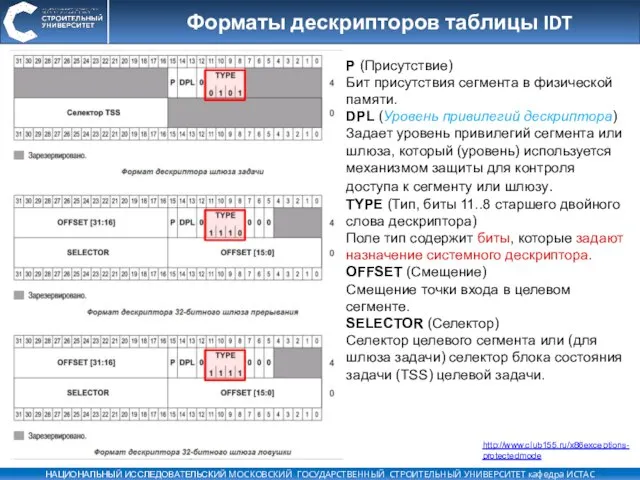

- 43. Форматы дескрипторов таблицы IDT http://www.club155.ru/x86exceptions-protectedmode P (Присутствие) Бит присутствия сегмента в физической памяти. DPL (Уровень привилегий

- 44. Схема передачи управления при прерывании в контексте текущей задачи Полученный дескриптор анализируется, и если его тип

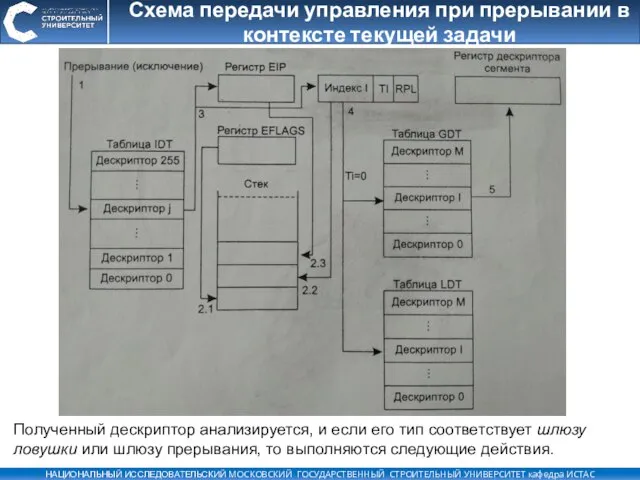

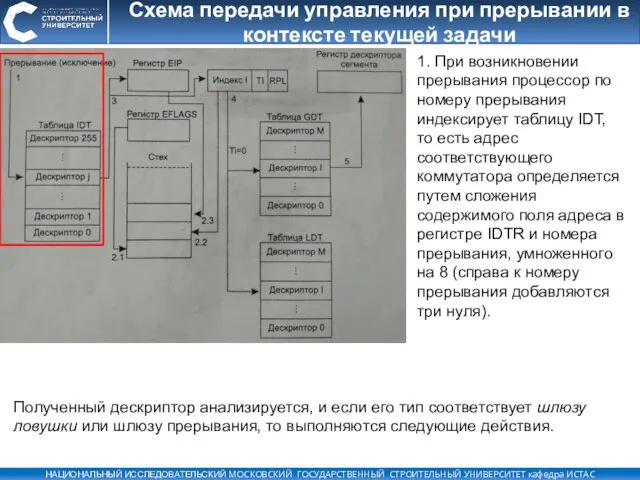

- 45. Схема передачи управления при прерывании в контексте текущей задачи Полученный дескриптор анализируется, и если его тип

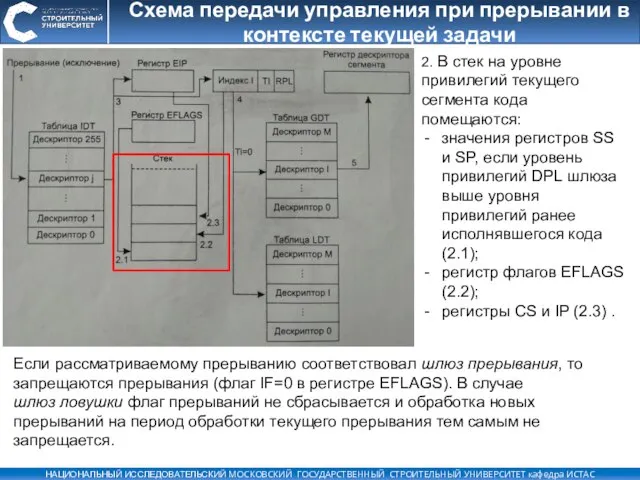

- 46. Схема передачи управления при прерывании в контексте текущей задачи 2. В стек на уровне привилегий текущего

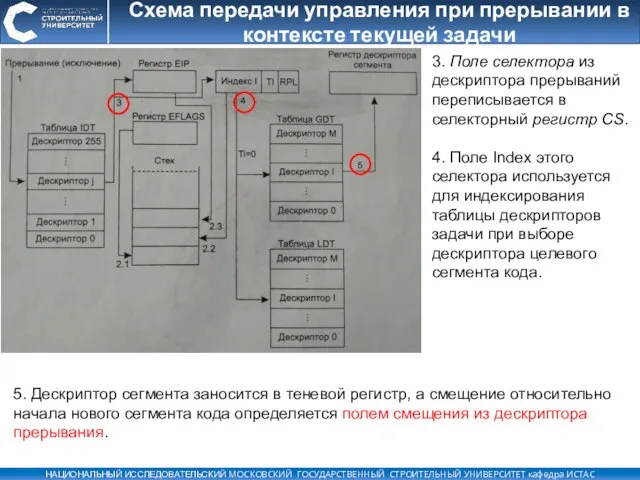

- 47. Схема передачи управления при прерывании в контексте текущей задачи 3. Поле селектора из дескриптора прерываний переписывается

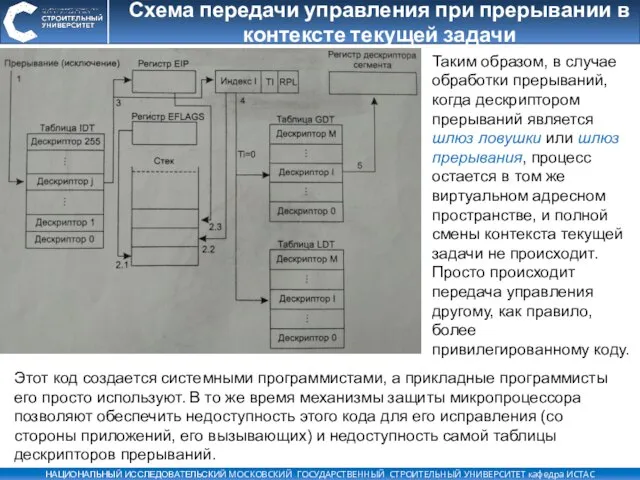

- 48. Схема передачи управления при прерывании в контексте текущей задачи Этот код создается системными программистами, а прикладные

- 50. Скачать презентацию

Востребованные компьютерные программы среди обучающихся школы

Востребованные компьютерные программы среди обучающихся школы Какой браузер лучше

Какой браузер лучше Инфомагия. Игра (8 класс)

Инфомагия. Игра (8 класс) Протокол IPv6. Вычислительные сети и коммуникации

Протокол IPv6. Вычислительные сети и коммуникации Утилиты ОС. Текстовый редактор

Утилиты ОС. Текстовый редактор Forbes 1917. История успеха

Forbes 1917. История успеха Интеллектуальная игра. Город Интернет

Интеллектуальная игра. Город Интернет Инструкция по экспорту документов

Инструкция по экспорту документов О применении алгоритма CLAHE к обработке спектрозональных изображений

О применении алгоритма CLAHE к обработке спектрозональных изображений Презентация на тему Представление об объектах окружающего мира

Презентация на тему Представление об объектах окружающего мира  Hello world. Your first program

Hello world. Your first program Аппаратное обеспечение ПК. Характеристики мобильных устройств

Аппаратное обеспечение ПК. Характеристики мобильных устройств Антиплагиат. Алгоритм проверки на плагиат

Антиплагиат. Алгоритм проверки на плагиат Кодирование звука

Кодирование звука Защита информации

Защита информации Освоение технологии работы в графическом редакторе

Освоение технологии работы в графическом редакторе Надежность программных продуктов

Надежность программных продуктов Рунет: жизнь на яркой стороне

Рунет: жизнь на яркой стороне How it+ differs from ++i

How it+ differs from ++i Современные информационные технологии в документационном обеспечении

Современные информационные технологии в документационном обеспечении I always come to work

I always come to work INEX. Главное меню

INEX. Главное меню Ключевые слова. Файлы и файловые структуры

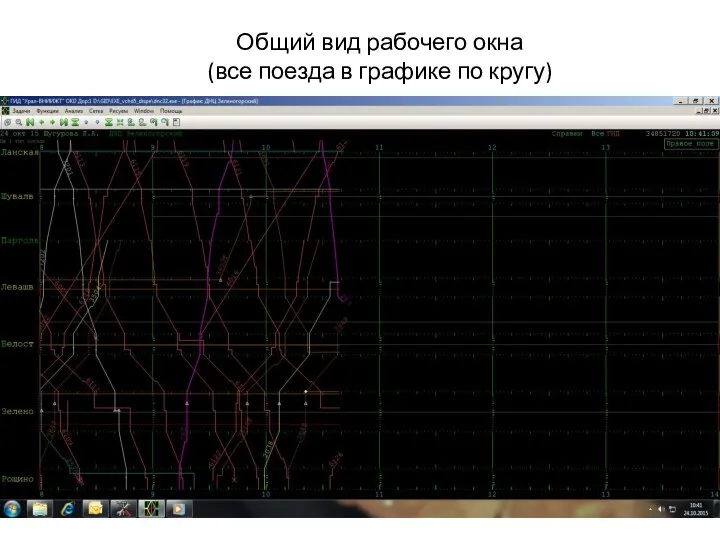

Ключевые слова. Файлы и файловые структуры Общий вид рабочего окна (все поезда в графике по кругу)

Общий вид рабочего окна (все поезда в графике по кругу) Система распределенных реестров

Система распределенных реестров урок 3

урок 3 Понятие информационной технологии, ее свойства. Роль информационных технологий в развитии общества

Понятие информационной технологии, ее свойства. Роль информационных технологий в развитии общества Мобильные вирусы: миф или угроза

Мобильные вирусы: миф или угроза