Содержание

- 2. Комбинационная логика C L Входы Выходы

- 3. Комбинационная логика I O Tcd Tpd

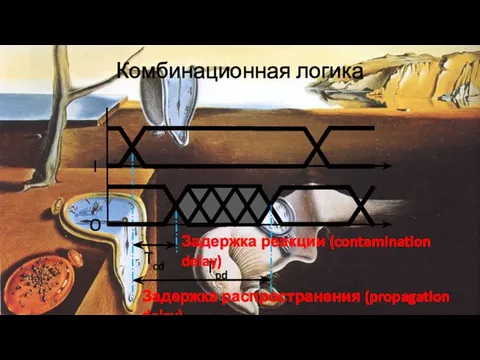

- 4. Комбинационная логика I O Tcd Tpd Задержка реакции (contamination delay) Задержка распространения (propagation delay)

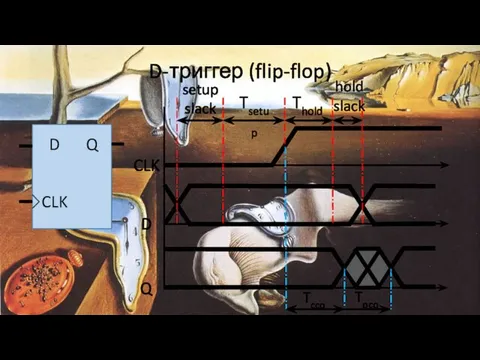

- 5. D-триггер (flip-flop) D Q CLK CLK D Q setup slack hold slack Tsetup Thold Tccq Tpcq

- 6. D-триггер (flip-flop) D Q CLK CLK D setup slack hold slack Tsetup Thold Запас на предустановку

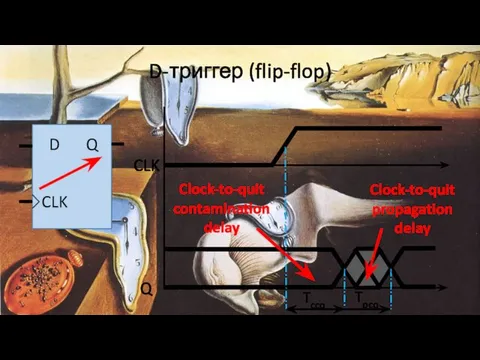

- 7. D-триггер (flip-flop) D Q CLK CLK Q Tccq Tpcq Clock-to-quit contamination delay Clock-to-quit propagation delay

- 8. Тракт между регистрами D Q CLK C L D Q CLK R1 R2 Q1 D2

- 9. Тракт между регистрами CLK D2 Q1 Tccq Tpcq Tclk Tcd Tpd

- 10. Тракт между регистрами Tclk ≥ Tpcq + Tpd + Tsetup Thold ≤ Tccq + Tcd Tpd

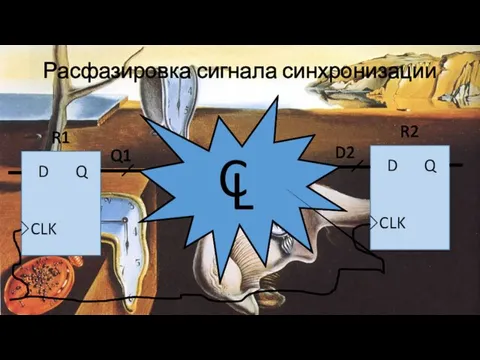

- 11. Расфазировка сигнала синхронизации D Q CLK C L D Q CLK R1 R2 Q1 D2

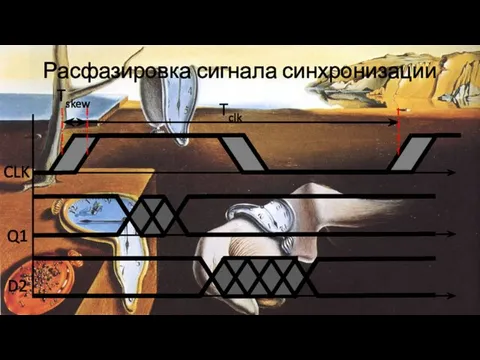

- 12. Расфазировка сигнала синхронизации CLK D2 Q1 Tskew Tclk

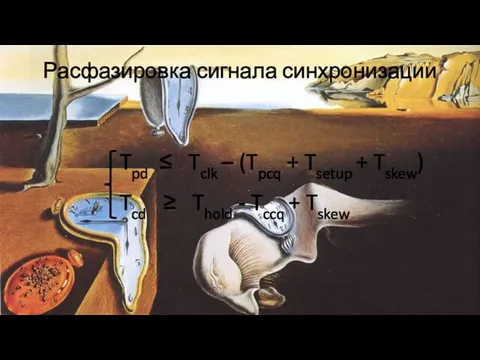

- 13. Расфазировка сигнала синхронизации Tpd ≤ Tclk – (Tpcq + Tsetup + Tskew) Tcd ≥ Thold -

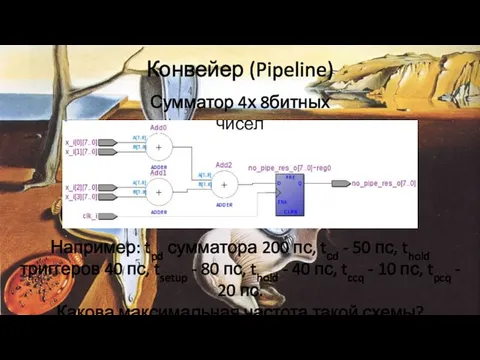

- 14. Конвейер (Pipeline) Сумматор 4х 8битных чисел Например: tpd сумматора 200 пс, tсd - 50 пс, thold

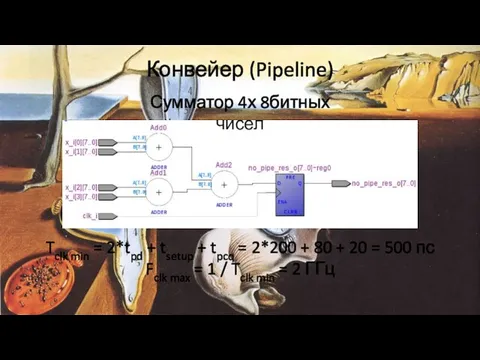

- 15. Конвейер (Pipeline) Сумматор 4х 8битных чисел Tclk min = 2*tpd + tsetup + tpcq = 2*200

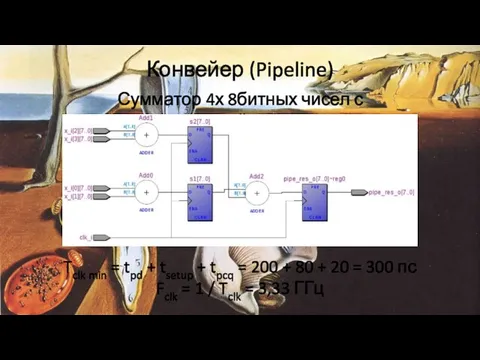

- 16. Конвейер (Pipeline) Сумматор 4х 8битных чисел с конвейером Tclk min = tpd + tsetup + tpcq

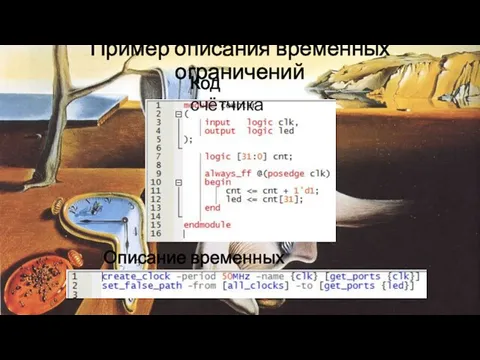

- 17. Пример описания временных ограничений Код счётчика Описание временных ограничений

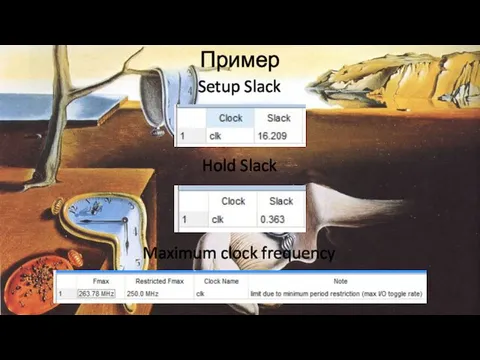

- 18. Пример Setup Slack Hold Slack Maximum clock frequency

- 20. Скачать презентацию

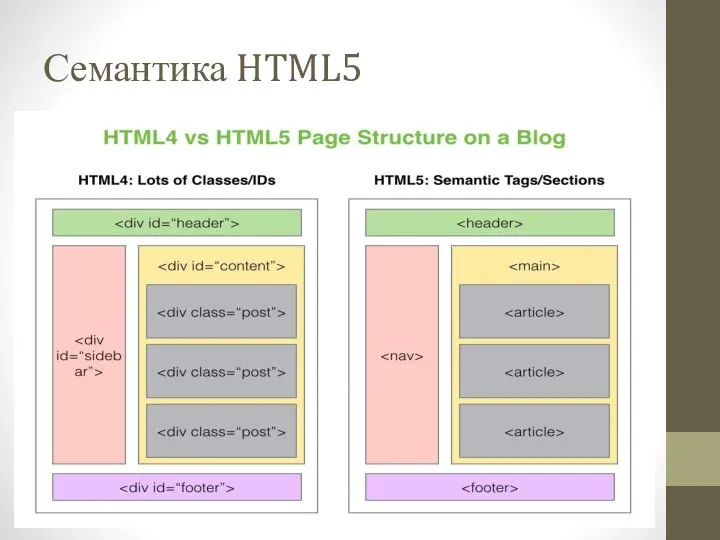

Семантика HTML 5

Семантика HTML 5 Data Science. Ярмарка вакансий

Data Science. Ярмарка вакансий Табличный процессор Excel

Табличный процессор Excel Образование на основе онлайновых социальных сетей

Образование на основе онлайновых социальных сетей Презентация на тему Время и числовая информация (2 класс)

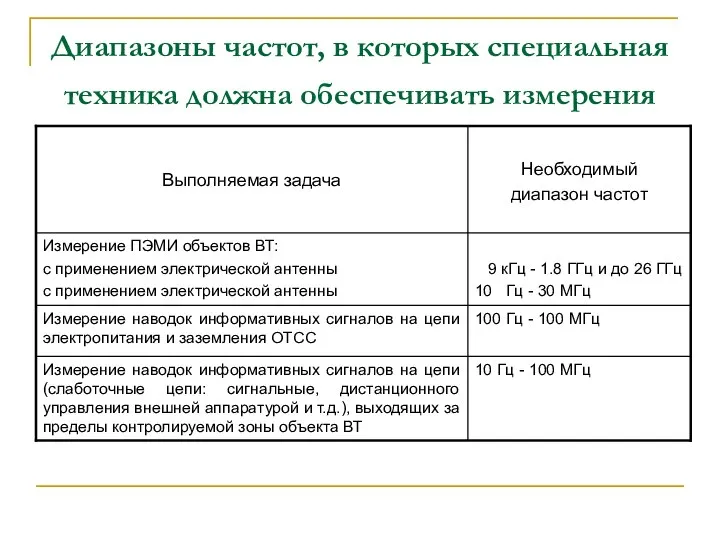

Презентация на тему Время и числовая информация (2 класс)  Диапазоны частот, в которых специальная техника должна обеспечивать измерения. Средства защиты информации

Диапазоны частот, в которых специальная техника должна обеспечивать измерения. Средства защиты информации Источники дохода от арбитража трафика

Источники дохода от арбитража трафика Машинное обучение

Машинное обучение Электронная вычислительная машина

Электронная вычислительная машина Представление цифровой информации в компьютере

Представление цифровой информации в компьютере Организация процесса конструирования

Организация процесса конструирования Понятие информации в теории Шеннона

Понятие информации в теории Шеннона Основы логики

Основы логики Десятичная система счисления

Десятичная система счисления Массив независимых дисков с избыточностью (RAID)

Массив независимых дисков с избыточностью (RAID) Информация для родителей. Безопасный интернет

Информация для родителей. Безопасный интернет Анализ проблемы и моделирование предметной области с использованием системного подхода

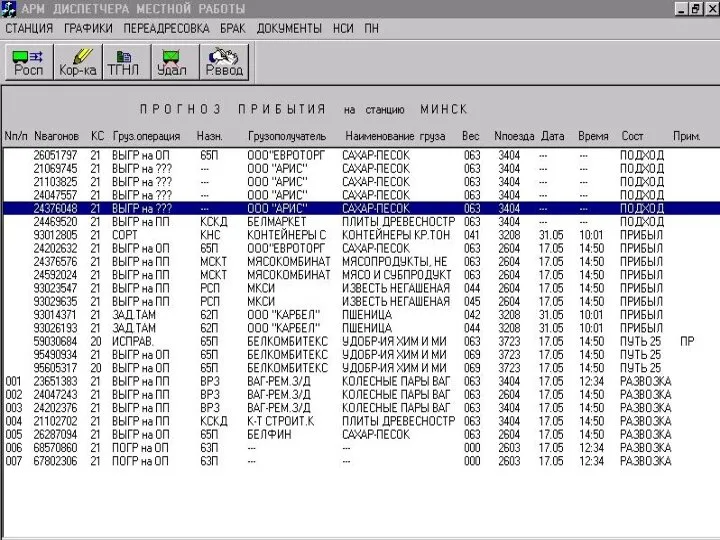

Анализ проблемы и моделирование предметной области с использованием системного подхода Описание и работа автоматизированной системы управления сортировочной станцией. Формы АРМ ДСЦМ

Описание и работа автоматизированной системы управления сортировочной станцией. Формы АРМ ДСЦМ Виды склеек

Виды склеек Устройство ПК

Устройство ПК Достижение целевого показателя

Достижение целевого показателя Начало 3 лабораторной. Часть 1: Рисование

Начало 3 лабораторной. Часть 1: Рисование Одномерные массивы

Одномерные массивы Skype. Позвони писателю

Skype. Позвони писателю Компьютерные сети. Тема 4

Компьютерные сети. Тема 4 Тест по табличному процесору Excel

Тест по табличному процесору Excel Текстовая информация. Ключевые слова

Текстовая информация. Ключевые слова Доработки применения КТРУ на версию 9.3

Доработки применения КТРУ на версию 9.3