Содержание

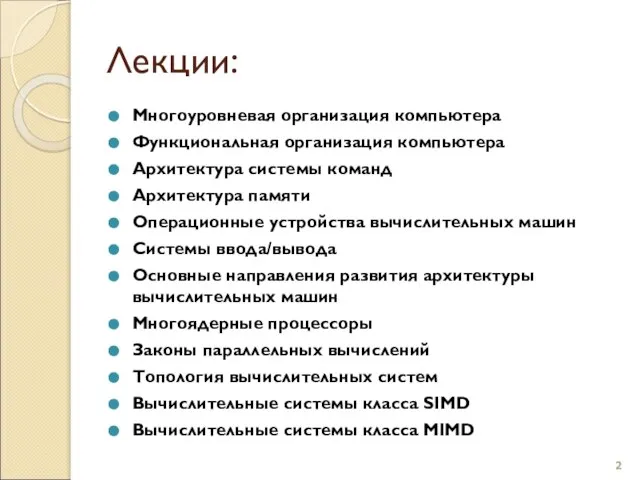

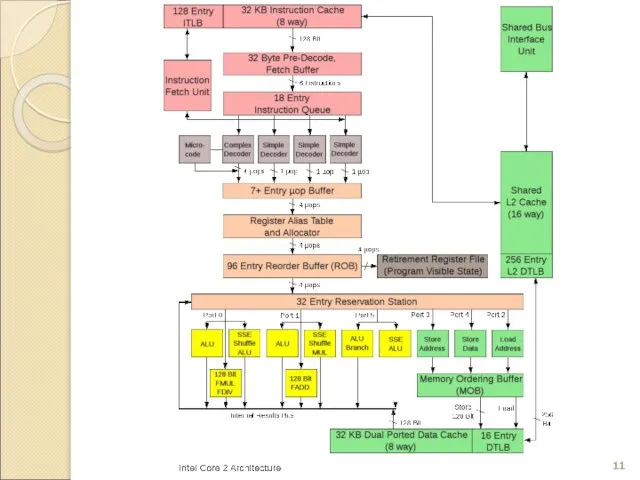

- 2. Лекции: Многоуровневая организация компьютера Функциональная организация компьютера Архитектура системы команд Архитектура памяти Операционные устройства вычислительных машин

- 3. Практикум: Арифметические основы вычислительных машин CISK и RISK-системы команд

- 4. Базовые принципы работы компьютера

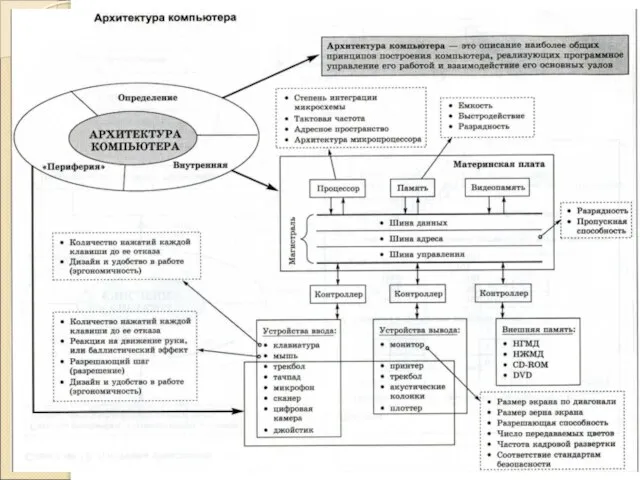

- 5. "Архитектура - это наиболее общие принципы построения ЭВМ, реализующие программное управление работой и взаимодействием основных ее

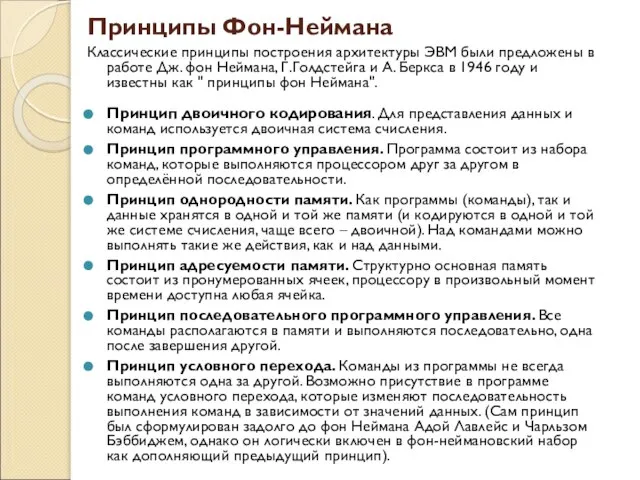

- 6. Принципы Фон-Неймана Классические принципы построения архитектуры ЭВМ были предложены в работе Дж. фон Неймана, Г.Голдстейга и

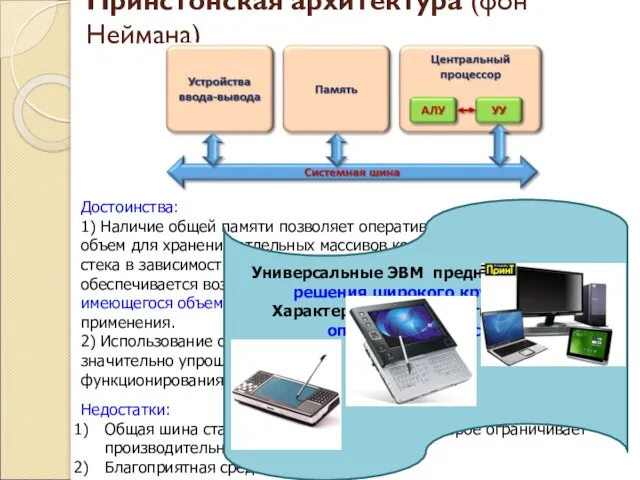

- 10. Принстонская архитектура (фон Неймана) Достоинства: 1) Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения

- 12. Гарвардская архитектура Недостатки: Большее число шин, сложнее реализовать Устройство управления Фиксированный объем памяти, выделенной для команд

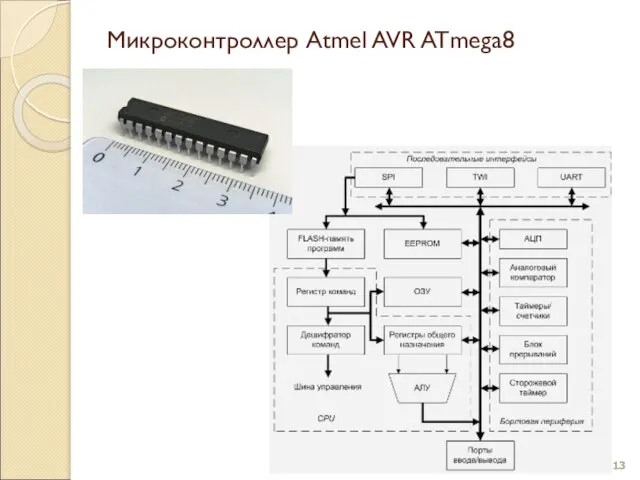

- 13. Микроконтроллер Atmel AVR ATmega8

- 14. Многоуровневая организация компьютера

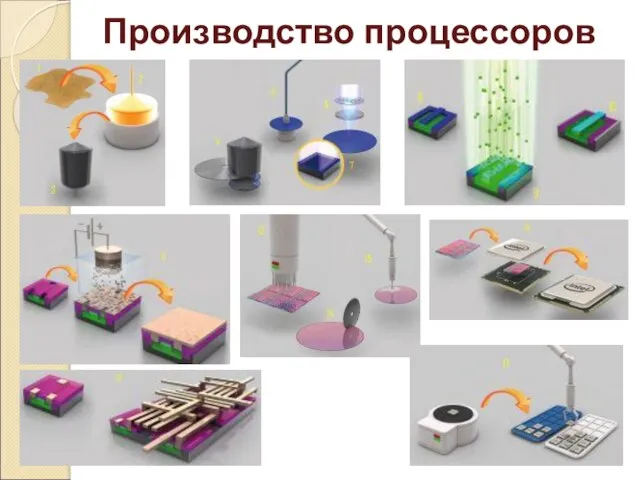

- 15. Производство процессоров

- 16. Архитектура системы команд компьютера

- 17. Архитектура системы команд как интерфейс между программным и аппаратным обеспечением Архитектура системы команд

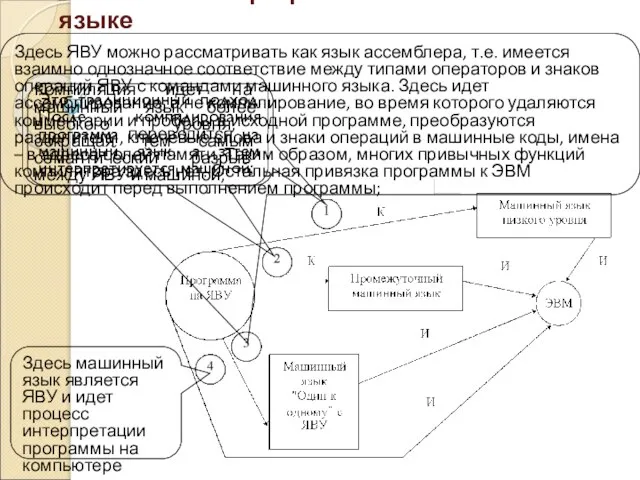

- 18. Соотношение программ на ЯВУ и машинном языке Здесь ЯВУ можно рассматривать как язык ассемблера, т.е. имеется

- 19. Требования ЯВУ к архитектуре ЭВМ : память состоит из набора дискретных именуемых переменных. ЯВУ наряду с

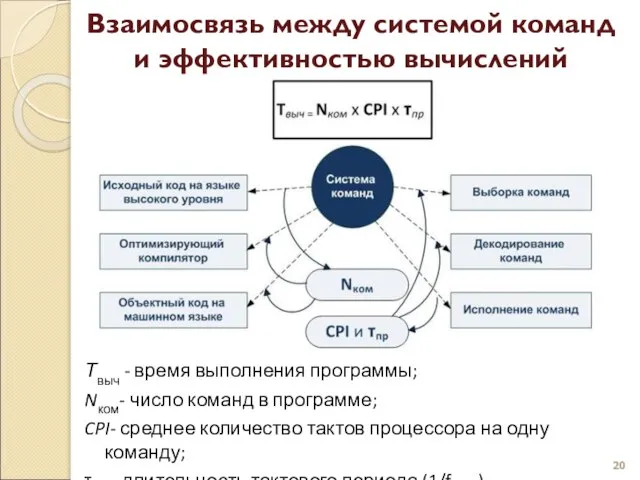

- 20. Взаимосвязь между системой команд и эффективностью вычислений Твыч - время выполнения программы; Nком- число команд в

- 21. Система команд вычислительной машины - полный перечень команд, которые способна выполнять данная ВМ. Архитектура системы команд

- 22. Архитектура системы команд (англ. instruction set architecture, ISA) — часть архитектуры компьютера, определяющая программируемую часть ядра

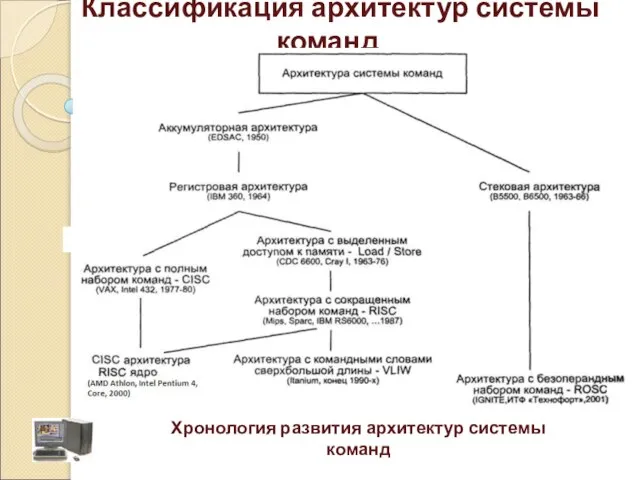

- 23. Хронология развития архитектур системы команд Классификация архитектур системы команд

- 24. Классификация архитектур системы команд По составу и сложности команд (CISC, RISC, VLIW, ROSC) По типу выполняемых

- 25. Классификация по составу и сложности команд архитектура с полным набором команд: CISC (Complex Instruction Set Computer);

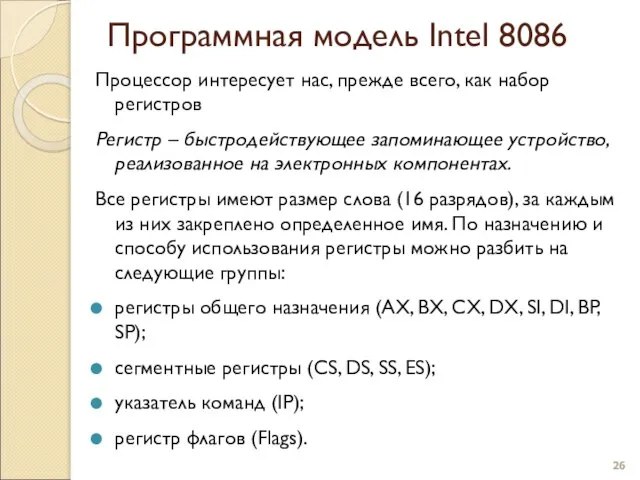

- 26. Программная модель Intel 8086 Процессор интересует нас, прежде всего, как набор регистров Регистр – быстродействующее запоминающее

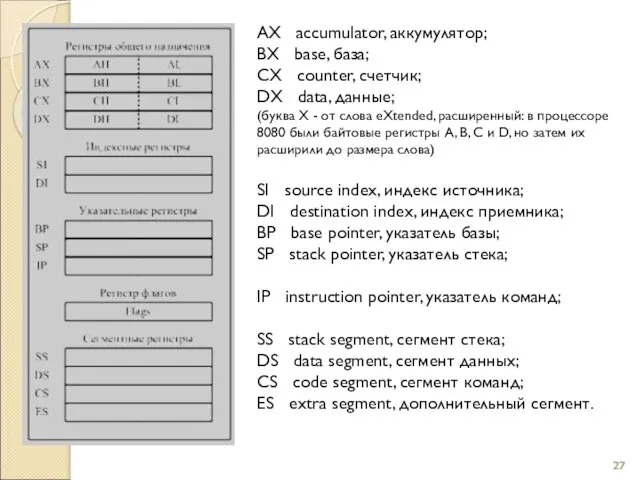

- 27. AX accumulator, аккумулятор; BX base, база; CX counter, счетчик; DX data, данные; (буква X - от

- 28. Сегментные регистры Указатель команд

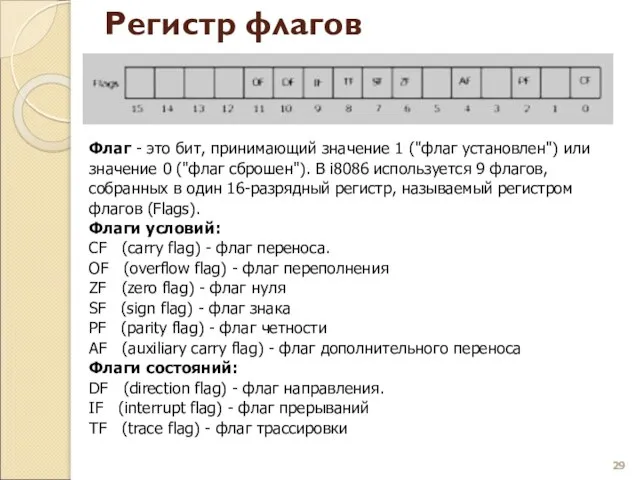

- 29. Регистр флагов Флаг - это бит, принимающий значение 1 ("флаг установлен") или значение 0 ("флаг сброшен").

- 30. Форматы команд Длина команды Разрядность полей команды Количество адресов в команде Способы адресации операндов Способы адресации

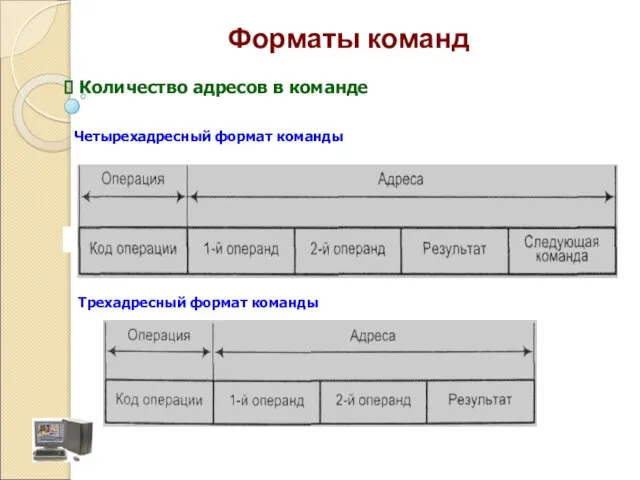

- 31. Четырехадресный формат команды Трехадресный формат команды Количество адресов в команде Форматы команд

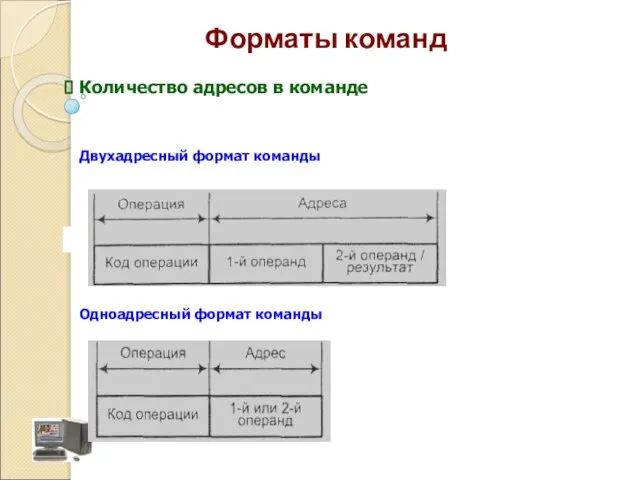

- 32. Двухадресный формат команды Одноадресный формат команды Количество адресов в команде Форматы команд

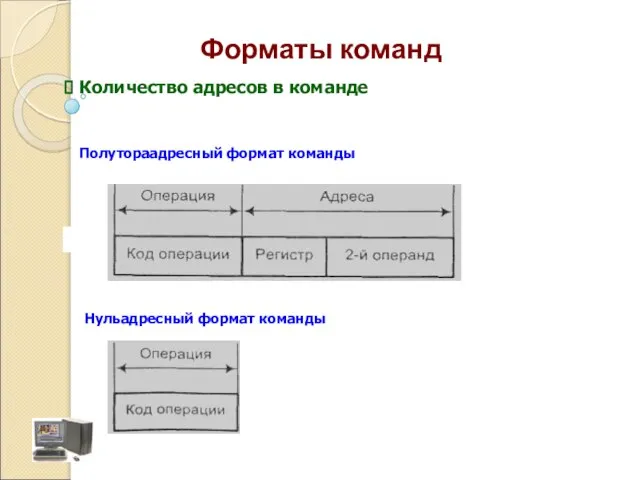

- 33. Полутораадресный формат команды Количество адресов в команде Нульадресный формат команды Форматы команд

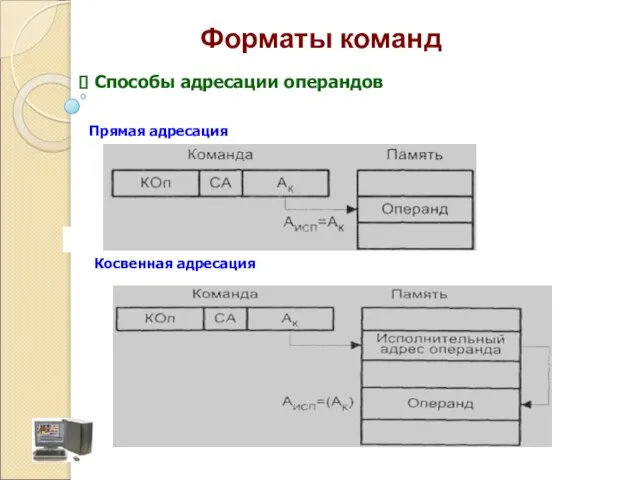

- 34. Прямая адресация Косвенная адресация Способы адресации операндов Форматы команд

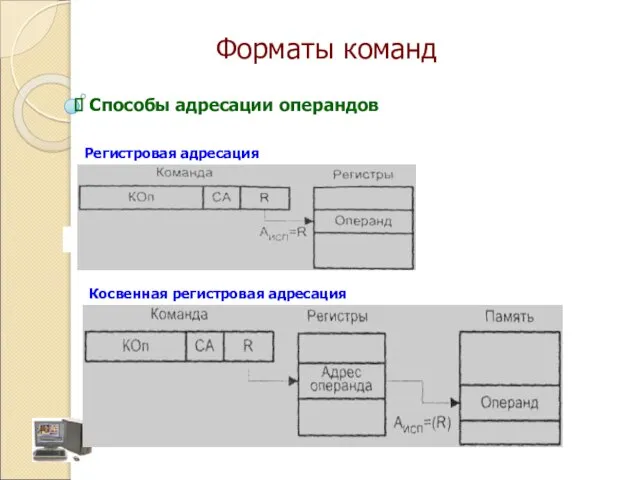

- 35. Регистровая адресация Косвенная регистровая адресация Способы адресации операндов Форматы команд

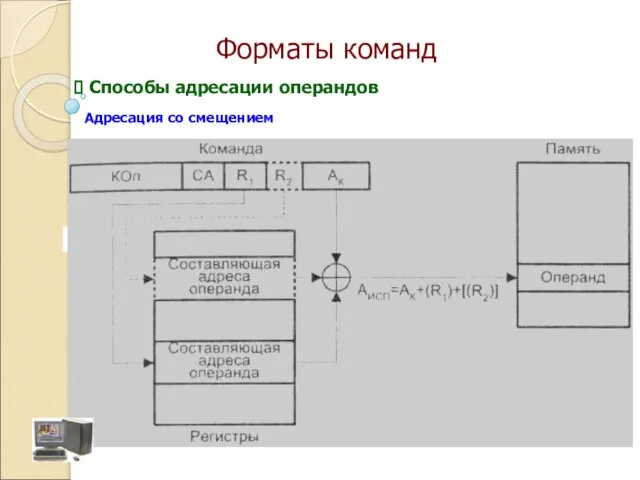

- 36. Адресация со смещением Способы адресации операндов Форматы команд

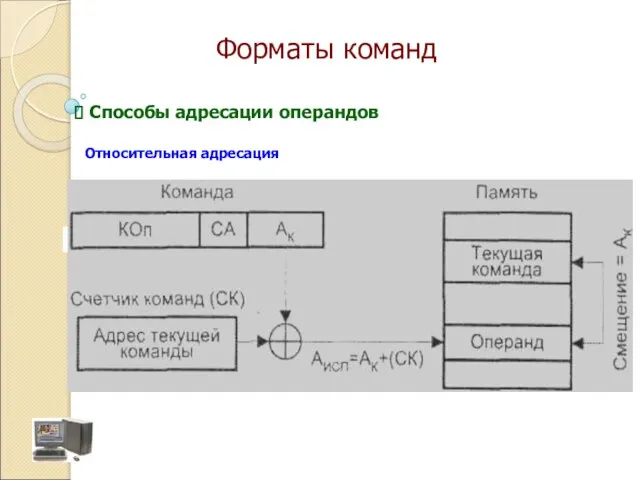

- 37. Относительная адресация Способы адресации операндов Форматы команд

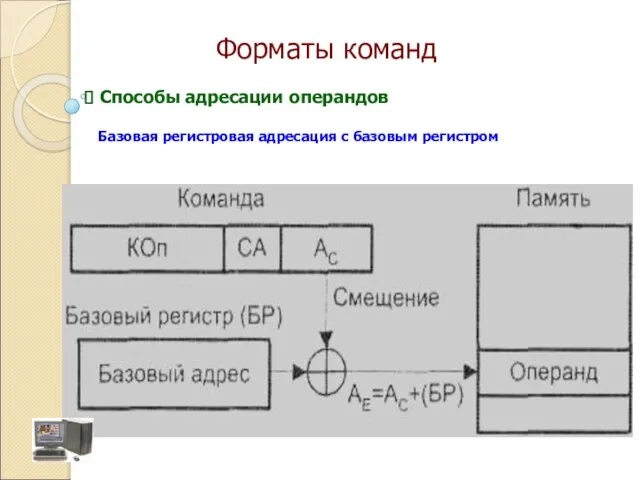

- 38. Базовая регистровая адресация с базовым регистром Способы адресации операндов Форматы команд

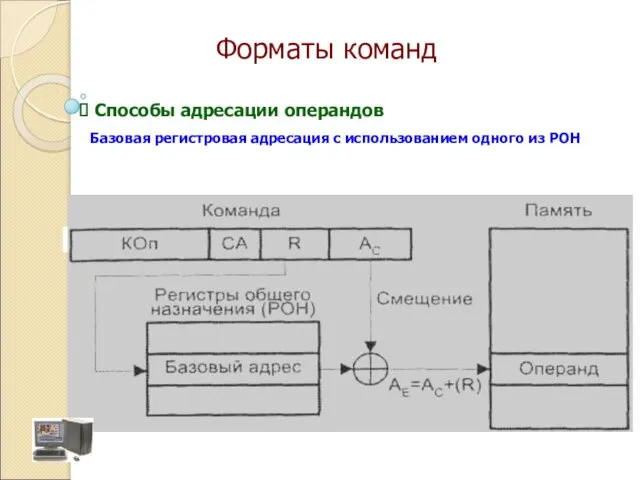

- 39. Способы адресации операндов Базовая регистровая адресация с использованием одного из РОН Форматы команд

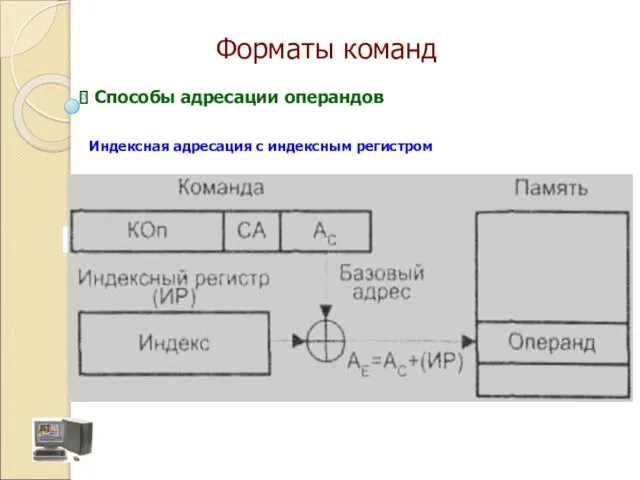

- 40. Индексная адресация с индексным регистром Способы адресации операндов Форматы команд

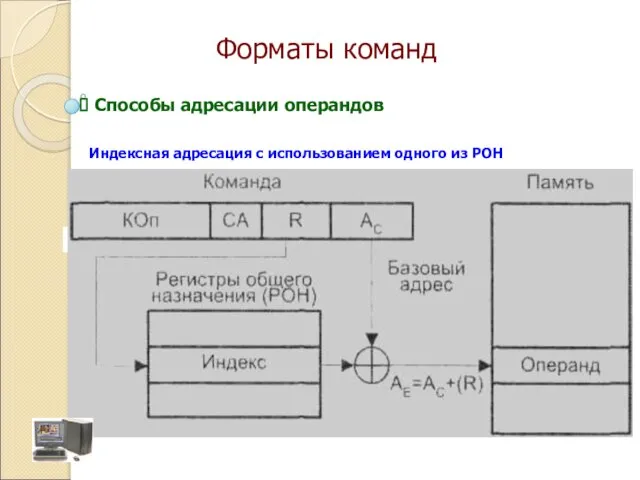

- 41. Индексная адресация с использованием одного из РОН Способы адресации операндов Форматы команд

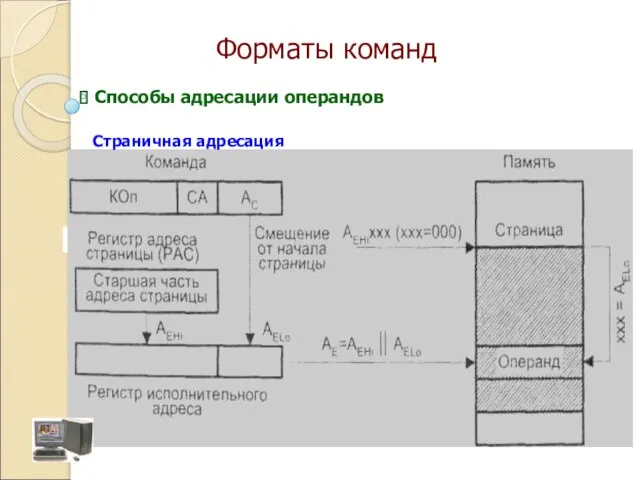

- 42. Страничная адресация Способы адресации операндов Форматы команд

- 43. CISC архитектура команд большое количество машинных команд, часть из которых аппаратно реализуют сложные операторы ЯВУ; наличие

- 44. Достоинства: Система команд процессоров с CISC–архитектурой может содержать несколько сотен команд разного формата (от 1 до

- 45. RISC архитектура команд каждая команда независимо от ее типа выполняется за один машинный цикл, длительность которого

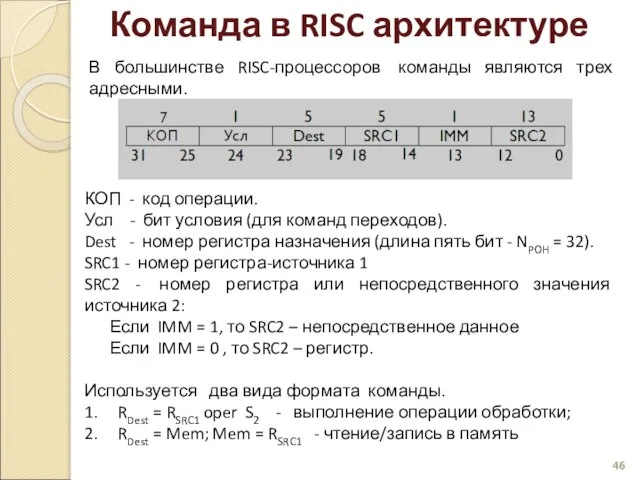

- 46. КОП - код операции. Усл - бит условия (для команд переходов). Dest - номер регистра назначения

- 47. Достоинства: Повышение производительности обработки программ вычислительных задач. Благодаря использованию простых команд и минимума их форматов сокращается

- 48. Недостатки: Нарушение основных принципов программирования: минимум длины исполняемого кода программы снижение семантического разрыва между исходным описанием

- 49. В последних микропроцессорах фирмы Intel и AMD широко используются идеи, свойственные RISC-архитектуре, начиная с Intel Pentium

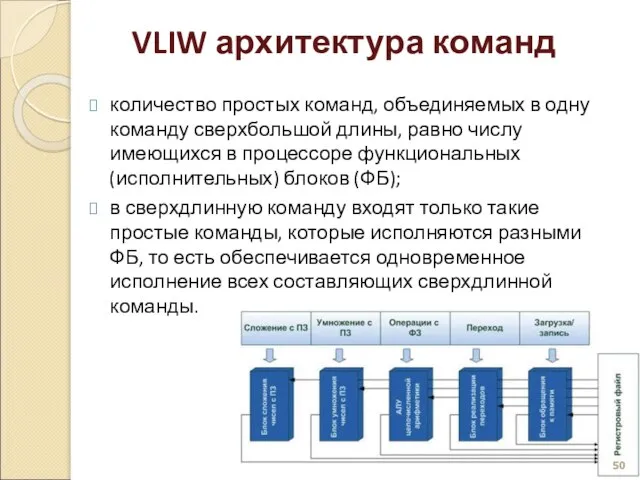

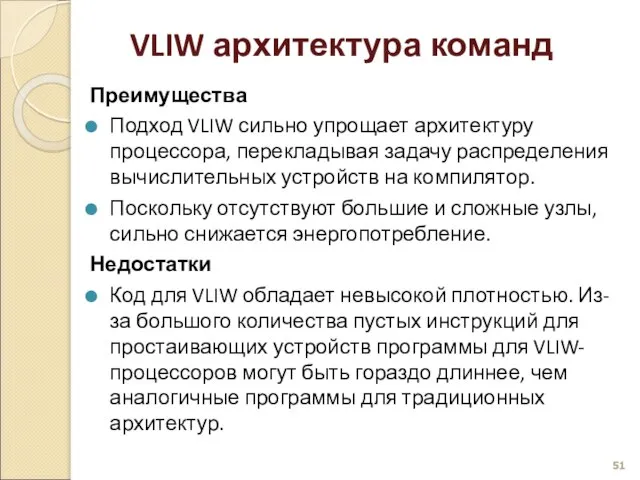

- 50. VLIW архитектура команд количество простых команд, объединяемых в одну команду сверхбольшой длины, равно числу имеющихся в

- 51. VLIW архитектура команд Преимущества Подход VLIW сильно упрощает архитектуру процессора, перекладывая задачу распределения вычислительных устройств на

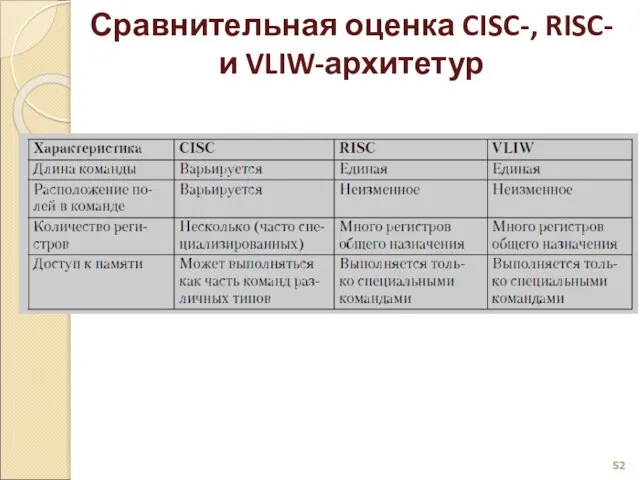

- 52. Сравнительная оценка CISC-, RISC- и VLIW-архитетур

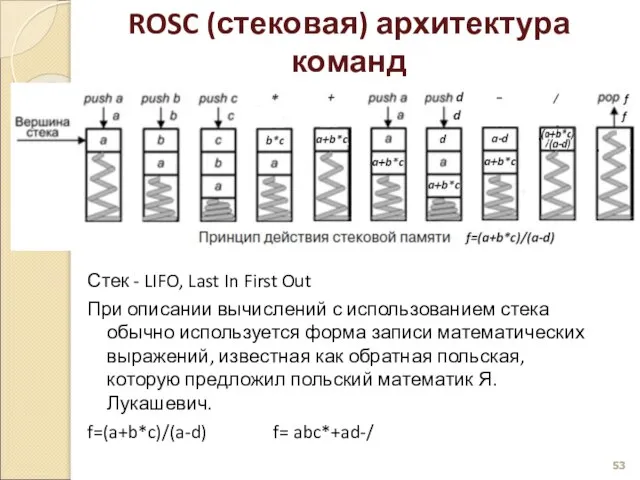

- 53. ROSC (стековая) архитектура команд Стек - LIFO, Last In First Out При описании вычислений с использованием

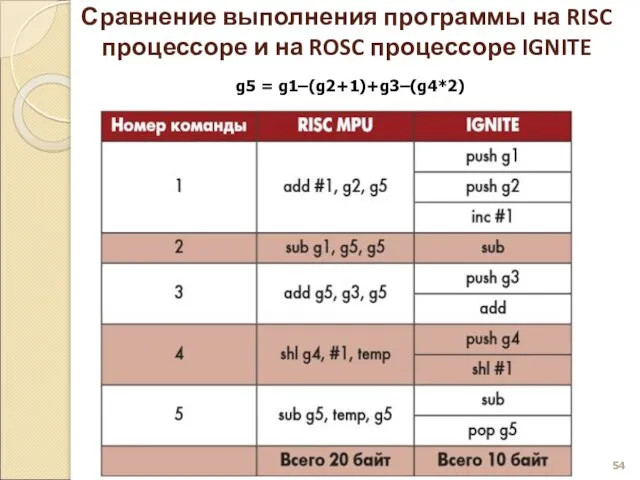

- 54. Сравнение выполнения программы на RISC процессоре и на ROSC процессоре IGNITE g5 = g1–(g2+1)+g3–(g4*2)

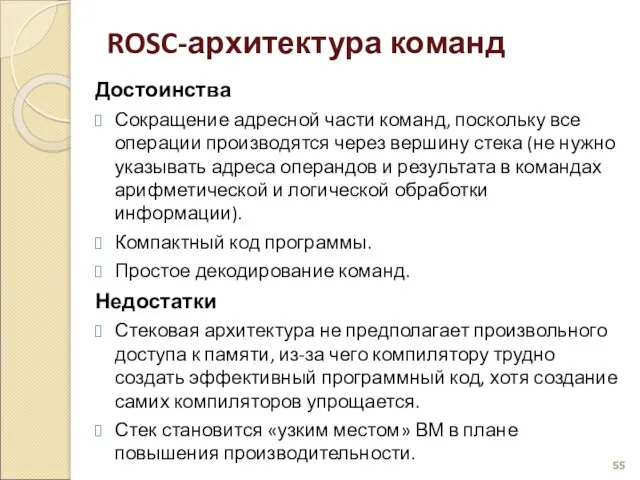

- 55. Достоинства Сокращение адресной части команд, поскольку все операции производятся через вершину стека (не нужно указывать адреса

- 56. Классификация по месту хранения операндов стековая; аккумуляторная; регистровая; с выделенным доступом к памяти.

- 57. Стековая архитектура

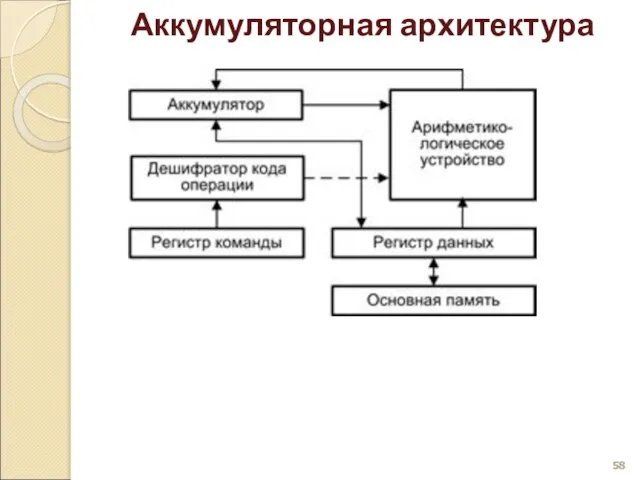

- 58. Аккумуляторная архитектура

- 59. Регистровая архитектура

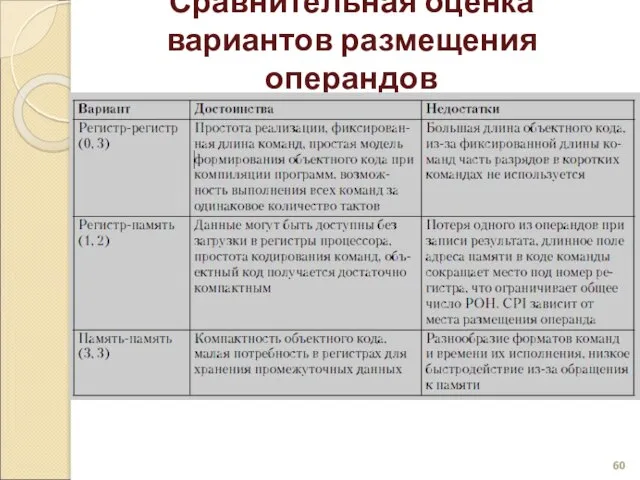

- 60. Сравнительная оценка вариантов размещения операндов

- 61. Архитектура с выделенным доступом к памяти

- 62. Классификация данных

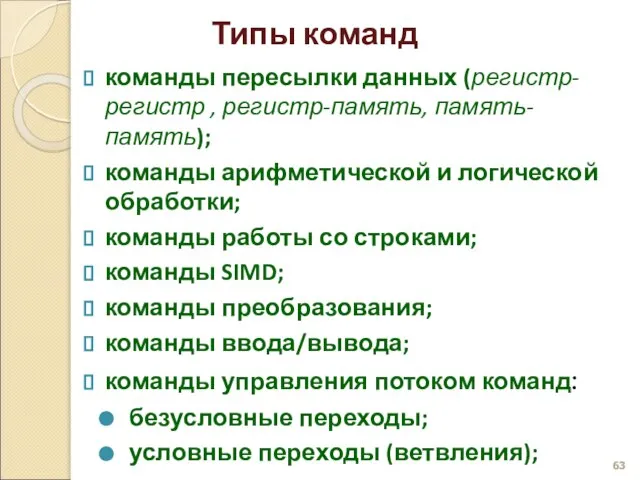

- 63. Типы команд команды пересылки данных (регистр-регистр , регистр-память, память-память); команды арифметической и логической обработки; команды работы

- 64. Тип выполняемых операций Команды пересылки и загрузки данных (память – регистр) Команды арифметической и логической обработки

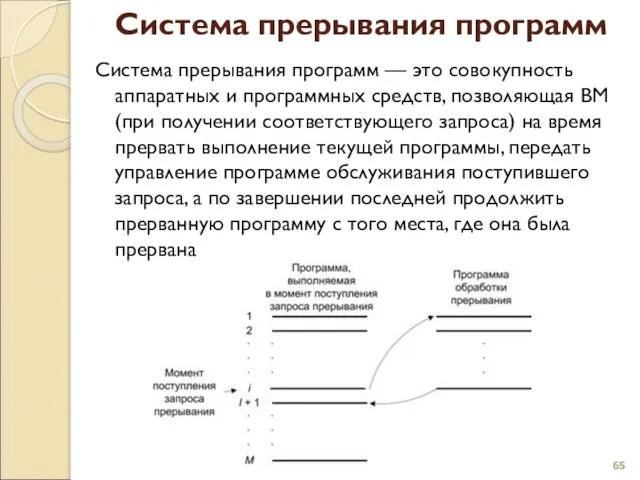

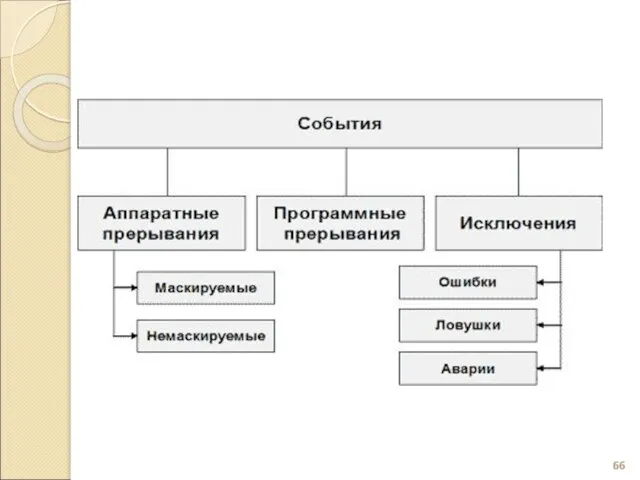

- 65. Система прерывания программ Система прерывания программ — это совокупность аппаратных и программных средств, позволяющая ВМ (при

- 67. Цикл команды с учетом прерываний 1. Установка запрета на прием запросов прерывания. 2. Сохранение всей информации

- 68. Характеристики систем прерывания время реакции TР — время между появлением запроса прерывания и началом выполнения первой

- 69. С позиций глубины прерывания можно рассматривать три варианта СПП: СПП способна воспринимать только один запрос; глубина

- 70. временная диаграмма процесса прерывания

- 71. Допустимые моменты прерывания программ Метод помеченного оператора (метод опорных точек) – наличие в коде команд специального

- 72. Дисциплины обслуживания прерываний P = pn–1 … p1 p0 - код прерывания (pi – запрос от

- 73. Идентификация источника запроса прерывания ⇐ обзорная СПП СПП с векторными прерываниями ⇒

- 74. Система приоритетов Система приоритетов позволяет определить: имеет ли право поступивший запрос прерывания прервать выполняемую в данный

- 75. Обслуживание прерывания

- 77. Скачать презентацию

Развитие визуального восприятия. Воображение. Правила создания образа

Развитие визуального восприятия. Воображение. Правила создания образа Весенний вечер

Весенний вечер Вводные слова. Сочинение-рассуждение

Вводные слова. Сочинение-рассуждение Бесполое размножение

Бесполое размножение Pretty Little Liars

Pretty Little Liars Рак печени

Рак печени  Венгрия

Венгрия РАЗВИТИЕ ТЕХНОЛОГИЙ ПРОВЕДЕНИЯ МЕЖРЕГИОНАЛЬНЫХ СДЕЛОК

РАЗВИТИЕ ТЕХНОЛОГИЙ ПРОВЕДЕНИЯ МЕЖРЕГИОНАЛЬНЫХ СДЕЛОК Устный счёт на уроке математики в 1 классе

Устный счёт на уроке математики в 1 классе Разделка рыбы и приготовление полуфабрикатов из рыбы

Разделка рыбы и приготовление полуфабрикатов из рыбы СOВМЕСТНЫЙ АНАЛИЗ ПАЛЕОХРОНОЛОГИЙ ПРИБАЙКАЛЬЯ

СOВМЕСТНЫЙ АНАЛИЗ ПАЛЕОХРОНОЛОГИЙ ПРИБАЙКАЛЬЯ Что это за листья (1 класс)

Что это за листья (1 класс) Гербы и эмблемы. 5 класс

Гербы и эмблемы. 5 класс Развитие личности обучающихся учреждения дополнительного образования детей и молодежи средствами социокультурной деятельности

Развитие личности обучающихся учреждения дополнительного образования детей и молодежи средствами социокультурной деятельности Устав НЭПК «Союз «Атамекен» в новой редакции Астана 2012 г.

Устав НЭПК «Союз «Атамекен» в новой редакции Астана 2012 г. Презентация на тему Астероиды и кометы

Презентация на тему Астероиды и кометы Интересный тест. Тест Локус контроля

Интересный тест. Тест Локус контроля Презентация на тему Живопись России 18 века

Презентация на тему Живопись России 18 века Отчёт по производственной практикеДля получения рабочей профессиипрофессия 30.20 «Автомеханик»07.06 – 27.06.12 года

Отчёт по производственной практикеДля получения рабочей профессиипрофессия 30.20 «Автомеханик»07.06 – 27.06.12 года Падежные окончания

Падежные окончания Как снять уникальный видеоролик. Советы по подготовке к съёмке

Как снять уникальный видеоролик. Советы по подготовке к съёмке Урок «Заботы и любви»

Урок «Заботы и любви» Advert

Advert Презентация на тему Звуковые волны в различных средах

Презентация на тему Звуковые волны в различных средах Новогодний бал-маскарад«В ночь перед рождеством!»

Новогодний бал-маскарад«В ночь перед рождеством!» Положение о наставничестве АО ОДК-СТАР

Положение о наставничестве АО ОДК-СТАР Персональное решение. Профессиональный аутсорсинг персонала в г. Сыктывкаре

Персональное решение. Профессиональный аутсорсинг персонала в г. Сыктывкаре Seasons of the year

Seasons of the year