Содержание

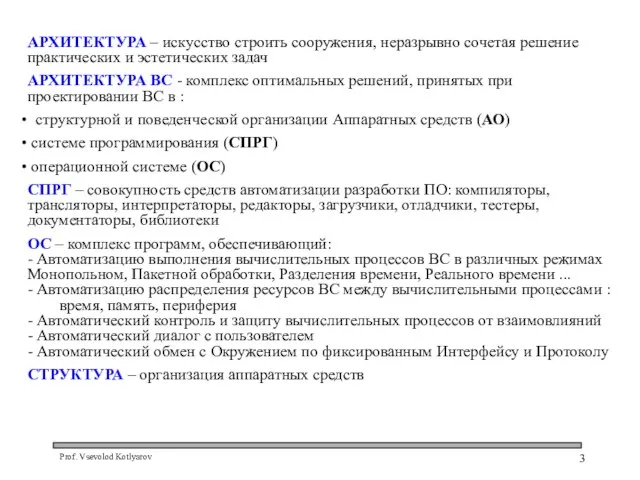

- 3. АРХИТЕКТУРА – искусство строить сооружения, неразрывно сочетая решение практических и эстетических задач АРХИТЕКТУРА ВС - комплекс

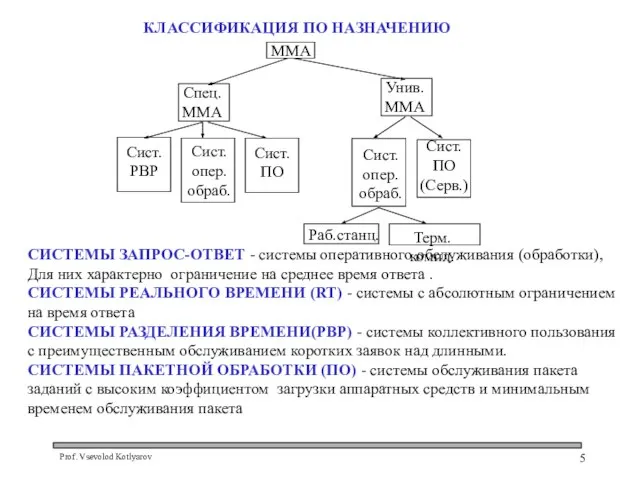

- 5. КЛАССИФИКАЦИЯ ПО НАЗНАЧЕНИЮ СИСТЕМЫ ЗАПРОС-ОТВЕТ - системы оперативного обслуживания (обработки), Для них характерно ограничение на среднее

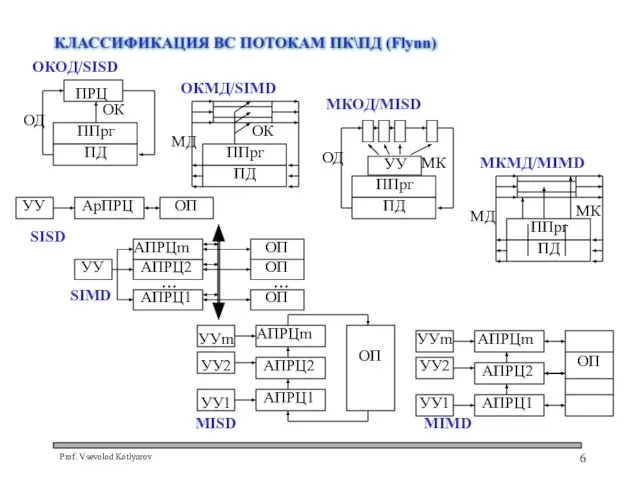

- 6. КЛАССИФИКАЦИЯ ВС ПОТОКАМ ПК\ПД (Flynn)

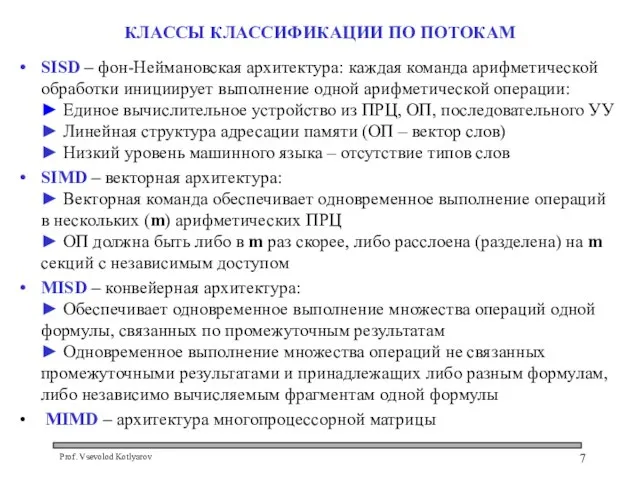

- 7. КЛАССЫ КЛАССИФИКАЦИИ ПО ПОТОКАМ SISD – фон-Неймановская архитектура: каждая команда арифметической обработки инициирует выполнение одной арифметической

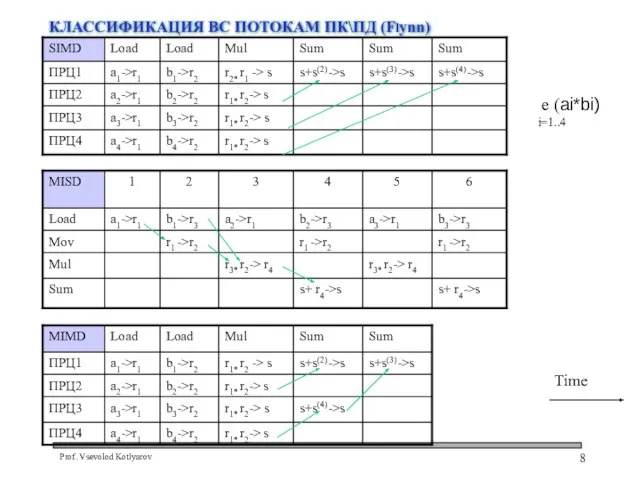

- 8. КЛАССИФИКАЦИЯ ВС ПОТОКАМ ПК\ПД (Flynn) Time е (ai*bi) i=1..4

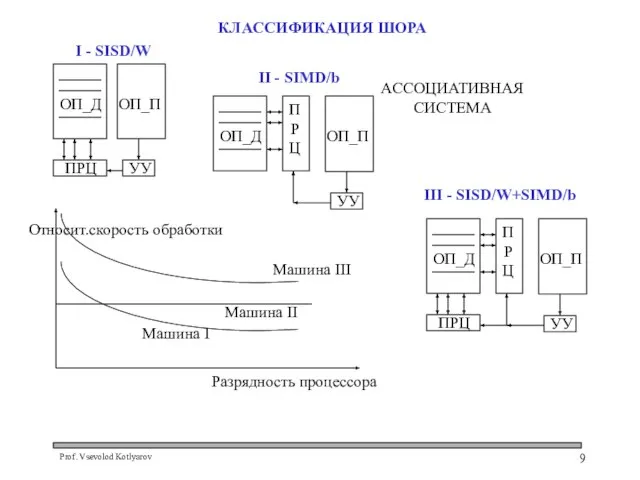

- 9. КЛАССИФИКАЦИЯ ШОРА

- 10. КЛАССЫ КЛАССИФИКАЦИИ ШОРА I – обычная ВМ с последовательной обработкой слов и параллельной обработкой разрядов слов

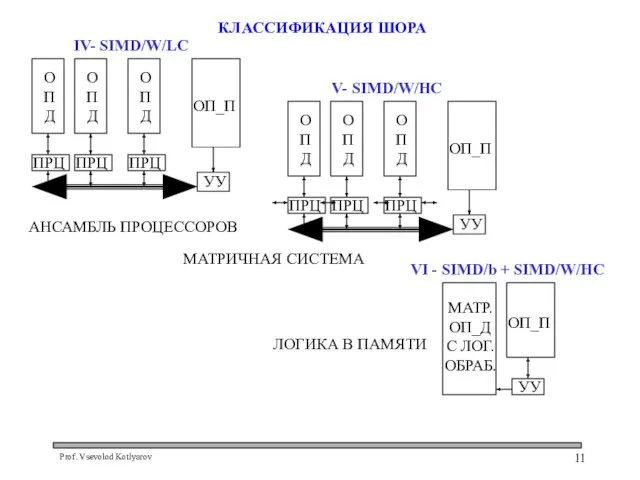

- 11. КЛАССИФИКАЦИЯ ШОРА

- 12. КЛАССЫ КЛАССИФИКАЦИИ ШОРА IV – ансамбль ПРЦ получается путем интеграции модулей машины I в единую вычислительную

- 13. КЛАССИФИКАЦИЯ ПО СТЕПЕНИ ПАРАЛЛЕЛИЗМА ОБРАБОТКИ 1 2 3 4 5 6 7 I-Обычн.ПРЦ II-Одноразр.ПРЦ III-Ансамбль ПРЦ

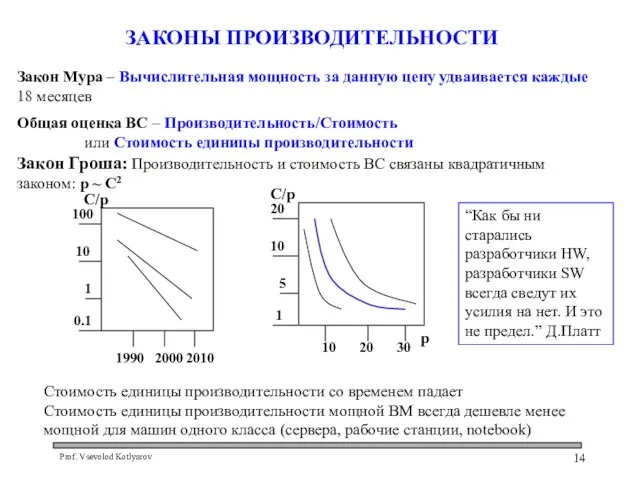

- 14. Закон Гроша: Производительность и стоимость ВС связаны квадратичным законом: p ~ C2 C/p 1990 2000 Закон

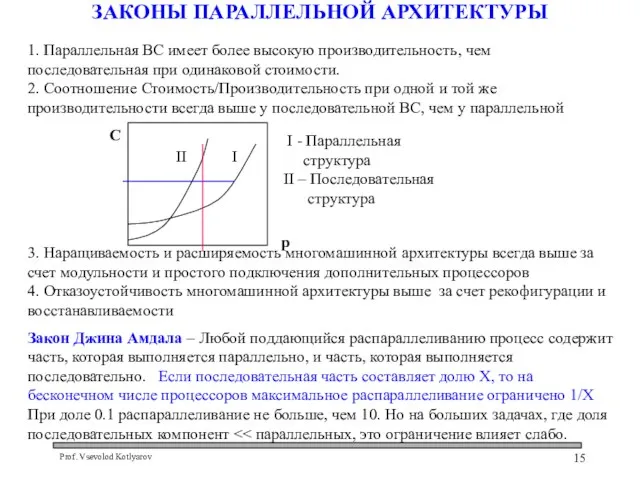

- 15. ЗАКОНЫ ПАРАЛЛЕЛЬНОЙ АРХИТЕКТУРЫ 1. Параллельная ВС имеет более высокую производительность, чем последовательная при одинаковой стоимости. 2.

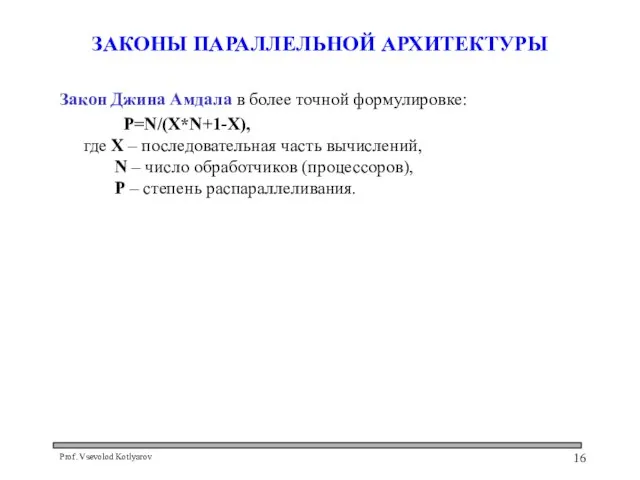

- 16. ЗАКОНЫ ПАРАЛЛЕЛЬНОЙ АРХИТЕКТУРЫ Закон Джина Амдала в более точной формулировке: P=N/(X*N+1-X), где X – последовательная часть

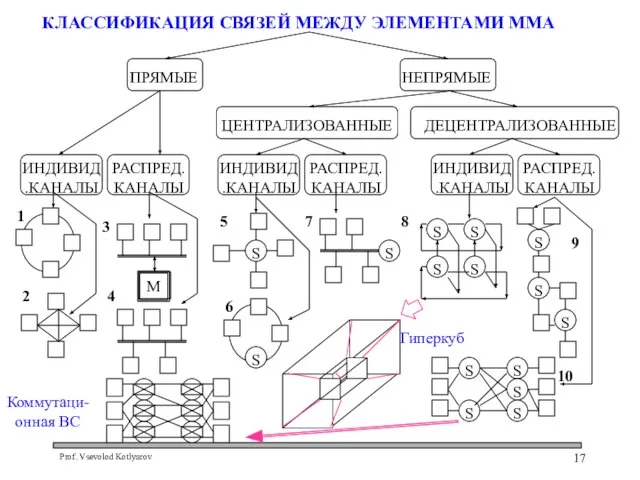

- 17. КЛАССИФИКАЦИЯ СВЯЗЕЙ МЕЖДУ ЭЛЕМЕНТАМИ ММА

- 18. КЛАССИФИКАЦИЯ СВЯЗЕЙ МЕЖДУ ЭЛЕМЕНТАМИ ММА

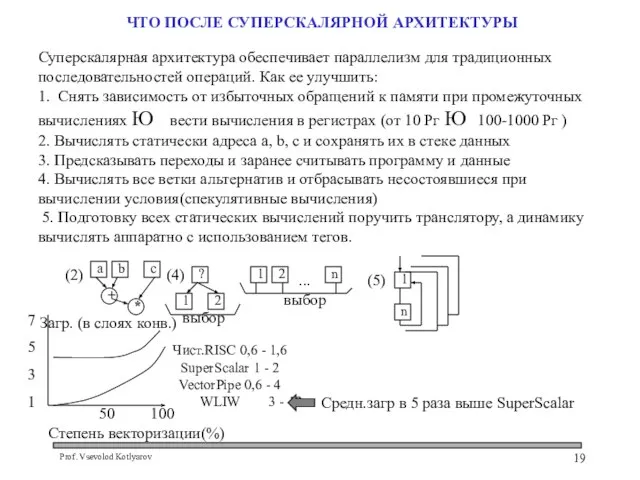

- 19. ЧТО ПОСЛЕ СУПЕРСКАЛЯРНОЙ АРХИТЕКТУРЫ Суперскалярная архитектура обеспечивает параллелизм для традиционных последовательностей операций. Как ее улучшить: 1.

- 21. Скачать презентацию

Presentation Title

Presentation Title  Насколько революционным был промышленный переворот

Насколько революционным был промышленный переворот Сервис безопасности

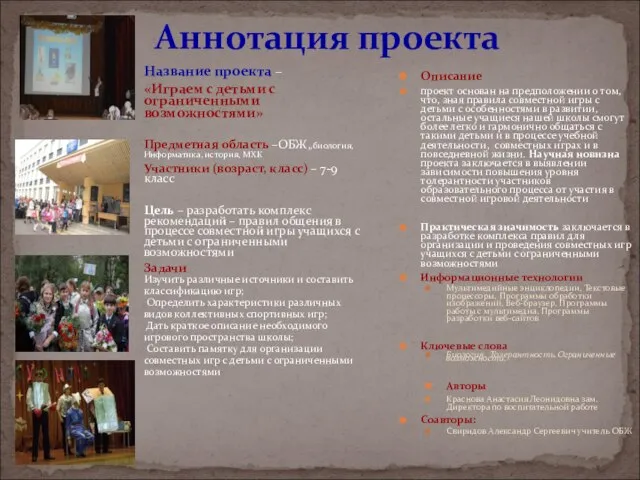

Сервис безопасности Аннотация проекта

Аннотация проекта Лучшая региональная практика

Лучшая региональная практика Украшение блюд

Украшение блюд Предмет астрономии.Астрономия в д ревности.Астрология.

Предмет астрономии.Астрономия в д ревности.Астрология. THE PRICE of FAME

THE PRICE of FAME Сучасні технології в обслуговуванні людей із обмеженнями зору Олеся Шкурат, Центр інформаційних ресурсів Посольства США в Украї

Сучасні технології в обслуговуванні людей із обмеженнями зору Олеся Шкурат, Центр інформаційних ресурсів Посольства США в Украї Айал Толстяков. Персонализация. Herbalife

Айал Толстяков. Персонализация. Herbalife ВЫПОЛНИЛА СТУДЕНТКА 42 ГРУППЫ, СЕСТРИНСКОГО ДЕЛА КУНДОЗЕРОВА

ВЫПОЛНИЛА СТУДЕНТКА 42 ГРУППЫ, СЕСТРИНСКОГО ДЕЛА КУНДОЗЕРОВА Счастье - это весна в сердце

Счастье - это весна в сердце BGP протокол маршрутизации

BGP протокол маршрутизации  Учеба в Великобритании

Учеба в Великобритании Педагогическая ситуация и приемы ее решения

Педагогическая ситуация и приемы ее решения Первая печатная книга на Руси

Первая печатная книга на Руси Профильный лагерь Старт в IT

Профильный лагерь Старт в IT Проектный метод в обучении младших школьников как средство формирования учебной мотивации в рамках системно-деятельностного под

Проектный метод в обучении младших школьников как средство формирования учебной мотивации в рамках системно-деятельностного под Рамы. Лекция 13

Рамы. Лекция 13 Особенности познавательных процессов детей с нарушениями речи

Особенности познавательных процессов детей с нарушениями речи Слова, друзья, живая сила. В них сила правды и добра.

Слова, друзья, живая сила. В них сила правды и добра. 8_09

8_09 Древняя Русь

Древняя Русь Лёгкая атлетика, бег, 11 класс

Лёгкая атлетика, бег, 11 класс Владение морфологическими нормами

Владение морфологическими нормами «И пальцы просятся к перу...» (модель организации творческой работы с текстом)

«И пальцы просятся к перу...» (модель организации творческой работы с текстом) Итоговое сочинение (изложение) как условие допуска к ГИА

Итоговое сочинение (изложение) как условие допуска к ГИА Презентация на тему Типичные ошибки ЕГЭ русский язык

Презентация на тему Типичные ошибки ЕГЭ русский язык