Слайд 2Kratak opis karakteristika procesora

Dizajn trajao od 1976. do 1978. godine, kada je

lansiran

16 bitova

frekvencija od 5 do 10 MHz

29000 tranzistora

Širina memorijske magistrale 20 bitova

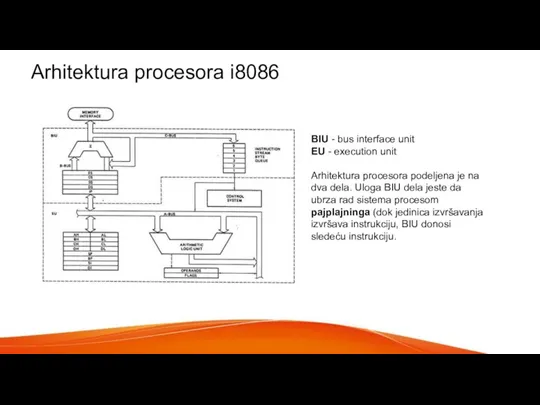

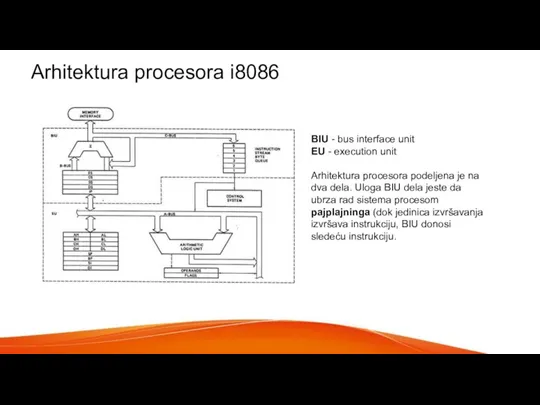

Слайд 3Arhitektura procesora i8086

BIU - bus interface unit

EU - execution unit

Arhitektura procesora podeljena

je na dva dela. Uloga BIU dela jeste da ubrza rad sistema procesom pajplajninga (dok jedinica izvršavanja izvršava instrukciju, BIU donosi sledeću instrukciju.

Слайд 4Arhitektura procesora i8086 - registri opšte namene

AX - accumulator register (AH

/ AL).

BX - base address register (BH / BL).

CX - count register (CH / CL).

DX - data register (DH / DL).

Слайд 5Arhitektura procesora i8086 - ofset registri

SI - source index register.

DI - destination index register.

BP - base pointer.

SP - stack pointer.

Слайд 6Arhitektura procesora i8086 - segmentni registri

CS - pokazuje na segment koji

sadrži kod programa (code segment)

DS - pokazuje na segment gde su promenljive definisane (data segment)

ES - segment opšte namene, za proizvoljno korišćenje, (extra segment)

SS - pokazuje na stek segment (stack segment)

Слайд 7Arhitektura i8086

Instruction System Byte Queue (Prefetch Queue) jeste bafer za nadolazeće

instrukcije koje BIU donosi. Ona je veličine 6 bajtova (ne 6 instrukcija, instrukcije mogu biti različiti veličine)

Procesor čeka da se isprazne 2 bajta iz ovog reda pre nego što donese nove (procesor je 16-obitni)

Red se invalidira ukoliko dođe do skoka

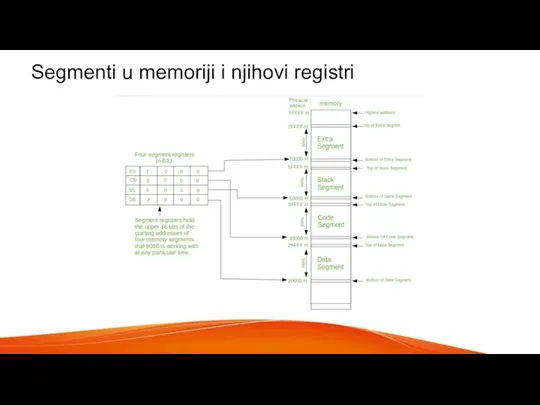

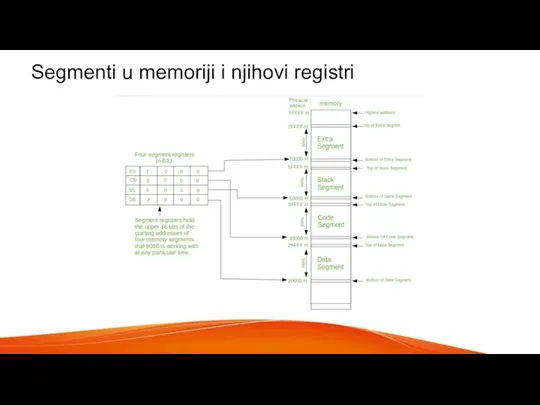

Слайд 8Segmenti u memoriji i njihovi registri

Слайд 9Segmenti u memoriji i njihovi registri

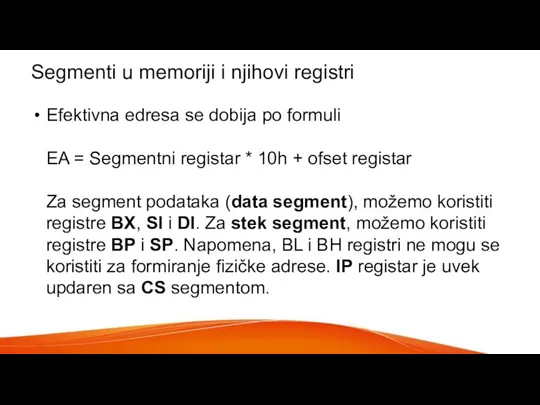

Efektivna edresa se dobija po formuli

EA

= Segmentni registar * 10h + ofset registar

Za segment podataka (data segment), možemo koristiti registre BX, SI i DI. Za stek segment, možemo koristiti registre BP i SP. Napomena, BL i BH registri ne mogu se koristiti za formiranje fizičke adrese. IP registar je uvek updaren sa CS segmentom.

Слайд 10Segmenti u memoriji i njihovi registri

Generalno, u asembleru možemo da pristupamo različitim

lokacijama u memoriji. Realnu fizičku adresu kojoj pristupamo računa sam procesor, a mi dajemo ofset

[BX + SI + 5h] --> DS * 10h + BX + SI + 5h

[DI + 16h] --> DS * 10h + DI + 16h

....

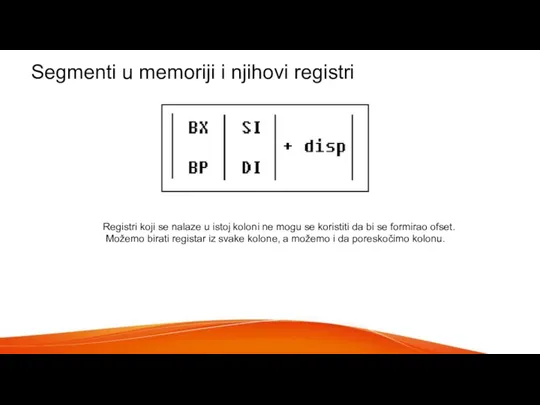

Слайд 11Segmenti u memoriji i njihovi registri

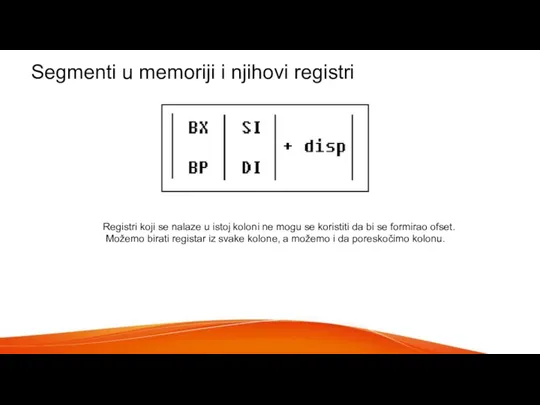

Registri koji se nalaze u istoj

koloni ne mogu se koristiti da bi se formirao ofset.

Možemo birati registar iz svake kolone, a možemo i da poreskočimo kolonu.

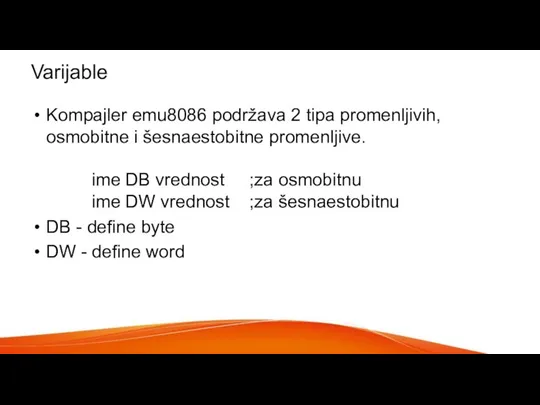

Слайд 12Varijable

Kompajler emu8086 podržava 2 tipa promenljivih, osmobitne i šesnaestobitne promenljive.

ime DB

vrednost ;za osmobitnu

ime DW vrednost ;za šesnaestobitnu

DB - define byte

DW - define word

Слайд 13Varijable

Promenljivoj se ne mora dati ime. U tom slučaju, ona će dobiti

adresu, i to je jedini način na koji može da joj se pristupi. Vrednost promeljive može biti zapisana u proizvoljnom sistemu, ili može biti ? ukoliko nije inicijalizovana.

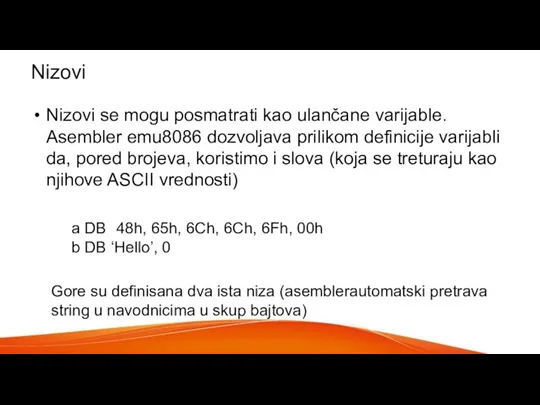

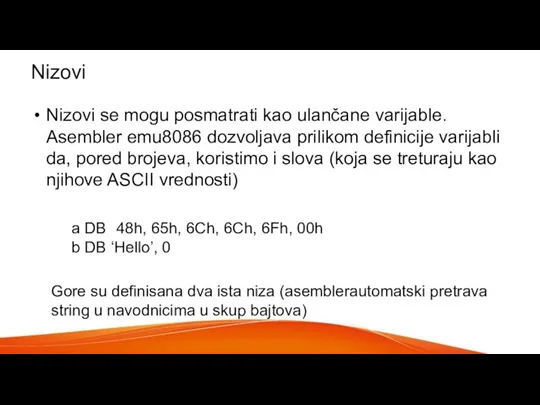

Слайд 14Nizovi

Nizovi se mogu posmatrati kao ulančane varijable. Asembler emu8086 dozvoljava prilikom definicije

varijabli da, pored brojeva, koristimo i slova (koja se treturaju kao njihove ASCII vrednosti)

a DB 48h, 65h, 6Ch, 6Ch, 6Fh, 00h

b DB ‘Hello’, 0

Gore su definisana dva ista niza (asemblerautomatski pretrava string u navodnicima u skup bajtova)

Слайд 15Nizovi

Elementima niza može se pristupati na standardan način, preko uglastih zagrada

a[5]

Pored toga,

moguće je koristiti i registre BX, SI, DI i BP da pristupimo elementima

MOV SI, 5

a[SI]

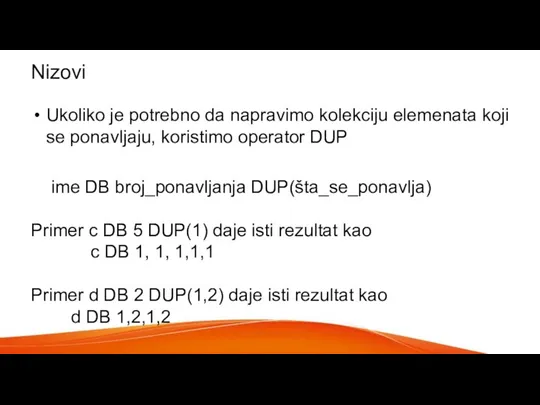

Слайд 16Nizovi

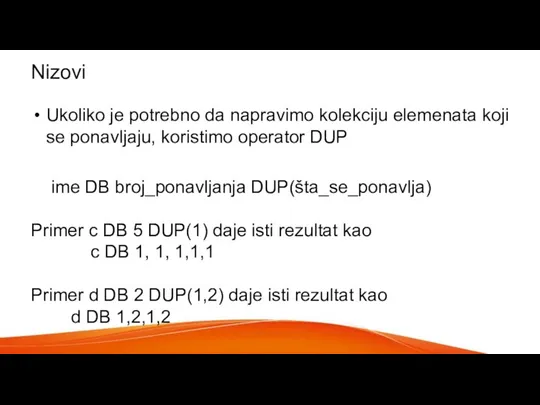

Ukoliko je potrebno da napravimo kolekciju elemenata koji se ponavljaju, koristimo operator

DUP

ime DB broj_ponavljanja DUP(šta_se_ponavlja)

Primer c DB 5 DUP(1) daje isti rezultat kao c DB 1, 1, 1,1,1

Primer d DB 2 DUP(1,2) daje isti rezultat kao d DB 1,2,1,2

Слайд 17Dobijanje adrese varijable

Kako bismo dobili adresu neke promenljive, koristimo instrukcije LEA (load

effective address) ili OFFSET.

Primer: LEA AX, varijabla

Слайд 18Prekidi

Prekide možemo posmatrati kao određene procedure koje se izvršavaju u nekom trenutku.

Možemo govoriti o hardverskim i o softverskim prekidima.

Hardverski prekidi nastaju nada neki hardverski uređaj pošalje signal procesoru da obradi neki rezultat

Softverski prekidi definisani su u kodu, i njihova uloga je da pozovu specijalne procedure.

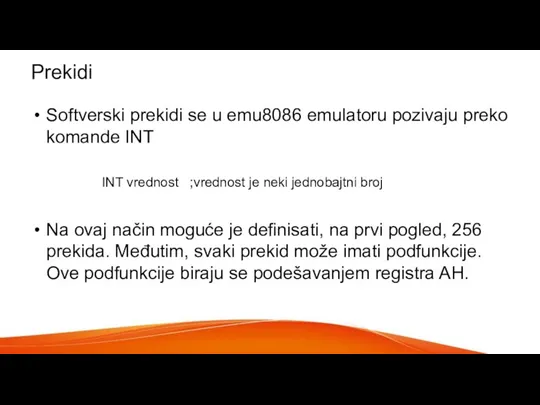

Слайд 19Prekidi

Softverski prekidi se u emu8086 emulatoru pozivaju preko komande INT

INT vrednost ;vrednost

je neki jednobajtni broj

Na ovaj način moguće je definisati, na prvi pogled, 256 prekida. Međutim, svaki prekid može imati podfunkcije. Ove podfunkcije biraju se podešavanjem registra AH.

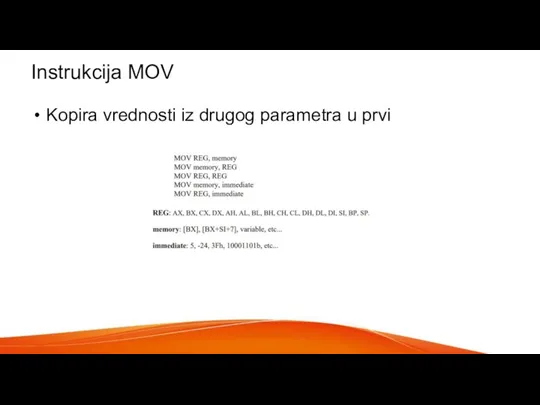

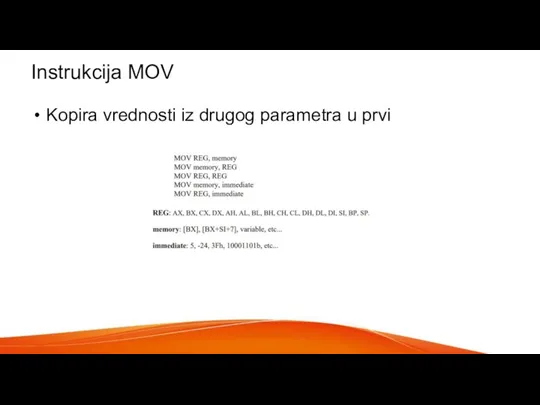

Слайд 20Instrukcija MOV

Kopira vrednosti iz drugog parametra u prvi

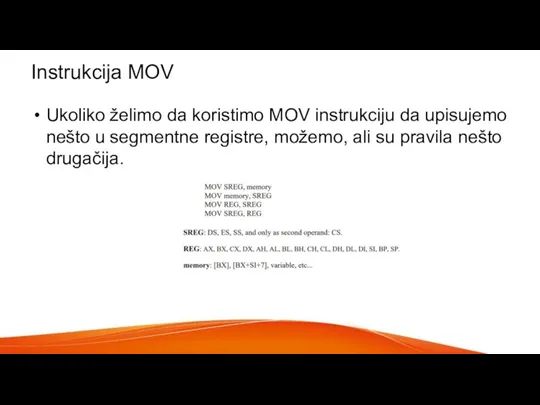

Слайд 21Instrukcija MOV

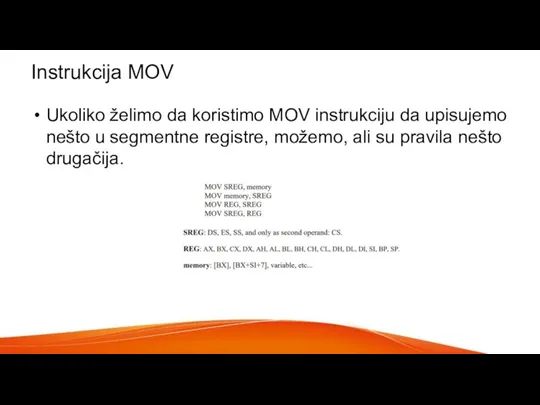

Ukoliko želimo da koristimo MOV instrukciju da upisujemo nešto u segmentne

registre, možemo, ali su pravila nešto drugačija.

Слайд 22Aritmetičke i logičke funkcije

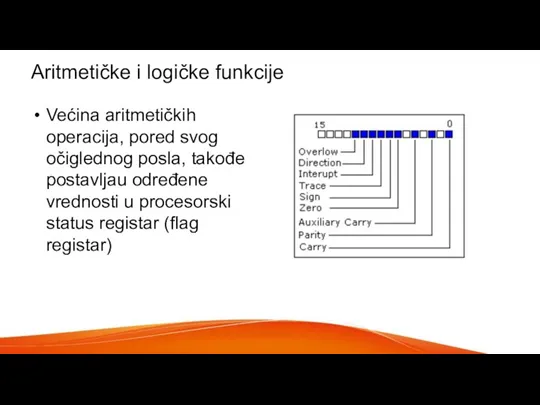

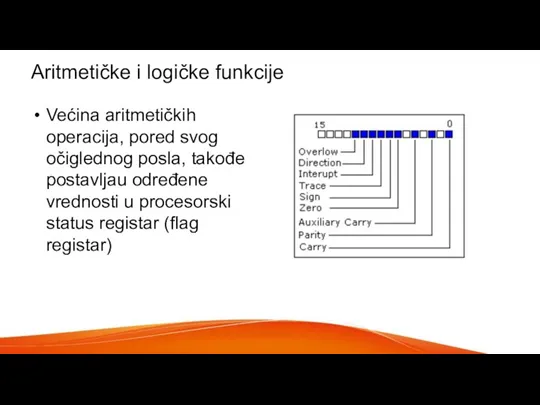

Većina aritmetičkih operacija, pored svog očiglednog posla, takođe postavljau

određene vrednosti u procesorski status registar (flag registar)

Слайд 23Aritmetičke i logičke funkcije

Carry Flag (CF) - postavljen na 1 kada postoji

neoznačeno prekoračenje

Zero Flag (ZF) - postaljen na 1 kada je rezultat operacije 0

Sign Flag (SF) -postavlje na 1 kada je rezultat negativan

Overflow Flag (OF) - postavljen na 1 kada postoji označeno prekoračenje

Слайд 24Aritmetičke i logičke funkcije

Parity Flag (PF) - postavljen na 1 kada postoji

paran broj bitova jedinice u rezultatu (postamtraju se samo najnižih 8 bitova)

Auxiliary Flag (AF) - postavljen na 1 ukoliko postoji neoznačeno prekoračenje na najnižoj nibli

Interrupt enable Flag (IF) - postavljen na 1 ukoliko CPU reaguje na prekide od eksternih uređaja

Direction Flag (DF) - za procesuiranje lanaca podataka, 0 ili jedan definišu smer u kojem se procesuiranje izvršava

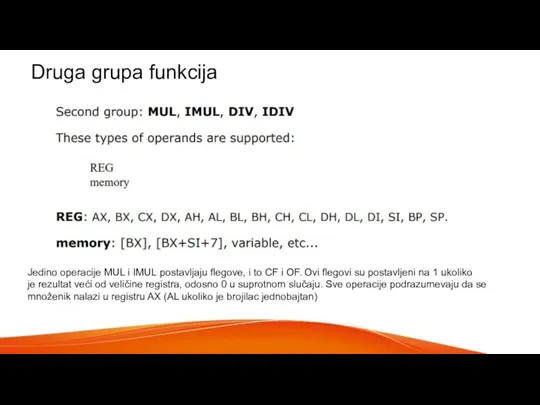

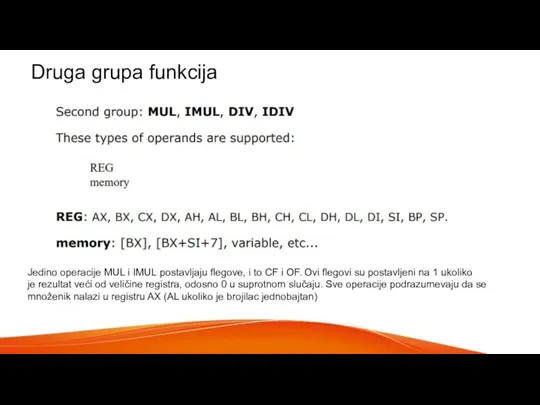

Слайд 26Druga grupa funkcija

Jedino operacije MUL i IMUL postavljaju flegove, i to CF

i OF. Ovi flegovi su postavljeni na 1 ukoliko

je rezultat veći od veličine registra, odosno 0 u suprotnom slučaju. Sve operacije podrazumevaju da se

množenik nalazi u registru AX (AL ukoliko je brojilac jednobajtan)

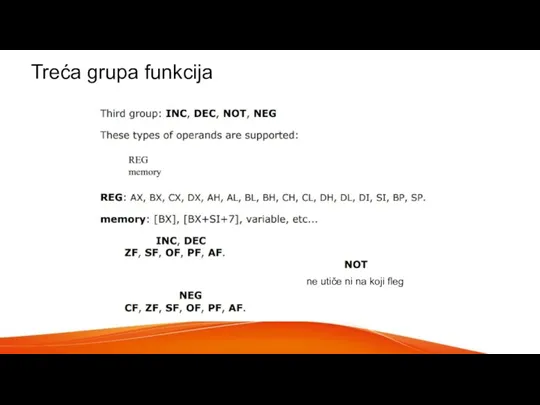

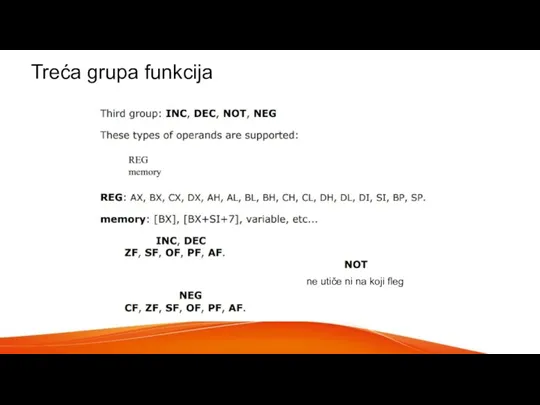

Слайд 27Treća grupa funkcija

ne utiče ni na koji fleg

Слайд 28Kontrola toka

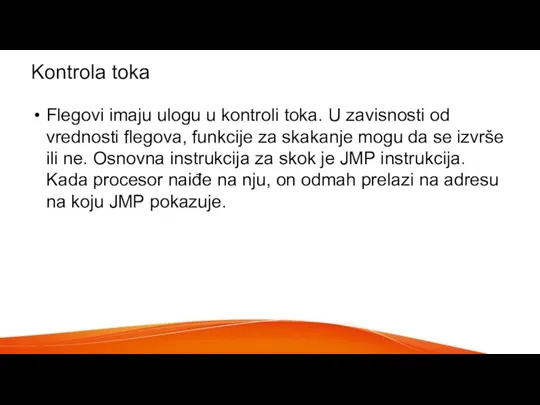

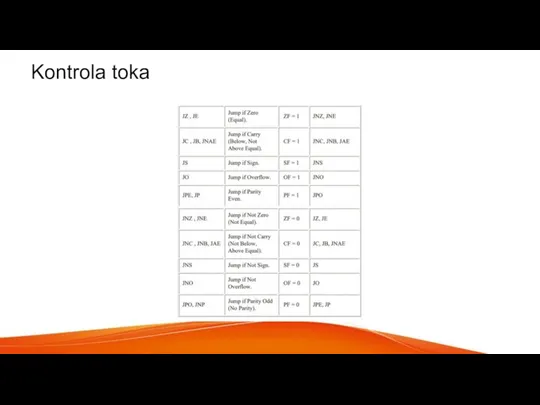

Flegovi imaju ulogu u kontroli toka. U zavisnosti od vrednosti flegova,

funkcije za skakanje mogu da se izvrše ili ne. Osnovna instrukcija za skok je JMP instrukcija. Kada procesor naiđe na nju, on odmah prelazi na adresu na koju JMP pokazuje.

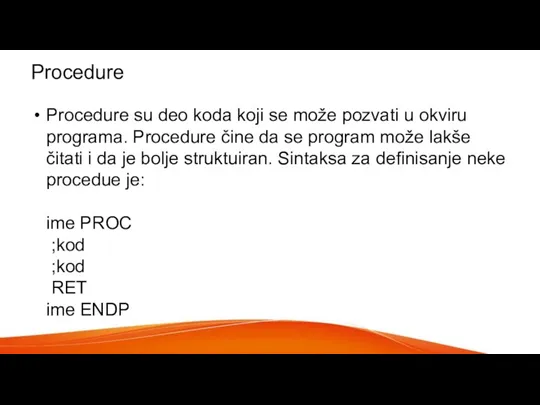

Слайд 30Procedure

Procedure su deo koda koji se može pozvati u okviru programa. Procedure

čine da se program može lakše čitati i da je bolje struktuiran. Sintaksa za definisanje neke procedue je:

ime PROC

;kod

;kod

RET

ime ENDP

Слайд 31Procedure

Kako bi se procedura pozvala, koristi se ključna reč CALL.

Слайд 32Stek

Uloga steka jeste u čuvanju privremenih podataka, kada treba da im se

pristupa po principu LIFO. Implicntno, stek se koristi kada se pozivaju instrukcije CALL i INT, kako bi se na njega postavila adresa povratka.

Povratak na tu adresu izvršava se instrukcijama RET (u slučaju CALL instrukcije), ondnosno IRET (u slučaju softverskog prekida)

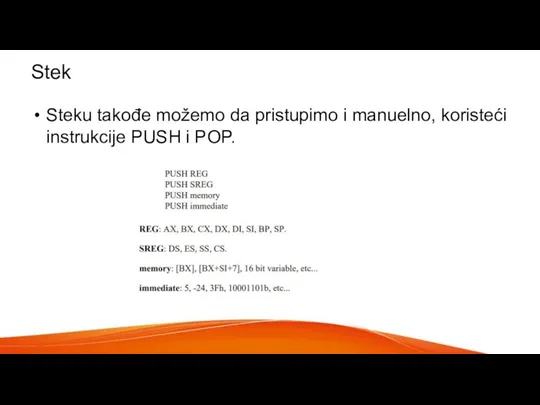

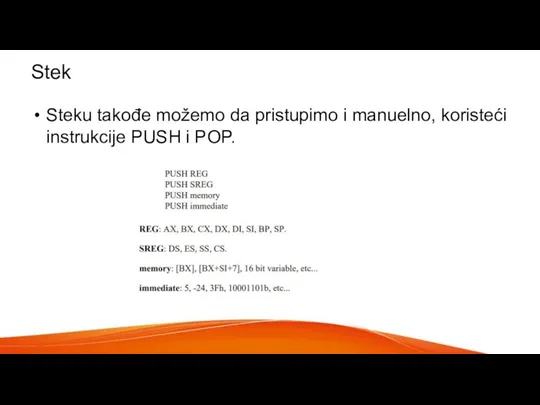

Слайд 33Stek

Steku takođe možemo da pristupimo i manuelno, koristeći instrukcije PUSH i POP.

Международное сотрудничество в области сертификации. Схемы сертификации. Добровольная и обязательная сертификация. Сделали: Тор

Международное сотрудничество в области сертификации. Схемы сертификации. Добровольная и обязательная сертификация. Сделали: Тор Международный день без интернета

Международный день без интернета Разделенный город как крайняя форма сегрегации городского пространства

Разделенный город как крайняя форма сегрегации городского пространства Японский виски

Японский виски Тема урока: «Прямоугольник и квадрат»

Тема урока: «Прямоугольник и квадрат» Гражданское общество и правовое государство

Гражданское общество и правовое государство Эллинистические государства в IV-IIв. до н.э. Эллинистическая культура

Эллинистические государства в IV-IIв. до н.э. Эллинистическая культура Hungry Frog

Hungry Frog Анонимные Наркоманы

Анонимные Наркоманы ТЕМА УРОКА:

ТЕМА УРОКА: Русский язык

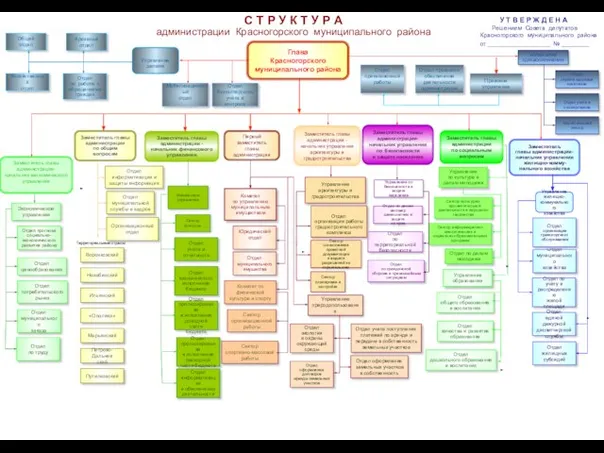

Русский язык С Т Р У К Т У Р А администрации Красногорского муниципального района

С Т Р У К Т У Р А администрации Красногорского муниципального района Презентация на тему Историко-культурные объекты, сформированные на территории средневекового Тараза Южного Казахстана

Презентация на тему Историко-культурные объекты, сформированные на территории средневекового Тараза Южного Казахстана Финансовая математика

Финансовая математика Реновация промышленных зданий

Реновация промышленных зданий Как менялась этика на протяжении веков

Как менялась этика на протяжении веков Классный час «Жизнь – это…»

Классный час «Жизнь – это…» Sale 30% Bestia

Sale 30% Bestia Presentation Title

Presentation Title  Продажа мобильного ПО своими руками

Продажа мобильного ПО своими руками Государственная (итоговая) аттестация выпускников 9-х классов

Государственная (итоговая) аттестация выпускников 9-х классов география

география Зеленый Меморандум СБ. Кейс 2

Зеленый Меморандум СБ. Кейс 2 Крещенские вечера

Крещенские вечера Институты и субинституты финансового права

Институты и субинституты финансового права Презентацию подготовил ученик 3 «А» класса ГОУ средней общеобразовательной школы № 511 Добролюбов Егор Учитель: Ваниосова Н.В.

Презентацию подготовил ученик 3 «А» класса ГОУ средней общеобразовательной школы № 511 Добролюбов Егор Учитель: Ваниосова Н.В. Приметы и суеверия. Les superstitions et les présages

Приметы и суеверия. Les superstitions et les présages Способы завязывания платков

Способы завязывания платков