Содержание

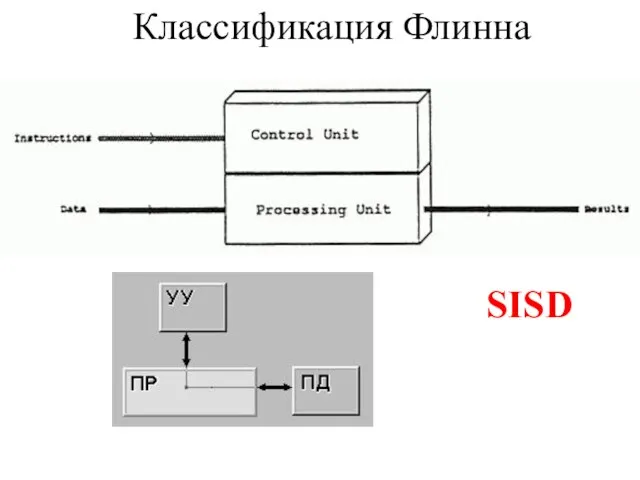

- 2. Классификация Флинна SISD

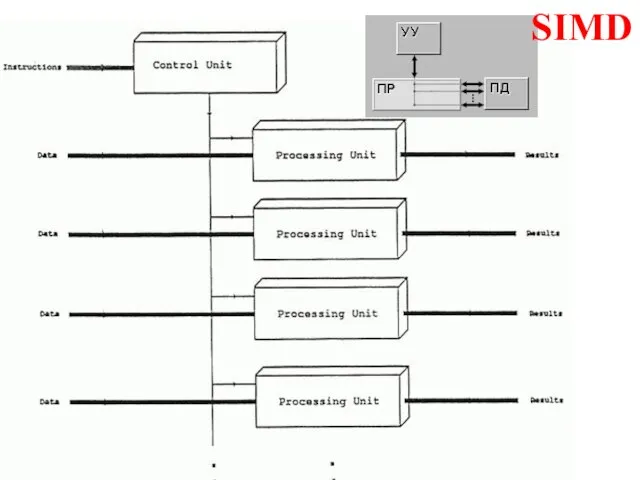

- 3. SIMD

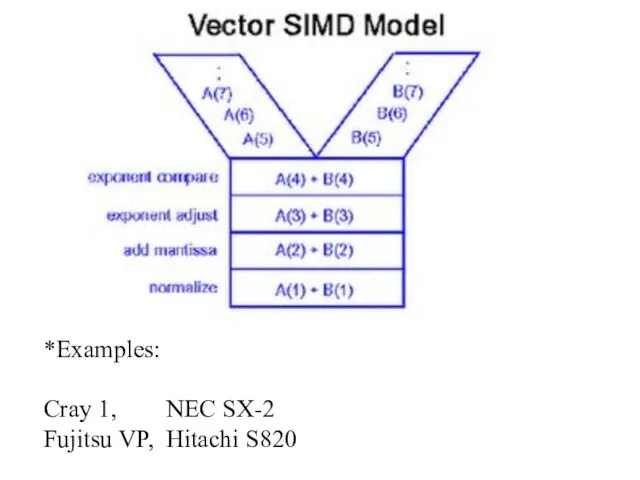

- 4. *Examples: Cray 1, NEC SX-2 Fujitsu VP, Hitachi S820

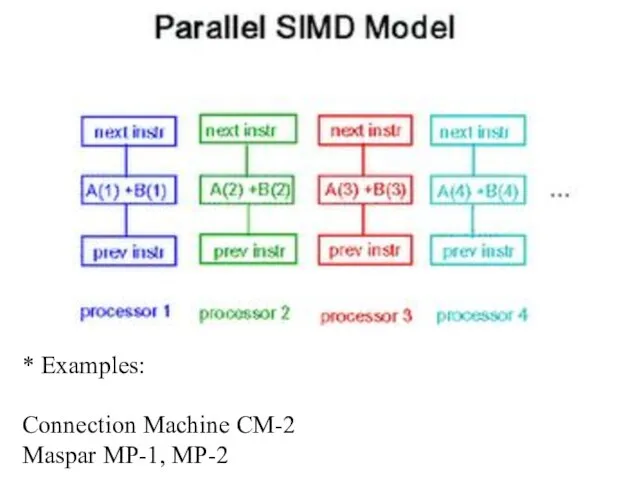

- 5. * Examples: Connection Machine CM-2 Maspar MP-1, MP-2

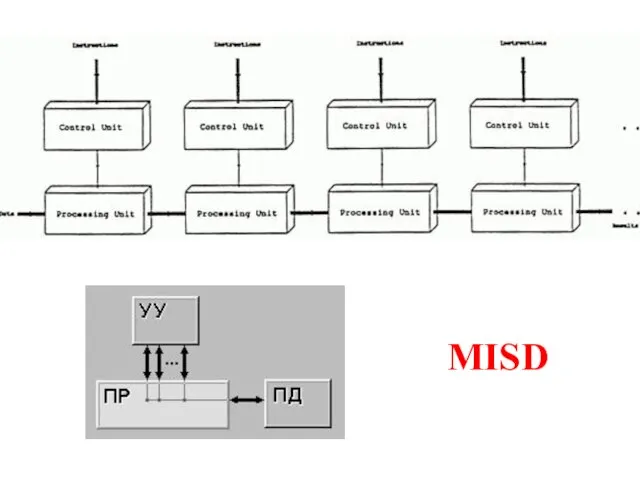

- 6. MISD

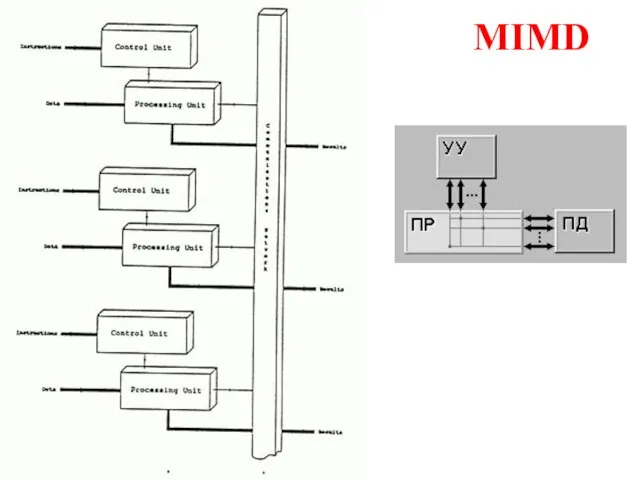

- 7. MIMD

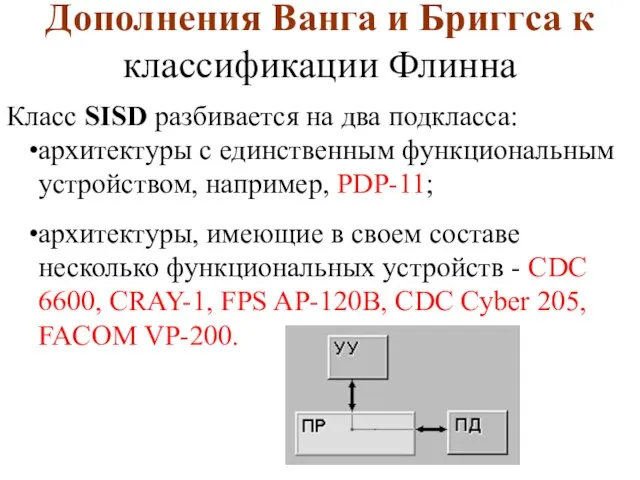

- 9. Дополнения Ванга и Бриггса к классификации Флинна Класс SISD разбивается на два подкласса: архитектуры с единственным

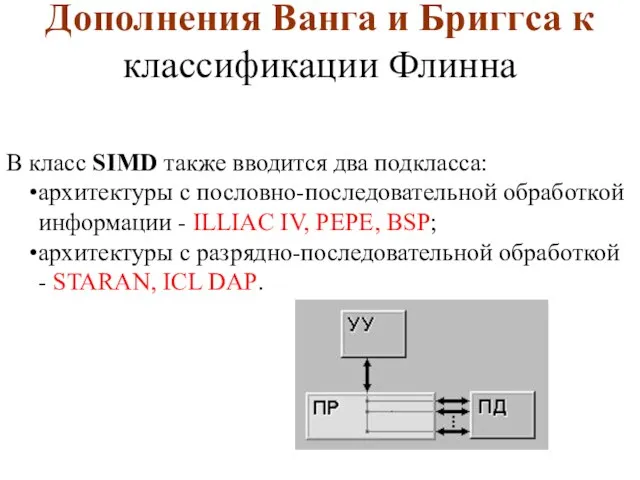

- 10. Дополнения Ванга и Бриггса к классификации Флинна В класс SIMD также вводится два подкласса: архитектуры с

- 11. Дополнения Ванга и Бриггса к классификации Флинна В классе MIMD авторы различают вычислительные системы со слабой

- 12. Классификация Хокни

- 13. Классификация Хокни Множественный поток команд может быть обработан двумя способами: либо одним конвейерным устройством обработки, работающем

- 14. Классификация Хокни Далее, среди MIMD машин с переключателем Хокни выделяет те, в которых вся память распределена

- 15. Классификация Хокни При рассмотрении MIMD машин с сетевой структурой считается, что все они имеют распределенную память,

- 17. Предлагается рассматривать архитектуру любого компьютера, как абстрактную структуру, состоящую из четырех компонент: процессор команд (IP -

- 18. Функции процессора команд во многом схожи с функциями устройств управления последовательных машин и, согласно Д.Скилликорну, сводятся

- 19. Функции процессора данных делают его во многом похожим на арифметическое устройство традиционных процессоров: DP получает от

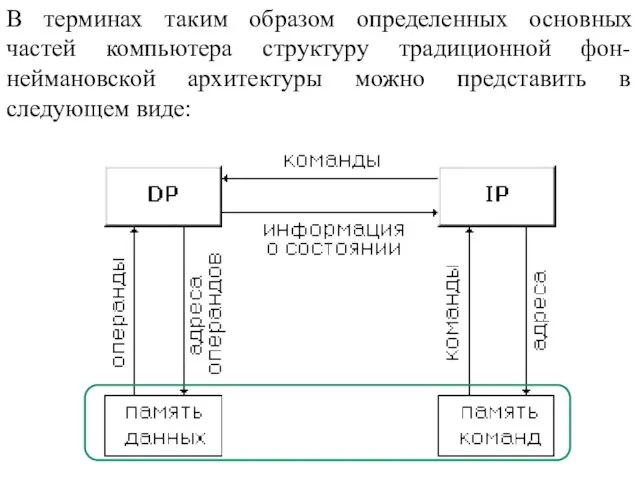

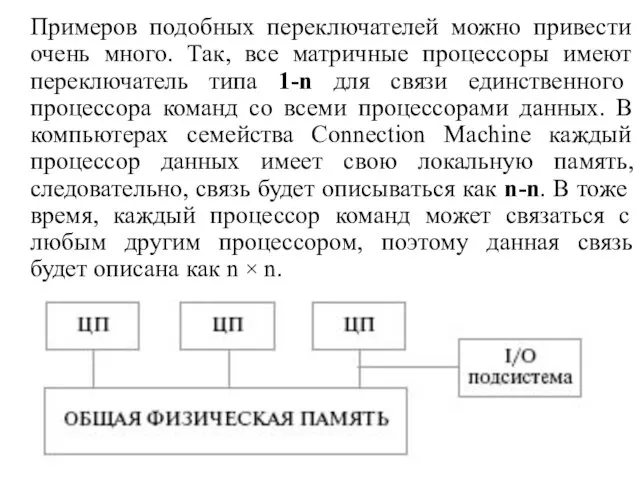

- 20. В терминах таким образом определенных основных частей компьютера структуру традиционной фон-неймановской архитектуры можно представить в следующем

- 21. Для описания параллельных вычислительных систем автор зафиксировал четыре типа переключателей, без какой-либо явной связи с типом

- 22. Примеров подобных переключателей можно привести очень много. Так, все матричные процессоры имеют переключатель типа 1-n для

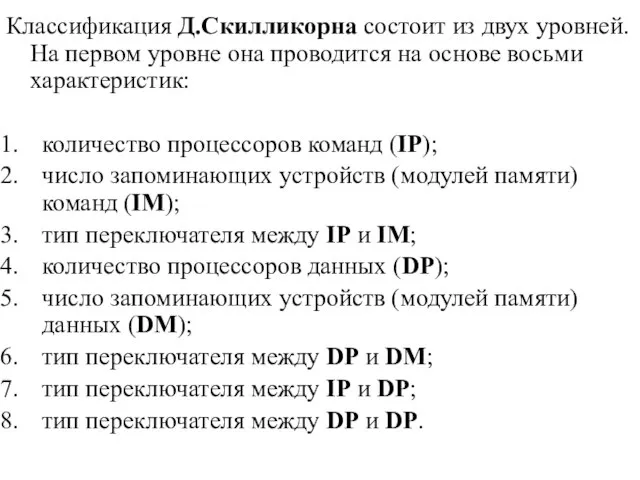

- 23. Классификация Д.Скилликорна состоит из двух уровней. На первом уровне она проводится на основе восьми характеристик: количество

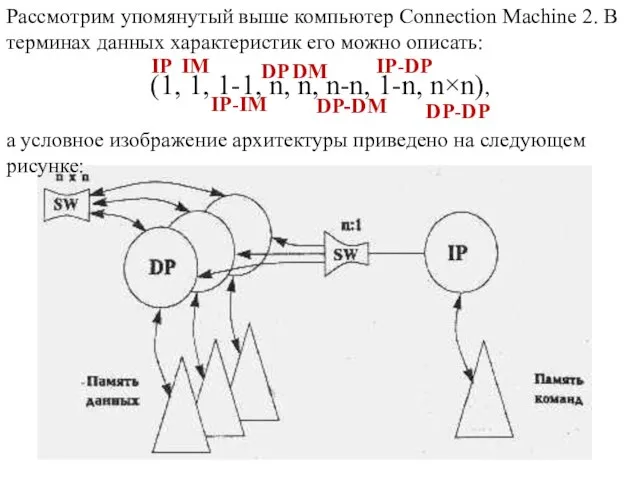

- 24. Рассмотрим упомянутый выше компьютер Connection Machine 2. В терминах данных характеристик его можно описать: IP IM

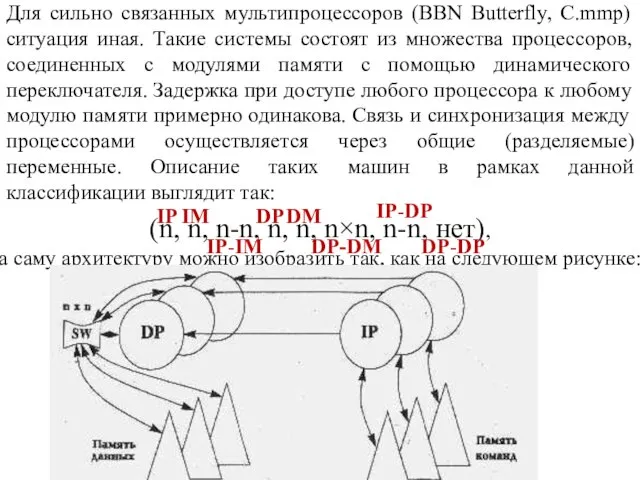

- 25. Для сильно связанных мультипроцессоров (BBN Butterfly, C.mmp) ситуация иная. Такие системы состоят из множества процессоров, соединенных

- 26. Используя введенные характеристики и предполагая, что рассмотрение количественных характеристик можно ограничить только тремя возможными вариантами значений:

- 27. На втором уровне классификации Д.Скилликорн просто уточняет описание, сделанное на первом уровне, добавляя возможность конвейерной обработки

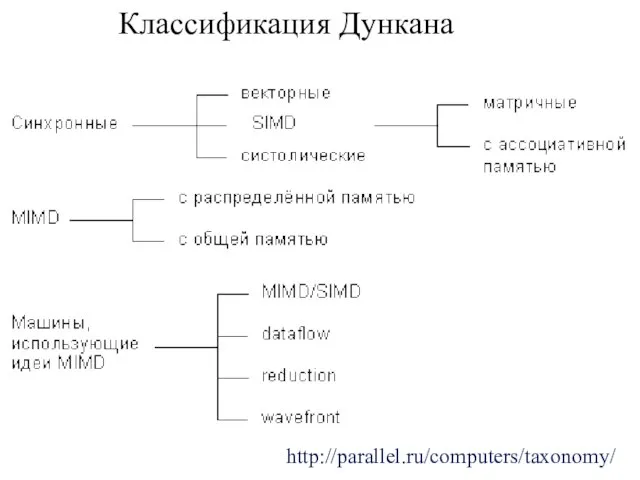

- 28. Классификация Дункана Из класса параллельных машин должны быть исключены те, в которых параллелизм заложен лишь на

- 29. Классификация Дункана Классификация должна быть согласованной с классификацией Флинна, показавшей правильность выбора идеи потоков команд и

- 30. Классификация Дункана http://parallel.ru/computers/taxonomy/

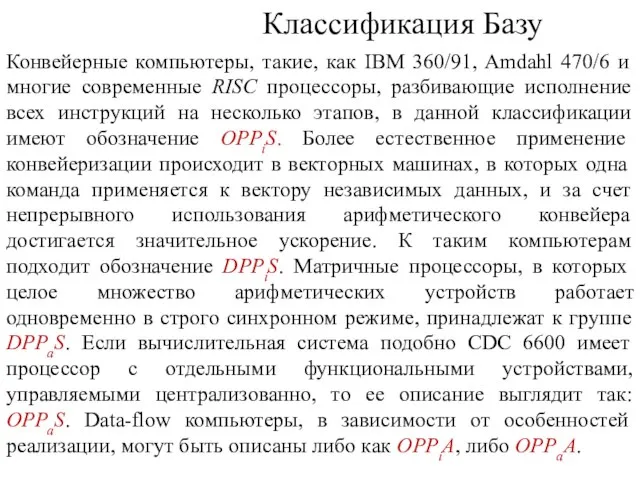

- 31. Классификация Базу

- 32. Классификация Базу Конвейерные компьютеры, такие, как IBM 360/91, Amdahl 470/6 и многие современные RISC процессоры, разбивающие

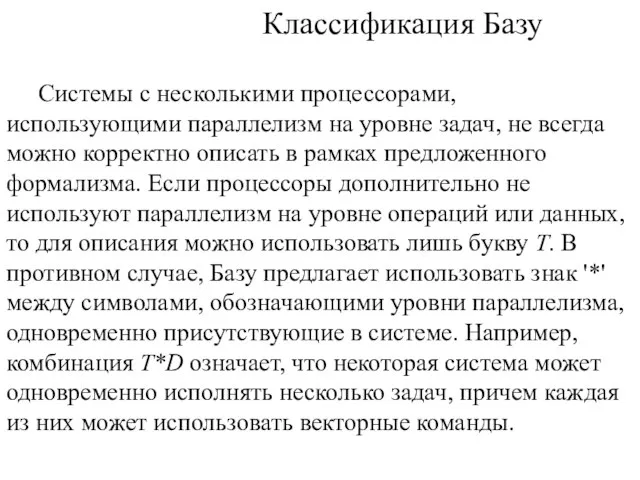

- 33. Классификация Базу Системы с несколькими процессорами, использующими параллелизм на уровне задач, не всегда можно корректно описать

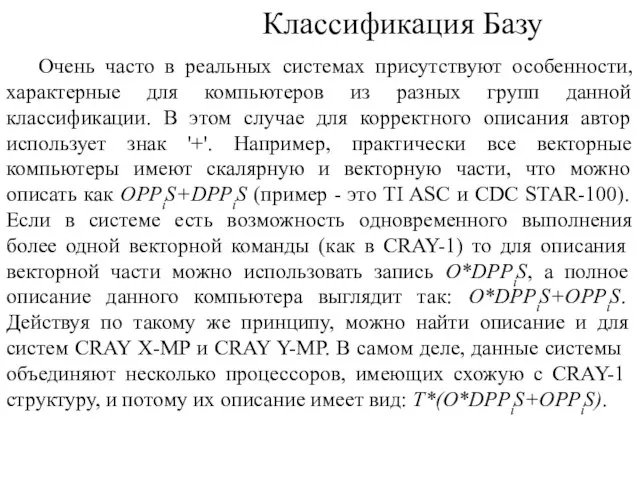

- 34. Классификация Базу Очень часто в реальных системах присутствуют особенности, характерные для компьютеров из разных групп данной

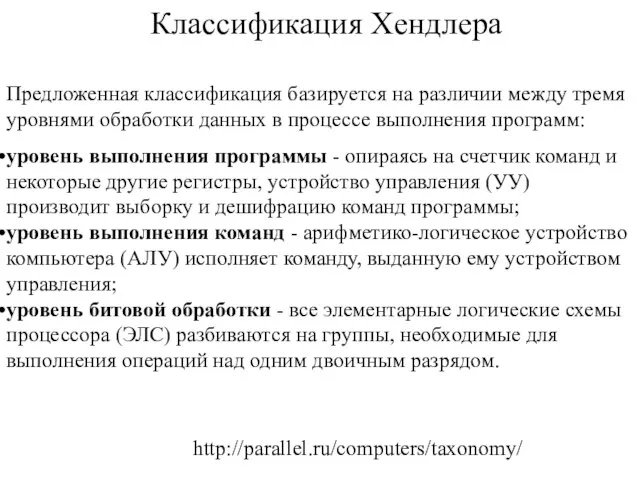

- 35. Классификация Хендлера http://parallel.ru/computers/taxonomy/ Предложенная классификация базируется на различии между тремя уровнями обработки данных в процессе выполнения

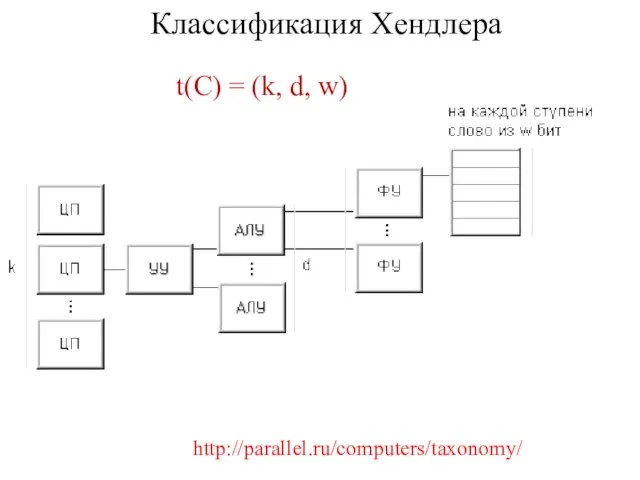

- 36. Классификация Хендлера http://parallel.ru/computers/taxonomy/ t(C) = (k, d, w)

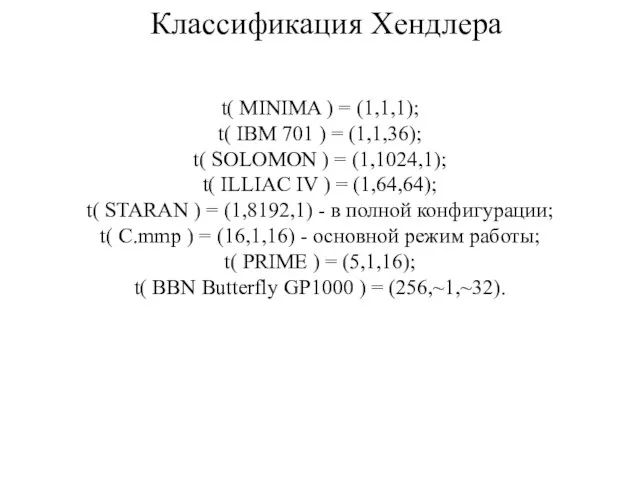

- 37. t( MINIMA ) = (1,1,1); t( IBM 701 ) = (1,1,36); t( SOLOMON ) = (1,1024,1);

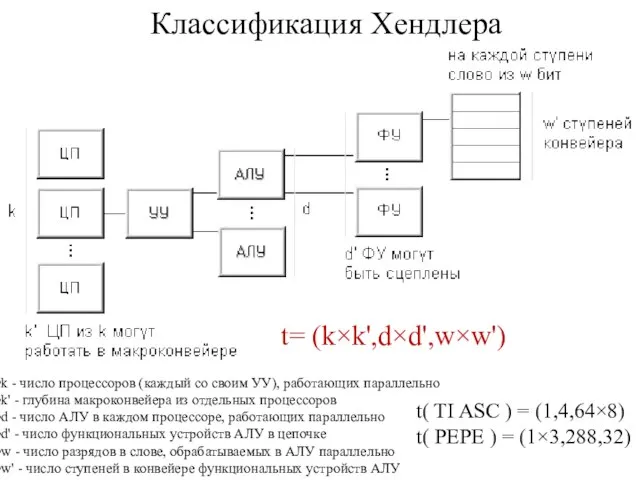

- 38. Классификация Хендлера t= (k×k',d×d',w×w') k - число процессоров (каждый со своим УУ), работающих параллельно k' -

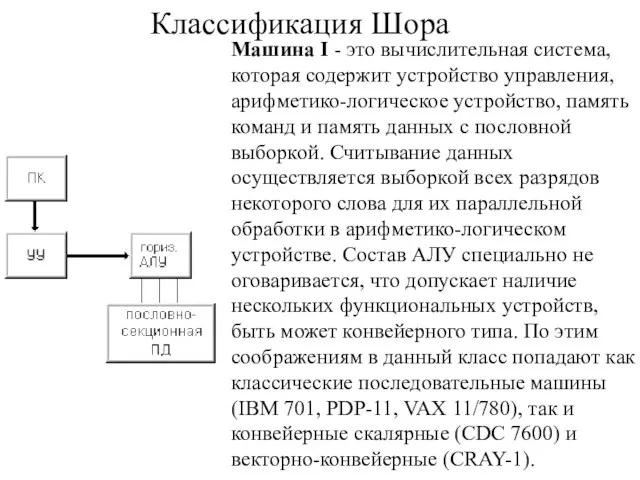

- 39. Классификация Шора Машина I - это вычислительная система, которая содержит устройство управления, арифметико-логическое устройство, память команд

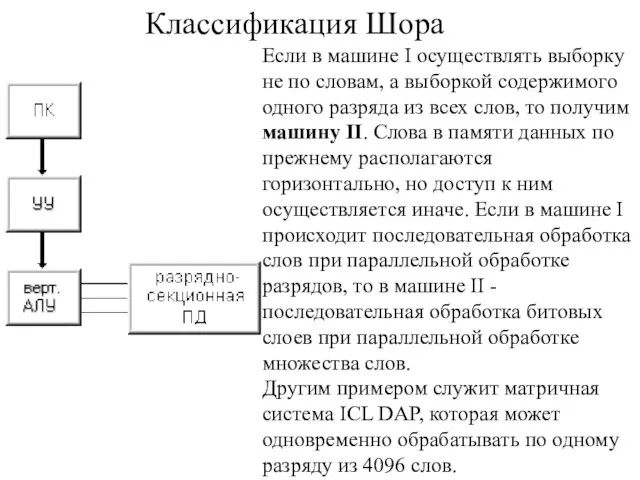

- 40. Классификация Шора Если в машине I осуществлять выборку не по словам, а выборкой содержимого одного разряда

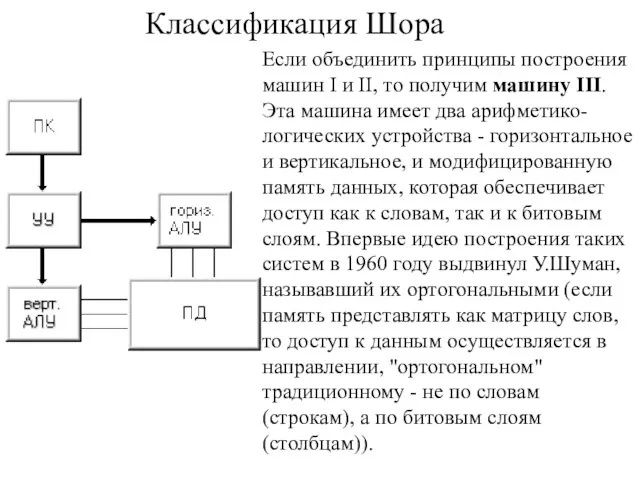

- 41. Классификация Шора Если объединить принципы построения машин I и II, то получим машину III. Эта машина

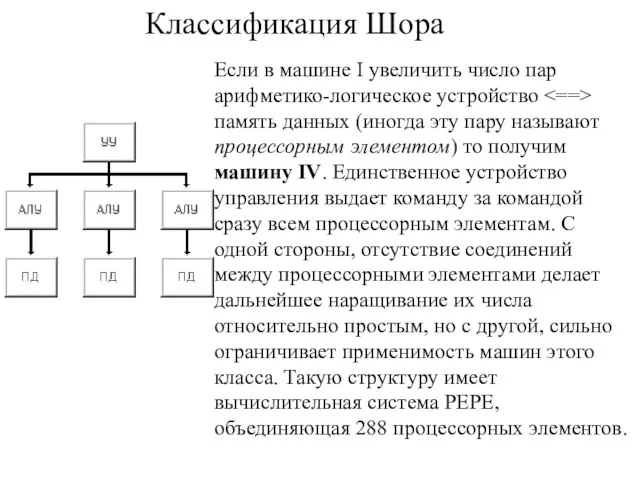

- 42. Классификация Шора Если в машине I увеличить число пар арифметико-логическое устройство память данных (иногда эту пару

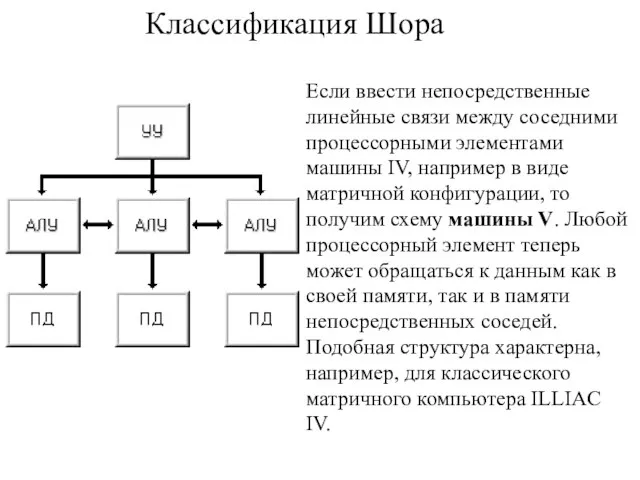

- 43. Классификация Шора Если ввести непосредственные линейные связи между соседними процессорными элементами машины IV, например в виде

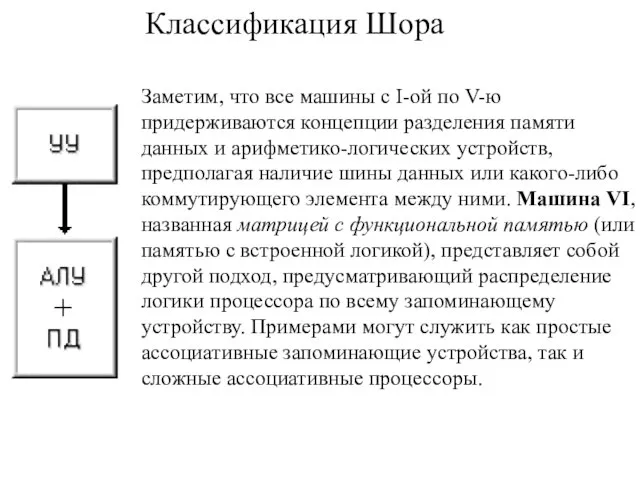

- 44. Классификация Шора Заметим, что все машины с I-ой по V-ю придерживаются концепции разделения памяти данных и

- 45. Классификация Шнайдера В 1988 году Л.Шнайдер (L.Snyder) предложил новый подход [16] к описанию архитектур параллельных вычислительных

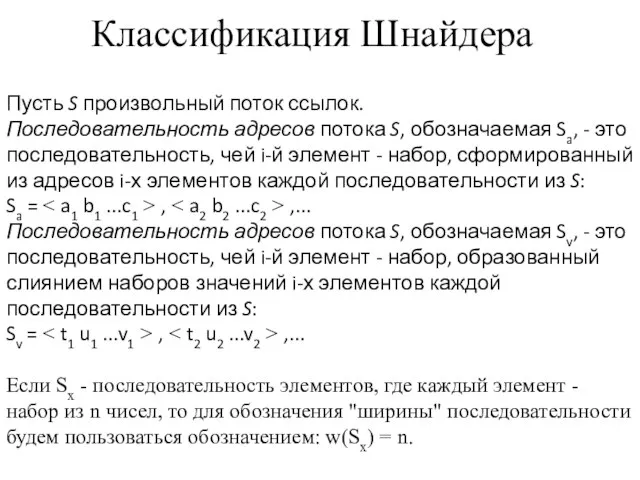

- 46. Пусть S произвольный поток ссылок. Последовательность адресов потока S, обозначаемая Sa, - это последовательность, чей i-й

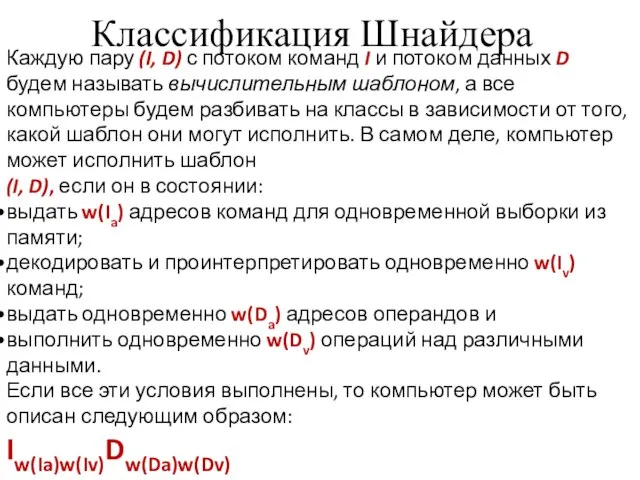

- 47. Классификация Шнайдера Каждую пару (I, D) с потоком команд I и потоком данных D будем называть

- 48. Классификация Шнайдера Рассмотрим классическую последовательную машину. Согласно классификации Флинна, она попадает в класс SISD, следовательно |I|

- 49. Классификация Шнайдера Теперь возьмем две машину из класса SIMD Goodyear Aerospace MPP Единственный поток команд означает

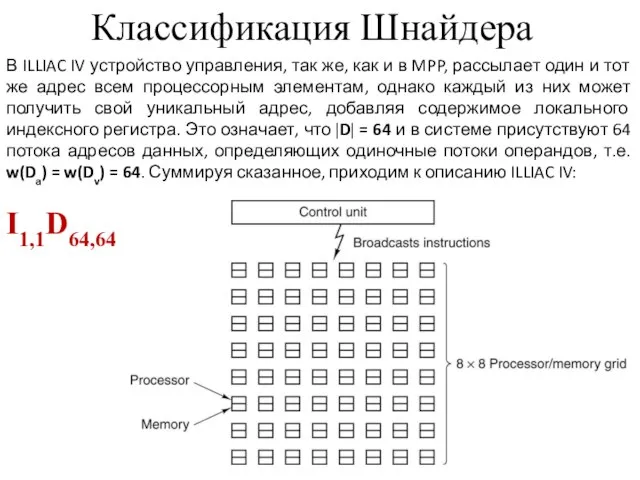

- 50. Классификация Шнайдера В ILLIAC IV устройство управления, так же, как и в MPP, рассылает один и

- 51. Классификация Шнайдера Для более четкой классификации Шнайдер вводит три предиката для обозначения значений, которые могут принимать

- 53. Скачать презентацию

![Классификация Шнайдера В 1988 году Л.Шнайдер (L.Snyder) предложил новый подход [16] к](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/409374/slide-44.jpg)

«Обзор законодательства Республики Казахстан в сфере социальной поддержки и обеспечения социальными услугами»

«Обзор законодательства Республики Казахстан в сфере социальной поддержки и обеспечения социальными услугами» Роспись петуха по мотивам Филимоновской росписи

Роспись петуха по мотивам Филимоновской росписи Гражданское право. Понятие и виды сроков в гражданском праве

Гражданское право. Понятие и виды сроков в гражданском праве Модернизм

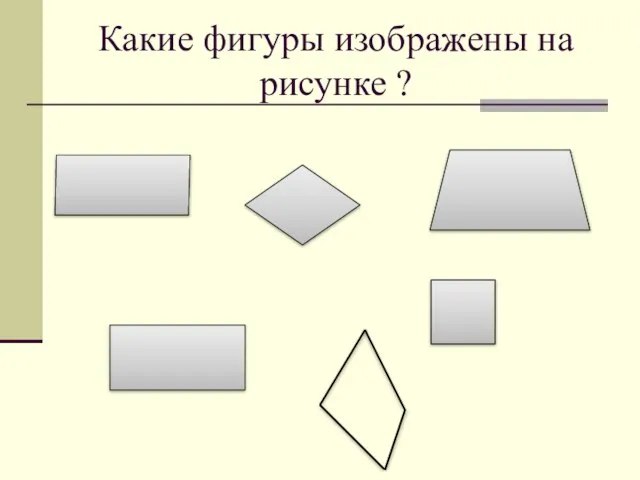

Модернизм Какие фигуры изображены на рисунке ?

Какие фигуры изображены на рисунке ? Перенос слова переносятся по слогам

Перенос слова переносятся по слогам Принтеры

Принтеры Методическая разработка «Создание презентаций» Элективный курс для 10 класса.

Методическая разработка «Создание презентаций» Элективный курс для 10 класса. Вейк-лебедка - летний бизнес. Вейкпарк в пляжной зоне

Вейк-лебедка - летний бизнес. Вейкпарк в пляжной зоне Федеральное Собрание РФ

Федеральное Собрание РФ Инжиниринг нефтехимии и нефтегазопереработки

Инжиниринг нефтехимии и нефтегазопереработки Китайский клуб МИИТа

Китайский клуб МИИТа Мой город, с тебя начинается Родина (город Сатка)

Мой город, с тебя начинается Родина (город Сатка) Спартакиада пенсионеров муниципального образования Город Гатчина

Спартакиада пенсионеров муниципального образования Город Гатчина Эры. Основные события органического мира

Эры. Основные события органического мира Презентация на тему Операционные системы на мобильных устройствах

Презентация на тему Операционные системы на мобильных устройствах  Живопись

Живопись Михайленко Юлия Борисовна учитель начальных классов ГБОУ гимназии № 1518 г. Москвы

Михайленко Юлия Борисовна учитель начальных классов ГБОУ гимназии № 1518 г. Москвы Муниципальное общеобразовательное учреждение лингвистическая гимназия № 70

Муниципальное общеобразовательное учреждение лингвистическая гимназия № 70 МОСКВА- ГОРОД ГЕРОЙ . Битва за Москву(30 сентября 1941- 20 апреля 1942)

МОСКВА- ГОРОД ГЕРОЙ . Битва за Москву(30 сентября 1941- 20 апреля 1942) Векторы в пространстве и не только

Векторы в пространстве и не только Презентация на тему История развития отечественной вычислительной техники

Презентация на тему История развития отечественной вычислительной техники Трансформация изображения через трансформацию формы - серия открыток

Трансформация изображения через трансформацию формы - серия открыток ОРНАМЕНТЫ в национальном костюме

ОРНАМЕНТЫ в национальном костюме Цветник для солнечного места “Степной бриз ”

Цветник для солнечного места “Степной бриз ” Презентация на тему Тургенев. Стихи в прозе

Презентация на тему Тургенев. Стихи в прозе 287 Воскресшему служу я

287 Воскресшему служу я Берлину заменить Северный поток-2 другим проектом

Берлину заменить Северный поток-2 другим проектом