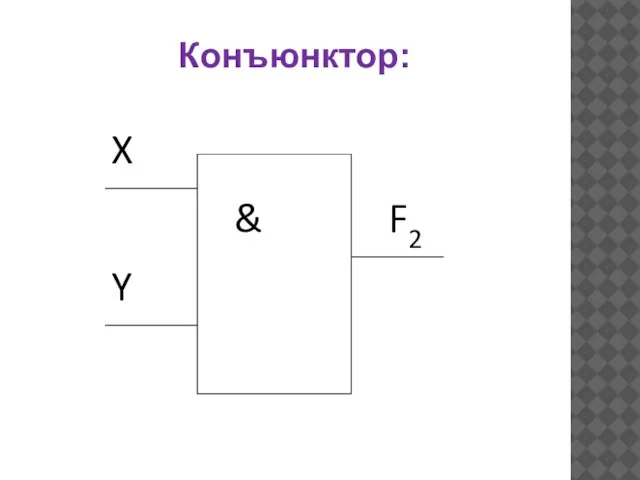

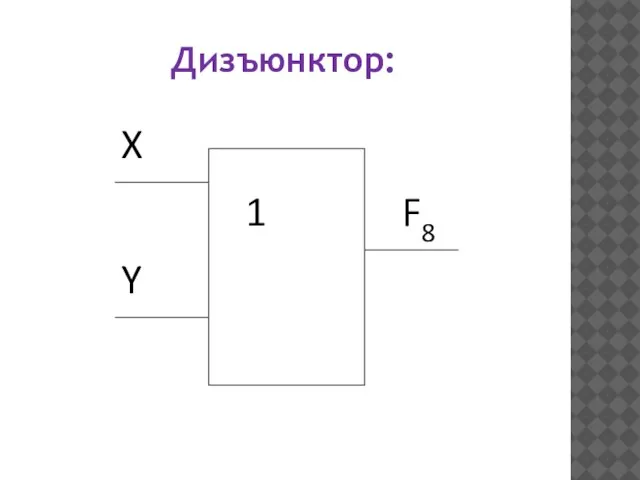

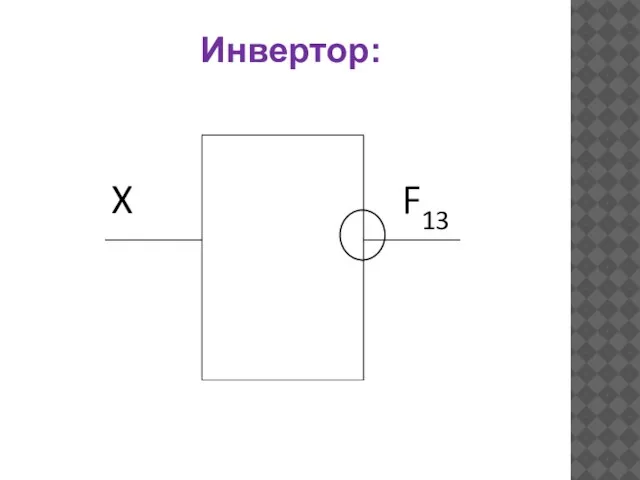

Слайд 2Дискретный преобразователь, который после обработки входных двоичных сигналов выдает на выходе сигнал,

являющийся значением одной из логических операций, называется логическим элементом.

Устройства компьютера (сумматоры в процессоре, ячейки памяти в оперативной памяти и т.д) строятся на основе базовых логических элементов.

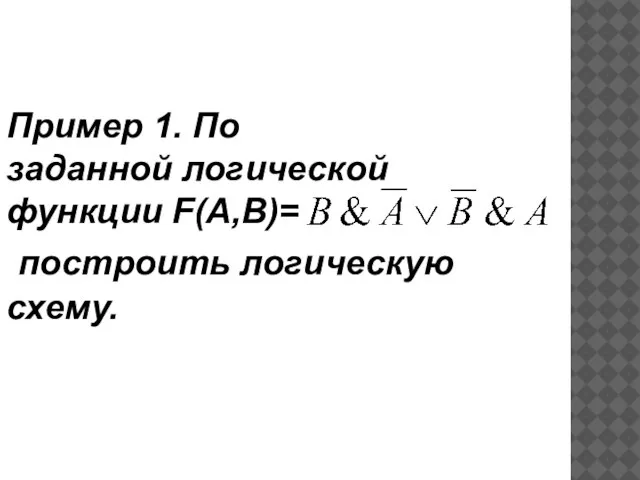

Слайд 6Пример 1. По заданной логической функции F(A,B)=

построить логическую схему.

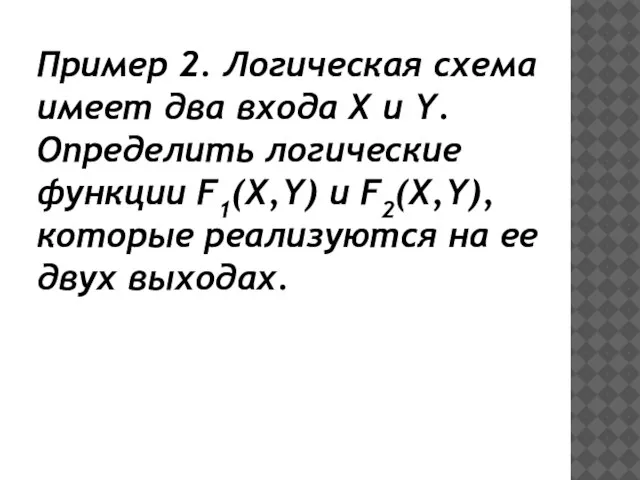

Слайд 7Пример 2. Логическая схема имеет два входа X и Y. Определить логические

функции F1(X,Y) и F2(X,Y), которые реализуются на ее двух выходах.

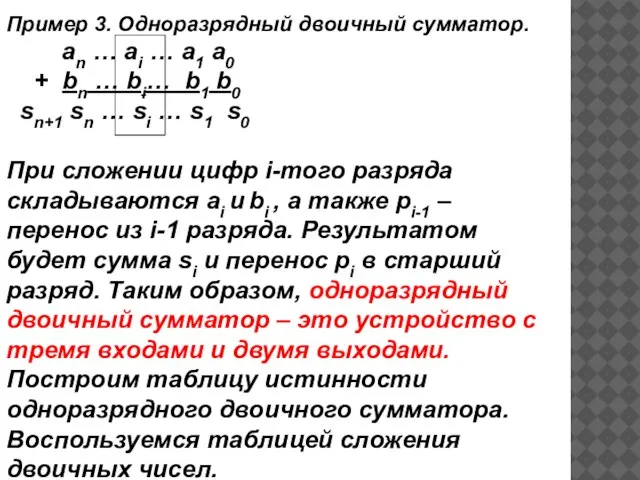

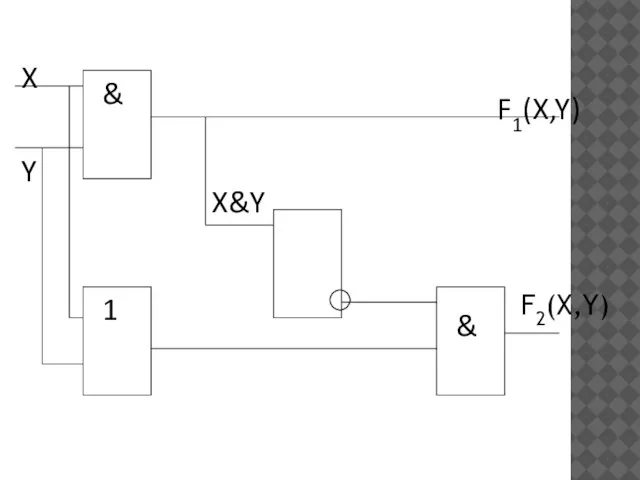

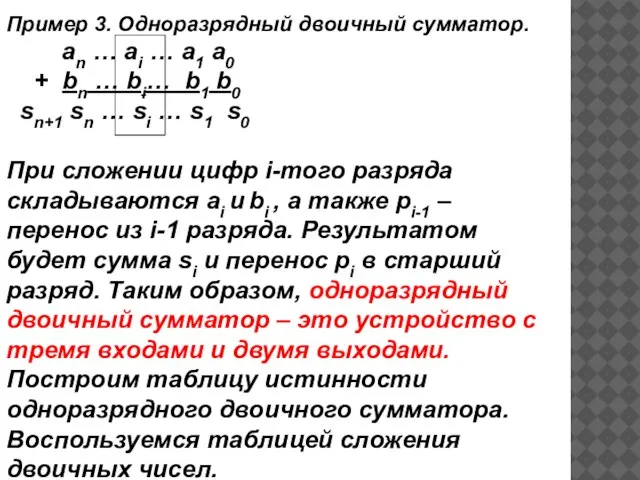

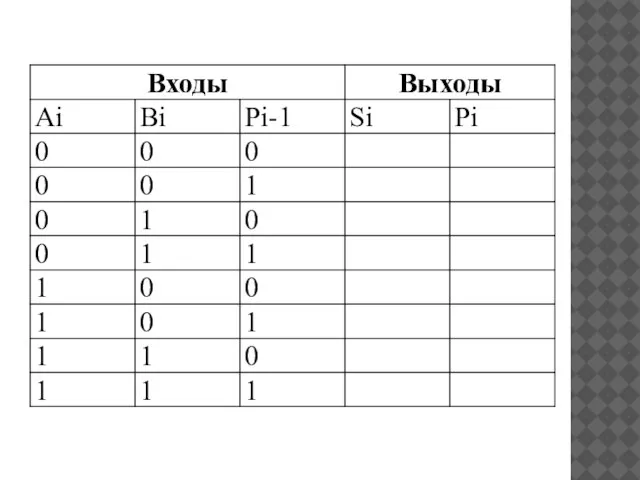

Слайд 9Пример 3. Одноразрядный двоичный сумматор.

an … ai … a1 a0

+

bn … bi… b1 b0

sn+1 sn … si … s1 s0

При сложении цифр i-того разряда складываются ai и bi , а также pi-1 – перенос из i-1 разряда. Результатом будет сумма si и перенос pi в старший разряд. Таким образом, одноразрядный двоичный сумматор – это устройство с тремя входами и двумя выходами.

Построим таблицу истинности одноразрядного двоичного сумматора. Воспользуемся таблицей сложения двоичных чисел.

Слайд 11Триггер.

Для хранения информации в оперативной памяти компьютера, а также во внутренних регистрах

процессора используются триггеры. Триггер может находиться в одном из двух устойчивых состояний, что позволяет запоминать, хранить и считывать 1 бит информации.

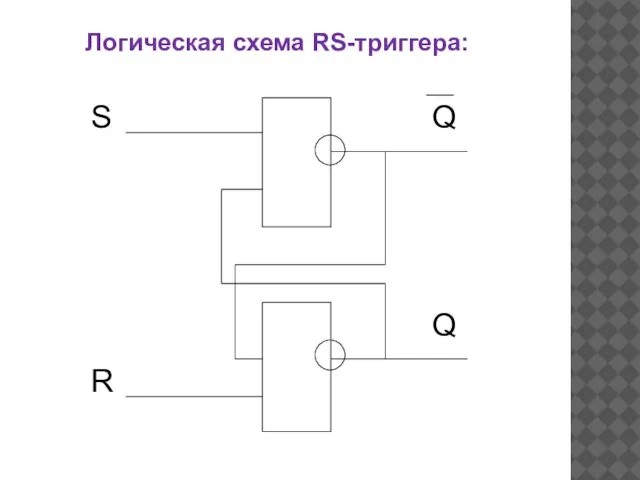

Слайд 12Самый простой триггер – RS-триггер. Он состоит из двух логических элементов ИЛИ-НЕ,

которые реализуют логическую функцию F9.

Входы и выходы элементов соединены кольцом: выход первого соединен со входом второго и выход второго со входом первого.

Триггер имеет два входа S (set-установка) и R(reset-сброс) и два выхода Q (прямой) и Q (инверсный).

Слайд 15Автор презентации:

Ширяева Ольга Мухадинновна,

Муниципальное Общеобразовательное Учреждение

«Средняя общеобразовательная школа №2»,

учитель информатики,

1 квалификационной категории.

http://www.shiryaeva.86sch2-nyagan.edusite.ru

Искусство эпохи возрождения в Италии

Искусство эпохи возрождения в Италии Передача оценки аудио в периметр ЕРЦ по Волгограду

Передача оценки аудио в периметр ЕРЦ по Волгограду Фитнес для людей с ограниченными возможностями

Фитнес для людей с ограниченными возможностями Особенности локализации в области e-Learningна примере проектов NETg и MicrosoftКомпания «Логрус»Май 2007

Особенности локализации в области e-Learningна примере проектов NETg и MicrosoftКомпания «Логрус»Май 2007 Значение физической культуры и спорта в жизни человека

Значение физической культуры и спорта в жизни человека НАНОТЕХНОЛОГИИ

НАНОТЕХНОЛОГИИ Проект «Программа развития образовательного учреждения»

Проект «Программа развития образовательного учреждения» Понятие о правоотношениях в сфере физической культуры и спорта. Билет 2

Понятие о правоотношениях в сфере физической культуры и спорта. Билет 2 Молодежный билет

Молодежный билет Античная философия

Античная философия Организационное собрание с первокурсниками Академии архитектуры и искусств Южного федерального университета 1 сентября 2021

Организационное собрание с первокурсниками Академии архитектуры и искусств Южного федерального университета 1 сентября 2021 Качественное исследование. Понятие, сущность, особенности

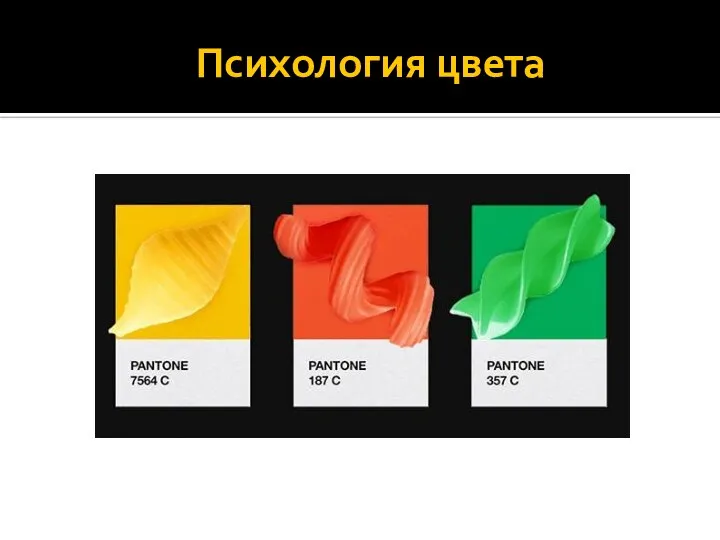

Качественное исследование. Понятие, сущность, особенности Психология цвета

Психология цвета Универсальные меры предосторожности

Универсальные меры предосторожности RU TV

RU TV Великие химики

Великие химики Виды памяти, вытесняющие статическую память

Виды памяти, вытесняющие статическую память Оценка эффективности использования комплекса маркетинговых инструментов в аптечном пространстве Олег Фельдман, КОМКОН-Фарма, Г

Оценка эффективности использования комплекса маркетинговых инструментов в аптечном пространстве Олег Фельдман, КОМКОН-Фарма, Г Пошив спортивной формы и экипировки для всех видов спорта с нанесением символики

Пошив спортивной формы и экипировки для всех видов спорта с нанесением символики Дружок

Дружок Карнавал животных

Карнавал животных Метод подстановки решения систем уравнений

Метод подстановки решения систем уравнений Формы знаний о мире

Формы знаний о мире Janssen_digital_diary_v.04

Janssen_digital_diary_v.04 Поисковый спам как способ заработка Иван Васильевич

Поисковый спам как способ заработка Иван Васильевич Комплексный анализ каузативных конструкций в итальянском языке

Комплексный анализ каузативных конструкций в итальянском языке What can he do?

What can he do? Алкоголизм и его влияние на развитие здоровой личности

Алкоголизм и его влияние на развитие здоровой личности